流时钟生成器及包括该流时钟生成器的嵌入式DisplayPort系统的制作方法

流时钟生成器及包括该流时钟生成器的嵌入式displayport系统

技术领域

1.本公开涉及一种嵌入式displayport系统,更具体地,涉及一种能够生成与面板自刷新模式之前的正常模式中的流时钟具有相同频率的流时钟的装置,以及一种包括该装置的嵌入式displayport系统。

背景技术:

2.嵌入式displayport是依赖于具有数字通信形式的分组化数据的传输的显示接口。嵌入式displayport的协议基于数据分组执行通信,并且可具有嵌入在流数据中的时钟信号。

3.视频电子标准协会(vesa)提出了嵌入式displayport标准版本中的面板自刷新模式。面板自刷新模式是一种降低系统级功耗的方法。

4.当要显示的图像在多个显示帧期间具有静态状态时,嵌入式displayport执行面板自刷新模式。

5.在面板自刷新模式中,嵌入式displayport不接收其中嵌入有时钟的流数据,并且使用存储在内部帧缓冲器中的图像数据来显示相同的图像。

6.嵌入式displayport需要时钟生成电路,用于生成与面板自刷新模式之前的正常模式中的流时钟具有相同频率的流时钟,因为嵌入式displayport在面板自刷新模式中不接收时钟。

技术实现要素:

7.各种实施方式旨在提供一种能够生成与面板自刷新模式之前的正常模式中的流时钟具有相同频率的流时钟的装置以及包括该装置的嵌入式displayport系统。

8.在实施方式中,流时钟生成器可包括:内部振荡器,其配置为振荡内部时钟;频率调节器,其配置为比较内部时钟和链路符号时钟的频率,生成控制信号,并且使用控制信号调节内部时钟的频率,其中,链路符号时钟是从嵌入式displayport系统的流数据重构的;以及锁相环路,其配置为使用内部时钟生成流时钟,并且将流时钟的相位锁定到内部时钟的相位。

9.在实施方式中,嵌入式displayport系统可包括源设备和接收设备,源设备配置为在正常模式下提供流数据,接收设备配置为在正常模式下从流数据重构链路符号时钟,振荡内部时钟,比较内部时钟和链路符号时钟的频率,并调节内部时钟的频率,以及配置成在面板自刷新模式下使用内部时钟生成具有恒定频率的流时钟,以及使用流时钟将存储在帧缓冲器中的图像数据显示在显示面板上。

10.在实施方式中,嵌入式displayport系统可包括接收器和时序控制器,接收器配置成从接收的流数据重构链路符号时钟,时序控制器配置成控制待振荡的内部时钟、待比较的内部时钟和链路符号时钟的频率、待调节的内部时钟的频率、待使用内部时钟生成的具

有恒定频率的流时钟、以及存储在帧缓冲器中的待使用流时钟显示在显示面板上的图像数据。

附图说明

11.图1是根据实施方式的嵌入式displayport系统的框图。

12.图2是根据实施方式的流时钟生成器的框图。

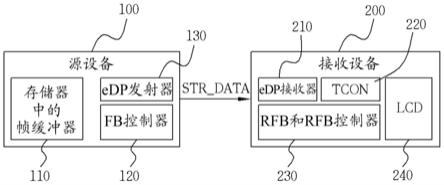

13.图3是示出根据实施方式的根据内部振荡器的控制信号的值的内部振荡器的输出频率特性的曲线图。

14.图4是根据实施方式的用于描述当内部振荡器进入面板自刷新模式时内部振荡器的操作的时序图。

具体实施方式

15.下面将参考附图更详细地描述示例性实施方式。然而,本公开可以以不同的形式实施,并且不应构造为限于本文中所述的实施方式。相反,提供这些实施方式使得本公开将是彻底的和完整的,并且将本公开的范围完全传达给本领域技术人员。在整个公开中,在本公开的各个附图和实施方式中,相同的附图标记表示相同的部件。

16.实施方式提供了一种能够生成与面板自刷新模式之前的正常模式中的流时钟具有相同频率的流时钟的装置,以及一种包括该装置的嵌入式displayport系统。

17.正常模式可限定为由接收设备重构由嵌入式displayport系统的源设备传送的图像数据并在显示面板上显示该图像数据的操作。

18.此外,面板自刷新模式是源设备与接收设备之间的可选功能,用于降低嵌入式displayport系统的功耗。面板自刷新模式可限定为在当待显示的图像数据是静态图像时源设备关闭且接收设备未关闭的状态下,使用存储在帧缓冲器中的图像数据在显示面板上显示静态图像的操作。

19.图1是根据实施方式的嵌入式displayport系统的框图。

20.参照图1,displayport系统可包括源设备100和接收设备200。

21.源设备100向接收设备200提供流数据str_data。在这种情况下,流数据str_data可具有嵌入其中的图像数据和链路符号时钟。

22.源设备100可在正常模式下向接收设备200提供流数据str_data。当待显示的图像具有静态状态时,源设备100可向接收设备200传送面板自刷新模式的进入信号,并且可被关闭。

23.源设备100可包括帧缓冲器110、帧缓冲器(fb)控制器120和发射器(tx)130。

24.帧缓冲器110存储要以帧为单位传送的图像数据。fb控制器120控制帧缓冲器110中的图像数据以帧为单位存储,并且控制存储在帧缓冲器110中的图像数据以帧为单位输出至发射器130。发射器130将存储在帧缓冲器110中的图像数据转换为根据嵌入式显示端口的协议限定的信号形式,并将其中嵌入了图像数据和链路符号时钟的流数据str_data传送至接收设备200。

25.接收设备200从源设备100接收流数据str_data,从流数据str_data重构图像数据和链路符号时钟,使用链路符号时钟生成流时钟,并且使用流时钟在显示面板上显示图像

数据。

26.接收设备200可包括接收器(rx)210、时序控制器(tcon)220、远程帧缓冲器(rfb)和rfb控制器230、以及显示面板(lcd)240。

27.接收器210从由源设备100传送的流数据str_data重构图像数据和链路符号时钟,并将图像数据提供给rfb和rfb控制器230。rfb和rfb控制器230以帧为单位存储图像数据,并以帧为单位将图像数据提供给时序控制器220。时序控制器220控制将在显示面板240上显示的图像。

28.更具体地,如果待显示的图像是静态图像,则源设备100可将面板自刷新模式的活动信号或进入信号作为数据包传送至接收设备200。

29.接收设备200检测活动信号或进入信号,并控制存储在rfb 230中的图像数据显示在显示面板240上,直到从源设备100接收到面板自刷新模式的非活动信号。在这种情况下,接收设备200可生成与面板自刷新模式之前的流时钟具有相同频率的流时钟,并且可使用流时钟在显示面板240上显示存储在rfb 230中的图像数据。

30.此外,接收设备200可在面板自刷新模式下跟踪源设备100在面板自刷新模式下的状态信号,并且当从源设备100接收到面板自刷新模式的非活动信号时,可与由源设备100提供的时序同步地在显示面板240上显示图像数据。

31.图2是根据实施方式的流时钟生成器30的框图。

32.参照图2,流时钟生成器30可包括内部振荡器32、频率调节器34和锁相环路(pll)36。

33.内部振荡器32振荡内部时钟osc_clk。可基于控制信号osc_con<9:0>的值来调节内部时钟osc_clk的频率。

34.频率调节器34可接收内部时钟osc_clk和链路符号时钟ls_clk,可比较内部时钟osc_clk和链路符号时钟ls_clk的频率,以及可生成控制信号osc_con<9:0>。链路符号时钟ls_clk可限定为从由源设备100传送的流数据str_data重构的信号。

35.频率调节器34使用控制信号osc_con<9:0>来调节内部时钟osc_clk的频率。频率调节器34可比较内部时钟osc_clk和链路符号时钟ls_clk的频率,并且可基于比较的结果来增大或减小控制信号osc_con<9:0>的值。例如,当从内部时钟osc_clk分频的分频时钟d_ls_clk的频率大于内部时钟osc_clk的频率时,频率调节器34可增大控制信号osc_con<9:0>的值,以及当分频时钟d_ls_clk的频率小于内部时钟osc_clk的频率时,频率调节器34可减小控制信号osc_con<9:0>的值。

36.频率调节器34在正常模式下使用控制信号osc_con<9:0>来调节内部时钟osc_clk的频率,并且在面板自刷新模式下保持控制信号osc_con<9:0>的值。

37.pll 36可使用内部时钟osc_clk生成流时钟str_clk,并且可将流时钟str_clk的相位锁定到内部时钟osc_clk的相位。pll36锁定流时钟str_clk的相位,使得流时钟str_clk的相位不摇动,并且允许输出具有恒定频率的流时钟str_clk。

38.pll 36可包括:相位差检测器(pfd)(未示出),用于比较内部时钟osc_clk和反馈流时钟str_clk的相位并检测相位差;低通环路滤波器(未示出),用于确定pll的高频分量和同步特性或响应特性;以及电压控制器(vco)(未示出),用于基于相位差调节延迟电路(未示出)的延迟量,已经将流时钟str_clk的相位锁定到内部时钟osc_clk的相位。在本文

中省略了pll 36的详细描述。

39.此外,频率调节器34可包括分频器341、计数器342和控制逻辑电路343。

40.分频器341可通过对链路符号时钟ls_clk进行分频来提供分频时钟d_ls_clk。计数器342可比较分频时钟d_ls_clk和内部时钟osc_clk的频率,并且可基于比较的结果输出计数信号。控制逻辑电路343可响应于计数信号而增大或减小控制信号osc_con<9:0>的值。

41.例如,当从内部时钟osc_clk分频的分频时钟d_ls_clk的频率大于内部时钟osc_clk的频率时,控制逻辑电路343可增大控制信号osc_con<9:0>的值,以及当分频时钟d_ls_clk的频率小于内部时钟osc_clk的频率时,可减小控制信号osc_con<9:0>的值。

42.换言之,在嵌入式displayport系统中,接收设备200的接收器210从以链路符号时钟ls_clk的速度传送的流数据str_data重构链路符号时钟ls_clk和图像数据。在这种情况下,链路符号时钟ls_clk在高比特率(hbr)模式中限定为270mbps,而在降低比特率(rbr)模式中限定为162mbps。为了减小取决于工艺、电压和温度(pvt)的芯片之间的内部振荡器32的频率偏差,接收设备200可包括频率调节器34,用于比较使用接收器210的时钟数据恢复(crd)电路重构的链路符号时钟ls_clk和在正常模式(即,面板刷新模式的非活动状态)下由内部振荡器32生成的内部时钟osc_clk,并且通过调节内部时钟osc_clk的频率来生成恒定流时钟str_clk。

43.频率调节器34在面板自刷新模式的活动状态下具有关闭状态,并且可保持恒定的频率,因为它在面板自刷新模式的非活动状态下具有控制信号osc_con<9:0>的值。

44.当接收设备200从源设备100接收到面板自刷新模式的非活动信号时,频率调节器34再次操作并连续地调节内部振荡器32的内部时钟osc_clk的频率。内部时钟osc_clk的频率根据芯片的特性而彼此不同,但是频率调节器34比较内部时钟osc_clk和从接收设备200的接收器210重构的链路符号时钟ls_clk的频率,并生成新控制信号osc_con<9:0>的值。pll使用新控制信号osc_con<9:0>的值来生成流时钟str_clk。因此,尽管内部时钟osc_clk的频率在芯片之间彼此不同,但是可应用上述实施方式。

45.在参照图2描述的实施方式中,已经描述了时序控制器220包括流时钟生成器30,但是本公开不限于此。流时钟生成器30可包括在接收器210中,或者可与接收器210和时序控制器220分开形成。

46.图3是示出根据实施方式的根据内部振荡器32的控制信号的值的内部振荡器32的输出频率特性的曲线图。

47.参照图3,根据控制信号osc_con<9:0>的值的内部振荡器32的内部时钟osc_clk的频率特性示出了不同的线性特性。尽管在芯片之间振荡器的频率是不同的,但是内部振荡器32可通过改变控制信号osc_con<9:0>的值来输出具有期望频率的内部时钟osc_clk。

48.例如,下面描述在hbr模式下调节内部振荡器32的频率的操作。例如,频率为27mhz的内部时钟osc_clk可基于频率为30khz的分频时钟d_ls_clk进行计数,该分频时钟d_ls_clk是通过从频率为135mhz的链路符号时钟ls_clk除以4500而获得的。通过增大或减小控制信号osc_con<9:0>的值直到计数值落在给定范围内(899<计数值<901),可将内部时钟osc_clk的频率调节为与链路符号时钟ls_clk的频率相对应。每当生成计数信号“1”时,用计数结果来更新控制信号osc_con<9:0>。在这种情况下,计数信号之间的间隔可以是33.33μs,即,分频时钟d_ls_clk的一个周期。例如,当内部振荡器32的频率最初高于27mhz时,控

制信号osc_con<9:0>的值可减小到十六进制(200->1ff->1fd->

…-

>1f5)。当内部振荡器32的频率最初低于27mhz时,控制信号osc_con<9:0>的值可增大到十六进制(200->201->202->...>20c)。此外,其中控制信号osc_con<9:0>的值被增大或减小的比特间隔可设置为可选地调节。

49.图4是根据实施方式的用于描述当内部振荡器32进入面板自刷新模式时内部振荡器32的操作的时序图。

50.参照图4,psr模式=“0”指示正常模式(即,面板自刷新模式关闭),而psr模式=“1”指示进入自刷新模式。当psr模式信号为“0”时,频率调节器34基于计数信号继续更新控制信号osc_con<9:0>的值。当psr模式信号为“1”时,频率调节器34保持psr模式“0”中的控制信号osc_con<9:0>的值。因此,内部振荡器32输出与面板自刷新模式之前的正常模式中的频率相同的频率。

51.如上所述,根据实施方式,在面板自刷新模式下,可生成具有与正常模式中的频率相同的频率的流时钟str_clk。

52.此外,根据实施方式,比较内部时钟osc_clk和链路符号时钟ls_clk的频率,并且调节内部时钟osc_clk的频率。因此,尽管源设备100在面板自刷新模式下关闭,但是可生成和保持与在面板自刷新模式之前的正常模式中的流时钟相同的流时钟str_clk。

53.此外,根据实施方式,尽管由于芯片之间的振荡器特性、外部功率或操作期间的芯片温度导致输出频率彼此不同,但是可生成具有恒定频率的流时钟str_clk。

54.虽然上面已经描述了各种实施方式,但是本领域技术人员将理解,所描述的实施方式仅是示例性的。因此,不应基于所描述的实施方式来限制本文中所描述的公开内容。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1