源极驱动器与极性反转控制电路的制作方法

源极驱动器与极性反转控制电路

【技术领域】

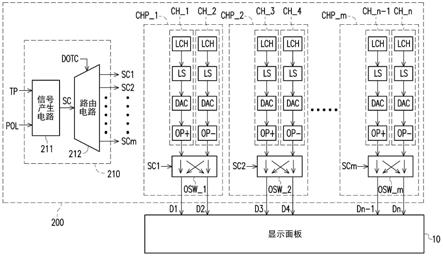

1.本发明是有关于一种电子电路,且特别是有关于一种源极驱动器与极性反转控制电路。

背景技术:

2.在显示设备中,源极驱动器可以依照时序控制器(timing controller)的控制去驱动显示面板,以显示影像。为了避免液晶(liquid crystal)分子的特性被破坏,时序控制器可以控制源极驱动器去进行极性反转。一般而言,源极驱动器包括多个通道对,用以驱动显示面板。这些通道对的每一个包括正极性通道、负极性通道与输出切换电路。正极性通道用以提供高于共同电压(common voltage)的正极性驱动电压。负极性通道用以提供低于共同电压的负极性驱动电压。

3.图1是已知的一种源极驱动器20的电路方框(circuit block)示意图。图1所示源极驱动器20可以依照时序控制器(未图示)的控制去驱动显示面板10以显示影像。源极驱动器20包括多个通道对p_1、p_2、

…

、p_m,其中m为整数。通道对p_1包括正极性通道ch_1、负极性通道ch_2、信号产生电路p1与输出切换电路osw1。输出切换电路osw1的第一输入端与第二输入端分别耦接至正极性通道ch_1的输出端与负极性通道ch_2的输出端。通道对p_2包括正极性通道ch_3、负极性通道ch_4、信号产生电路p2与输出切换电路osw2。输出切换电路osw2的第一输入端与第二输入端分别耦接至正极性通道ch_3的输出端与负极性通道ch_4的输出端。以此类推,通道对p_m包括正极性通道ch_n-1、负极性通道ch_n、信号产生电路pm与输出切换电路oswm。输出切换电路oswm的第一输入端与第二输入端分别耦接至正极性通道ch_n-1的输出端与负极性通道ch_n的输出端。

4.输出切换电路osw1~oswm的第一输出端与第二输出端耦接至显示面板10的数据线d1、d2、d3、d4、

…

、dn-1与dn,如图1所示。正极性通道(例如ch_1、ch_3与ch_n-1)的每一个具有闩锁器(latch)lch、电平转换器(level shifter)ls、数字模拟转换器(digital to analog converter)dac以及正极性放大器op+。正极性放大器op+用以提供正极性驱动电压。负极性通道(例如ch_2、ch_4与ch_n)的每一个具有闩锁器lch、电平转换器ls、数字模拟转换器dac以及负极性放大器op-。负极性放大器op-用以提供负极性驱动电压。

5.时序控制器(未图示)可以输出极性信号pol给源极驱动器20,以控制源极驱动器20的极性反转操作。举例来说,当极性信号pol为逻辑态“0”时,数据线d1~dn的极性配置为“+-+-+-+

-…”

,其中“+”表示正极性驱动电压,而

“-”

表示负极性驱动电压。当极性信号pol为逻辑态“1”时,数据线d1~dn的极性配置为

“-

+-+-+-+

…”

。然而依据显示面板10的特性、设计需求以及(或是)其他考虑因素,在其他应用情境中的数据线d1~dn的极性配置(极性关系)可能不同于在前述应用情境中的数据线d1~dn的极性配置(极性关系)。举例来说,在另一应用情境中,当极性信号pol为逻辑态“0”时,数据线d1~dn的极性配置需要被设定为“+

--

+-++

-…”

(或者,当极性信号pol为逻辑态“1”时,数据线d1~dn的极性配置为

“-

++-+

--

+

…”

)。

6.亦即,在不同应用情境中,数据线d1~dn的极性配置(极性关系)可能不同。因此,定制化的信号产生电路p1~pm被配置在已知的源极驱动器20的这些通道对p_1~p_m中。这些信号产生电路p1~pm可以依照极性信号pol来产生不同的切换控制信号s1、s2、

…

、sm给这些输出切换电路osw1~oswm。基此,这些输出切换电路osw1~oswm可以输出符合定制化的极性配置(极性关系)的驱动电压给显示面板10的数据线d1~dn。

7.一般而言,极性信号pol与信号产生电路p1~pm的逻辑电路是操作在低压范围,而切换控制信号s1~sm需要操作在高压范围。因此,在信号产生电路p1~pm的每一个里面需要配置一个电平转换器。当这些通道对p_1~p_m的数量m越大时,信号产生电路p1~pm的数量越多。大量的信号产生电路p1~pm(电平转换器)会占用源极驱动器20的有限芯片面积。

8.须注意的是,“背景技术”段落的内容是用来帮助了解本发明。在“背景技术”段落所公开的部分内容(或全部内容)可能不是所属技术领域中普通技术人员所知道的已知技术。在“背景技术”段落所公开的内容,不代表该内容在本发明申请前已被所属技术领域中普通技术人员所知悉。

技术实现要素:

9.本发明提供一种源极驱动器与极性反转控制电路,以尽可能地减小电路面积。

10.在本发明的一实施例中,上述的源极驱动器包括多个通道对以及一个极性反转控制电路。这些通道对适于驱动显示面板。这些通道对的每一个包括正极性通道、负极性通道与输出切换电路。输出切换电路的第一输入端与第二输入端分别耦接至正极性通道的输出端与负极性通道的输出端。输出切换电路的第一输出端与第二输出端耦接至显示面板。极性反转控制电路包括信号产生电路以及路由电路。信号产生电路被配置为产生极性控制信号。路由电路耦接至信号产生电路,以接收极性控制信号。路由电路被配置为输出对应于极性控制信号的多个切换控制信号给这些输出切换电路。路由电路依据极性反转配置信号来改变极性控制信号与这些切换控制信号之间的对应关系。

11.在本发明的一实施例中,上述的极性反转控制电路包括信号产生电路以及路由电路。信号产生电路被配置为产生极性控制信号。路由电路耦接至信号产生电路,以接收极性控制信号。路由电路被配置为输出对应于极性控制信号的多个切换控制信号给源极驱动器的多个通道对的多个输出切换电路。路由电路依据极性反转配置信号来改变极性控制信号与这些切换控制信号之间的对应关系。

12.基于上述,本发明诸实施例所述多个通道对可以共享同一个信号产生电路。因此,源极驱动器的电路面积可以尽可能地减小。

13.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

【附图说明】

14.图1是已知的一种源极驱动器的电路方框(circuit block)示意图。

15.图2是依照本发明的一实施例的一种源极驱动器的电路方框示意图。

16.图3是依照本发明的一实施例说明图2所示信号产生电路的电路方框示意图。

17.图4是依照本发明的一实施例说明图2所示输出切换电路的电路方框示意图。

18.图5是依照本发明的一实施例说明图2所示路由电路的电路方框示意图。

19.图6是依照本发明的另一实施例说明图2所示路由电路的电路方框示意图。

20.图7是依照本发明的又一实施例说明图2所示路由电路的电路方框示意图。

21.【符号说明】

22.10:显示面板

23.20、200:源极驱动器

24.210:极性反转控制电路

25.211:信号产生电路

26.212:路由电路

27.310:逻辑电路

28.320、330:电平转换器

29.410、420、430、440:缓冲器

30.450、460、470、480:开关

31.610、710:解码电路

32.ch_1、ch_3、ch_n-1:正极性通道

33.ch_2、ch_4、ch_n:负极性通道

34.chp_1、chp_2、chp_m、p_1、p_2、p_m:通道对

35.ca1、ca2、cb1、cb2、cc1、cc2、cd1、cd2、ct1、ct2、ct3:控制信号

36.d1、d2、d3、d4、dn-1、dn:数据线

37.dac:数字模拟转换器

38.dotc:极性反转配置信号

39.dotc2、dotc1:位

40.lch:闩锁器

41.ls:电平转换器

42.op+:正极性放大器

43.op-:负极性放大器

44.osw_1、osw_2、osw_m、osw1、osw2、oswm:输出切换电路

45.p1、p2、pm:信号产生电路

46.pol:极性信号

47.s1、s2、sm、sc1、sc2、scm:切换控制信号

48.sc:极性控制信号

49.sn、sp:逻辑信号

50.swn、swnb、swp、swpb:原切换信号

51.swn1、swn1b、swp1、swp1b:切换信号

52.tp:线闩锁信号

【具体实施方式】

53.在本技术说明书全文(包括权利要求书)中所使用的“耦接(或连接)”一词可指任何直接或间接的连接手段。举例而言,若文中描述第一装置耦接(或连接)于第二装置,则应

该被解释成该第一装置可以直接连接于该第二装置,或者该第一装置可以通过其他装置或某种连接手段而间接地连接至该第二装置。本技术说明书全文(包括权利要求书)中提及的“第一”、“第二”等用语是用以命名元件(element)的名称,或区别不同实施例或范围,而并非用来限制元件数量的上限或下限,亦非用来限制元件的次序。另外,凡可能之处,在附图及具体实施方式中使用相同标号的元件/构件/步骤代表相同或类似部分。不同实施例中使用相同标号或使用相同用语的元件/构件/步骤可以相互参照相关说明。

54.图2是依照本发明的一实施例的一种源极驱动器200的电路方框(circuit block)示意图。图2所示源极驱动器200可以依照时序控制器(未图示)的控制去驱动显示面板10以显示影像。源极驱动器200包括多个通道对chp_1、chp_2、

…

、chp_m,其中m为整数。通道对chp_1包括正极性通道ch_1、负极性通道ch_2与输出切换电路osw_1。输出切换电路osw_1的第一输入端与第二输入端分别耦接至正极性通道ch_1的输出端与负极性通道ch_2的输出端。通道对chp_2包括正极性通道ch_3、负极性通道ch_4与输出切换电路osw_2。输出切换电路osw_2的第一输入端与第二输入端分别耦接至正极性通道ch_3的输出端与负极性通道ch_4的输出端。以此类推,通道对chp_m包括正极性通道ch_n-1、负极性通道ch_n与输出切换电路osw_m,其中n为整数。输出切换电路osw_m的第一输入端与第二输入端分别耦接至正极性通道ch_n-1的输出端与负极性通道ch_n的输出端。图2所示极性通道ch_1~ch_n可以参照图1所示极性通道ch_1~ch_n的相关说明,故不再赘述。

55.输出切换电路osw_1~osw_m的第一输出端与第二输出端耦接至显示面板10的数据线d1、d2、d3、d4、..、dn-1与dn,如图2所示。极性反转控制电路210可以接收时序控制器(未图示)所提供的线闩锁(line latch)信号tp与极性信号pol。所示线闩锁信号tp可以是为一条线的起始脉冲(start pulse)。依据线闩锁信号tp与极性信号pol,极性反转控制电路210可以输出多个切换控制信号sc1、sc2、

…

、scm给这些输出切换电路osw_1~osw_m。

56.依据显示面板10的特性、设计需求以及(或是)其他考虑因素,在不同应用情境中,数据线d1~dn的极性配置(极性关系)可能不同。比如说,在某一个应用情境中,当极性信号pol为逻辑态“0”时,数据线d1~dn的极性配置需要被设定为“+-+-+-+

-…”

,其中“+”表示正极性驱动电压,而

“-”

表示负极性驱动电压。在另一个应用情境中,当极性信号pol一样是逻辑态“0”时,数据线d1~dn的极性配置却需要被设定为“+

--

+-++

-…”

。

57.极性反转控制电路210可以依照线闩锁信号tp与极性信号pol来产生不同的切换控制信号sc1~scm给这些输出切换电路osw_1~osw_m。极性反转控制电路210可以依据极性反转配置信号dotc来改变这些切换控制信号sc1~scm的逻辑配置,进而控制/改变数据线d1~dn的极性配置(极性关系)。比如说,在极性反转配置信号dotc为逻辑态“0”的情况下(在某一个应用情境中),当极性信号pol为逻辑态“0”时,极性反转控制电路210可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+-+-+-+

-…”

。在极性反转配置信号dotc为逻辑态“1”的情况下(在另一个应用情境中),当极性信号pol一样是逻辑态“0”时,极性反转控制电路210可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-++

-…”

。

58.通道对chp_1~chp_m可以共享同一个极性反转控制电路210,而极性反转控制电路210可以依照不同应用情境去改变这些切换控制信号sc1~scm的逻辑配置。基于这些切换控制信号sc1~scm的控制,这些输出切换电路osw_1~osw_m可以输出符合定制化的极性

配置(极性关系)的驱动电压给显示面板10的数据线d1~dn。

59.在图2所示实施例中,极性反转控制电路210包括信号产生电路211以及路由电路212。信号产生电路211可以接收时序控制器(未图示)所提供的线闩锁信号tp与极性信号pol。依据线闩锁信号tp与极性信号pol,信号产生电路211可以产生极性控制信号sc给路由电路212。信号产生电路211可以依照设计需求来实现。举例来说,在一些实施例中,当线闩锁信号tp为逻辑态“1”时,不论极性信号pol的逻辑态为何,极性控制信号sc为逻辑态“1”。当线闩锁信号tp与极性信号pol为逻辑态“0”时,极性控制信号sc为逻辑态“0”。当线闩锁信号tp为逻辑态“0”且极性信号pol为逻辑态“1”时,极性控制信号sc为逻辑态“1”。

60.路由电路212受控于极性反转配置信号dotc。路由电路212耦接至信号产生电路211,以接收极性控制信号sc。路由电路212可以输出对应于极性控制信号sc的多个切换控制信号sc1~scm给这些通道对chp_1~chp_m的输出切换电路osw_1~osw_m。路由电路212可以依据极性反转配置信号dotc来改变极性控制信号sc与这些切换控制信号sc1~scm之间的对应关系。

61.举例来说,在极性反转配置信号dotc为逻辑态“00”的情况下(在某一个应用情境中),当极性控制信号sc为逻辑态“0”时,路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+-+-+-+

-…”

。在极性反转配置信号dotc为逻辑态“01”的情况下(在另一个应用情境中),当极性控制信号sc一样是逻辑态“0”时,路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-++

-…”

。在极性反转配置信号dotc为逻辑态“10”的情况下(在又一个应用情境中),当极性控制信号sc一样是逻辑态“0”时,路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-+-+

…”

。

62.图3是依照本发明的一实施例说明图2所示信号产生电路211的电路方框示意图。在图3所示实施例中,极性控制信号sc包括原切换信号swp、swpb、swn与swnb。其中,原切换信号swpb为原切换信号swp的反相信号,而原切换信号swnb为原切换信号swn的反相信号。无论如何,在其他实施例中的极性控制信号sc不应受限于图3所示极性控制信号sc。

63.图3所示信号产生电路211包括逻辑电路310、电平转换器320以及电平转换器330。逻辑电路310可以依据线闩锁信号tp与极性信号pol来产生逻辑信号sp与逻辑信号sn。逻辑电路310可以依照设计需求来实现。举例来说,在一些实施例中,当线闩锁信号tp为逻辑态“1”时,不论极性信号pol的逻辑态为何,逻辑信号sp为逻辑态“1”(例如高电压电平)而逻辑信号sn为逻辑态“0”(例如低电压电平)。当线闩锁信号tp与极性信号pol均为逻辑态“0”时,逻辑信号sp与逻辑信号sn均为逻辑态“0”。当线闩锁信号tp为逻辑态“0”且极性信号pol为逻辑态“1”时,逻辑信号sp与逻辑信号sn均为逻辑态“1”。

64.电平转换器320耦接至逻辑电路310,以接收逻辑信号sp。电平转换器320可以产生原切换信号swp与原切换信号swpb。电平转换器330耦接至逻辑电路310,以接收逻辑信号sn。电平转换器330可以产生原切换信号swn与原切换信号swnb。

65.图4是依照本发明的一实施例说明图2所示输出切换电路osw_1的电路方框示意图。图2所示其他输出切换电路osw_2~osw_m与切换控制信号sc2~scm可以参照图4所示输出切换电路osw_1与切换控制信号sc1的相关说明来类推,故不予赘述。在图4所示实施例中,切换控制信号sc1包括切换信号swp1、切换信号swp1b、切换信号swn1与切换信号swn1b。

切换信号swp1b为切换信号swp1的反相信号。切换信号swn1b为切换信号swn1的反相信号。

66.请参照图2与图4。图4所示通道对chp_1的输出切换电路osw_1包括缓冲器410、缓冲器420、缓冲器430、缓冲器440、开关450、开关460、开关470与开关480。缓冲器410的输入端耦接至路由电路212,以接收切换信号swp1。缓冲器420的输入端耦接至路由电路212,以接收切换信号swp1b。缓冲器430的输入端耦接至路由电路212,以接收切换信号swn1。缓冲器440的输入端耦接至路由电路212,以接收切换信号swn1b。

67.在图4所示实施例中,开关450与开关480可以是p沟道金属氧化物半导体(p-channel metal oxide semiconductor,pmos)晶体管,而开关460与开关470可以是n沟道金属氧化物半导体(n-channel metal oxide semiconductor,nmos)晶体管。然而在其他实施例中,开关450、开关460、开关470与开关480的实施方式不应受限于图4。

68.开关450的控制端耦接至缓冲器410的输出端。开关450的第一端耦接至输出切换电路osw_1的第一输入端,亦即耦接至正极性通道ch_1的正极性放大器op+。开关450的第二端耦接至输出切换电路osw_1的第一输出端,亦即耦接至显示面板10。开关460的控制端耦接至缓冲器420的输出端。开关460的第一端耦接至输出切换电路osw_1的第二输入端,亦即耦接至负极性通道ch_2的负极性放大器op-。开关460的第二端耦接至输出切换电路osw_1的该第二输出端,亦即耦接至显示面板10。开关470的控制端耦接至缓冲器430的输出端。开关470的第一端耦接至输出切换电路osw_1的第二输入端。开关470的第二端耦接至输出切换电路osw_1的第一输出端。开关480的控制端耦接至缓冲器440的输出端。开关480的第一端耦接至输出切换电路osw_1的第一输入端。开关480的第二端耦接至输出切换电路osw_1的第二输出端。

69.图5是依照本发明的一实施例说明图2所示路由电路212的电路方框示意图。图5所示路由电路212包括多个开关,其中这些开关都受控于极性反转配置信号dotc。请参照图2、图3、图4与图5,极性控制信号sc包括原切换信号swp、swpb、swn与swnb。切换控制信号sc1包括切换信号swp1、切换信号swp1b、切换信号swn1与切换信号swn1b。

70.路由电路212可以选择将原切换信号swp作为切换信号swp1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swpb作为切换信号swp1b而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swn作为切换信号swn1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swnb作为切换信号swn1b而输出给输出切换电路osw_1。

71.由切换控制信号sc1的相关说明来类推,切换控制信号sc2可以包括切换信号swp2、切换信号swp2b、切换信号swn2与切换信号swn2b。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swp与原切换信号swnb其中一个作为切换信号swp2而输出给输出切换电路osw_2。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swpb与原切换信号swn其中一个作为切换信号swp2b而输出给输出切换电路osw_2。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swn与原切换信号swpb其中一个作为切换信号swn2而输出给输出切换电路osw_2。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swnb与原切换信号swp其中一个作为切换信号swn2b而输出给输出切换电路osw_2。

72.举例来说,当极性反转配置信号dotc为第一逻辑态时,路由电路212可以选择将原

切换swp信号作为切换信号swp2,路由电路212可以选择原切换信号swpb作为切换信号swp2b,路由电路212可以选择原切换信号swn作为切换信号swn2,以及路由电路212可以选择原切换信号swnb作为切换信号swn2b。当极性反转配置信号dotc为第二逻辑态(不同于所述第一逻辑态)时,路由电路212可以选择原切换信号swnb作为切换信号swp2,路由电路212可以选择原切换信号swn作为切换信号swp2b,路由电路212可以选择原切换信号swpb作为切换信号swn2,以及路由电路212可以选择原切换信号swp作为切换信号swn2b。

73.由切换控制信号sc1的相关说明来类推,切换控制信号sc3(未图示)可以包括切换信号swp3、切换信号swp3b、切换信号swn3与切换信号swn3b。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swp与原切换信号swnb其中一个作为切换信号swp3。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swpb与原切换信号swn其中一个作为切换信号swp3b。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swn与原切换信号swpb其中一个作为切换信号swn3。路由电路212可以依据极性反转配置信号dotc而选择将原切换信号swnb与原切换信号swp其中一个作为切换信号swn3b。

74.由切换控制信号sc1的相关说明来类推,切换控制信号sc4(未图示)可以包括切换信号swp4、切换信号swp4b、切换信号swn4与切换信号swn4b。路由电路212可以选择将原切换信号swp作为切换信号swp4。路由电路212可以选择将原切换信号swpb作为切换信号swp4b。路由电路212可以选择将原切换信号swn作为切换信号swn4。路由电路212可以选择将原切换信号swnb作为切换信号swnb。

75.因此在极性反转配置信号dotc为第一逻辑态(例如逻辑态“0”)的情况下(在某一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+-+-+-+

-…”

或

“-

+-+-+-+

…”

(由原切换信号swp与swn决定)。在极性反转配置信号dotc为第二逻辑态(例如逻辑态“1”)的情况下(在另一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-++

-…”

或

“-

++-+

--

+

…”

(由原切换信号swp与swn决定)。

76.图6是依照本发明的另一实施例说明图2所示路由电路212的电路方框示意图。图6所示路由电路212包括解码电路610与多个开关,其中这些开关都受控于解码电路610的解码结果(控制信号ct1、ct2与ct3)。解码电路610可以对极性反转配置信号dotc进行解码,以产生解码结果。举例来说,极性反转配置信号dotc和解码结果之间的关系可以是下面表1所示的情况。

77.表1:解码电路610的输入和输出之间的关系

[0078][0079]

在表1中,极性反转配置信号dotc的位dotc2与dotc1均为逻辑态“0”,而控制信号ct1、ct2与ct3(解码结果)为逻辑态“1”、“0”与“0”。在极性反转配置信号dotc的位dotc2与

dotc1为逻辑态“0”与“1”的情况下,控制信号ct1、ct2与ct3为逻辑态“0”、“1”与“0”。在极性反转配置信号dotc的位dotc2与dotc1为逻辑态“1”与“0”(或均为“1”)的情况下,控制信号ct1、ct2与ct3为逻辑态“0”、“0”与“1”。

[0080]

请参照图2、图3、图4与图6,极性控制信号sc包括原切换信号swp、swpb、swn与swnb。切换控制信号sc1包括切换信号swp1、切换信号swp1b、切换信号swn1与切换信号swn1b。路由电路212可以选择将原切换信号swp作为切换信号swp1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swpb作为切换信号swp1b而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swn作为切换信号swn1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swnb作为切换信号swn1b而输出给输出切换电路osw_1。

[0081]

由切换控制信号sc1的相关说明来类推,切换控制信号sc2可以包括切换信号swp2、切换信号swp2b、切换信号swn2与切换信号swn2b。路由电路212可以依据解码结果(控制信号ct1、ct2与ct3)而选择将原切换信号swp与原切换信号swnb其中一个作为切换信号swp2而输出给输出切换电路osw_2。路由电路212可以依据解码结果而选择原切换信号swpb与原切换信号swn其中一个作为切换信号swp2b而输出给输出切换电路osw_2。路由电路212可以依据解码结果而选择原切换信号swn与原切换信号swpb其中一个作为切换信号swn2而输出给输出切换电路osw_2。路由电路212可以依据解码结果而选择原切换信号swnb与切换信号swp其中一个作为切换信号swn2b而输出给输出切换电路osw_2。

[0082]

举例来说,当解码结果为第一逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“1”、“0”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp2,路由电路212可以选择原切换信号swpb作为切换信号swp2b,路由电路212可以选择原切换信号swn作为切换信号swn2,以及路由电路212可以选择原切换信号swnb作为切换信号swn2b。当解码结果为第二逻辑态或第三逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“0”、“1”与“0”,或是控制信号ct1、ct2与ct3为逻辑态“0”、“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp2,路由电路212可以选择原切换信号swn作为切换信号swp2b,路由电路212可以选择原切换信号swpb作为切换信号swn2,以及路由电路212可以选择原切换信号swp作为切换信号swn2b。

[0083]

由切换控制信号sc1的相关说明来类推,切换控制信号sc3(未图示)可以包括切换信号swp3、切换信号swp3b、切换信号swn3与切换信号swn3b。当解码结果为第一逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“1”、“0”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp3,路由电路212可以选择原切换信号swpb作为切换信号swp3b,路由电路212可以选择原切换信号swn作为切换信号swn3,以及路由电路212可以选择原切换信号swnb作为切换信号swn3b。当解码结果为第二逻辑态或第三逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“0”、“1”与“0”,或是控制信号ct1、ct2与ct3为逻辑态“0”、“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp3,路由电路212可以选择原切换信号swn作为切换信号swp3b,路由电路212可以选择原切换信号swpb作为切换信号swn3,以及路由电路212可以选择原切换信号swp作为切换信号swn3b。

[0084]

由切换控制信号sc1的相关说明来类推,切换控制信号sc4(未图示)可以包括切换信号swp4、切换信号swp4b、切换信号swn4与切换信号swn4b。当解码结果为第一逻辑态或第

二逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“1”、“0”与“0”,或是控制信号ct1、ct2与ct3为逻辑态“0”、“1”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp4,路由电路212可以选择原切换信号swpb作为切换信号swp4b,路由电路212可以选择原切换信号swn作为切换信号swn4,以及路由电路212可以选择原切换信号swnb作为切换信号swn4b。当解码结果为第三逻辑态时(例如控制信号ct1、ct2与ct3为逻辑态“0”、“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp4,路由电路212可以选择原切换信号swn作为切换信号swp4b,路由电路212可以选择原切换信号swpb作为切换信号swn4,以及路由电路212可以选择原切换信号swp作为切换信号swn4b。

[0085]

因此,极性反转配置信号dotc和数据线d1~dn的极性配置之间的关系可以是下面表2所示的情况。在表2中,在极性反转配置信号dotc为第一逻辑态(例如逻辑态“00”)的情况下(在某一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+-+-+-+

-…”

或

“-

+-+-+-+

…”

(由原切换信号swp与swn决定)。在极性反转配置信号dotc为第二逻辑态(例如逻辑态“01”)的情况下(在另一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-++

-…”

或

“-

++-+

--

+

…”

(由原切换信号swp与swn决定)。在极性反转配置信号dotc为第三逻辑态(例如逻辑态“10”或“11”)的情况下(在又一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-+-+

…”

或

“-

++-+-+

-…”

(由原切换信号swp与swn决定)。

[0086]

表2:极性反转配置信号dotc与数据线d1~dn的极性配置之间的关系

[0087]

dotcd1d2d3d4d5d6d7d800+-+-+-+-01+

--

+-++-10或11+

--

+-+-+

[0088]

图7是依照本发明的又一实施例说明图2所示路由电路212的电路方框示意图。图7所示路由电路212包括解码电路710与多个开关,其中这些开关都受控于解码电路710的解码结果(控制信号ca1、ca2、cb1、cb2、cc1、cc2、cd1与cd2)。解码电路710可以对极性反转配置信号dotc进行解码,以产生解码结果。举例来说,极性反转配置信号dotc和解码结果之间的关系可以是下面表3所示的情况。

[0089]

表3:解码电路710的输入和输出之间的关系

[0090][0091]

在表3中,在极性反转配置信号dotc的位dotc2与dotc1均为逻辑态“0”的情况下,控制信号ca1、ca2、cb1、cb2、cc1、cc2、cd1与cd2(解码结果)为逻辑态“1”、“0”、“1”、“0”、“1”、“0”、“1”与“0”。在极性反转配置信号dotc的位dotc2与dotc1为逻辑态“0”、“1”的情况

下,控制信号ca1、ca2、cb1、cb2、cc1、cc2、cd1与cd2为逻辑态“1”、“0”、“0”、“1”、“0”、“1”、“1”与“0”。在极性反转配置信号dotc的位dotc2与dotc1为逻辑态“1”与“0”(或均为“1”)的情况下,控制信号ca1、ca2、cb1、cb2、cc1、cc2、cd1与cd2为逻辑态“1”、“0”、“0”、“1”、“0”、“1”、“0”与“1”。

[0092]

请参照图2、图3、图4与图7,极性控制信号sc包括原切换信号swp、swpb、swn与swnb。切换控制信号sc1包括切换信号swp1、切换信号swp1b、切换信号swn1与切换信号swn1b。路由电路212可以选择将原切换信号swp作为切换信号swp1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swpb作为切换信号swp1b而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swn作为切换信号swn1而输出给输出切换电路osw_1。路由电路212可以选择将原切换信号swnb作为切换信号swn1b而输出给输出切换电路osw_1。

[0093]

由切换控制信号sc1的相关说明来类推,切换控制信号sc2可以包括切换信号swp2、切换信号swp2b、切换信号swn2与切换信号swn2b。路由电路212可以依据解码结果(控制信号cb1与cb2)而选择将原切换信号swp与原切换信号swnb其中一个作为切换信号swp2而输出给输出切换电路osw_2。路由电路212可以依据解码结果(控制信号cb1与cb2)而选择原切换信号swpb与原切换信号swn其中一个作为切换信号swp2b而输出给输出切换电路osw_2。路由电路212可以依据解码结果(控制信号cb1与cb2)而选择原切换信号swn与原切换信号swpb其中一个作为切换信号swn2而输出给输出切换电路osw_2。路由电路212可以依据解码结果(控制信号cb1与cb2)而选择原切换信号swnb与切换信号swp其中一个作为切换信号swn2b而输出给输出切换电路osw_2。

[0094]

举例来说,当解码结果为第一逻辑态时(例如控制信号cb1与cb2为逻辑态“1”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp2,路由电路212可以选择原切换信号swpb作为切换信号swp2b,路由电路212可以选择原切换信号swn作为切换信号swn2,以及路由电路212可以选择原切换信号swnb作为切换信号swn2b。当解码结果为第二逻辑态或第三逻辑态时(例如控制信号cb1与cb2为逻辑态“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp2,路由电路212可以选择原切换信号swn作为切换信号swp2b,路由电路212可以选择原切换信号swpb作为切换信号swn2,以及路由电路212可以选择原切换信号swp作为切换信号swn2b。

[0095]

由切换控制信号sc1的相关说明来类推,切换控制信号sc3(未图示)可以包括切换信号swp3、切换信号swp3b、切换信号swn3与切换信号swn3b。当解码结果为第一逻辑态时(例如控制信号控制信号cc1与cc2为逻辑态“1”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp3,路由电路212可以选择原切换信号swpb作为切换信号swp3b,路由电路212可以选择原切换信号swn作为切换信号swn3,以及路由电路212可以选择原切换信号swnb作为切换信号swn3b。当解码结果为第二逻辑态或第三逻辑态时(例如控制信号cc1与cc2为逻辑态“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp3,路由电路212可以选择原切换信号swn作为切换信号swp3b,路由电路212可以选择原切换信号swpb作为切换信号swn3,以及路由电路212可以选择原切换信号swp作为切换信号swn3b。

[0096]

由切换控制信号sc1的相关说明来类推,切换控制信号sc4(未图示)可以包括切换信号swp4、切换信号swp4b、切换信号swn4与切换信号swn4b。当解码结果为第一逻辑态或第

二逻辑态时(例如控制信号cd1与cd2为逻辑态“1”与“0”),路由电路212可以选择原切换信号swp作为切换信号swp4,路由电路212可以选择原切换信号swpb作为切换信号swp4b,路由电路212可以选择原切换信号swn作为切换信号swn4,以及路由电路212可以选择原切换信号swnb作为切换信号swn4b。当解码结果为第三逻辑态时(例如控制信号cd1与cd2为逻辑态“0”与“1”),路由电路212可以选择原切换信号swnb作为切换信号swp4,路由电路212可以选择原切换信号swn作为切换信号swp4b,路由电路212可以选择原切换信号swpb作为切换信号swn4,以及路由电路212可以选择原切换信号swp作为切换信号swn4b。

[0097]

因此在极性反转配置信号dotc为第一逻辑态(例如逻辑态“00”)的情况下(在某一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+-+-+-+

-…”

或

“-

+-+-+-+

…”

(由原切换信号swp与swn决定)。在极性反转配置信号dotc为第二逻辑态(例如逻辑态“01”)的情况下(在另一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-++

-…”

或

“-

++-+

--

+

…”

(由原切换信号swp与swn决定)。在极性反转配置信号dotc为第三逻辑态(例如逻辑态“10”或“11”)的情况下(在又一个应用情境中),路由电路212可以改变这些切换控制信号sc1~scm的逻辑配置以将数据线d1~dn的极性配置设定为“+

--

+-+-+

…”

或

“-

++-+-+

-…”

(由原切换信号swp与swn决定)。

[0098]

依照不同的设计需求,上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212的方框的实现方式可以是硬件(hardware)、固件(firmware)、软件(software,即程序)或是前述三者中的多者的组合形式。

[0099]

以硬件形式而言,上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212的方框可以实现于集成电路(integrated circuit)上的逻辑电路。上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212的相关功能可以利用硬件描述语言(hardware description languages,例如verilog hdl或vhdl)或其他合适的编程语言来实现为硬件。举例来说,上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212的相关功能可以被实现于一或多个控制器、微控制器、微处理器、专用集成电路(application-specific integrated circuit,asic)、数字信号处理器(digital signal processor,dsp)、场可程序逻辑门阵列(field programmable gate array,fpga)及/或其他处理单元中的各种逻辑区块、模块和电路。

[0100]

以软件形式及/或固件形式而言,上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212的相关功能可以被实现为编程码(programming codes)。例如,利用一般的编程语言(programming languages,例如c、c++或汇编语言)或其他合适的编程语言来实现上述极性反转控制电路210、信号产生电路211以及(或是)路由电路212。所述编程码可以被记录/存放在记录介质中,所述记录介质中例如包括只读存储器(read only memory,rom)、存储装置及/或随机存取内存(random access memory,ram)。计算机、中央处理器(central processing unit,cpu)、控制器、微控制器或微处理器可以从所述记录介质中读取并执行所述编程码,从而达成相关功能。作为所述记录介质,可使用“非临时的计算机可读取介质(non-transitory computer readable medium)”,例如可使用带(tape)、碟(disk)、卡(card)、半导体内存、可程序设计的逻辑电路等。而且,所述程序也可经由任意传输介质(通信网路或广播电波等)而提供给所述计算机(或cpu)。所述通信网路例如是互联

网(internet)、有线通信(wired communication)、无线通信(wireless communication)或其它通信介质。

[0101]

综上所述,上述诸实施例所述信号产生电路211被配置为产生极性控制信号sc(例如原切换信号swp、swpb、swn与swnb)。路由电路212耦接至信号产生电路211,以接收极性控制信号sc。路由电路212被配置为输出对应于极性控制信号sc的多个切换控制信号sc1~scm给源极驱动器200的多个通道对chp_1~chp_m的多个输出切换电路osw_1~osw_m。路由电路212可以依据极性反转配置信号dotc来改变极性控制信号sc与这些切换控制信号sc1~scm之间的对应关系。因此,极性反转控制电路210可以适应不同的应用情境改变这些切换控制信号sc1~scm的逻辑配置,以将数据线d1~dn的极性配置设定为符合客户要求的极性配置。

[0102]

虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视后附的权利要求书所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1