一种显示模组、电子设备的制作方法

一种显示模组、电子设备

1.本技术要求于2020年07月30日提交国家知识产权局、申请号为202010753480.4、申请名称为“一种屏幕组件、屏幕模组和电子设备”的中国专利申请的优先权,其全部内容通过引用结合在本技术中。

技术领域

2.本技术涉及显示技术领域,尤其涉及一种显示模组、电子设备。

背景技术:

3.目前,能够实现自发光的显示模组,例如采用有源矩阵有机发光二极管(active matrix organic light emitting diode,amoled)技术的显示模组,其子像素(sub pixel)中设置有机发光二极管(organic light emitting diode,oled)。通过控制不同oled的发光亮度,即可以实现灰阶显示。因此无需设置用于提供背光源的背光模组(back light unit,blu),从而能够减小显示模组的厚度。

4.如图1所示,amoled显示模组中设置有薄膜晶体管(thin film transistor,tft)背板10,以及用于承载控制芯片11的印刷电路板(printed circuit board,pcb)。tft背板10中设置有主要由tft构成的驱动电路,该驱动电路用于驱动位于tft背板上方的oled器件发光。然而,由于上述tft背板10和pcb的存在,会使得自发光的显示模组很难进一步降低厚度和重量,不利于显示模组的轻薄化设计。

技术实现要素:

5.本技术提供一种显示模组、电子设备,用于改善自发光的显示模组厚度和重量较大的问题。

6.为达到上述目的,本技术采用如下技术方案:

7.在本技术的一方面,提供一种显示模组。该显示模组包括电路板、集成芯片以及像素芯片组。集成芯片与电路板电连接。集成芯片包括第一芯片本体以及集成于第一芯片本体中的多个显示像素驱动电路。像素芯片组包括多个发光芯片。此外,至少一个像素芯片组设置于一个集成芯片远离电路板的一侧表面。设置于集成芯片上的一个发光芯片与集成芯片中的一个显示像素驱动电路电连接,显示像素驱动电路用于驱动发光芯片发光。这样一来,由于用于驱动发光芯片发光的显示像素驱动电路可以集成于上述集成芯片中的第一芯片本体中,因此本技术实施例提供的显示模组相对于目前的amoled显示模组而言,无需制作tft背板,能够有效减小显示模组的重量,减薄显示模组的厚度。

8.可选的,显示模组还包括电路衬底。电路衬底与电路板电连接,电路衬底集成有多个显示像素驱动电路。电路衬底在电路板上的垂直投影的面积,小于集成芯片在电路板上的垂直投影的面积。显示模组还包括两个或者两个以上的上述像素芯片组。一个像素芯片组设置于一个电路衬底远离电路板的一侧表面。设置于电路衬底上的一个发光芯片与电路衬底中的一个显示像素电路电连接。同理,将用于驱动发光芯片发光的显示像素驱动电路

集成于电路衬底中,能够有效减小显示模组的重量,减薄显示模组的厚度。

9.可选的,电路板包括主视区和位于主视区周边的周边区。集成芯片设置于主视区,电路衬底设置于周边区。周边区位于电路板的边缘位置。集成芯片的尺寸较大,与电路板的接触面积较大,而电路衬底的尺寸较小,与电路板的接触面积较小。在此情况下,显示模组在运输或使用的过程中,上述周边区容易在外力作用下,例如受到碰撞的过程中发生轻微的变形。因此,可以将尺寸较小的电路衬底设置于周边区,将尺寸较大的集成芯片设置于不容易发生变形的主视区,从而当显示模组在外力作用下,使得周边区发生碰撞时,不容易使得电路衬底发生断裂,有利于提高产品的可靠性。

10.可选的,显示模组还包括转轴,转轴设置于电路板远离集成芯片的一侧。电路板为柔性电路板。电路板包括第一主视区、第二主视区、第一周边区、第二周边区以及弯折区。其中,弯折区位于第一主视区和第二主视区之间,且转轴在电路板的垂直投影位于弯折区内。第一周边区设置于第一主视区的周边,第二周边区设置于第二主视区的周边。集成芯片设置于第一主视区和第二主视区;多个电路衬底设置于弯折区、第一周边区以及第二周边。由上述可知,集成芯片的尺寸较大,与电路板的接触面积较大,而电路衬底的尺寸较小,与电路板的接触面积较小。电路板的第一周边区和第二周边区位于电路板的边缘位置。在此情况下,显示模组在运输或使用的过程中,上述第一周边区和第二周边区容易在外力作用下,例如受到碰撞的过程中发生轻微的变形。因此,可以将尺寸较小的电路衬底设置于第一周边区和第二周边区,将尺寸较大的集成芯片设置于不容易发生变形的主视区,从而当显示模组在外力作用下,使得第一周边区和第二周边区发生碰撞时,不容易使得电路衬底发生断裂,有利于提高产品的可靠性。

11.可选的,电路板包括多条金属走线,多条金属走线设置于弯折区。金属走线呈弯曲状,且金属走线的两端分别与两个电路衬底相连接。这样一来,由于金属走线具有一定的拉伸性能,能够随着弯折区的弯折而发生变形,减小由于弯折区形变而在电路衬底所在位置产生的应力,达到进一步减小电路衬底发生断裂的目的。

12.可选的,弯折区的多个电路衬底呈矩阵形式排列。多条金属走线包括多条第一金属走线和多条第二金属走线。第一金属走线沿第一方向与相邻的两个电路衬底相连接,第二金属走线沿第二方向与相邻的两个电路衬底相连接。其中,第一方向与第二方向垂直。这样一来,上述多条第一金属走线和多条第二金属走线可以构成网状结构将弯折区中的多个电路衬底相连接,从而能够增加弯折区的韧性,进一步减小电路衬底发生断裂。

13.可选的,同一像素芯片组中的多个发光芯片包括第一发光芯片、第二发光芯片以及第三发光芯片。第一发光芯片、第二发光芯片以及第三发光芯片分别用于发出三原色光。这样一来,同一个像素芯片组中的第一发光芯片、第二发光芯片以及第三发光芯片可以构成一个像素。通过调节同一个像素芯片组中的第一发光芯片、第二发光芯片以及第三发光芯片各自的发光亮度,可以达到控制显示模组进行彩色显示时,显示图像的像素灰阶的目的。

14.可选的,集成芯片还包括集成于第一芯片本体中的多个指纹像素采集电路。像素芯片组还包括指纹采集芯片。设置于集成芯片上的一个指纹采集芯片与集成芯片中的一个指纹像素采集电路电连接,指纹像素采集电路用于驱动指纹采集芯片进行指纹采集。其中,不同像素芯片组中的多个指纹采集芯片构成指纹采集器。这样一来,无需单独在电路板上

设置指纹采集器,而是将指纹采集器的采集像素集成于每个像素芯片组中,从而有利于提高显示模组的集成度。

15.可选的,集成芯片还包括集成于第一芯片本体中的多个指纹像素采集电路;电路衬底还集成有一个指纹像素采集电路。像素芯片组还包括指纹采集芯片。设置于集成芯片上的一个指纹采集芯片与集成芯片中的一个指纹像素采集电路电连接,设置于电路衬底上的指纹采集芯片与电路衬底中的指纹像素采集电路电连接。指纹像素采集电路用于驱动指纹采集芯片进行指纹采集。其中,不同像素芯片组中的多个指纹采集芯片构成指纹采集器。这样一来,集成芯片和电路衬底上方的像素芯片组中均设置有指纹采集器的采集像素,有利于提高指纹采集的精度。此外,指纹采集芯片和指纹像素采集电路的技术效果同上所述,此处不再赘述。

16.可选的,集成芯片还包括集成于第一芯片本体中的多个光线发射像素驱动电路和多个光线接收像素驱动电路。像素芯片组还包括光线发射芯片以及光线接收芯片。设置于集成芯片上的一个光线发射芯片与集成芯片中的一个光线发射像素驱动电路电连接,一个光线接收芯片与集成芯片中的一个光线接收像素驱动电路电连接。光线发射像素驱动电路用于驱动光线发射芯片发射光线。光线接收像素驱动电路用于驱动光线接收芯片接收光线。其中,不同像素芯片组中的多个光线发射芯片构成光线发射器,不同像素芯片组中的多个光线接收芯片构成光线接收器。因此无需单独在电路板上设置光线发射器,而是将光线发射器的像素集成于每个像素芯片组中,从而有利于提高显示模组的集成度。因此无需单独在电路板上设置光线接收器,而是将光线接收器的像素集成于每个像素芯片组中,从而有利于提高显示模组的集成度。

17.可选的,集成芯片还包括集成于第一芯片本体中的多个光线发射像素驱动电路和多个光线接收像素驱动电路。电路衬底还集成有一个光线发射像素驱动电路和一个光线接收像素驱动电路。像素芯片组还包括光线发射芯片以及光线接收芯片。设置于集成芯片上的一个光线发射芯片与集成芯片中的一个光线发射像素驱动电路电连接,一个光线接收芯片与集成芯片中的一个光线接收像素驱动电路电连接。设置于电路衬底上的一个光线发射芯片与电路衬底中的一个光线发射像素驱动电路电连接,一个光线接收芯片与电路衬底中的一个光线接收像素驱动电路电连接。光线发射像素驱动电路用于驱动光线发射芯片发射光线;光线接收像素驱动电路用于驱动光线接收芯片接收光线。其中,不同像素芯片组中的多个光线发射芯片构成光线发射器,不同像素芯片组中的多个光线接收芯片构成光线接收器。这样一来,集成芯片和电路衬底上方的像素芯片组中均设置有光线发射器和光线接收器的像素,有利于提高指纹采集的精度。此外,光线发射芯片、光线接收芯片以及光线发射像素驱动电路和光线接收像素驱动电路的技术效果同上所述,此处不再赘述。

18.可选的,第一芯片本体包括系统级芯片、电源管理单元、中央处理器、图像处理器,或者,存储芯片。不同集成芯片中的第一芯片本体的类型可以不同,从而可以集成更多的芯片。

19.可选的,集成芯片还包括第二芯片本体。第二芯片本体与第一芯片本体堆叠设置,且第二芯片本体位于第一芯片本体靠近电路板的一侧。第二芯片本体包括系统级芯片、电源管理单元、中央处理器或者图像处理器;第一芯片本体包括存储芯片。这样一来,通过将第一芯片本体和第二芯片本体堆叠后形成上述集成芯片,可以进一步节省显示模组中的部

件空间。

20.可选的,电路板为柔性电路板。电路板包括第一部分以及与第一部分相连接的第二部分。像素芯片组在电路板上的垂直投影位于第一部分,第二部分弯折于第一部分远离像素芯片组的一侧。显示模组还包括附加电子元件,附加电子元件设置于第二部分靠近第一部分的表面上,且与电路板电连接。这样一来,可以使得显示模组中集成更多的电子元器件,提高显示模组的集成度。

21.可选的,显示模组还包括转接板。转接板与电路板电连接,至少两个集成芯片设置于转接板远离电路板的一侧表面,且通过转接板电连接。该转接板内可以形成有用于实现上述至少两个集成芯片相互通信的电路。这样一来,无需将所有集成电路之间互联的电路结构制作与电路板中,能够节约电路板中布局电路的空间。

22.可选的,电路衬底还包括依次远离电路板的衬底本体和重布线层,显示像素驱动电路的晶体管集成于衬底本体中,显示像素驱动电路中的走线集成于重布线层中。其中,衬底本体的材料包括单晶硅。这样一来,可以采用上述cmos工艺在硅基底内形成用于构成显示像素电路的晶体管。然后,在制作有晶体管的衬底本体远离电路板的一侧制作上述重布线层。通过该重布线层中的金属走线将衬底本体中的晶体管按照设计要求进行互联,从而形成上述显示像素驱动电路。

23.可选的,显示模组还包括封装层,封装层位于像素芯片组远离电路板的一侧,且覆盖集成芯片以及像素芯片组。封装层用于对集成芯片以及像素芯片组进行保护,避免水氧侵蚀集成芯片以及像素芯片。

24.可选的,显示模组还包括盖板,盖板覆盖封装层远离电路板的一侧表面,且与封装层相连接,对封装层进行保护。

25.可选的,显示模组还包括散热层,散热层覆盖电路板远离像素芯片组的一侧表面,且与电路板相连接。这样一来,散热层能够对显示模组产生的热量,以及电池产生的热量传递至其余部件,例如显示模组的外壳。这样一来,由于外壳与空气相接触,从而能够使得显示模组内部的热量传递至显示模组外部,起到散热的作用。

26.本技术的另一方面,提供一种电子设备,包括电池以及如上所述的任意一种显示模组。该电池位于电路板远离像素芯片组的一侧。电池用于向显示模组供电。上述电子设备具有与前述是实施例提供的显示模组相同的技术效果,此处不再赘述。

27.本技术的另一方面,提供一种显示模组,包括电路板、电路衬底以及像素芯片组。电路衬底与电路板电连接,电路衬底集成有多个显示像素驱动电路。像素芯片组包括多个发光芯片。一个像素芯片组设置于一个电路衬底远离电路板的一侧表面;设置于电路衬底上的一个发光芯片与电路衬底中的一个显示像素电路电连接,显示像素驱动电路用于驱动发光芯片发光。该显示模组具有与前述实施例提供的显示模组相同的技术效果,此处不再赘述。

28.可选的,显示模组还包括转轴,转轴设置于电路板远离电路衬底的一侧。电路板为柔性电路板。电路板包括第一区、第二区以及位于第一区和第二区之间的弯折区。转轴在柔性电路板的垂直投影位于弯折区内。电路板包括多条金属走线,多条金属走线设置于弯折区;金属走线呈弯曲状,且金属走线的两端分别与两个电路衬底相连接。金属走线的技术效果同上所述,此处不再赘述。

29.可选的,弯折区的多个电路衬底呈矩阵形式排列呈矩阵形式排列。多条金属走线包括多条第一金属走线和多条第二金属走线。第一金属走线沿第一方向与相邻的两个电路衬底相连接,第二金属走线沿第二方向与相邻的两个电路衬底相连接;其中,第一方向与第二方向垂直。第一金属走线和多条第二金属走线的技术效果同上所述,此处不再赘述。

30.可选的,同一像素芯片组中的多个发光芯片包括第一发光芯片、第二发光芯片以及第三发光芯片。第一发光芯片、第二发光芯片以及第三发光芯片分别用于发出三原色光。第一发光芯片、第二发光芯片以及第三发光芯片的技术效果同上所述,此处不再赘述。

31.可选的,电路衬底还集成有指纹像素采集电路。像素芯片组还包括指纹采集芯片。设置于电路衬底上的一个指纹采集芯片与电路衬底中的一个指纹像素采集电路电连接。指纹像素采集电路用于驱动指纹采集芯片进行指纹采集。其中,不同像素芯片组中的多个指纹采集芯片构成指纹采集器。指纹采集芯片和指纹像素采集电路的技术效果同上所述,此处不再赘述。

32.可选的,电路衬底还集成有光线发射像素驱动电路和光线接收像素驱动电路。像素芯片组还包括光线发射芯片以及光线接收芯片。设置于电路衬底上的一个光线发射芯片与电路衬底中的一个光线发射像素驱动电路电连接,一个光线接收芯片与电路衬底中的一个光线接收像素驱动电路电连接。光线发射像素驱动电路用于驱动光线发射芯片发射光线;光线接收像素驱动电路用于驱动光线接收芯片接收光线。其中,不同像素芯片组中的多个光线发射芯片构成光线发射器,不同像素芯片组中的多个光线接收芯片构成光线接收器。光线发射像素驱动电路和光线接收像素驱动电路,以及光线发射芯片以及光线接收芯片的技术效果同上所述,此处不再赘述。

33.可选的,电路衬底还包括依次远离电路板的衬底本体和重布线层,显示像素驱动电路的晶体管集成于衬底本体中,显示像素驱动电路中的走线集成于重布线层中。其中,衬底本体的材料包括单晶硅。衬底本体和重布线层的技术效果同上所述,此处不再赘述。

34.可选的,电路板为柔性电路板。电路板包括第一部分以及与第一部分相连接的第二部分;多个电路衬底设置于第一部分。第二部分弯折于第一部分远离电路衬底的一侧。显示模组还包括附加电子元件,附加电子元件设置于第二部分靠近第一部分的表面上,且与电路板电连接。电路板的第一部分、第二部分,以及附加电子元件的技术效果同上所述,此处不再赘述。

35.本技术的另一方面,提供一种电子设备,包括电池以及如上所述的任意一种显示模组。该电池位于电路板远离像素芯片组的一侧。电池用于向显示模组供电。上述电子设备具有与前述是实施例提供的显示模组相同的技术效果,此处不再赘述。

附图说明

36.图1为现有技术提供的一种amoled电子设备的结构示意图;

37.图2为本技术实施例提供的一种电子设备的结构示意图;

38.图3a为图2中显示模组的一种结构示意图;

39.图3b为图3a中集成芯片的一种结构示意图;

40.图4为本技术实施例提供的另一种显示模组的结构示意图;

41.图5a为本技术实施例提供的dcu的一种结构示意图;

42.图5b为本技术实施例提供的dcu的另一种结构示意图;

43.图6a为本技术实施例提供的pu的一种结构示意图;

44.图6b为本技术实施例提供的dcu和pu的一种结构示意图;

45.图6c为本技术实施例提供的pu的另一种结构示意图;

46.图7a为本技术实施例提供的一种集成芯片的结构示意图;

47.图7b为本技术实施例提供的dcu的另一种结构示意图;

48.图8a为本技术实施例提供的一种电路衬底的结构示意图;

49.图8b为本技术实施例提供的pu的另一种结构示意图;

50.图9a为本技术实施例提供的一种集成芯片的结构示意图;

51.图9b为本技术实施例提供的dcu的另一种结构示意图;

52.图10a为本技术实施例提供的一种电路衬底的结构示意图;

53.图10b为本技术实施例提供的一种晶圆的结构示意图;

54.图10c为图10b所示的晶圆的部分结构示意图;

55.图10d为本技术实施例提供的另一种晶圆的结构示意图;

56.图10e为本技术实施例提供的pu的另一种结构示意图;

57.图11为本技术实施例提供的一种电子设备的结构示意图;

58.图12为本技术实施例提供的一种可折叠的显示模组的结构示意图;

59.图13a为图12中电路板的一种区域划分示意图;

60.图13b为图12中电路板的弯折结构示意图;

61.图14a为本技术实施例提供的一种显示模组的结构示意图;

62.图14b为本技术实施例提供的一种pu与电路板的绑定过程示意图;

63.图14c为本技术实施例提供的一种dcu与电路板的绑定过程示意图;

64.图14d为本技术实施例提供的另一种dcu与电路板的绑定过程示意图;

65.图15a为本技术实施例提供的另一种显示模组的结构示意图;

66.图15b为本技术实施例提供的另一种显示模组的结构示意图;

67.图16a为本技术实施例提供的另一种电子设备的结构示意图;

68.图16b为本技术实施例提供的另一种电子设备的结构示意图;

69.图17为本技术实施例提供的另一种电子设备的结构示意图;

70.图18a为本技术实施例提供的一种电路板的区域划分示意图;

71.图18b采用图18a所示的电路板构成的显示模组的一种结构示意图;

72.图19为本技术实施例提供的另一种显示屏的结构示意图;

73.图20为本技术实施例提供的另一种显示屏的结构示意图;

74.图21为本技术实施例提供的一种区域划分示意图;

75.图22为本技术实施例提供的另一种显示模组的结构示意图;

76.图23为本技术实施例提供的另一种电子设备的结构示意图。

77.附图标记:

78.10

‑

tft背板;11

‑

控制芯片;02

‑

电子设备;01

‑

显示模组;13

‑

电池;14

‑

电路板;20

‑

集成芯片;201

‑

第一芯片本体;30

‑

电路衬底;40

‑

像素芯片组;202

‑

第二芯片本体;401

‑

发光芯片;401a

‑

第一发光芯片;401b

‑

第二发光芯片;401c

‑

第三发光芯片;100

‑

显示像素驱动电

路;301

‑

衬底本体;101

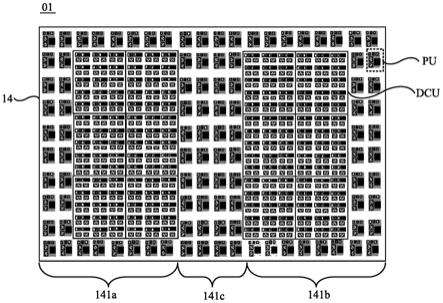

‑

指纹像素采集电路;402

‑

指纹采集芯片;102

‑

光线发射像素驱动电路;103

‑

光线接收像素驱动电路;403

‑

光线发射芯片;404

‑

光线接收芯片;200

‑

晶圆;60

‑

焊盘;51

‑

光线发射器;52

‑

光线接收器;15

‑

转轴;140a

‑

第一主视区;140b

‑

第二主视区;141a

‑

第一周边区;141b

‑

第二周边区;141c

‑

弯折区;80

‑

转接板;81

‑

焊球;61

‑

金属走线;61a

‑

第一金属轴线;61b

‑

第二金属走线;71

‑

封装层;72

‑

盖板;73

‑

散热层;142

‑

第一部分;143

‑

第二部分;203

‑

附加电子元件;151

‑

第一区;152

‑

第二区。

具体实施方式

79.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。

80.以下,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。

81.此外,本技术中,“左”、“右”等方位术语可以包括但不限于相对附图中的部件示意置放的方位来定义的,应当理解到,这些方向性术语可以是相对的概念,它们用于相对于的描述和澄清,其可以根据附图中部件附图所放置的方位的变化而相应地发生变化。

82.在本技术中,除非另有明确的规定和限定,术语“连接”应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或成一体;可以是直接相连,也可以通过中间媒介间接相连。此外,术语“电连接”可以是直接的电性连接,也可以是通过中间媒介间接的电性连接。

83.本技术实施例提供一种电子设备,该电子设备可以包括手机(mobile phone)、平板电脑(pad)、电视、智能穿戴产品(例如,智能手表、智能手环)、虚拟现实(virtual reality,vr)终端设备、增强现实(augmented reality ar)终端设备等具有显示功能的电子产品。本技术实施例对上述电子设备的具体形式不做特殊限制。以下为了方便说明,以上述电子设备02为如图2所示的手机为例进行说明。该电子设备02可以包括用于显示图像的显示模组01,以及位于该显示模组01背面的电池13,电池13用于向显示模组01供电。以下通过不同的示例对该显示模组01的结构进行详细的说明。

84.示例一

85.本示例中,电子设备02中的显示模组01,如图3a所示,可以包括电路板14。该电路板14可以具有相对设置的第一表面a1和第二表面a2。在此基础上,上述显示模组01还可以包括设置于电路板14的第一表面a1上,且与该电路板14电连接的集成芯片20和电路衬底30。本技术是以显示模组01包括两个或者两个(以下简称多个)以上的集成芯片20,以及多个电路衬底30为例进行的说明。

86.在本技术的一些实施例中,如图3a所示,集成芯片20可以包括第一芯片本体(chiplet)201。如图3b(沿图3a中的箭头b1得到的俯视图)所示,第一芯片本体201的横截面(与第一表面a1平行)可以为矩形,该矩形的任意一条边的尺寸l(以下简称单边尺寸)可以为毫米级。

87.示例的,上述第一芯片本体201可以为系统级芯片(system on a chip,soc)、电源管理单元(power management unit,pmu)、图像处理器(graphics processing unit,gpu)

或者中央处理器(central processing unit,cpu)。或者,上述第一芯片本体201可以为存储芯片,例如,通用闪存存储器(universal flash storage,ufs),或者双倍数据速率(double data rate,ddr)存储器。不同的集成芯片20中的第一芯片本体201可以不相同。上述第一芯片本体201可以为裸芯片(die),也可以为对裸芯片进行封装后得到的芯片封装结构。

88.或者,在本技术的另一些实施例中,如图4所示,上述集成芯片20可以包括第一芯片201和第二芯片本体202。该第二芯片本体202与第一芯片本体201堆叠设置。例如,第二芯片本体202可以位于第一芯片本体201靠近电路板14的一侧。在此情况下,第二芯片本体202可以与电路板14直接电连接,而第一芯片本体201可以采用倒装芯片绑定(flip chip bonding)工艺,使得第一芯片本体201中的电路结构所在的正面朝向第二芯片本体202远离电路板14的一侧表面。并且,第一芯片本体201可以通过贯穿第二芯片本体202的穿透硅通孔(through silicon via,tsv)与电路板14间接电连接。同理,第二芯片本体202的单边尺寸可以为毫米级。

89.示例的,上述第二芯片本体202可以包括soc、pmu、cpu或者gpu。该第一芯片本体201可以包括ufs或者ddr。或者,又示例的,第一芯片本体201可以包括soc、pmu、cpu或者gpu。第二芯片本体202可以包括ufs或者ddr。

90.在此基础上,上述显示模组01还可以包括如图4所示的多个像素芯片组40。该多个像素芯片组40中,至少一个像素芯片组40设置于一个集成芯片20远离电路板14的一侧表面。示例的,一个集成芯片20远离电路板14的一侧表面上可以设置有如图5a(沿图4中的b2箭头得到的俯视图)所示的多个上述像素芯片组40。

91.示例的,上述像素驱动组40可以为显示模组01用于实现显示功能的部件的最小重复单元。在此情况下,每个像素芯片组40可以包括多个发光芯片401。其中,该发光芯片401是指采用半导体芯片制备工艺,在晶圆(wafer)上形成阵列排布的晶粒,每个晶粒具有发光层。然后对形成有上述晶粒的晶圆进行切割,使得各个晶粒彼此独立。切割后每个独立的晶粒作为上述发光芯片401,该晶粒被切割后形成的边缘作为该发光芯片401的边界。在本技术的一些实施例中,该发光芯片401可以为晶粒尺寸在几十微米的微型(micro)发光二极管(light emitting diode,led),或者,晶粒尺寸在100微米以上的小型(mini)led。上述发光芯片401为电流驱动器件。在此情况下,每个发光芯片401可以作为显示模组01的一个子像素(sub pixel),同一像素芯片组40中的多个发光芯片404可以至少发出三原色光,此时上述像素芯片组40可以作为显示模组01的一个像素(pixel),使得显示模组01能够显示图像。

92.由上述可知,集成芯片20中第一芯片本体201或第二芯片本体202的单边尺寸可以为毫米级,例如10mm左右,以下为了方便说明,可以将集成芯片20以及设置于该集成芯片20上的多个像素芯片组40称为毫米级显示芯片集成单元(display chiplet unit,dcu)100。

93.在本技术的一些实施例中,如图5a所示,同一像素芯片组40中的多个发光芯片可以包括第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c。其中,第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c可以分别用于发出三原色光。例如,第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c可以分别用于发出红(red,r)光、蓝(blue,b)光以及绿(green,g)光。这样一来,同一个像素芯片组40中的第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c可以构成一个像素(pixel)。通过调节同一个像

素芯片组40中的第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c各自的发光亮度,可以达到控制显示模组01进行彩色显示时,显示图像的像素灰阶的目的。

94.基于此,为了能够驱动设置于该集成芯片20上的发光芯片401发光,如图5b所示,上述集成芯片20还包括集成于第一芯片本体201中的多个显示像素驱动电路100。例如,在采用互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)工艺制作上述第一芯片本体201(例如soc、pmu、cpu、gpu、ufs或者ddr)的过程中,可以将该显示像素驱动电路100集成于第一芯片本体201中。在此情况下,上述设置于集成芯片20上的一个发光芯片401可以与该集成芯片20中的一个显示像素驱动电路100电连接。上述显示像素驱动电路100用于驱动发光芯片401发光。

95.需要说明的是,该显示像素驱动电路100可以包括多个采用cmos工艺形成的晶体管。上述显示像素驱动电路100可以包括驱动晶体管和多个开关晶体管。通过控制开关晶体管的到导通和关闭可以将与显示数据有关的数据电压写入至驱动晶体管。该驱动晶体管可以根据上述数据电压产生与该数据电压相匹配的驱动电流。由于上述发光芯片401为电流驱动器件,因此当上述驱动电流流过发光芯片401时,可以驱动发光芯片401发光。通过控制驱动电流的大小,可以对发光芯片401的发光亮度进行控制。本技术对显示像素驱动电路100中的多个晶体管的连接方式不做限定,只要能够达到驱动与其电连接的发光芯片401发光的目的即可。

96.此外,当集成芯片20中具有一个芯片本体,例如上述第一芯片本体201时,以及集成芯片20包括层叠设置的第一芯片本体201和第二芯片本体202时,该第一芯片本体201均与像素芯片组40直接接触。在此情况下,为了使得显示像素驱动电路100与设置于集成芯片20上的发光器件401之间的信号传输距离最短,提高信号传输的效率,上述均是以该显示像素驱动电路100集成于第一芯片本体201为例进行的说明。

97.或者,在本技术的另一些实施例中,当集成芯片20包括层叠设置的第一芯片本体201和第二芯片本体202时,还可以将上述显示像素驱动电路100集成于第二芯片本体202中。在此情况下,设置于集成芯片20上的发光器件401可以通过第一芯片本体201,与集成于第二芯片本体202中的该显示像素驱动电路100间接电连接。

98.在此基础上,如图4所示,该显示模组01中的上述多个像素芯片组40中,一个像素芯片组40设置于一个电路衬底30远离电路板14的一侧表面。即,如图6a所示,一个电路衬底30上设置有一个像素芯片组40。该像素芯片组40的结构同上所述,可以包括第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c。

99.如图6b所示,电路衬底30在电路板14(如图4所示)上的垂直投影的面积,小于集成芯片20在电路板14上的垂直投影的面积。示例的,该电路衬底30的单边尺寸可以为微米级,例如60μm左右。因此,以下为了方便说明,可以将电路衬底30以及设置于该电路衬底30上的一个像素芯片组40称为微米级像素集成单元(pixel unit,pu)。

100.基于此,为了能够驱动设置于该电路衬底30上的发光芯片发光,如图6c所示,该电路衬底30可以包括多个显示像素驱动电路100。在本技术的一些实施例中,电路衬底30还可以包括依次远离电路板14的衬底本体301和重布线层(re

‑

distribution layer,rdl)。衬底本体301的材料可以为单晶硅,此时,该衬底本体301可以称为硅基底。

101.这样一来,可以采用上述cmos工艺在硅基底内形成用于构成显示像素电路100的

晶体管。然后,在制作有晶体管的衬底本体301远离电路板14的一侧制作上述rdl。通过该rdl中的金属走线将衬底本体301中的晶体管按照设计要求进行互联,从而形成上述显示像素驱动电路100。此时,显示像素驱动电路100的晶体管集成于衬底本体301中,显示像素驱动电路100中的走线集成于rdl中。在此情况下,设置于电路衬底30上的一个发光芯片401可以与电路衬底30中的一个显示像素电路100电连接,从而可以在显示像素驱动电路100的驱动作用下发光。

102.综上所述,本技术实施例提供的显示模组01包括电路板14,以及设置于电路板14同一侧的多个dcu和多个pu。其中,如图5b所示,dcu包括与电路板14电连接的集成芯片20,以及设置于该集成芯片20远离电路板14一侧的像素芯片组40。该像素芯片组40中设置有多个发光芯片401。每个发光芯片401就与集成于集成芯片20的第一芯片本体201中的一个显示像素驱动电路100电连接。此外,如图6b所示,pu包括与电路板14电连接的电路衬底30,以及设置于该电路衬底30远离电路板14一侧的像素芯片组40。该像素芯片组40中同样设置有多个发光芯片401。电路衬底30上的一个发光芯片401可以与集成于电路衬底30中的一个显示像素驱动电路100电连接。上述显示像素驱动电路100可以驱动与其电连接的发光芯片401发光。每个发光芯片401可以作为显示模组01的一个子像素,使得整个显示模组01能够实现图像显示。

103.这样一来,一方面,由于用于驱动发光芯片401发光的显示像素驱动电路100可以集成于上述dcu中的第一芯片本体201以及pu中的电路衬底30中,因此本技术实施例提供的显示模组01相对于目前的amoled显示模组而言,无需制作tft背板,能够有效减小显示模组01的重量,减薄显示模组01的厚度。另一方面,部分发光芯片401与集成芯片20层叠设置,部分发光芯片401与电路衬底30层叠设置,集成芯片20和电路衬底30均设置于电路板14的同一侧,因此提高了显示模组01的集成度。又一方面,以发光芯片401为micro led为例,micro led相对于oled而言,功耗更低,有利于减小显示模组01中电池的体积。此外,micro led相对于oled而言,亮度更高,尺寸更小从而具有更小的开口率。这样一来,能够有效节约显示模组01中的部件空间,有利于集成更多的电子元器件。

104.在此基础上,为了使得显示模组01能够具有指纹识别功能,如图7a所示,上述dcu中的集成芯片20还可以包括集成于第一芯片本体201中的多个指纹像素采集电路101。此时,上述像素驱动组40可以为显示模组01用于实现显示功能以及指纹采集功能的部件的最小重复单元。在此情况下,如图7b所示,当设置于第一芯片本体201上的像素芯片组40还包括指纹采集芯片402时,设置于第一芯片本体201上的一个指纹采集芯片402可以与第一芯片本体201中的一个指纹像素采集电路101(如图7a所示)电连接。该指纹像素采集电路101用于驱动指纹采集芯片402进行指纹采集。

105.此外,上述pu中的电路衬底30还可以包括集成于电路衬底30中的,如图8a所示的上述指纹像素采集电路101。在此情况下,如图8b所示,当设置于衬底本体301上的像素芯片组40还包括指纹采集芯片402时,设置于衬底本体301上的一个指纹采集芯片402可以与该电路衬底30中的一个指纹像素采集电路101(如图8a所示)电连接。

106.在此情况下,每个像素芯片组40中的指纹采集芯片402可以作为一个指纹采集器的采集像素。这样一来,不同像素芯片组40中的多个指纹采集芯片402可以共同构成上述指纹采集器,因此无需单独在电路板14上设置指纹采集器,而是将指纹采集器的采集像素集

成于每个像素芯片组40中,从而有利于提高显示模组的集成度。此时,设置集成芯片20上的像素芯片组40,或者,设置于电路衬底30上的像素芯片组40中的至少一个像素芯片组40可以包括第一发光芯片401a、第二发光芯片401b、第三发光芯片401c以及上述指纹采集芯片402。

107.需要说明的是,该指纹像素采集电路101可以包括多个采用cmos工艺形成的晶体管,本技术对指纹像素采集电路101中的多个晶体管的连接方式不做限定,只要能够达到驱动与其电连接的指纹采集芯片402进行指纹采集的目的即可。

108.本技术对指纹采集芯片402进行指纹采集的方式不做限定。例如,该指纹采集芯片402可以采用光学方式对指纹进行采集,此时指纹采集芯片402内设置有光电转换元件,通过指纹中脊线和谷线反射光线的不同,对指纹的类别进行采集,并将采集结果传输至soc或者cpu。或者,又例如,上述指纹采集芯片402还可以采用半导体电极与指纹中的脊线和谷线之间形成的电容(或电感)不同,对指纹进行采集,并将采集结果传输至soc或者cpu。soc或者cpu根据指纹采集芯片402的采集结果以及指纹采集芯片402的位置坐标可以获得指纹的图案,达到指纹采集或识别的目的。

109.在此基础上,为了使得显示模组01能够具有面部或者手势识别功能,上述dcu中的集成芯片20如图9a所示,还可以包括集成于第一芯片本体201中的光线发射像素驱动电路102和光线接收像素驱动电路103。示例的,可以通过cmos工艺在制作第一芯片本体201(例如soc、pmu、cpu、gpu、ufs或者ddr)的同时,将上述光线发射像素驱动电路102、光线接收像素驱动电路103,以及如图9a所示的显示像素驱动电路100、指纹像素采集电路101集成于该第一芯片本体201中,从而形成上述集成芯片20。

110.基于此,上述像素驱动组40可以为显示模组01用于实现显示功能以及面部或者手势识别功能的部件的最小重复单元。在此情况下,如图9b所示,当设置于第一芯片本体201上的像素芯片组40还包括光线发射芯片403以及光线接收芯片404时,可以采用芯片到晶圆(die to wafer,d2w),也可以称为(chip to wafer,c2w)的绑定(bonding)方式将光线发射芯片403设置于集成芯片20上,并与第一芯片本体201中的光线发射像素驱动电路102(如图9a所述)电连接。此外,可以采用d2w的绑定方式将光线接收芯片404设置于集成芯片20上,并与第一芯片本体201中的光线接收像素驱动电路103(如图9a所示)电连接。该光线发射像素驱动电路102用于驱动光线发射芯片403发射光线,光线接收像素驱动电路103用于驱动光线接收芯片404接收光线。

111.同理,当设置于集成芯片20上的像素芯片组40包括上述第一发光芯片401a、第二发光芯片401b、第三发光芯片401c、指纹采集芯片402时,可以通过巨量转移的方法,利用上述d2w的绑定方式,将第一发光芯片401a、第二发光芯片401b、第三发光芯片401c中的任意一个发光芯片设置于集成芯片20上,并与第一芯片本体201中的一个显示像素驱动电路100电连接。同理采用d2w的绑定方式,将指纹采集芯片402设置于集成芯片20上,与第一芯片本体201中的指纹像素采集电路101电连接。此时,设置集成芯片20上的至少一个像素芯片组40可以包括第一发光芯片401a、第二发光芯片401b、第三发光芯片401c、指纹采集芯片402、光线发射芯片403以及光线接收芯片404。

112.此外,上述pu中的电路衬底30如图10a所示,还可以包括集成于电路衬底30中的上述光线发射像素驱动电路102和光线接收像素驱动电路103。示例的,可以在如图10b所示的

硅(si)晶圆(wafer)200上,采用cmos工艺制作光线发射像素驱动电路102和光线接收像素驱动电路103,以及上述显示像素驱动电路100、指纹像素采集电路101中的晶体管。然后,由上述可知,在制作有晶体管的晶圆200上制作上述rld。通过该rld中的金属走线将晶圆200中的晶体管按照设计要求进行互联,从而形成上述光线发射像素驱动电路102、光线接收像素驱动电路103,以及上述显示像素驱动电路100、指纹像素采集电路101。

113.在此基础上,还可以在rld远离晶圆200的一侧表面上,制作如图10c所示的多个焊盘60。接下来,如图10d所示,当设置于pu中的像素芯片组40还包括光线发射芯片403以及光线接收芯片404时,可以采用d2w的绑定方式,通过上述焊盘60(如图10c所示)将光线发射芯片403设置于晶圆200上,并与晶圆200中的光线发射像素驱动电路102(如图10b所示)电连接。此外,采用d2w的绑定方式,通过上述焊盘60将光线接收芯片404设置于晶圆200上,并与晶圆200中的光线接收像素驱动电路103(如图10b所示)电连接。

114.同理,当设置于pu中的像素芯片组40包括上述第一发光芯片401a、第二发光芯片401b、第三发光芯片401c、指纹采集芯片402时,可以通过巨量转移的方法,采用上述d2w的绑定方式,通过上述焊盘60将第一发光芯片401a、第二发光芯片401b、第三发光芯片401c中的任意一个发光芯片设置于晶圆200上,并与晶圆200中的一个显示像素驱动电路100(如图10b所示)电连接。同理采用d2w的绑定方式,通过上述焊盘60将指纹采集芯片402设置于晶圆200上,并与晶圆200中的指纹像素采集电路101(如图10b所示)电连接。此时,设置于晶圆200上的至少一个pu中的像素芯片组40可以包括第一发光芯片401a、第二发光芯片401b、第三发光芯片401c、指纹采集芯片402、光线发射芯片403以及光线接收芯片404。

115.接下来,如图10d所示,可以沿在晶圆200上预先设置的切割路径(cl)对晶圆200进行切割,形成如图10e所示的独立的pu。

116.在此情况下,每个像素芯片组40中的光线发射芯片403可以作为如图11所示的光线发射器51的像素。这样一来,不同像素芯片组40中的多个光线发射芯片403可以共同构成上述光线发射器51。因此无需单独在电路板14上设置光线发射器51,而是将光线发射器51的像素集成于每个像素芯片组40中,从而有利于提高显示模组的集成度。同理,每个像素芯片组40中的光线接收芯片404可以作为如图11所示的光线接收器52的像素。这样一来,不同像素芯片组40中的多个光线接收芯片404可以共同构成上述光线接收器52。因此无需单独在电路板14上设置光线接收器52,而是将光线接收器52的像素集成于每个像素芯片组40中,从而有利于提高显示模组的集成度。

117.需要说明的是,由上述可知,该光线发射像素驱动电路102和光线接收像素驱动电路103可以包括多个采用cmos工艺形成的晶体管,本技术对光线发射像素驱动电路102和光线接收像素驱动电路103中的多个晶体管的连接方式不做限定,只要能够使得光线发射像素驱动电路102驱动与其电连接的光线发射芯片403发射光线,光线接收像素驱动电路103驱动与其电连接的光线接收芯片404接收光线即可。

118.示例的,本技术对采用图11所示的光线发射器51和光线接收器52,实现面部或者手势识别的方式不做限定。例如,可以通过识别结构光的变形,达到识别面部或者手势的目的。在此情况下,可以控制光线发射器51中作为像素的各个光线发射芯片403进行发光,使得光线发射器51发出具有特定图案的光线s1,当该光线照射到如图11所示的用户面部时,用户面部会对入射的光线进行反射,形成反射光s2。接下来,光线接收器52中作为像素的各

个光线接收芯片404接收上述反射光s2,并进行光电转换,将光信号转换成电信号后传输至soc或者cpu。soc或者cpu根据光线接收器52输出的信号以及光线接收器52中各个光线接收芯片404的位置坐标,可以获得用户面部反射光s2的图案,并将该图案与光线发射器51发出的光线s1的原始图案进行比对,获得结构光的变形程度,最终达到识别用户面部(或手势)的目的。

119.或者,又例如,可以通过识别光线的飞行时间(time of flight,tof),达到识别面部或者手势的目的。在此情况下,可以控制光线发射器51中各个光线发射芯片403发出光线s1。当该光线照射到如图11所示的用户面部时,用户面部会对入射的光线进行反射,形成反射光s2。接下来,光线接收器52中各个光线接收芯片404接收用户面部的反射光s2。soc或者cpu根据光线接收器52接收到反射光s2的时间以及光线接收器52中各个光线接收芯片404的位置坐标,获得用户面部与显示模组01之间的距离,达到识别用户面部(或手势)的目的。

120.在此基础上,可以将上述dcu和pu设置于上述电路板14的第一表面a1上,并与电路板14电连接,从而可以形成该显示装置01的显示屏。以电子设备02中的显示模组01具有如图9b所示的dcu,以及如图10b所示的pu,并且,dcu和pu中的像素芯片组40包括第一发光芯片401a、第二发光芯片401b、第三发光芯片401c、指纹采集芯片402、光线发射芯片403以及光线接收芯片404为例,对该显示模组01中dcu和pu的设置方式进行举例说明。

121.在本技术的一些实施例中,如图12所示,用于承载上述dcu和pu的电路板14为柔性电路板(flexible printed circuit,fpc)。在此基础上,该显示装置01还可以包括转轴15。该转轴15可以设置于电路板14的第二表面a2所在的一侧。这样一来,在转轴15的作用下,可以使得电路板14在转轴15位置处进行弯折,从而使得整个显示模组01能够折叠。

122.在此情况下,如图13a所示,电路板14可以包括第一主视区140a、第二主视区140b、第一周边区141a、第二周边区141b以及弯折区141c。其中,弯折区141c位于第一主视区140a和第二主视区140b之间。并且,如图13b所示,转轴15在电路板14的垂直投影位于图13a所示的弯折区141c内。在此情况下,当电路板14在转轴15的作用下发生弯折时,电路板14中弯折区141c所在的部分会发生弯曲变形。此外,第一周边区141a设置于第一主视区140a的周边,第二周边区141b设置于第二主视区140b的周边。

123.由上述可知,dcu中的集成芯片20在电路板14上的垂直投影的面积,大于pu中电路衬底30在电路板14上的垂直投影的面积。示例的,dcu的单边尺寸为毫米级,而pu的单边尺寸为微米级。此外,电路板14在弯折的过程中,弯折区141c会发生变形。在此情况下,可以如图14a所示,将尺寸较小的pu设置于弯折区141c。由于pu的尺寸较小,因此pu与弯折区141c的接触面积相对于弯折区141c发生形变的面积而言较小,所以在弯折区141c发生弯折的过程中,不容易使得pu发生断裂,有利于提高产品的可靠性。

124.此外,上述电路板14的第一周边区141a和第二周边区141b位于电路板14的边缘位置。在此情况下,显示模组01在运输或使用的过程中,上述第一周边区141a和第二周边区141b容易在外力作用下,例如受到碰撞的过程中发生轻微的变形。因此,可以将尺寸较小的pu设置于第一周边区141a和第二周边区141b,从而当显示模组01在外力作用下,使得第一周边区141a和第二周边区141b发生碰撞时,不容易使得pu发生断裂,有利于提高产品的可靠性。

125.示例的,当沿如图10c所示的切割路径(cl)对晶圆200进行切割,以形成如图10d所

示的独立的pu后,可以采用芯片到柔性电路板(chip to fpc)的工艺,通过设置于pu中衬底本体301远离像素集成组件40一侧表面上的焊盘60(如图14b所示),将各个独立的pu焊接于如图14a所示的电路板14的第一周边区141a、第二周边区141b以及弯折区141c,以与电路板14电连接,从而可以完成pu的组装。

126.此外,由于dcu的尺寸较大,因此与电路板14的接触面积较大,所以可以将dcu设置于电路板14中不容易发生变形的区域,例如图13b所示的第一主视区140a和第二主视区140b。在此情况下,如图14a所示,多个pu分布于以矩阵形式排列在一起的多个dcu的周边。

127.在本技术的一些实施例中,当显示模组01具有多个dcu,且多个dcu之间需要相互通信时,可以将用于实现多个dcu相互通信的电路(图中未示出)制作于电路板14中,在此情况下,可以采用芯片到柔性电路板(chip to fpc)的绑定方式,如图14c所示,将每个dcu通过集成芯片20靠近电路板14一侧的焊盘60,焊接于电路板14上与电路板14电连接,从而实现dcu的组装。

128.或者,在本技术的另一些实施例中,在显示模组01具有多个需要相互通信的dcu,但是电路板14中制作电路的空间有限时,如图14d所示,该显示模组01还可以包括转接板(interposer)80。转接板80与电路板14电连接,至少两个dcu设置于转接板80远离电路板14的一侧表面。该转接板80内形成有用于实现上述至少两个dcu相互通信的电路(图中未示出)。这样一来,可以先将不同dcu,通过集成芯片20内采用不同工艺节点构成的芯片本体(包括第一芯片本体201和第二芯片本体202),采用倒装绑定工艺集成于该转接板80上形成一个集成模块。然后再将该集成模块通过设置于转接板80靠近电路板14一侧的可以通过焊球(solder ball)81绑定到电路板14上与该电路板14电连接,从而实现dcu的组装。

129.需要说明的是,上述采用不同工艺节点构成的芯片本体是指,不同的芯片本体在制作的过程中采用的工艺节点(例如,芯片本体中晶体管的最小线宽)不同。例如,当芯片本体为soc时,工艺节点可以为7nm、5nm或者3nm。当芯片本体为pmu时,工艺节点可以但不限于90nm。当芯片本体为ufs时,工艺节点可以但不限于14nm。

130.由上述可知,当用户折叠显示模组01时,电路板14的弯折区141c会发生弯折,且该弯折区141c的形变量大于收到碰撞而发生形变的第一周边区141a和第二周边区141b的形变量。因此,为了进一步避免位于弯折区的pu发生断裂,提高显示模组01的弯折可靠性,如图15a所示,上述电路板14还包括多条设置于弯折区141c的金属走线61。

131.该金属走线61可以在制作电路板14的过程中一并制作而成。构成该金属走线61的材料可以为电路板14中常用的金属材料例如,金属铜。上述金属走线61呈弯曲状,例如,为s型或者为ω型。并且,该金属走线61的两端分别与两个pu的电路衬底30相连接。当采用上述芯片到柔性电路板的绑定工艺,通过设置于电路衬底30上的焊盘60(如图14b所示),将各个独立的pu焊接于电路板14的弯折区141c时,可以将两个pu的电路衬底30与该电路板14上的金属走线61相连接。这样一来,由于金属走线61具有一定的拉伸性能,能够随着弯折区141c的弯折而发生变形,减小由于弯折区141c形变而在pu所在位置产生的应力,达到进一步减小pu发生断裂的目的。

132.在本技术的一些实施例中,如图15b所示,弯折区141c中的多个pu中的电路衬底30呈矩阵形式排列。在此情况下,上述多条金属走线可以包括多条第一金属走线61a和多条第二金属走线61b。其中,第一金属走线61a沿第一方向x与相邻的两个pu中的电路衬底30相连

接,第二金属走线61b沿第二方向y与相邻的两个pu中的电路衬底30相连接。其中,第一方向与第二方向垂直。这样一来,上述多条第一金属走线61a和多条第二金属走线61b可以构成网状结构将弯折区141c中的多个pu相连接,从而能够增加弯折区141c的韧性,进一步减小pu发生断裂。

133.在此基础上,当上述dcu和pu均设置于电路板14上之后,如图16a所示,还可以在dcu和pu远离电路板14的一侧依次制作封装层71和盖板72。其中,封装层71覆盖上述dcu和pu,用于对dcu和pu进行保护,避免水氧侵蚀dcu和pu。盖板72可以覆盖封装层71远离电路板14的一侧表面,且与封装层71相连接,对封装层71进行保护。示例的,构成上述封装层71的材料可以为透明的树脂材料,可以通过成膜工艺直接在dcu和pu远离电路板14的一侧表面形成一层树脂薄膜作为上述封装层71即可。

134.因此,相对于amoled显示模组采用的薄膜封装(thin film encapsulation)工艺,形成由多层交替设置的有机薄膜层和无机薄膜层构成的封装结构而言,本技术实施例提供的显示模组01的封装层71的结构和制作工艺更加简单。当显示模组01为柔性显示模组时,构成上述盖板72的材料可以为透明的树脂材料。需要说明的是,本技术实施例中的透明材料是指,该材料的透光率可以达到85%以上。

135.此外,上述显示模组01还可以包括如图16a所示的散热层73。其中,散热层73可以覆盖电路板14远离dcu(包括集成芯片20和像素芯片组40)和pu包括电路衬底30和像素芯片组40)的一侧表面,且与电路板14相连接。构成该散热层73的材料可以包括石墨烯。电池13可以位于散热层73远离电路板14的一侧。散热层73能够对dcu和pu中发光芯片401产生的热量,以及电池13产生的热量传递至其余部件,例如显示模组01的外壳(图中位置处)。这样一来,由于外壳与空气相接触,从而能够使得显示模组01内部的热量传递至显示模组01外部,起到散热的作用。

136.需要说明的是,本技术对电池13的数量不做限定,例如,如图16a所示,上述显示模组01可以包括两个电池13,分别位于转轴15的两侧。

137.由图16a可知,不同dcu中的第一芯片本体201可以不相同,例如图16a中所示的不同位置的第一芯片本体201可以分别为soc、pmu、ddr以及usf。这样一来,可以使得显示模组01中集成更多不同功能的芯片。此外,由上述可知,dcu中还可以包括如图16b所示的层叠设置的第一芯片本体201和第二芯片本体202。通过将两个芯片本体层叠设置,可以进一步减小显示模组01的部件空间,从而有利于集成更多不同功能的芯片。

138.在此基础上,在电路板14为fpc的情况下,为了使得显示模组01中能够集成更多的附加电子元件,如图17所示,该电路板14可以包括第一部分142以及与第一部分142相连接的第二部分143。多个dcu(包括集成芯片20和像素芯片组40)和多个pu(包括电路衬底30和像素芯片组40)设置于第一部分142。在此情况下,设置于dcu和pu远离电路板14一侧的像素芯片组40在电路板14上的垂直投影可以位于该电路板14的第一部分142中。此外,第二部分143弯折于第一部分142远离dcu的一侧。

139.在此情况下,上述显示模组01还包括至少一个附加电子元件203,该附加电子元件203可以设置于第二部分143靠近第一部分142的表面上,且与电路板14电连接。在本技术的一些实施例中,上述附加电子元件203可以为芯片,例如soc、pmu、cpu、gpu、ufs或者ddr等。或者,在本技术的另一些实施例中,上述附加电子元件203还可以为传感器等器件。

140.上述是以电路板14为fpc为例进行的说明,在本技术的另一些实施例中,该电路板14还可以为pcb。在此情况下,上述显示模组01,例如手机为不能够折叠的直板手机。此时,如图18a所示,电路板14可以包括主视区140和位于主视区140周边的周边区141。

141.由上述可知,由于周边区141位于主视区140的周边,显示模组01在运输或使用的过程中,上述周边区141容易在外力作用下,例如受到碰撞的过程中发生轻微的变形。然而,位于周边区141内部的主视区140不容易在外力作用下发生变形。因此,可以将尺寸较小的pu设置于周边区141,从而当显示模组01在外力作用下,使得周边区141发生碰撞时,不容易使得pu发生断裂,有利于提高产品的可靠性。并且,将尺寸较大的dcu设置于不容易发生变形的主视区140。在此情况下,如图18b所示,多个pu(包括电路衬底30和像素芯片组40)分布于以矩阵形式排列在一起的多个dcu(包括集成芯片20和像素芯片组40)的周边。

142.需要说明的是,dcu和pu设置于电路板14上,且与该电路板14电连接的方式同上所述,此处不再赘述。上述均是每个dcu的像素芯片组40,以及每个pu的像素芯片组40在包括多个发光芯片(例如,如图10e所示的第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c)的基础上,还包括指纹采集芯片402、光线发射芯片403以及光线接收芯片404为例进行的说明。

143.在本技术的另一些实施例中,可以在显示模组01中仅需要进行指纹采集的位置的dcu和pu的像素芯片组40中设置指纹采集芯片402。同理,可以在显示模组01中,仅需要设置光线发射器51(如图11所示)的位置处的dcu和pu的像素芯片组40中,设置光线发射芯片403。在显示模组01中,仅需要设置光线接收器52(如图11所示)的位置处的dcu和pu的像素芯片组40中,设置光线发射芯片403。

144.此外,对于直板显示模组而言,上述封装层71和盖板72,以及散热层73和电池13的设置方式同上所述,此处不再赘述。

145.示例二

146.本示例与示例一相同,电子设备02中的显示模组01如图19所示包括电路板14。此外,与示例一的不同之处在于,该显示模组01仅包括dcu。该dcu同上所述包括集成芯片20和位于集成芯片20远离电路板14一侧表面的多个像素芯片组40。

147.图19以像素芯片组40包括多个发光芯片(例如,第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c)的基础上,还包括指纹采集芯片402、光线发射芯片403以及光线接收芯片404为例。在此情况下,该集成电路20可以包括集成于第一芯片本体201中的显示像素驱动电路100、指纹像素采集电路101、光线发射像素驱动电路102和光线接收像素驱动电路103。发光芯片、指纹采集芯片402、光线发射芯片403以及光线接收芯片404分别与集成于第一芯片本体201中的上述显示像素驱动电路100、指纹像素采集电路101、光线发射像素驱动电路102和光线接收像素驱动电路103电连接。上述dcu的制作过程以及dcu与电路板14电连接的过程同上所述,此处不再赘述。

148.同理,在本技术的一些实施例中,可以在显示模组01中仅需要进行指纹采集的位置的dcu的像素芯片组40中设置指纹采集芯片402。在显示模组01中,仅需要设置光线发射器51(如图11所示)的位置处的dcu的像素芯片组40中,设置光线发射芯片403。在显示模组01中,仅需要设置光线接收器52(如图11所示)的位置处的dcu的像素芯片组40中,设置光线发射芯片403。

149.此外,本示例提供的显示模组01中,上述封装层71和盖板72,以及散热层73和电池13的设置方式同上所述,此处不再赘述。

150.示例三

151.本示例与示例一相同,电子设备02中的显示模组01如图20所示包括电路板14。此外,与示例一的不同之处在于,该显示模组01仅包括pu。该pu同上所述包括电路衬底30和位于电路衬底30远离电路板14一侧表面的多个像素芯片组40。

152.图20以像素芯片组40包括多个发光芯片(例如,第一发光芯片401a、第二发光芯片401b以及第三发光芯片401c)的基础上,还包括指纹采集芯片402、光线发射芯片403以及光线接收芯片404为例。在此情况下,该电路衬底30可以包括集成于衬底本体301中的显示像素驱动电路100、指纹像素采集电路101、光线发射像素驱动电路102和光线接收像素驱动电路103。发光芯片、指纹采集芯片402、光线发射芯片403以及光线接收芯片404分别与集成于电路衬底30的衬底本体301中的上述显示像素驱动电路100、指纹像素采集电路101、光线发射像素驱动电路102和光线接收像素驱动电路103电连接。上述pu的制作过程以及pu与电路板14电连接的过程同上所述,此处不再赘述。

153.同理,在本技术的一些实施例中,可以在显示模组01中仅需要进行指纹采集的位置的pu的像素芯片组40中设置指纹采集芯片402。在显示模组01中,仅需要设置光线发射器51(如图11所示)的位置处的pu的像素芯片组40中,设置光线发射芯片403。在显示模组01中,仅需要设置光线接收器52(如图11所示)的位置处的pu的像素芯片组40中,设置光线发射芯片403。

154.此外,在本示例中,上述电路板14可以为pcb。或者,电路板14可以为fpc,且显示模组01包括位于电路板14远离上述pu一侧的转轴15。在此情况下,该电路板14可以具有如图21所示的第一区151、第二区152以及位于第一区151和第二区152之间的弯折区141c。同上所述,转轴15在电路板14的垂直投影位于弯折区141c。

155.同理,当用户折叠显示模组01时,电路板14的弯折区141c会发生弯折,且该弯折区141c的形变量大于收到碰撞而发生形变的第一周边区141a和第二周边区141b的形变量。因此,为了进一步避免位于弯折区的pu发生断裂,提高显示模组01的弯折可靠性,如图22所示,上述电路板14还包括多条设置于弯折区141c的金属走线(例如,多条第一金属走线61a和多条第二金属走线61b)。任意一条金属走线的两端分别与相邻两个pu的电路衬底30相连接。上述金属走线的形状、制作过程以及第一金属走线61a和第二金属走线61b的设置方式同上所述,此处不再赘述。

156.此外,如图23所示,本示例提供的显示模组01中的封装层71和盖板72,以及散热层73和电池13的设置方式同上所述,此处不再赘述。并且,当电路板14为fpc时,该电路板14可以包括第一部分142以及与第一部分142相连接的第二部分143。多个pu(包括电路衬底30和像素芯片组40)设置于第一部分142。此外,第二部分143弯折于第一部分142远离pu的一侧。显示模组01中的一些附加电子元件203,例如soc、pmu、cpu、gpu、ufs、ddr,或者传感器等,可以设置于第二部分143靠近第一部分142的表面上,且与电路板14电连接。

157.以上,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1