扫描信号线驱动电路、显示装置及扫描信号线的驱动方法与流程

1.以下的公开涉及一种显示装置,更详细而言,涉及用于驱动配设于显示装置的显示部的扫描信号线的扫描信号线驱动电路以及扫描信号线的驱动方法。

背景技术:

2.以往,已知有具备显示部的液晶显示装置,该显示部包含多条源极总线(数据信号线)和多条栅极总线(扫描信号线)。在这样的液晶显示装置中,在源极总线与栅极总线之间的交叉点设置有形成像素的像素形成部。各像素形成部包括:薄膜晶体管(像素tft)、用于保持像素电压值的像素电容等,该薄膜晶体管是栅极端子连接至通过对应的交叉点的栅极总线并且源极端子与通过该交叉点的源极总线连接的开关元件。在液晶显示装置中,还设置有用于驱动栅极总线的栅极驱动器(扫描信号线驱动电路)和用于驱动源极总线的源极驱动器(数据信号线驱动电路)。

3.表示像素电压值的数据信号通过源极总线传送。然而,各源极总线无法一时(同时)传递表示多行量的像素电压值的数据信号。因此,向设置于显示部的多个像素形成部内的像素电容依次逐行进行数据信号的写入(充电)。为了实现该目的,在各帧期间,栅极驱动器依次选择上述多条栅极总线。

4.然而,以往来,栅极驱动器大多作为ic((integrated circuit:集成电路)芯片而搭载于构成液晶面板的基板的周边部上。然而,近年来,在基板上直接形成栅极驱动器的情况逐渐变多。这样的栅极驱动器被称为“单片栅极驱动器”等。

5.作为上述单片栅极驱动器,已知有由隔着显示部以对置的方式配置的第一栅极驱动器和第二栅极驱动器构成的单片栅极驱动器。在这样的构成中,作为从栅极驱动器向栅极总线施加扫描信号的方式,已知有:如图26所示,向各栅极总线的两端施加扫描信号的双侧输入方式;以及如图27所示,向显示部中的栅极总线的一端和另一端交替地施加扫描信号的单侧输入方式(例如,对第奇数行的栅极总线从第一栅极驱动器施加扫描信号且对第偶数行的栅极总线从第二栅极驱动器施加扫描信号的方式)。另外,在图26和图27中附加了附图标记uc1~uc4的构成要素是后述的单位电路。采用图27所示的单侧输入方式的液晶显示装置例如被公开在日本特开2014

‑

71451号公报中。

6.一般而言,栅极驱动器具有将分别包含一个双稳态电路的多个单位电路级联连接的构成。各单位电路连接于上述多条栅极总线中的任一条,并向该所连接的栅极总线施加扫描信号。在图27所示的单侧输入方式中,第奇数行的栅极总线连接有第一栅极驱动器内的单位电路,第偶数行的栅极总线连接有第二栅极驱动器内的单位电路。即,与上述多条栅极总线连接的单位电路被交替地配置在上述多条栅极总线的一端侧和另一端侧。因此,图27所示的单侧输入方式的栅极驱动器被称为“交错配置方式”的栅极驱动器。

7.图28是表示采用双侧输入方式的情况下的第一栅极驱动器900的构成的概略电路图。该第一栅极驱动器900包含移位寄存器901和输出缓冲部902,基于由第一至第四栅极时钟信号gck1至gck4构成的四相的时钟信号进行动作。第二栅极驱动器的构成与第一栅极驱

动器900的构成相同。以下,假定在显示部配设有i条栅极总线。

8.移位寄存器901包含彼此级联连接的i个双稳态电路sr((1)~sr((i),且构成为基于第一至第四栅极时钟信号gck1~gck4将起始脉冲依次从第一级双稳态电路sr(1)传送到最终级双稳态电路sr(i)。输出缓冲部902包含与构成移位寄存器901的i个双稳态电路sr((1)~sr((i)分别对应的i个缓冲电路buff((1)~buff((i)。i个缓冲电路buff((1)~buff((i)循环地对应有第一至第四栅极时钟信号gck1~gck4。i个缓冲电路buff((1)~buff((i)的输出端分别连接有i条栅极总线gl((1)~gl((i)。各缓冲电路buff接收对应的双稳态电路sr的输出信号和对应的栅极时钟信号gck,并根据这些信号生成要施加到栅极总线gl的扫描信号。例如,第n个缓冲电路buff(n)根据第n级的双稳态电路sr(n)的输出信号以及第一栅极时钟信号gck1生成扫描信号,并将该扫描信号施加于第n行的栅极总线gl((n)。

9.图29是示出上述第一栅极驱动器900中与一条栅极总线gl对应的电路(单位电路)的构成的电路图。此外,假设图29所示的单位电路是与第n行的栅极总线gl((n)对应的单位电路。该单位电路由移位寄存器901中的第n级双稳态电路sr(n)和输出缓冲部902中的第n缓冲电路buff(n)构成。

10.此外,在本说明书中,列举使用n沟道型的薄膜晶体管(tft)的示例进行说明。关于此,在n沟道型晶体管中,漏极和源极中具有较高电位的被称为漏极,但在本说明书的说明中,一个被定义为漏极而另一个被定义为源极,因此有时源极电位高于漏极电位。

11.如图29所示,双稳态电路sr(n)包含两个n沟道型的薄膜晶体管ta1、ta2。薄膜晶体管ta1的漏极端子连接至高电平电源线vdd,薄膜晶体管ta2的源极端子连接至低电平电源线vss,薄膜晶体管ta1的源极端子与薄膜晶体管ta2的漏极端子相互连接而构成输出端。以下,将包括该输出端的节点称为“状态节点”。薄膜晶体管ta1的栅极端子相当于置位端子s,薄膜晶体管ta2的栅极端子相当于复位端子r。双稳态电路sr(n)通过向与状态节点na((n)连接的电容(缓冲电路buff((n)内的薄膜晶体管tb的栅极电容等构成的、后述的升压电容cbst)对电荷进行充电或放电而成为两个状态的任一状态。即,若向薄膜晶体管ta1的栅极端子即置位端子s被施加有源信号(高电平的信号),则双稳态电路sr((n)成为置位状态(状态节点na((n)的电压为高电平的状态),若向薄膜晶体管ta2的栅极端子即复位端子r被施加有源信号(高电平的信号),则双稳态电路sr(n)成为复位状态(状态节点na(n)的电压为低电平的状态)。对于图29所示的双稳态电路sr((n),置位端子s连接至第(n

‑

2)行的栅极总线gl(n

‑

2),复位端子r连接至第(n+3)行的栅极总线gl(n+3)。此外,在双稳态电路sr(n)为置位状态时,从其输出端输出有源信号。此处的有源信号是指高电平的信号(也包括通过后述的升压动作而成为比通常的高电平更高的电平的信号)。

12.如图29所示,缓冲电路buff(n)包含作为n沟道型的薄膜晶体管的缓冲晶体管tb、和升压电容器cbst。缓冲晶体管tb的漏极端子被施加有作为与该缓冲电路buff(n)对应的栅极时钟信号的第一栅极时钟信号gck1。缓冲晶体管tb的栅极端子相当于缓冲电路buff((n)的输入端,且连接至上述状态节点na((n)。缓冲晶体管tb的源极端子相当于缓冲电路buff((n)的输出端,经由升压电容器cbst连接至缓冲晶体管tb的栅极端子,并且连接至第n行的栅极总线gl(n)。

13.接着,对交错配置方式的栅极驱动器的构成进行说明。图30是示出由分别配置在栅极总线gl((1)~gl((i)的一端侧和另一端侧的第一栅极驱动器910和第二栅极驱动器

920构成的交错配置方式的栅极驱动器的构成的概略电路图。在使用这种交错配置方式的栅极驱动器的液晶显示装置中,连接到第一栅极驱动器910的栅极总线gl和连接到第二栅极驱动器920的栅极总线gl交替地配置在显示部上。

14.该交错配置方式的栅极驱动器也根据由第一至第四栅极时钟信号gck1~gck4构成的四相的时钟信号进行动作。但是,第一栅极驱动器910基于第一和第三栅极时钟信号gck1和gck3进行动作,并且第二栅极驱动器920基于第二和第四栅极时钟信号gck2和gck4进行动作。第一栅极驱动器910包括第一移位寄存器911和第一输出缓冲部912。第一移位寄存器911具有将从图28所示的第一栅极驱动器900内的移位寄存器901中的i个双稳态电路sr((1)~sr((i)中每隔一个选择的双稳态电路(

……

,sr((n

‑

2),sr((n),sr((n+2),

…

)级联连接的构成。第一输出缓冲部912包含与这些双稳态电路(

……

,sr((n

‑

2),sr((n),sr((n+2),

…

)分别对应的缓冲电路(

…

,buff((n

‑

2),buff((n),buff((n+2),

…

)。第一输出缓冲部912内的各缓冲电路buff基于对应的双稳态电路sr的输出信号和第一栅极时钟信号gck1或第三栅极时钟信号gck3中的任一个,生成要施加到栅极总线gl的扫描信号。另一方面,第二栅极驱动器920包含第二移位寄存器921及第二输出缓冲部922。第二移位寄存器921具有将上述i个双稳态电路sr((1)~sr((i)中的不包含在第一移位寄存器911中的双稳态电路(

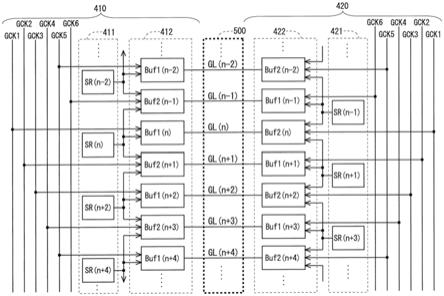

……

、sr((n

‑

1)、sr((n+1)、sr((n+3)

……

)级联连接的构成。第二输出缓冲部922包含与这些双稳态电路(

……

、sr(n

‑

1)、sr(n+1)、sr((n+3)

……

)分别对应的缓冲电路(

……

、buff((n

‑

1)、buff((n+1)、buff((n+3)

……

)。第二输出缓冲部922内的各缓冲电路buff基于对应的双稳态电路sr的输出信号和第二栅极时钟信号gck2或者第四栅极时钟信号gck4中的任一个,生成要施加到栅极总线gl的扫描信号。

15.根据交错配置方式的栅极驱动器,相对于配设于显示部的各栅极总线gl仅从一侧施加扫描信号,因此第一栅极驱动器910和第二栅极驱动器920各自所占的面积变小,能够实现显示装置的窄边框化。另外,根据日本的特开2014

‑

71451号公报所公开的液晶显示装置,构成栅极驱动部的多个级(单位电路)交错配置,并且对于各栅极总线,一端与第一栅极驱动部或第二栅极驱动部内的级连结,另一端与放电电路(放电晶体管)连结。根据这样的构成,能够实现窄边框化,并且设置有辅助栅极总线的放电的放电电路(放电晶体管),因此防止栅极驱动电压的放电延迟(参照同一公报的第0042、0065

‑

0066段落)。

16.然而,在日本的特开2014

‑

71451号公报所公开的液晶显示装置中,辅助栅极总线的放电的放电晶体管在栅极总线的放电开始后开始从截止状态到导通状态的转换,因此不能进行充分高速地放电。另外,在交错配置方式的栅极驱动器中,由于各栅极总线中仅从其一个端部被施加有扫描信号,因此在其另一个端部,扫描信号的波形钝化,对像素电容充电的速度降低。因此,在显示面板的尺寸大的情况下,难以使用交错配置方式的栅极驱动器来显示良好的图像。

17.因此,在日本的特开2019

‑

74560号公报中公开了实现窄边框化以及栅极总线的快速的充放电的液晶显示装置的发明。在该公报的第七实施方式和第八实施方式的栏中,记载了为了实现窄边框化而使多个缓冲电路与一个双稳态电路相关联的构成。另外,将多个缓冲电路与一个双稳态电路相关联这一构成也记载在sid 2018digest的“novel

‑

to

‑

nrchitectureof bidirectional gate driver for ultra

‑

narrow

‑

border display”(p.1223

‑

1226)(作者:zhijun wang,hongtao huang,chao dai,and di xia)中。

技术实现要素:

本发明所要解决的技术问题

18.另外,近年来的显示装置中,也有能够切换栅极驱动器内的移位寄存器中的移位方向(即,切换多条栅极总线的扫描顺序)的装置。然而,在日本特开2019

‑

74560号公报中记载的液晶显示装置不能进行移位方向的切换。另外,根据sid 2018digest的“novel

‑

to

‑

nrchitectureof bidirect ional gate driver for ultra

‑

narrow

‑

border display”中记载的构成,能够进行移位方向的切换,但相当于双稳态电路的“inter

‑

stage transfer unit(级间传输单元)”中包含11个薄膜晶体管,因此窄边框化的效果小。

19.因此,希望实现栅极总线的高速充放电以及栅极总线的扫描顺序的切换为可能的且能够实现窄边框化的显示装置。用于解决问题的方案

20.根据本发明的若干个实施方式的扫描信号线驱动电路,为向配设于显示装置的显示部的多条扫描信号线依次施加导通电平的扫描信号的扫描信号线驱动电路,其包括:第一扫描信号线驱动部,其配置在所述多条扫描信号线的一端侧并基于多相时钟信号进行动作;第二扫描信号线驱动部,其配置在所述多条扫描信号线的另一端侧并基于所述多相时钟信号进行动作;第一控制线,当以升序向所述多条扫描信号线进行导通电平的扫描信号的施加时,提供相当于导通电平的电压,当以降序向所述多条扫描信号线施加导通电平的扫描信号时,提供相当于截止电平的电压;以及第二控制线,当以升序向所述多条扫描信号线进行导通电平的扫描信号的施加时,提供相当于截止电平的电压,当以降序向所述多条扫描信号线施加导通电平的扫描信号时,提供相当于导通电平的电压,所述第一扫描信号线驱动部以及所述第二扫描信号线驱动部的每一个包含:移位寄存器,其包括相互级联连接的多个双稳态电路;多个第一缓冲电路,与所述多个双稳态电路一一对应,且每隔1条分别与多条扫描信号线连接;以及多个第二缓冲电路,分别与未连接到所述多个第一缓冲电路的多条扫描信号线连接,构成所述第一扫描信号线驱动部所包含的所述移位寄存器的所述多个双稳态电路,与第奇数行的多条扫描信号线一一对应,所述第一扫描信号线驱动部所包含的每个第一缓冲电路连接至第奇数行的扫描信号线,所述第一扫描信号线驱动部所包含的每个第二缓冲电路连接至第偶数行的扫描信号线,构成所述第二扫描信号线驱动部所包含的所述移位寄存器的所述多个双稳态电路,与第偶数行的多条扫描信号线一一对应,所述第二扫描信号线驱动部所包含的每个第一缓冲电路连接至第偶数行的扫描信号线,

所述第二扫描信号线驱动部所包含的每个第二缓冲电路连接至第奇数行的扫描信号线,每个第一缓冲电路基于与连接目的地的扫描信号线对应的双稳态电路的输出信号和所提供的时钟信号,向连接目的地的扫描信号线施加导通电平的扫描信号,每个第二缓冲电路基于与相邻于连接目的地的扫描信号线的一方的扫描信号线对应的双稳态电路的输出信号、与相邻于连接目的地的扫描信号线的另一方的扫描信号线对应的双稳态电路的输出信号和所提供的时钟信号,向连接目的地的扫描信号线施加导通电平的扫描信号,将i设为整数,连接到第i行的扫描信号线的所述第一缓冲电路、连接到第(i

‑

1)行的扫描信号线的所述第二缓冲电路以及连接到第(i+1)行的扫描信号线的所述第二缓冲电路被提供有同一双稳态电路的输出信号,并且被提供有所述多相时钟信号中的相位彼此不同的时钟信号,连接至同一扫描信号线的所述第一缓冲电路及所述第二缓冲电路被提供有所述多相时钟信号中的同一时钟信号,将j以及k设为整数,与第k行的扫描信号线对应的双稳态电路包括:第一状态节点,其连接至输出信号的输出目的地的所述第一缓冲电路;第一的第一状态节点控制晶体管,其具有连接至第(k

‑

j)行的扫描信号线的控制端子或被施加有与施加到第(k

‑

j)行的扫描信号线的扫描信号相同相位的波形的信号的控制端子、连接至所述第一控制线的第一导通端子和连接至所述第一状态节点的第二导通端子;以及第二的第一状态节点控制晶体管,其具有连接至第(k+j)行的扫描信号线的控制端子或被施加有与施加到第(k+j)行的扫描信号线的扫描信号相同相位的波形的信号的控制端子、连接至所述第二控制线的第一导通端子和连接至所述第一状态节点的第二导通端子。

21.(2)另外,根据本发明的若干个实施方式的扫描信号线驱动电路包含上述(1)的构成,所述j为等于或大于2的整数,所述多相时钟信号的相数等于或大于(j+2),所述多相时钟信号的脉冲宽度相当于1个水平扫描期间以上且(j

‑

1)个水平扫描期间以下的长度。

22.(3)另外,根据本发明的若干个实施方式的扫描信号线驱动电路包含上述(1)的构成,每个第一缓冲电路包括:第一缓冲晶体管,其具有与对应的双稳态电路所包含的所述第一状态节点连接的控制端子、被施加有对应的时钟信号的第一导通端子和连接至对应的扫描信号线的第二导通端子;以及第一电容器,其一端连接至所述第一缓冲晶体管的控制端子,另一端连接至所述第一缓冲晶体管的第二导通端子。

23.(4)另外,根据本发明的若干个实施方式的扫描信号线驱动电路包含上述(1)的构

成,每个第二缓冲电路包括:第二状态节点;第二缓冲晶体管,其具有连接至所述第二状态节点的控制端子、被施加有对应的的时钟信号的第一导通端子和连接至对应的扫描信号线的第二导通端子;以及第一控制晶体管,其具有连接至所述第二控制线的控制端子、连接至所述第一状态节点的第一导通端子和连接至所述第二状态节点的第二导通端子,其中所述第一状态节点被包含于与相邻于连接目的地的扫描信号线的一方的扫描信号线对应的双稳态电路中,第二控制晶体管,其具有连接至所述第一控制线的控制端子、连接至所述第一状态节点的第一导通端子和连接至所述第二状态节点的第二导通端子,其中所述第一状态节点被包含于与相邻于连接目的地的扫描信号线的另一方的扫描信号线对应的双稳态电路中,第二电容器,其一端连接至所述第二缓冲晶体管的控制端子,另一端连接至所述第二缓冲晶体管的第二导通端子。

24.(5)另外,根据本发明的若干个实施方式的扫描信号线驱动电路包含上述(1)的构成,每个第一缓冲电路包括:第一缓冲晶体管,其具有与对应的双稳态电路所包含的所述第一状态节点连接的控制端子、被施加有对应的时钟信号的第一导通端子和连接至对应的扫描信号线的第二导通端子;以及第一电容器,其一端连接至所述第一缓冲晶体管的控制端子,另一端连接至所述第一缓冲晶体管的第二导通端子,每个第二缓冲电路包括:第二状态节点;第二缓冲晶体管,其具有连接至所述第二状态节点的控制端子、被施加有对应的的时钟信号的第一导通端子和连接至对应的扫描信号线的第二导通端子;以及第一控制晶体管,其具有连接至所述第二控制线的控制端子、连接至所述第一状态节点的第一导通端子和连接至所述第二状态节点的第二导通端子,其中所述第一状态节点被包含于与相邻于连接目的地的扫描信号线的一方的扫描信号线对应的双稳态电路中,第二控制晶体管,其具有连接至所述第一控制线的控制端子、连接至所述第一状态节点的第一导通端子和连接至所述第二状态节点的第二导通端子,其中所述第一状态节点被包含于与相邻于连接目的地的扫描信号线的另一方的扫描信号线对应的双稳态电路中,第二电容器,其一端连接至所述第二缓冲晶体管的控制端子,另一端连接至所述第二缓冲晶体管的第二导通端子,以使所述第一缓冲电路的扫描信号线的驱动能力和所述第二缓冲电路的扫描信号线的驱动能力成为相同程度的方式,进行针对所述第一缓冲晶体管以及所述第二缓冲晶体管的互不相同的尺寸的设定和针对对所述第一电容器以及所述第二电容器的互不相同的电容值的设定。

25.(6)另外,根据本发明的若干个实施方式的显示装置为具有显示部的显示装置,所述显示部设有多条数据信号线、与所述多条数据信号线交叉的多条扫描信号线、沿着所述多条数据信号线以及所述多条扫描信号线配置成矩阵状的多个像素形成部,所述显示装置包括:数据信号线驱动电路,其驱动所述多条数据信号线;如权利要求1至5中任一项所述的扫描信号线驱动电路;以及显示控制电路,其控制所述数据信号线驱动电路以及所述扫描信号线驱动电路。

26.(7)另外,根据本发明的若干个实施方式的显示装置包含上述或上述(6)的构成,所述扫描信号线驱动电路与所述显示部一体地形成于同一基板上。

27.(8)另外,根据本发明的若干个实施方式的(扫描信号线的)驱动方法,为配设于显示装置的显示部的多条扫描信号线的驱动方法,所述显示装置包括:第一扫描信号线驱动部,其配置在所述多条扫描信号线的一端侧并基于多相时钟信号进行动作;第二扫描信号线驱动部,其配置在所述多条扫描信号线的另一端侧并基于所述多相时钟信号进行动作;第一控制线,当以升序向所述多条扫描信号线进行导通电平的扫描信号的施加时,提供相当于导通电平的电压,当以降序向所述多条扫描信号线施加导通电平的扫描信号时,提供相当于截止电平的电压;以及第二控制线,当以升序向所述多条扫描信号线进行导通电平的扫描信号的施加时,提供相当于截止电平的电压,当以降序向所述多条扫描信号线施加导通电平的扫描信号时,提供相当于导通电平的电压,所述第一扫描信号线驱动部以及所述第二扫描信号线驱动部的每一个包含:移位寄存器,包括相互级联连接的多个双稳态电路;多个第一缓冲电路,与所述多个双稳态电路一一对应,且每隔1条分别与多条扫描信号线连接;以及多个第二缓冲电路,分别与未连接到所述多个第一缓冲电路的多条扫描信号线连接,构成所述第一扫描信号线驱动部所包含的所述移位寄存器的所述多个双稳态电路,与第奇数行的多条扫描信号线一一对应,所述第一扫描信号线驱动部所包含的每个第一缓冲电路连接至第奇数行的扫描信号线,所述第一扫描信号线驱动部所包含的每个第二缓冲电路连接至第偶数行的扫描信号线,构成所述第二扫描信号线驱动部所包含的所述移位寄存器的所述多个双稳态电路,与第偶数行的多条扫描信号线一一对应,所述第二扫描信号线驱动部所包含的每个第一缓冲电路连接至第偶数行的扫描信号线,所述第二扫描信号线驱动部所包含的每个第二缓冲电路连接至第奇数行的扫描

信号线,每个第一缓冲电路基于与连接目的地的扫描信号线对应的双稳态电路的输出信号和所提供的时钟信号,向连接目的地的扫描信号线施加导通电平的扫描信号,每个第二缓冲电路基于与相邻于连接目的地的扫描信号线的一方的扫描信号线对应的双稳态电路的输出信号、与相邻于连接目的地的扫描信号线的另一方的扫描信号线对应的双稳态电路的输出信号和所提供的时钟信号,向连接目的地的扫描信号线施加导通电平的扫描信号,将i设为整数,连接到第i行的扫描信号线的所述第一缓冲电路、连接到第(i

‑

1)行的扫描信号线的所述第二缓冲电路以及连接到第(i+1)行的扫描信号线的所述第二缓冲电路被提供有同一双稳态电路的输出信号,并且被提供有所述多相时钟信号中的相位彼此不同的时钟信号,连接至同一扫描信号线的所述第一缓冲电路及所述第二缓冲电路被提供有所述多相时钟信号中的同一时钟信号,将j以及k设为整数,与第k行的扫描信号线对应的双稳态电路包括:第一状态节点,其连接至输出信号的输出目的地的所述第一缓冲电路;第一的第一状态节点控制晶体管,其具有连接至第(k

‑

j)行的扫描信号线的控制端子或被施加有与施加到第(k

‑

j)行的扫描信号线的扫描信号相同相位的波形的信号的控制端子、连接至所述第一控制线的第一导通端子和连接至所述第一状态节点的第二导通端子;以及第二的第一状态节点控制晶体管,其具有连接至第(k+j)行的扫描信号线的控制端子或被施加有与施加到第(k+j)行的扫描信号线的扫描信号相同相位的波形的信号的控制端子、连接至所述第二控制线的第一导通端子和连接至所述第一状态节点的第二导通端子,在以升序向所述多条扫描信号线施加导通电平的扫描信号时,针对所述移位寄存器向初级侧的双稳态电路施加起始脉冲,在以降序向所述多条扫描信号线施加导通电平的扫描信号时,针对所述移位寄存器向最终级侧的双稳态电路施加起始脉冲,在以升序向所述多条扫描信号线施加导通电平的扫描信号时和以降序向所述多条扫描信号线施加导通电平的扫描信号时,关于所述多相时钟信号的时钟脉冲的产生顺序相反,所述驱动方法包含:第一的第一状态节点控制晶体管导通步骤,使所述第一的第一状态节点控制晶体管从截止状态变化为导通状态;第一的第一状态节点控制晶体管截止步骤,使所述第一的第一状态节点控制晶体管从导通状态变化为截止状态;第二的第一状态节点控制晶体管导通步骤,使所述第二的第一状态节点控制晶体管从截止状态变化为导通状态;以及第二的第一状态节点控制晶体管截止步骤,使所述第二的第一状态节点控制晶体管从导通状态变化为截止状态,

在以升序向所述多条扫描信号线进行导通电平的扫描信号的施加时,以所述第一的第一状态节点控制晶体管导通步骤、所述第一的第一状态节点控制晶体管截止步骤、所述第二的第一状态节点控制晶体管导通步骤以及所述第二的第一状态节点控制晶体管截止步骤的顺序进行处理,在以降序向所述多条扫描信号线进行导通电平的扫描信号的施加时,以所述第二的第一状态节点控制晶体管导通步骤、所述第二的第一状态节点控制晶体管截止步骤、所述第一的第一状态节点控制晶体管导通步骤以及所述第一的第一状态节点控制晶体管截止步骤的顺序进行处理。发明效果

28.根据本发明的若干个实施方式的扫描信号线驱动电路,配设于显示装置的显示部的各扫描信号线由第一扫描信号线驱动部和第二扫描信号线驱动部驱动。即,各扫描信号线中,从其两端施加有导通电平或截止电平的电压作为扫描信号。由此,由于能够对各扫描信号线高速地进行充电以及放电,因此对于尺寸大的显示部也能够通过高速地驱动而良好地显示图像。此处,第一扫描信号线驱动部内的移位寄存器由与第奇数行的扫描信号线对应的双稳态电路构成,第二扫描信号线驱动部内的移位寄存器由与第偶数行的扫描信号线对应的双稳态电路构成。而且,根据各双稳态电路的输出信号来控制两个缓冲电路(第一及第二缓冲电路)的动作。通过如以上的构成,能够降低实现移位寄存器所需的面积,实现窄边框化。另外,将j和k设为整数,与第k行的扫描信号线对应的双稳态电路包含有:第一状态节点,其连接至输出信号的输出目的地的第一缓冲电路;第一的第一状态节点控制晶体管,其具有连接至第(k

‑

j)行的扫描信号线的控制端子、连接至第一控制线的第一导通端子和连接至第一状态阶段的第二导通端子;以及第二的第一状态节点控制晶体管,其具有连接至第(k+j)行的扫描信号线的控制端子、连接至第二控制线的第一导通端子和连接至第一状态阶段的第二导通端子。此处,当以升序向多条扫描信号线施加导通电平的扫描信号时,向第一控制线施加相当于导通电平的电压的同时向第二控制线施加相当于截止电平的电压,当以降序向多条扫描信号线施加导通电平的扫描信号时,向第一控制线施加相当于截止电平的电压的同时向第二控制线施加相当于导通电平的电压。另外,第二缓冲电路构成为基于与相邻于连接目的地的扫描信号线的一方的扫描信号线对应的双稳态电路的输出信号、与相邻于连接目的地的扫描信号线的另一方的扫描信号线对应的双稳态电路的输出信号、以及时钟信号,向连接目的地的扫描信号线施加导通电平的扫描信号。根据以上的构成,当对移位寄存器向初级侧的双稳态电路施加起始脉冲时,进行正向扫描,当对移位寄存器向最终级侧的双稳态电路施加起始脉冲时,进行反向扫描。这样,能够进行扫描信号线的扫描顺序的切换。如上所述,实现一种扫描信号线的高速地充放电和扫描信号线的扫描顺序的切换为可能的且能够实现窄边框化的显示装置。

附图说明

29.图1是示出在一实施方式中的栅极驱动器的整体构成的概略电路图。图2是示出上述第一实施方式涉及的有源矩阵型的液晶显示装置的整体构成的框图。图3是示出在上述第一实施方式中,显示部内的一个像素形成部的电构成的电路

图。图4是示出在上述实施方式中,第一栅极驱动器的构成的电路图。图5是示出在上述实施方式中,第二栅极驱动器的构成的电路图。图6是示出在上述实施方式中,双稳态电路的详细构成的电路图。图7是示出在上述实施方式中,连接到第n行的栅极总线的缓冲电路(第一缓冲电路及第二缓冲电路)的详细构成的电路图。图8是示出在上述实施方式中,用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。图9是关于上述实施方式的、通过模拟得到的正向扫描时的信号波形图。图10是示出在上述实施方式中,用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。图11是关于上述实施方式的、通过模拟得到的反向扫描时的信号波形图。图12是示出在第一变形例中,双稳态电路的详细构成的电路图。图13是用于说明在上述第一变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图14是用于说明在上述第一变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图15是用于说明在第二变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图16是用于说明在上述第二变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图17是用于说明在第三变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图18是用于说明在上述第三变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图19是示出在第四变形例中,双稳态电路的详细构成的电路图。图20是用于说明在上述第四变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图21是用于说明在上述第四变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图22是用于说明在第五变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图23是用于说明在上述第五变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图24是用于说明在第六变形例中,进行正向扫描时的栅极驱动器的动作的信号波形图。图25是用于说明在上述第六变形例中,进行反向扫描时的栅极驱动器的动作的信号波形图。图26是用于说明现有例中涉及的双侧输入方法的图。

图27是用于说明现有例中涉及的单侧输入方法的图。图28是示出现有例中涉及的、采用了双侧输入方式的情况下的第一栅极驱动器的构成的概略电路图。图29是示出现有例中涉及的、在第一栅极驱动器中与一条栅极总线对应的电路(单位电路)的构成的电路图。图30是示出现有例中涉及的、由分别配置在栅极总线的一端侧和另一端侧的第一栅极驱动器和第二栅极驱动器构成的交错配置方式的栅极驱动器的构成的概略电路图。

具体实施方式

30.以下,一边参照附图一边说明一实施方式。此外,关于以下提及的各晶体管,栅极端子相当于控制端子,漏极端子和源极端子中的一方相当于第一导通端子,另一方相当于第二导通端子。另外,本实施方式中的晶体管假设全部为n沟道型的薄膜晶体管,但本发明并不限定于此。

31.<1.整体构成以及动作概要>图2是示出一实施方式涉及的有源矩阵型的液晶显示装置的整体构成的框图。该液晶显示装置具备显示控制电路200、源极驱动器(数据信号线驱动电路)300和液晶面板600。液晶面板600中包含有由第一栅极驱动器410和第二栅极驱动器420构成的栅极驱动器(扫描信号线驱动电路)和显示部500。如图2所示,第一栅极驱动器410和第二栅极驱动器420以隔着显示部500相对的方式配置。在本实施方式中,在构成液晶面板600的两块基板中的一块基板(有源矩阵基板)上一体地形成有构成显示部500的像素电路和栅极驱动器。此外,由第一栅极驱动器410实现第一扫描信号线驱动部,由第二栅极驱动器420实现第二扫描信号线驱动部。

32.在显示部500上设置有:作为多条(j条)数据信号线的源极总线sl(1)~sl(j);作为与该多条源极总线sl(1)~sl(j)交叉的多条(i条)扫描信号线的栅极总线gl(1)~gl(i);以及沿着该多条源极总线sl(1)~sl(j)和该多条栅极总线gl(1)~gl(i)配置成矩阵状的多个(i

×

j个)像素形成部ps。各像素形成部ps与该多条源极总线sl(1)~sl(j)中的任一条对应,并且与该多条栅极总线gl(1)~gl(i)中的任一条对应。此外,液晶面板600的方式也不限于对液晶层在垂直方向上施加电场的va(vertical alignment:垂直取向)方式、tn(twisted nematic:扭曲向列)方式等,也可以是对液晶层在大致平行方向上施加电场的ips(in

‑

plane switching:面内开关)方式。

33.另外,在本实施方式涉及的液晶显示装置中,能够切换栅极驱动器内的移位寄存器中的移位方向(切换多条栅极总线gl的扫描顺序)。关于此,在以下的说明中,将以“第一行、第二行、

……

、第(i

‑

1)行、第i行”的顺序进行栅极总线gl的扫描称为“正向扫描”,将以“第i行、第(i

‑

1)行、

……

、第二行、第一行”的顺序进行栅极总线gl的扫描称为“反向扫描”。

34.图3是示出显示部500内的一个像素形成部ps(n,m)的电构成的电路图。如图3所示,像素形成部ps(n,m)由如下构成:薄膜晶体管10,其栅极端子与通过对应的交叉点的栅极总线gl(n)连接,并且源极端子与通过该交叉点的源极总线sl(m)连接;像素电极ep,其与该薄膜晶体管10的漏极端子连接;共用电极ec,其是共用地设置于上述多个像素形成部ps的相对电极;以及液晶层,其被夹持在共用地设置于上述多个像素形成部ps的像素电极ep

与共用电极ec之间。并且,利用由像素电极ep和共用电极ec形成的液晶电容clc构成像素电容cp。此外,通常来说,为了将电荷可靠地保持于像素电容cp而与液晶电容clc并联地设有辅助电容,但是辅助电容与本发明没有直接关系,因此省略其说明和图示。在液晶面板600为ips方式的情况下,共用电极ec形成于构成液晶面板600的两块基板中的上述一块基板(有源矩阵基板)上。在液晶面板600为va方式等的情况下,共用电极ec形成于构成液晶面板600的两块基板中的另一块基板上。

35.作为像素形成部ps内的薄膜晶体管10,能够采用在沟道层中使用了非晶硅的薄膜晶体管(a

‑

si tft)、在沟道层中使用了微晶硅的薄膜晶体管、在沟道层中使用了氧化物半导体的薄膜晶体管(氧化物tft)、在沟道层中使用了低温多晶硅的薄膜晶体管(ltps

‑

tft)等。作为氧化物tft,例如可采用具有包含in

‑

ga

‑

zn

‑

o类的半导体(例如氧化铟镓锌)的氧化物半导体层的薄膜晶体管。关于这些方面,对于第一栅极驱动器410及第二栅极驱动器420内的薄膜晶体管来说也是同样的。

36.显示控制电路200接收从外部施加的图像信号dat以及定时控制信号tg,输出数字视频信号dv、用于控制源极驱动器300的动作的源极控制信号sct、用于控制第一栅极驱动器410的动作的第一栅极控制信号gct1以及用于控制第二栅极驱动器420的动作的第二栅极控制信号gct2。源极控制信号sct包含有源极起始脉冲信号、源极时钟信号以及锁存选通信号。第一栅极控制信号gct1包含有正向扫描用的栅极起始脉冲信号、反向扫描用的栅极起始脉冲信号、相位彼此不同的第一至第六栅极时钟信号gck1至gck6、以及用于控制位移方向的信号(后述的第一及第二位移方向控制信号uda、udb)。对于第二栅极控制信号gct2而言,与第一栅极控制信号gct1相同。

37.基于从显示控制电路200发送来的数字视频信号dv和源极控制信号sct,源极驱动器300分别将数据信号d(1)至d(j)施加到源极总线sl(1)至sl(j)。此时,源极驱动器300中,在源极时钟信号的脉冲产生的时刻,表示要施加到各源极总线sl的电压的数字视频信号dv被依次保持。并且,在锁存选通信号的脉冲产生的时刻,上述保持的数字视频信号dv被转换为模拟电压。该转换后的模拟电压作为数据信号d(1)~d(j)被同时施加到所有源极总线sl(1)~sl(j)。

38.第一栅极驱动器410配置于栅极总线gl(1)~gl(i)的一端侧,并基于从显示控制电路200发送来的第一栅极控制信号gct1分别对栅极总线gl(1)~gl(i)的一端侧施加扫描信号g(1)~g(i)。另一方面,第二栅极驱动器420配置于栅极总线gl(1)~gl(i)的另一端侧,并基于从显示控制电路200发送来的第二栅极控制信号gct2分别对栅极总线gl(1)~gl(i)的另一端侧施加扫描信号g(1)~g(i)。由此,在各帧期间内,从两端向栅极总线gl(1)~gl(i)依次施加有源扫描信号。这样的对栅极总线gl(1)~gl(i)施加有源扫描信号,以1帧期间(1垂直扫描期间)为周期重复进行。

39.如上所述,向源极总线sl(1)~sl(j)施加数据信号d(1)~d(j),向栅极总线gl(1)~gl(i)施加扫描信号g(1)~g(i)。由此,基于数字视频信号dv的像素数据被写入各像素形成部ps。

40.另外,液晶面板600的背面侧设有未图示的背光源单元。由此,背光被照射到液晶面板600的背面。该背光单元也通过显示控制电路200驱动,但也可以是通过其他方法驱动的构成。此外,在显示面板600为反射型的情况下,不需要背光源单元。

41.如上所述,基于数字视频信号(dv)的像素数据被写入各像素形成部ps,并且背光被照射到液晶面板600的背面,从而将从外部施加的图像信号dat所表示的图像显示在显示部500上。

42.<2.栅极驱动器><2.1栅极驱动器的整体构成>图1是示出本实施方式中的栅极驱动器的整体构成的概略电路图。此外,图1仅示出了与第(n

‑

2)~(n+4)行的栅极总线gl(n

‑

2)~gl(n+4)对应的构成要素。该栅极驱动器由配置于栅极总线gl(1)~gl(i)的一端侧(图1中的左侧)的第一栅极驱动器410、和配置于栅极总线gl(1)~gl(i)的另一端侧(图1中的右侧)的第二栅极驱动器420构成。第一栅极驱动器410和第二栅极驱动器420均基于由第一至第六栅极时钟信号gck1~gck6构成的6相时钟信号进行动作。

43.第一栅极驱动器410包含第一移位寄存器411及第一扫描信号输出部412。第一移位寄存器411具有将与(i/2)条的第奇数行的栅极总线gl一一对应的(i/2)个双稳态电路sr级联连接的构成。第一扫描信号输出部412包括:(i/2)个第一缓冲电路buf1,分别连接至(i/2)条的第奇数行的栅极总线gl;(i/2)个第二缓冲电路buf2,分别连接至(i/2)条的第偶数行的栅极总线gl。

44.第二栅极驱动器420包含第二移位寄存器421和第二扫描信号输出部422。第二移位寄存器421具有将与(i/2)条的第偶数行的栅极总线gl一一对应的(i/2)个双稳态电路sr级联连接的构成。第二扫描信号输出部422包括:(i/2)个第一缓冲电路buf1,分别连接至(i/2)条的第偶数行的栅极总线gl;(i/2)个第二缓冲电路buf2,分别连接至(i/2)条的第奇数行的栅极总线gl。

45.此外,各双稳态电路sr和各第二缓冲电路buf2也连接至分别提供用于控制移位方向(多条栅极总线的扫描顺序)的第一及第二偏移方向控制信号的第一及第二偏移方向控制线(图1中未示出)。对第一偏移方向控制信号和第一偏移方向控制线附加相同的附图标记uda,对第二偏移方向控制信号和第二偏移方向控制线附加相同的附图标记udb。在本实施方式中,通过第一偏移方向控制线uda实现第一控制线,通过第二偏移方向控制线udb实现第二控制线。

46.在本实施方式中的栅极驱动器中,与图30所示的现有的栅极驱动器不同,第一移位寄存器411及第二移位寄存器421中的来自各双稳态电路sr的输出信号控制1个第一缓冲电路buf1及2个第二缓冲电路buf2的动作。与此相关,在第一栅极驱动器410中,例如,来自与第n行的栅极总线gl(n)对应的双稳态电路sr(n)的输出信号被施加到与第(n

‑

1)行的栅极总线gl(n

‑

1)连接的第二缓冲电路buf2(n

‑

1)、与第n行的栅极总线gl(n)连接的第一缓冲电路buf1(n)、以及与第(n+1)行的栅极总线gl(n+1)连接的第二缓冲电路buf2(n+1)。另外,在第二栅极驱动器420中,例如,来自与第(n

‑

1)行的栅极总线gl(n

‑

1)对应的双稳态电路sr(n

‑

1)的输出信号被施加到与第(n

‑

2)行的栅极总线gl(n

‑

2)连接的第二缓冲电路buf2(n

‑

2)、与第(n

‑

1)行的栅极总线gl(n

‑

1)连接的第一缓冲电路buf1(n

‑

1))、以及与第n行的栅极总线gl(n)连接的第二缓冲电路buf2(n)。

47.关于6相时钟信号,在第一栅极驱动器410中,向第一缓冲电路buf1施加第一栅极时钟信号gck1、第三栅极时钟信号gck3以及第五栅极时钟信号gck5中的任一个,向第二缓

冲电路buf2施加第二栅极时钟信号gck2、第四栅极时钟信号gck4以及第六栅极时钟信号gck6中的任一个。在第二栅极驱动器420中,向第一缓冲电路buf1施加第二栅极时钟信号gck2、第四栅极时钟信号gck4以及第六栅极时钟信号gck6中的任一个,向第二缓冲电路buf2施加第一栅极时钟信号gck1、第三栅极时钟信号gck3以及第五栅极时钟信号gck5中的任一个。另外,如图1所示,向与同一栅极总线gl连接的第一缓冲电路buf1及第二缓冲电路buf2提供上述6相时钟信号中的同一时钟信号。进一步地,如图1所示,向被施加有同一双稳态电路sr的输出信号的第一缓冲电路buf1及第二缓冲电路buf2提供上述6相时钟信号中的相位彼此不同的时钟信号。详细而言,将i设为整数,向连接到第i行的栅极总线gl(i)的第一缓冲电路buf1(i)、连接到第(i

‑

1)行的栅极总线gl(i

‑

1)的第二缓冲电路buf2(i

‑

1)和连接到第(i+1)行的栅极总线gl(i+1)的第二缓冲电路buf2(i+1)提供上述六相时钟信号中的相位彼此不同的时钟信号。

48.每个第一缓冲电路buf1基于与连接目的地的栅极总线gl对应的双稳态电路sr的输出信号和对应的栅极时钟信号gckk(k为1~6中的任一个),生成要施加到连接目的地的栅极总线gl的扫描信号g。每个第二缓冲电路buf2基于与相邻于连接目的地的栅极总线gl的一方的栅极总线gl对应的双稳态电路sr的输出信号、与相邻于连接目的地的栅极总线gl的另一方的栅极总线gl对应的双稳态电路sr的输出信号以及对应的栅极时钟信号gckk(k为1~6中的任一个),生成要施加到连接目的地的栅极总线gl的扫描信号g。

49.另外,若着眼于任意的栅极总线gl,则一个端部连接至第一缓冲电路buf1,另一个端部连接至第二缓冲电路buf2。由此,各栅极总线gl的充电及放电通过第一缓冲电路buf1从一个端部进行的同时,通过第二缓冲电路buf2从另一个端部进行。

50.此外,为了使第一移位寄存器411中所包含的双稳态电路和第二移位寄存器421中所包含的双稳态电路实际作为移位寄存器而动作,需要根据栅极时钟信号的相数等在初级的双稳态电路之前和最终级的双稳态电路之后设置伪双稳态电路。然而,对于本领域技术人员来说,与此相关的具体构成是显而易见的,因此省略其说明。

51.<2.2栅极驱动器的详细构成>参照图4至图7,并着眼于与第n行的栅极总线gl(n)对应的结构要素,对本实施方式中的栅极驱动器的详细构成进行说明。

52.如图4所示,在第一栅极驱动器410中,栅极总线gl(n)连接至第一缓冲电路buf1(n)。第一缓冲电路buf1(n)被施加有第一栅极时钟信号gck1和双稳态电路sr(n)的输出信号。对第一缓冲电路buf1(n)施加输出信号的双稳态电路sr(n)也对连接到第(n

‑

1)行的栅极总线gl(n

‑

1)的第二缓冲电路buf2(n

‑

1)和连接到第(n+1)行的栅极总线gl(n+1)的第二缓冲电路buf2(n+1)施加输出信号。

53.如图5所示,在第二栅极驱动器420中,栅极总线gl(n)连接至第二缓冲电路buf2(n)。第二缓冲电路buf2(n)被施加有第一栅极时钟信号gck1、与第(n

‑

1)行的栅极总线gl(n

‑

1)对应的双稳态电路sr(n

‑

1)的输出信号和与第(n+1)行的栅极总线gl(n+1)对应的双稳态电路sr(n+1)的输出信号。

54.图6是示出与第n行的栅极总线gl(n)对应的双稳态电路sr(n)的详细构成的电路图。此外,与第n行以外的栅极总线gl对应的双稳态电路sr的构成也是同样的。该双稳态电路sr(n)包含有两个n沟道型薄膜晶体管ta、tb。对于薄膜晶体管ta,作为输入端子46的栅极

端子连接至第(n

‑

3)行的栅极总线gl(n

‑

3),漏极端子连接至第一移位方向控制线uda,源极端子连接至第一状态节点n1(n)。对于薄膜晶体管tb,作为输入端子47的的栅极端子连接至第(n+3)行的栅极总线gl(n+3),漏极端子连接至第二移位方向控制线udb,源极端子连接至第一状态节点n1(n)。此外,第一状态节点n1(n)为包含该双稳态电路sr(n)的输出端的节点。

55.在本实施方式中,由薄膜晶体管ta实现第一的第一状态节点控制晶体管,由薄膜晶体管tb实现第二的第一状态节点控制晶体管。

56.图7是示出连接至第n行的栅极总线gl(n)的缓冲电路(第一缓冲电路buf1(n)和第二缓冲电路buf2(n))的详细构成的电路图。

57.第一缓冲电路buf1(n)包含有n沟道型薄膜晶体管t1和升压电容器c1。对于薄膜晶体管t1,栅极端子连接至第一状态节点n1(n),漏极端子被施加有第一栅极时钟信号gck1,源极端子连接至栅极总线gl(n)。对于升压电容器c1,其一端连接至薄膜晶体管t1的栅极端子,另一端连接至薄膜晶体管t1的源极端子。此外,升压电容器c1并非必须的构成要素,可以仅设于必要的情况下。对于此,后述的升压电容器c2也是同样的。

58.第二缓冲电路buf2(n)包含有三个n沟道型的薄膜晶体管t2、t3a、t3b和升压电容器c2。对于薄膜晶体管t2,栅极端子连接至第二状态节点n2(n),漏极端子被施加有第一栅极时钟信号gck1,源极端子连接至栅极总线gl(n)。对于薄膜晶体管t3a,栅极端子连接至第二位移方向控制线udb,漏极端子连接至第一状态节点n1(n

‑

1),其中该第一状态节点n1(n

‑

1)被包含于与第(n

‑

1)行的栅极总线gl(n

‑

1)对应的双稳态电路sr(n

‑

1)中,源极端子连接至第二状态节点n2(n)。对于薄膜晶体管t3b,栅极端子连接至第一位移方向控制线uda,漏极端子连接至第一状态节点n1(n+1),源极端子连接至第二状态节点n2(n),其中该第一状态节点n1(n+1)被包含于与第(n+1)行的栅极总线gl(n+1)对应的双稳态电路sr(n

‑

1)中。对于升压电容器c2,其一端连接至薄膜晶体管t2的栅极端子,另一端连接至薄膜晶体管t2的源极端子。

59.在本实施方式中,由薄膜晶体管t1实现第一缓冲晶体管,由升压电容器c1实现第一电容器,由薄膜晶体管t2实现第二缓冲晶体管,由升压电容器c2实现第二电容器,由薄膜晶体管t3a实现第二控制晶体管,由薄膜晶体管t3b实现第三缓冲晶体管。

60.此外,关于图6所示的构成,可以对薄膜晶体管ta的栅极端子(输入端子46)施加与对第(n

‑

3)行的栅极总线gl(n

‑

3)施加的扫描信号g(n

‑

3)相同相位的波形的信号,也可以对薄膜晶体管tb的栅极端子(输入端子47)施加与对第(n+3)行的栅极总线gl(n+3)施加的扫描信号g(n+3)相同相位的波形的信号。在该情况下,例如,针对第一缓冲电路buf1或第二缓冲电路buf2的至少一个,采用分为用于驱动栅极总线gl的缓冲和生成施加给图6所示的双稳态电路的信号的缓冲的构成。

61.<2.3栅极驱动器的动作>接着,参照图1以及图6至图11,说明本实施方式中的栅极驱动器的动作。此外,关于第一移位方向控制线uda和第二移位方向控制线udb,高电平时的电压为高电平电源电压vdd,低电平时的电压为低电平电源电压vss。

62.<2.3.1正向扫描时的动作>图8是用于对进行正向扫描时(以升序向多个栅极总线gl施加高电平的扫描信号g

时)的栅极驱动器的动作进行说明的信号波形图。此处,着眼于第n行的栅极总线gl(n)处于选择状态的期间附近的动作。

63.在进行正向扫描时,对第一移位寄存器411和第二移位寄存器421施加正向扫描用的起始脉冲(栅极起始脉冲信号)。即,针对第一移位寄存器411和第二移位寄存器421,对初级侧的双稳态电路sr施加起始脉冲。另外,如图8所示,关于6相时钟信号,按“第一栅极时钟信号gck1、第二栅极时钟信号gck2、第三栅极时钟信号gck3、第四栅极时钟信号gck4、第五栅极时钟信号gck5、第六栅极时钟信号gck6”的顺序生成时钟脉冲。另外,第一移位方向控制线uda维持在高电平,第二移位方向控制线udb维持在低电平。

64.在时刻t00以前的期间中,第一状态节点n1(n

‑

1)、第一状态节点n1(n)、第二状态节点n2(n)以及第一状态节点n1(n+1)的电压均被维持在低电平。

65.当达到时刻t00,扫描信号g(n

‑

4)(图8中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n

‑

1)中,薄膜晶体管ta处于导通状态,第一状态节点n1(n

‑

1)的电压从低电平变化为高电平。此时,第二移位方向控制线udb被维持在低电平,因此第二缓冲电路buf2(n)内的薄膜晶体管t3a处于截止状态。因此,即使第一状态节点n1(n

‑

1)的电压从低电平变为高电平,第二状态节点n2(n)的电压也保持在低电平。

66.此外,时刻t00~t03中的第一状态节点n1(n

‑

1)的电压电平是比高电平电源电压vdd低了薄膜晶体管ta的阈值电压的电压电平。以下,将这样的电压电平称为“预充电电压电平”。此外,第二缓冲电路buf2(n)内的薄膜晶体管t3a的阈值电压的大小为:如果漏极端子的电压电平和源极端子的电压电平超过预充电电压电平,则该薄膜晶体管t3a变为截止状态。同样地,第二缓冲电路buf2(n)内的薄膜晶体管t3b的阈值电压的大小为:如果漏极端子的电压电平和源极端子的电压电平超过预充电电压电平,则该薄膜晶体管t3b变为截止状态。

67.当达到时刻t01,扫描信号g(n

‑

3)从低电平变化为高电平。由此,在双稳态电路sr(n)中,薄膜晶体管ta处于导通状态。由于薄膜晶体管ta的漏极端子与第一移位方向控制线uda连接,因此,由于薄膜晶体管ta处于导通状态,第一状态节点n1(n)的电压从低电平变化为高电平(预充电电压电平)。此时,由于施加给第一缓冲电路buf1(n)内的薄膜晶体管t1的漏极端子的第一栅极时钟信号gck1为低电平,因此扫描信号g(n)被维持在低电平。

68.当达到时刻t02,扫描信号g(n

‑

2)(图8中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n+1)中,薄膜晶体管ta处于导通状态,第一状态节点n1(n+1)的电压从低电平变化为预充电电压电平。此时,第一移位方向控制线uda被维持在高电平,因此第二缓冲电路buf2(n)内的薄膜晶体管t3b处于导通状态。因此,伴随着第一状态节点n1(n+1)的电压从低电平变化为预充电电压电平,第二状态节点n2(n)的电压也从低电平变化为预充电电压电平。

69.当达到时刻t03,扫描信号g(n

‑

3)从高电平变化为低电平。由此,在双稳态电路sr(n)中,薄膜晶体管ta处于截止状态。另外,在时刻t03,通过使第六栅极时钟信号gck6从低电平变化为高电平,基于与第(n

‑

1)行的栅极总线gl(n

‑

1)连接的第一缓冲电路buf1(n

‑

1)中的升压动作,第一状态节点n1(n

‑

1)的电压进一步上升。

70.当达到时刻t04,第一栅极时钟信号gck1从低电平变化为高电平。由此,在第一缓冲电路buf1(n)中,经由薄膜晶体管t1的第n行的栅极总线gl(n)的充电开始。此时,该栅极

总线gl(n)的电压变化(即,扫描信号g(n)的电压变化)经由升压电容器c1提升第一状态节点n1(n)的电压。通过这样的升压动作,向薄膜晶体管t1的栅极端子施加与通常的高电平相比充分高的电压。其结果,薄膜晶体管t1完全处于导通状态,第n行的栅极总线gl(n)从一端侧(图1中的左侧)充电至完全的高电平。

71.如图7所示,第一栅极时钟信号gck1也被施加到第二缓冲电路buf2(n)。详细而言,第一栅极时钟信号gck1被施加给第二缓冲电路buf2(n)内的薄膜晶体管t2的漏极端子。另外,在时刻t04紧前的时间点,第二状态节点n2(n)的电压变为预充电电压电平。因此,在时刻t04,在第二缓冲电路buf2(n)中,经由薄膜晶体管t2的第n行的栅极总线gl(n)的充电开始。此时,该栅极总线gl(n)的电压变化经由升压电容器c2提升第二状态节点n2(n)的电压。由此,向薄膜晶体管t2的栅极端子施加与通常的高电平相比充分高的电压。其结果,薄膜晶体管t2完全处于导通状态,第n行的栅极总线gl(n)从另一端侧(图1中的右侧)充电至完全的高电平。

72.在时刻t05,通过第六栅极时钟信号gck6从高电平变化为低电平,第一状态节点n1(n

‑

1)的电压降低至预充电电压电平。此时,薄膜晶体管t3a处于截止状态,第二状态节点n2(n)的电压不变化。另外,在时刻t05,通过使第二栅极时钟信号gck2从低电平变化为高电平,基于与第(n+1)行的栅极总线gl(n+1)连接的第一缓冲电路buf1(n+1)中的升压动作,第一状态节点n1(n+1)的电压进一步上升。如上所述,薄膜晶体管t3b具有当漏极端子的电压电平和源极端子的电压电平超过预充电电压电平时处于截止状态的阈值电压,因此此时,薄膜晶体管t3b处于截止状态,第二状态节点n2(n)的电压不变化。

73.在时刻t06,第一栅极时钟信号gck1从高电平变化为低电平。由此,第n行的栅极总线gl(n)的电荷经由第一缓冲电路buf1(n)内的薄膜晶体管t1从上述一端侧(图1中的左侧)放电,并且也经由第二缓冲电路buf2(n)内的薄膜晶体管t2从上述另一端侧(图1中的右侧)放电。其结果,扫描信号g(n)的电压高速下降到低电平。这样,在时刻t04变为选择状态的第n行的栅极总线gl(n)在时刻t06迅速地向非选择状态变化。

74.如上所述,在时刻t06,扫描信号g(n)的电压从高电平变化为低电平。由此,经由第一缓冲电路buf1(n)内的升压电容器c1,第一状态节点n1(n)的电压下降;经由第二缓冲电路buf2(n)内的升压电容器c2,第二状态节点n2(n)的电压下降。

75.另外,当达到时刻t06,扫描信号g(n+2)(图8中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n

‑

1)中,薄膜晶体管tb处于导通状态,因此第一状态节点n1(n

‑

1)的电压降低到低电平。

76.当达到时刻t07,扫描信号g(n+3)从低电平变化为高电平。由此,在双稳态电路sr(n)中,薄膜晶体管tb处于导通状态。由于薄膜晶体管tb的漏极端子与第二移位方向控制线udb连接,因此,薄膜晶体管tb处于导通状态,从而第一状态节点n1(n)的电压降低至低电平。

77.当达到时刻t08,扫描信号g(n+4)(图8中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n+1)中,薄膜晶体管tb处于导通状态,因此第一状态节点n1(n+1)的电压降低到低电平。此时,第二缓冲电路buf2(n)内的薄膜晶体管t3b处于导通状态,第二状态节点n2(n)的电压也降低到低电平。

78.当达到时刻t09,扫描信号g(n+3)从低电平变化为高电平。由此,在双稳态电路sr

(n)中,薄膜晶体管tb处于导通状态。

79.此外,在这个示例中,通过时刻t01的动作实现第一的第一状态节点控制晶体管导通步骤,通过时刻t03的动作实现第一的第一状态节点控制晶体管截止步骤,通过时刻t07的动作实现第二的第一状态节点控制晶体管导通步骤,通过时刻t09的动作实现第二的第一状态节点控制晶体管截止步骤。

80.图9是通过模拟得到的正向扫描时的信号波形图。所有的波形都是横轴为时间,纵轴为电压。第一状态节点n1(n)的电压变化及第二状态节点n2(n)的电压变化不依赖于第一状态节点n1(n

‑

1)的电压变化。若着眼于第一状态节点n1(n)和第二状态节点n2(n)的电压,则在第一状态节点n1(n)的电压从低电平变化为预充电电压电平后,第二状态节点n2(n)的电压从低电平变化为预充电电压电平。并且,第一状态节点n1(n)以及第二状态节点n2(n)在相同期间(附加了附图标记61的箭头所示的期间)被维持为与通常的高电平相比充分高的电压。之后,在第一状态节点n1(n)的电压从预充电电压电平变化为低电平后,第二状态节点n2(n)的电压从预充电电压电平变化为低电平。此处,第二状态节点n2(n)的电压在与第一状态节点n1(n+1)的电压相同的定时从低电平向预充电电压电平变化,另外,第二状态节点n2(n)的电压在与第一状态节点n1(n+1)的电压相同的定时从预充电电压电平向低电平变化。即,第二状态节点n2(n)的电压变化依赖于第一状态节点n1(n+1)的电压变化。

81.<2.3.2反向扫描时的动作>图10是用于对进行反向扫描时(以降序向多个栅极总线gl施加高电平的扫描信号g时)的栅极驱动器的动作进行说明的信号波形图。此处,也着眼于第n行的栅极总线gl(n)处于选择状态的期间附近的动作。

82.在进行反向扫描时,对第一移位寄存器411和第二移位寄存器421施加反向扫描用的起始脉冲(栅极起始脉冲信号)。即,针对第一移位寄存器411和第二移位寄存器421,对最终级侧的双稳态电路sr施加起始脉冲。另外,如图10所示,关于6相时钟信号,按“第六栅极时钟信号gck6、第五栅极时钟信号gck5、第四栅极时钟信号gck4、第三栅极时钟信号gck3、第二栅极时钟信号gck2、第一栅极时钟信号gck1”的顺序生成时钟脉冲。另外,第一移位方向控制线uda维持在低电平,第二移位方向控制线udb维持在高电平。

83.在时刻t10以前的期间中,第一状态节点n1(n

‑

1)、第二状态节点n2(n)、第一状态节点n1(n)及第一状态节点n1(n+1)的电压均被维持在低电平。

84.当达到时刻t10,扫描信号g(n+4)(图10中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n+1)中,薄膜晶体管tb处于导通状态,第一状态节点n1(n+1)的电压从低电平变化为高电平。此时,第一移位方向控制线uda被维持在低电平,因此第二缓冲电路buf2(n)内的薄膜晶体管t3b处于截止状态。因此,即使第一状态节点n1(n+1)的电压从低电平变化为高电平,第二状态节点n2(n)的电压也保持在低电平。

85.当达到时刻t11,扫描信号g(n+3)从低电平变化为高电平。由此,在双稳态电路sr(n)中,薄膜晶体管tb处于导通状态。由于薄膜晶体管tb的漏极端子与第二移位方向控制线udb连接,因此,由于薄膜晶体管tb处于导通状态,第一状态节点n1(n)的电压从低电平变化为高电平(预充电电压电平)。此时,由于施加给第一缓冲电路buf1(n)内的薄膜晶体管t1的漏极端子的第一栅极时钟信号gck1为低电平,因此扫描信号g(n)被维持在低电平。

86.当达到时刻t12,扫描信号g(n+2)(图10中未图示)从低电平变化为高电平。由此,

在双稳态电路sr(n

‑

1)中,薄膜晶体管tb处于导通状态,第一状态节点n1(n

‑

1)的电压从低电平变化为预充电电压电平。此时,第二移位方向控制线udb被维持在高电平,因此第二缓冲电路buf2(n)内的薄膜晶体管t3a处于导通状态。因此,伴随着第一状态节点n1(n

‑

1)的电压从低电平变化为预充电电压电平,第二状态节点n2(n)的电压也从低电平变化为预充电电压电平。

87.当达到时刻t13,扫描信号g(n+3)从低电平变化为高电平。由此,在双稳态电路sr(n)中,薄膜晶体管tr2处于导通状态。另外,当达到时刻t13,通过使第二栅极时钟信号gck2从低电平变化为高电平,基于与第(n+1)行的栅极总线gl(n+1)连接的第一缓冲电路buf1(n+1)中的升压动作,第一状态节点n1(n+1)的电压进一步上升。

88.当达到时刻t14,第一栅极时钟信号gck1从低电平变化为高电平。由此,与进行正向扫描时的时刻t04(参照图8)同样地,第n行的栅极总线gl(n)从一端侧(图1中的左侧)和另一端侧(图1中的右侧)双方被充电至完全的高电平。

89.在时刻t15,通过使第二栅极时钟信号gck2从高电平变化为低电平,第一状态节点n1(n+1)的电压降低至预充电电压电平。此时,薄膜晶体管t3b处于截止状态,第二状态节点n2(n)的电压不变化。另外,当达到时刻t15,通过使第六栅极时钟信号gck6从低电平变化为高电平,基于与第(n

‑

1)行的栅极总线gl(n

‑

1)连接的第一缓冲电路buf1(n

‑

1)中的升压动作,第一状态节点n1(n

‑

1)的电压进一步上升。如上所述,薄膜晶体管t3a具有当漏极端子的电压电平和源极端子的电压电平超过预充电电压电平时处于截止状态的阈值电压,因此此时,薄膜晶体管t3a处于截止状态,第二状态节点n2(n)的电压不变化。

90.在时刻t16,第一栅极时钟信号gck1从高电平变化为低电平。由此,与进行正向扫描时的时刻t06(参照图8)同样地,第n行的栅极总线gl(n)的电荷经由第一缓冲电路buf1(n)内的薄膜晶体管t1从上述一端侧(图1中的左侧)放电,并且也经由第二缓冲电路buf2(n)内的薄膜晶体管t2从上述另一端侧(图1中的右侧)放电。其结果,扫描信号g(n)的电压高速下降到低电平。这样,在时刻t14变为选择状态的第n行的栅极总线gl(n)在时刻t16迅速地向非选择状态变化。另外,与进行正向扫描时的时刻t06(参照图8)同样地,第一状态节点n1(n)的电压以及第二状态节点n2(n)的电压降低。

91.在时刻t16,此外,扫描信号g(n

‑

2)(图10中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n+1)中,薄膜晶体管tr1处于导通状态,因此第一状态节点n1(n+1)的电压降低到低电平。

92.当达到时刻t17,扫描信号g(n

‑

3)从低电平变化为高电平。由此,在双稳态电路sr(n)中,薄膜晶体管ta处于导通状态。由于薄膜晶体管ta的漏极端子与第一移位方向控制线uda连接,因此,由于薄膜晶体管ta处于导通状态,第一状态节点n1(n)的电压降低至低电平。

93.当达到时刻t18,扫描信号g(n

‑

4)(图10中未图示)从低电平变化为高电平。由此,在双稳态电路sr(n

‑

1)中,薄膜晶体管ta处于导通状态,因此第一状态节点n1(n

‑

1)的电压降低到低电平。此时,第二缓冲电路buf2(n)内的薄膜晶体管t3a处于导通状态,第二状态节点n2(n)的电压也降低到低电平。

94.当达到时刻t19,扫描信号g(n

‑

3)从高电平变化为低电平。由此,在双稳态电路sr(n)中,薄膜晶体管ta处于导通状态。

95.此外,在这个示例中,通过时刻t11的动作实现第二的第一状态节点控制晶体管导通步骤,通过时刻t13的动作实现第二的第一状态节点控制晶体管截止步骤,通过时刻t17的动作实现第一的第一状态节点控制晶体管导通步骤,通过时刻t19的动作实现第一的第一状态节点控制晶体管截止步骤。

96.图11是通过模拟得到的反向扫描时的信号波形图。所有的波形都是横轴为时间,纵轴为电压。第一状态节点n1(n)的电压变化及第二状态节点n2(n)的电压变化不依赖于第一状态节点n1(n+1)的电压变化。若着眼于第一状态节点n1(n)和第二状态节点n2(n)的电压,则在第一状态节点n1(n)的电压从低电平变化为预充电电压电平后,第二状态节点n2(n)的电压从低电平变化为预充电电压电平。并且,第一状态节点n1(n)以及第二状态节点n2(n)在相同期间(附加了附图标记62的箭头所示的期间)被维持为与通常的高电平相比充分高的电压。之后,在第一状态节点n1(n)的电压从预充电电压电平变化为低电平后,第二状态节点n2(n)的电压从预充电电压电平变化为低电平。此处,第二状态节点n2(n)的电压在与第一状态节点n1(n

‑

1)的电压相同的定时从低电平向预充电电压电平变化,另外,第二状态节点n2(n)的电压在与第一状态节点n1(n

‑

1)的电压相同的定时从预充电电压电平向低电平变化。即,第二状态节点n2(n)的电压变化依赖于第一状态节点n1(n

‑

1)的电压变化。

97.<2.4关于薄膜晶体管的尺寸以及升压电容器的电容值>此处,对薄膜晶体管的尺寸以及升压电容器的电容值进行说明。如上所述,在本实施方式中,各栅极总线gl的充放电通过第一缓冲电路buf1从一端部进行的同时,通过第二缓冲电路buf2从另一端部进行。关于此,来自一端部的栅极总线gl的充放电与来自另一端部的栅极总线gl的充放电以相同的方式进行。然而,对于第一缓冲电路buf1和第二缓冲电路buf2而言,电路构成、输入信号不同。因此,第一状态节点n1的电压波形与第二状态节点n2(n2)的电压波形不同。另外,在第一缓冲电路buf1和第二缓冲电路buf2中,由升压电容器进行的升压动作的效率也不同。因此,优选以使第一缓冲电路buf1的栅极总线gl的驱动能力和第二缓冲电路buf2的栅极总线gl的驱动能力成为相同程度的方式,进行针对薄膜晶体管t1以及薄膜晶体管t2的互不相同的尺寸的设定和针对增压电容器c1以及增压电容器c2的互不相同的电容值的设定。通过使作为缓冲晶体管的薄膜晶体管t1、t2的尺寸、升压动作的效率最佳化,能够使元件尺寸最小化而实现窄边框化。另外,若使第一缓冲电路buf1的栅极总线gl的驱动能力和第二缓冲电路buf2的栅极总线gl的驱动能力为相同程度,则各栅极总线gl从选择状态向非选择状态转换时的各像素形成部ps中的引入电压的大小在一端部附近和另一端部附近为相同程度。由此,抑制闪烁的发生。

98.此外,薄膜晶体管的驱动能力由沟道宽度w与沟道长度l之比w/l来决定。此处,假设沟道长度l为固定,设定薄膜晶体管的尺寸是指设定沟道宽度w。

99.<3.效果>根据本实施方式,显示部500内的各栅极总线gl由第一栅极驱动器410及第二栅极驱动器420驱动。即,各栅极总线gl中,从其两端施加高电平或低电平的电压作为扫描信号。由此,由于能够对各栅极总线gl高速地进行充电以及放电,因此对于尺寸大的显示部500也能够通过高速地驱动而良好地显示图像。此处,第一栅极驱动器410内的第一移位寄存器411由与第奇数行的栅极总线gl对应的双稳态电路sr构成,第二栅极驱动器420内的第二移位寄存器421由与第偶数行的栅极总线gl对应的双稳态电路sr构成。而且,根据各双稳态电

路的输出信号来控制三个缓冲电路(1个第一缓冲电路buf1和2个第二缓冲电路buf2)的动作。由于采用这样的构成,因此与以往相比,移位寄存器的实现所需的面积减少,能够实现作为显示面板的液晶面板600的窄边框化。

100.另外,在各双稳态电路sr中,作为用于控制与薄膜晶体管t1的栅极端子连接的第一状态节点n1的电压的构成要素,设置有两个薄膜晶体管,该薄膜晶体管t1作为连接至栅极总线gl的第一缓冲电路buf1内的缓冲晶体管。详细而言,将j和k设为整数,与第k行的栅极总线gl(k)对应的双稳态电路sr(k)设有薄膜晶体管ta和薄膜晶体管tb,该薄膜晶体管ta具有连接至第(k

‑

j)行的栅极总线gl(k

‑

j)的栅极端子、连接至第一移位方向控制线uda的漏极端子和连接至第一状态节点n1(k)的源极端子,该薄膜晶体管tb具有连接至第(k+j)行的栅极总线gl(k+j)的栅极端子、连接至第二移位方向控制线udb的漏极端子和连接至第一状态节点n1(k)的源极端子。此处,在进行正向扫描时,第一移位方向控制信号uda维持在高电平,并且第二移位方向控制信号udb维持在低电平,在进行反向扫描时,第一移位方向控制信号uda维持在低电平,并且第二移位方向控制信号udb维持在高电平。另外,第二缓冲电路buf2(k)构成为基于与相邻于连接目的地的栅极总线gl(k)的一方的栅极总线gl(k

‑

1)对应的双稳态电路sr(k

‑

1)的输出信号、与相邻于连接目的地的栅极总线gl(k)的另一方的栅极总线gl(k+1)对应的双稳态电路sr(k+1)的输出信号以及栅极时钟信号gck,驱动连接目的地的栅极总线gl(k)。根据以上的构成,当针对第一移位寄存器411和第二移位寄存器421向初级侧的双稳态电路sr施加起始脉冲时,进行正向扫描,当针对第一移位寄存器411和第二移位寄存器421向最终级侧的双稳态电路sr施加起始脉冲时,进行反向扫描。这样,能够进行栅极总线gl的扫描顺序的切换。

101.如上所述,根据本实施方式,实现了栅极总线gl的高速充放电以及栅极总线gl的扫描顺序的切换为可能的且能够实现窄边框化的显示装置。

102.<4.变形例>在上述实施方式中,关于与各栅极总线对应的双稳态电路sr(参照图6),输入端子46连接到3行前的栅极总线,输入端子47连接到3行后的栅极总线。另外,用作栅极时钟信号gck的多相时钟信号的相数为6,并且各栅极时钟信号gck的脉冲宽度是相当于2个水平扫描期间的长度。然而,对于这些可以实施各种各样的变形。因此,以下对上述实施方式的变形例进行说明。此外,在下文中,将z设为整数并将相当于z个水平扫描期间的长度称为“zh”。例如,将相当于2个水平扫描期间的长度称为“2h”。

103.<4.1第一变形例>图12是示出本变形例中的双稳态电路sr(n)的详细构成的电路图。输入端子46(薄膜晶体管ta的栅极端子)连接到第(n

‑

2)行的栅极总线gl(n

‑

2),输入端子47(薄膜晶体管tb的栅极端子)连接到第(n+2)行的栅极总线gl(n+2)。所使用的多相时钟信号(栅极时钟信号gck)的相数为4。但是,所使用的多相时钟信号的相数也可以为5以上。各栅极时钟信号gck的脉冲宽度为1h。

104.图13是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t21从低电平变化为预充电电压电平后,在时刻t23变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t24变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时

刻t25变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t23到时刻t24的1h期间,也被维持为与通常的高电平相比充分高的电压。如图13所示,产生第一至第四栅极时钟信号gck1~gck4的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

105.图14是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t31从低电平变化为预充电电压电平后,在时刻t33变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t34变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t35变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t33到时刻t34的1h期间,也被维持为与通常的高电平相比充分高的电压。如图14所示,产生第一至第四栅极时钟信号gck1~gck4的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

106.<4.2第二变形例>在本变形例中,双稳态电路sr的输入端子46(薄膜晶体管ta的栅极端子)以及输入端子47(薄膜晶体管tb的栅极端子)的连接目的地与上述实施方式相同(参照图6)。所使用的多相时钟信号(栅极时钟信号gck)的相数为5。但是,所使用的多相时钟信号的相数也可以为6以上。各栅极时钟信号gck的脉冲宽度为1h。

107.图15是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t41从低电平变化为预充电电压电平后,在时刻t44变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t45变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t47变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t44到时刻t45的1h期间,也被维持为与通常的高电平相比充分高的电压。如图15所示,产生第一至第五栅极时钟信号gck1~gck5的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

108.图16是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t51从低电平变化为预充电电压电平后,在时刻t54变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t55变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t57变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t54到时刻t55的1h期间,也被维持为与通常的高电平相比充分高的电压。如图16所示,产生第一至第五栅极时钟信号gck1~gck5的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

109.<4.3第三变形例>在本变形例中,双稳态电路sr的输入端子46(薄膜晶体管ta的栅极端子)以及输入

端子47(薄膜晶体管tb的栅极端子)的连接目的地与上述实施方式相同(参照图6)。所使用的多相时钟信号(栅极时钟信号gck)的相数为5。但是,所使用的多相时钟信号的相数也可以为6以上。各栅极时钟信号gck的脉冲宽度为2h。

110.图17是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t61从低电平变化为预充电电压电平后,在时刻t64变化为与通常的高电平相比充分高的电压电平。然后,在2h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t66变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t67变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t64到时刻t66的2h期间,也被维持为与通常的高电平相比充分高的电压。如图17所示,产生第一至第五栅极时钟信号gck1~gck5的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

111.图18是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t71从低电平变化为预充电电压电平后,在时刻t74变化为与通常的高电平相比充分高的电压电平。然后,在2h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t76变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t77变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t74到时刻t76的2h期间,也被维持为与通常的高电平相比充分高的电压。如图18所示,产生第一至第五栅极时钟信号gck1~gck5的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

112.<4.4第四变形例>图19是示出本变形例中的双稳态电路sr(n)的详细构成的电路图。输入端子46(薄膜晶体管ta的栅极端子)连接到第(n

‑

4)行的栅极总线gl(n

‑

4),输入端子47(薄膜晶体管tb的栅极端子)连接到第(n+4)行的栅极总线gl(n+4)。所使用的多相时钟信号(栅极时钟信号gck)的相数为6。但是,所使用的多相时钟信号的相数也可以为7以上。各栅极时钟信号gck的脉冲宽度为1h。

113.图20是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t81从低电平变化为预充电电压电平后,在时刻t85变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻t86变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t89变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t85到时刻t86的1h期间,也被维持为与通常的高电平相比充分高的电压。如图20所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

114.图21是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻t91从低电平变化为预充电电压电平后,在时刻t95变化为与通常的高电平相比充分高的电压电平。然后,在1h的期间,维持该充分高的电压电平。即,第一状态

节点n1(n)的电压在时刻t96变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻t99变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻t95到时刻t96的1h期间,也被维持为与通常的高电平相比充分高的电压。如图21所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

115.<4.5第五变形例>在本变形例中,双稳态电路sr的输入端子46(薄膜晶体管ta的栅极端子)以及输入端子47(薄膜晶体管tb的栅极端子)的连接目的地与上述第四变形例相同(参照图19)。所使用的多相时钟信号(栅极时钟信号gck)的相数为6。但是,所使用的多相时钟信号的相数也可以为7以上。各栅极时钟信号gck的脉冲宽度为2h。

116.图22是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻ta1从低电平变化为预充电电压电平后,在时刻ta5变化为与通常的高电平相比充分高的电压电平。然后,在2h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻ta7变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻ta9变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻ta5到时刻ta7的2h期间,也被维持为与通常的高电平相比充分高的电压。如图22所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

117.图23是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻tb1从低电平变化为预充电电压电平后,在时刻tb5变化为与通常的高电平相比充分高的电压电平。然后,在2h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻tb7变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻tb9变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻tb5到时刻tb7的2h期间,也被维持为与通常的高电平相比充分高的电压。如图23所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

118.<4.6第六变形例>在本变形例中,双稳态电路sr的输入端子46(薄膜晶体管ta的栅极端子)以及输入端子47(薄膜晶体管tb的栅极端子)的连接目的地与上述第四变形例相同(参照图19)。所使用的多相时钟信号(栅极时钟信号gck)的相数为6。但是,所使用的多相时钟信号的相数也可以为7以上。各栅极时钟信号gck的脉冲宽度为3h。

119.图24是用于说明进行正向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻tc1从低电平变化为预充电电压电平后,在时刻tc5变化为与通常的高电平相比充分高的电压电平。然后,在3h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻tc8变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻tc9变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电

压在从时刻tc5到时刻tc8的3h期间,也被维持为与通常的高电平相比充分高的电压。如图24所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向初级侧的双稳态电路sr提供起始脉冲,由此按升序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

120.图25是用于说明进行反向扫描时的栅极驱动器的动作的信号波形图。第一状态节点n1(n)的电压在时刻td1从低电平变化为预充电电压电平后,在时刻td5变化为与通常的高电平相比充分高的电压电平。然后,在3h的期间,维持该充分高的电压电平。即,第一状态节点n1(n)的电压在时刻td8变化为预充电电压电平。之后,第一状态节点n1(n)的电压在时刻td9变化为低电平。并且,与第一状态节点n1(n)的电压同样地,第二状态节点n2(n)的电压在从时刻td5到时刻td8的3h期间,也被维持为与通常的高电平相比充分高的电压。如图25所示,产生第一至第六栅极时钟信号gck1~gck6的时钟脉冲,并且针对第一移位寄存器411及第二移位寄存器421向最终级侧的双稳态电路sr提供起始脉冲,由此按降序向多个栅极总线gl施加高电平(导通电平)的扫描信号g。

121.<4.7总结>根据上述实施方式及上述所有变形例,概括而言,可以认为将j和k设为整数,各双稳态电路sr能采用以下的构成。与第k行的栅极总线gl(k)对应的双稳态电路sr(k)包括:与输出信号的输出目的地的第一缓冲电路buf1(k)连接的第一状态节点n1(k);以及源极端子连接至该第一状态节点n1(k)的两个薄膜晶体管ta、tb。对于薄膜晶体管ta,栅极端子连接至第(k

‑

j)行的栅极总线gl(k

‑

j),漏极端子连接至第一移位方向控制线uda。对于薄膜晶体管tb,栅极端子连接至第(k+j)行的栅极总线gl(k+j),漏极端子连接至第二移位方向控制线udb。第一移位方向控制线uda在正向扫描时被施加有高电平电源电压vdd,在反向扫描时被施加有低电平电源电压vss。第二移位方向控制线udb在正向扫描时被施加有低电平电源电压vss,在反向扫描时被施加有高电平电源电压vdd。

122.另外,在各双稳态电路sr中,在通过升压动作将第一状态节点n1的电压提高到与通常的高电平相比充分高的电压之前,需要进行第一状态节点n1的预充电的至少1h的期间和进行第二状态节点n2的预充电的至少1h的期间。因此,上述j为2以上的整数,以使比进行升压动作的定时早2h以上地开始第一状态节点n1的预充电。

123.另外,在第二缓冲电路buf2中,第二状态节点n2的电压通过升压动作从变为与通常的高电平相比充分高的电压的定时起(j+1)h后降低到低电平。此处,对于施加给第二缓冲电路buf2的栅极时钟信号gck,在上述升压动作后从高电平变化为低电平后,到第二状态节点n2的电压降低到低电平为止,为了不引起误动作,必须维持在低电平。因此,用作栅极时钟信号的多相时钟信号相数为(j+2)以上。

124.进一步地,在各双稳态电路sr中,第一状态节点n1的电压通过升压动作从变为与通常的高电平相比充分高的电压的定时起jh后,薄膜晶体管ta或薄膜晶体管tb变为导通状态。关于此,通过薄膜晶体管ta或者薄膜晶体管tb变为导通状态而使第一状态节点n1的电压降低时,如果施加给第一缓冲电路buf1内的薄膜晶体管t1的漏极端子的栅极时钟信号gck变为高电平,则可能产生误动作。因此,栅极时钟信号gck的脉冲宽度为(j

‑

1)以下。此外,栅极时钟信号gck的最小脉冲宽度为1h。

125.<5.其他>

以上详细地说明了本发明,但以上的说明在所有方面都是示例性的而不是限制性的。在不脱离本发明的范围的情况下,可以想到多个其他变更、变形。附图标记说明

126.10、t1、t2、ta、tb、t3a、t3b...薄膜晶体管410...第一栅极驱动器411...第一移位寄存器412...第一扫描信号输出部420...第二栅极驱动器421...第二移位寄存器422...第二扫描信号输出部500...显示部600...液晶面板buf1、buf2...第一缓冲电路、第二缓冲电路c1、c2...升压电容器sr...双稳态电路gl...栅极总线g...扫描信号gck1~gck6...栅极时钟信号n1、n3...第一状态节点、第二状态节点uda...第一移位方向控制信号、第一移位方向控制线udb...第二移位方向控制信号、第二移位方向控制线

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1