显示面板及其开关电路的驱动方法、显示装置与流程

1.本公开涉及显示技术领域,特别涉及一种显示面板及其开关电路的驱动方法、显示装置。

背景技术:

2.有机发光二极管(organic light

‑

emitting diode,oled)显示面板因其自发光、宽视角、广色域、可折叠和可弯曲等优点被广泛应用于各类显示装置中。

3.相关技术中,oled显示面板一般包括衬底基板,以及位于衬底基板上的多个像素。其中,每个像素一般包括像素电路和发光元件,像素电路与发光元件耦接,像素电路用于向发光元件传输驱动电流,以驱动发光元件发光。

4.但是,对于分辨率较大的oled显示面板而言,其包括的每个像素所占用衬底基板的面积较小,即每个像素电路的尺寸较小。相应的,每个像素电路所能提供的驱动电流较小。如此,导致显示面板需要显示低灰阶画面时,发光元件无法在较小的驱动电流可靠发光,显示面板出现低灰阶展开不良的现象。

技术实现要素:

5.本公开提供了一种显示面板及其开关电路的驱动方法、显示装置,可以解决相关技术中显示面板易出现低灰阶展开不良的问题。所述技术方案如下:

6.一方面,提供了一种显示面板,所述显示面板包括:

7.衬底基板,所述衬底基板具有显示区和位于所述显示区一侧的非显示区;

8.位于所述显示区的多个像素;

9.以及,位于所述非显示区的至少一个开关电路;

10.其中,每个所述开关电路分别与第一控制端、第一电源端和所述多个像素中的至少一个像素耦接,每个所述开关电路用于响应于所述第一控制端提供的第一控制信号,控制所述第一电源端与所述至少一个像素之间的通断;

11.所述至少一个像素还分别与栅极驱动端和数据信号端耦接,所述至少一个像素用于响应于所述栅极驱动端提供的栅极驱动信号,所述数据信号端提供的数据信号,以及所述第一电源端提供的第一电源信号发光。

12.可选的,所述至少一个像素包括:像素电路和发光元件;

13.所述开关电路与所述像素电路耦接,所述开关电路用于响应于所述第一控制信号,控制所述第一电源端与所述像素电路之间的通断;

14.所述像素电路还分别与所述栅极驱动端、所述数据信号端和所述发光元件的第一极耦接,所述发光元件的第二极与第二电源端耦接,所述像素电路用于响应于所述栅极驱动信号,所述数据信号和所述第一电源信号向所述发光元件的第一极传输驱动信号;

15.所述发光元件用于基于所述驱动信号和所述第二电源端提供的第二电源信号发光;

16.其中,所述第一电源信号的电位大于所述第二电源信号的电位。

17.可选的,所述至少一个像素包括:像素电路和发光元件;

18.所述开关电路与所述发光元件的第二极耦接,所述开关电路用于响应于所述第一控制信号,控制所述第一电源端与所述发光元件的第二极之间的通断;

19.所述像素电路分别与所述栅极驱动端、所述数据信号端、第二电源端和所述发光元件的第一极耦接,所述像素电路用于响应于所述栅极驱动信号,所述数据信号和所述第二电源端提供的第二电源信号向所述发光元件的第一极传输驱动信号;

20.所述发光元件用于基于所述驱动信号和所述第一电源信号发光;

21.其中,所述第一电源信号的电位小于所述第二电源信号的电位。

22.可选的,所述至少一个像素包括:像素电路和发光元件;

23.所述开关电路分别与所述像素电路和所述发光元件的第二极耦接,且所述开关电路还与第二电源端耦接,所述开关电路用于响应于所述第一控制信号,控制所述第一电源端与所述像素电路之间的通断,以及控制所述第二电源端与所述发光元件的第二极之间的通断;

24.所述像素电路还分别与所述栅极驱动端、所述数据信号端和所述发光元件的第一极耦接,所述像素电路用于响应于所述栅极驱动信号,所述数据信号和所述第一电源信号向所述发光元件的第一极传输驱动信号;

25.所述发光元件用于基于所述驱动信号和所述第二电源端提供的第二电源信号发光;

26.其中,所述第一电源信号的电位大于所述第二电源信号的电位。

27.可选的,所述开关电路包括:第一开关晶体管;

28.所述第一开关晶体管的栅极与所述第一控制端耦接,所述第一开关晶体管的第一极与所述第一电源端耦接,所述第一开关晶体管的第二极与所述至少一个像素耦接。

29.可选的,所述开关电路还分别与第二控制端和降噪电源端耦接;

30.所述开关电路还用于响应于所述第二控制端提供的第二控制信号,控制所述降噪电源端与所述至少一个像素之间的通断;

31.其中,所述降噪电源端提供的降噪电源信号的电位的绝对值小于所述第一电源信号的电位的绝对值。

32.可选的,所述开关电路还包括:第二开关晶体管;

33.所述第二开关晶体管的栅极与所述第二控制端耦接,所述第二开关晶体管的第一极与所述降噪电源端耦接,所述第二开关晶体管的第二极与所述至少一个像素耦接。

34.可选的,所述显示面板包括:一个开关电路,所述一个开关电路与所述多个像素均耦接。

35.可选的,所述显示面板的尺寸大于等于7英寸,且小于等于17英寸。

36.可选的,所述像素电路还与检测扫描端和检测信号线耦接,所述像素电路还用于响应于所述检测扫描端提供的检测扫描信号,控制所述检测信号线与所述发光元件的第一极之间的通断。

37.另一方面,提供了一种显示面板中开关电路的驱动方法,应用于如上述方面所述的开关电路中,所述方法包括:

38.在显示阶段,第一控制端提供的第一控制信号的电位为第一电位,所述开关电路响应于所述第一控制信号,控制第一电源端与至少一个像素导通,所述第一电源端向所述至少一个像素传输第一电源信号,所述至少一个像素用于响应于栅极驱动端提供的栅极驱动信号,数据信号端提供的数据信号,以及所述第一电源信号发光;

39.在插黑阶段,所述第一控制信号的电位为第二电位,所述开关电路响应于所述第一控制信号,控制所述第一电源端与所述至少一个像素断开连接。

40.可选的,所述开关电路还分别与第二控制端和降噪电源端耦接;所述方法还包括:

41.在所述插黑阶段,所述第二控制端提供的第二控制信号的电位为第一电位,所述开关电路响应于所述第二控制信号,控制所述降噪电源端与所述至少一个像素导通,所述降噪电源端向所述至少一个像素传输降噪电源信号;

42.其中,所述降噪电源信号的电位的绝对值小于所述第一电源信号的电位的绝对值。

43.又一方面,提供了一种显示装置,所述显示装置包括:驱动电路,以及如上述方面所述的显示面板;

44.其中,所述驱动电路与所述显示面板中的第一控制端耦接,用于向所述第一控制端提供第一控制信号。

45.可选的,所述驱动电路还与所述显示面板中的第二控制端耦接,用于向所述第二控制端提供第二控制信号。

46.可选的,所述显示面板中的开关电路与所述驱动电路集成设置。

47.本公开提供的技术方案带来的有益效果至少可以包括:

48.提供了一种显示面板及其开关电路的驱动方法、显示装置。该显示面板包括位于非显示区的开关电路,且该开关电路能够响应于第一控制端提供的第一控制信号,控制第一电源端与像素的通断,在第一电源端与像素导通时,像素能够响应于该第一电源端提供的电源信号发光。如此,可以在不受限于高分辨率的前提下,通过灵活设置第一控制信号的电位,实现对第一电源端和像素通断时长的控制。结合pwm调光原理可知,在对第一电源端和像素通断时长进行灵活控制的前提下,可以确保在显示面板需要显示低灰阶画面时像素也能可靠发光。进而,有效改善了显示面板出现的低灰阶展开不良现象。

附图说明

49.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

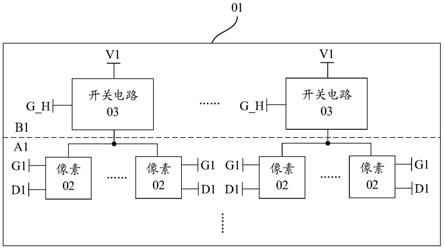

50.图1是本公开实施例提供的一种显示面板的结构示意图;

51.图2是本公开实施例提供的另一种显示面板的结构示意图;

52.图3是本公开实施例提供的又一种显示面板的结构示意图;

53.图4是本公开实施例提供的再一种显示面板的结构示意图;

54.图5是本公开实施例提供的再一种显示面板的结构示意图;

55.图6是本公开实施例提供的再一种显示面板的结构示意图;

56.图7是本公开实施例提供的再一种显示面板的结构示意图;

57.图8是本公开实施例提供的一种像素电路耦接的各信号端的时序图;

58.图9是本公开实施例提供的再一种显示面板的结构示意图;

59.图10是本公开实施例提供的再一种显示面板的结构示意图;

60.图11是本公开实施例提供的再一种显示面板的结构示意图;

61.图12是本公开实施例提供的再一种显示面板的结构示意图;

62.图13是本公开实施例提供的再一种显示面板的结构示意图;

63.图14是本公开实施例提供的再一种显示面板的结构示意图;

64.图15是本公开实施例提供的一种显示面板中开关电路的驱动方法流程图;

65.图16是本公开实施例提供的另一种开关电路的驱动方法流程图;

66.图17是本公开实施例提供的一种显示面板中电路的工作时序图;

67.图18是本公开实施例提供的一种显示装置的结构示意图。

具体实施方式

68.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

69.本公开所有实施例中采用的晶体管均可以为场效应管或其他特性相同的器件,根据在电路中的作用本公开的实施例所采用的晶体管主要为开关晶体管。由于这里采用的开关晶体管的源极、漏极是对称的,所以其源极、漏极是可以互换的。在本公开实施例中,将其中源极称为第一极,漏极称为第二极,或者,将其中漏极称为第一极,源极称为第二极。按附图中的形态规定晶体管的中间端为栅极、信号输入端为源极、信号输出端为漏极。此外,本公开实施例所采用的开关晶体管可以包括p型开关晶体管和n型开关晶体管中的任一种,其中,p型开关晶体管在栅极为低电平时导通,在栅极为高电平时截止,n型开关晶体管在栅极为高电平时导通,在栅极为低电平时截止。此外,本公开各个实施例中的多个信号都对应有有效电位和无效电位,有效电位和无效电位仅代表该信号的电位有2个状态量,不代表全文中有效电位或无效电位具有特定的数值。

70.显示领域中,目前较为成熟的显示面板包括:液晶显示(liquid crystal display,lcd)面板和oled显示面板。其中,lcd面板是一种通过控制液晶分子偏转以实现显示的显示面板。oled显示面板是一种通过电子与空穴直接的复合以激发出各种波长的光谱,从而形成图形以显示的显示面板。相对于lcd面板而言,oled显示面板的响应速度较快,且可以实现对比度最大化。如此,具有oled显示面板的oled显示装置有望成为下一代显示的主流产品。并且,随着产品不断的更新换代,高分辨率的中小尺寸产品的需求越发旺盛,分辨率的单位可以为显示面板每英寸所拥有的像素数(per pixel inch,ppi)。

71.但是,经测试,对于高ppi的显示面板而言,因每个像素的尺寸较小的缘故,像素中像素电路向发光元件传输较低驱动电流的能力较弱。在显示面板需基于较小的驱动电流显示低灰阶画面时,像素电路无法可靠驱动发光元件发光,显示面板无法可靠显示低灰阶画面。即,显示面板易出现低灰阶展开不良现象。

72.目前,一般采用如下两种方式来改善显示面板出现的低灰阶展开不良现象。其中,第一种:增大像素电路中向发光元件提供驱动电流的驱动晶体管的沟道长度。第二种:设置

像素电路还包括能够控制该驱动电流的发光控制晶体管。但是,无论哪种实现方式,均不利于显示面板高ppi的实现。且对于第二种方式而言,其还会增加所需设置的信号线数量,不利于显示装置窄边框的实现。

73.本公开实施例提供了一种显示面板。该显示面板不受高ppi的限制,且不易出现低灰阶展开不良现象,显示效果较好,且利于显示装置的窄边框实现。

74.图1是本公开实施例提供的一种显示面板的结构示意图。如图1所示,该显示面板包括:衬底基板01,该衬底基板01具有显示区a1,以及位于显示区a1一侧的非显示区b1。例如,参考图1,其示出的显示面板中,非显示区b1位于显示区a1的上方一侧。当然,在一些实施例中,结合图1,非显示区b1还可以位于显示区a1的左侧、右侧、下方一侧或是围绕显示区a1。

75.继续参考图1,该显示面板还包括:位于显示区a1的多个像素02,以及位于非显示区b1的至少一个开关电路03。

76.其中,每个开关电路03分别与第一控制端g_h、第一电源端v1和多个像素02中的至少一个像素02耦接。每个开关电路03用于响应于第一控制端g_h提供的第一控制信号,控制第一电源端v1与至少一个像素02之间的通断。

77.例如,每个开关电路03可以在第一控制信号的电位为第一电位时,控制第一电源端v1与至少一个像素02导通。此时,第一电源端v1提供的第一电源信号可以传输至该至少一个像素02。以及,每个开关电路03可以在第一控制信号的电位为第二电位时,控制第一电源端v1与至少一个像素02断开连接。此时,第一电源端v1提供的第一电源信号即无法传输至该至少一个像素02。

78.可选的,第一电位相对于第二电位可以为高电位,且对于开关电路03而言,第一电位可以为有效电位,第二电位可以为无效电位。

79.至少一个像素02还分别与栅极驱动端g1和数据信号端d1耦接。至少一个像素02用于响应于栅极驱动端g1提供的栅极驱动信号,数据信号端d1提供的数据信号,以及第一电源端v1提供的第一电源信号发光。

80.例如,像素02一般包括像素电路和发光元件,像素电路可以响应于接收到的信号向发光元件传输驱动信号(一般为驱动电流)。发光元件可以响应于接收到的信号发光。其中,像素电路接收到的信号和发光元件接收到的信号包括上述实施例记载的栅极驱动信号,数据信号和第一电源信号。

81.因像素02发光需要响应的信号包括第一电源端v1提供的第一电源信号,故在本公开实施例中,当开关电路03控制第一电源端v1与像素02导通后,像素02才可以进一步发光。如此,可以通过灵活设置第一控制端g_h提供的第一控制信号的电位,来调节第一电源端v1与像素02的通断时长。即调节第一电源端v1向像素02传输第一电源信号的时长。结合脉宽调制(pulse width modulation,pwm)调光原理,在灵活调节第一电源端v1向像素02传输第一电源信号的时长的基础上,可以实现对像素02中像素电路最终传输至发光元件的驱动电流的大小的控制,使得传输至发光元件的驱动电流满足低灰阶显示的需求。进而,即能够有效改善显示面板出现的低灰阶展开不良现象。

82.综上所述,本公开实施例提供了一种显示面板,该显示面板包括位于非显示区的开关电路,且该开关电路能够响应于第一控制端提供的第一控制信号,控制第一电源端与

像素的通断,在第一电源端与像素导通时,像素能够响应于该第一电源端提供的电源信号发光。如此,可以在不受限于高分辨率的前提下,通过灵活设置第一控制信号的电位,实现对第一电源端和像素通断时长的控制。结合pwm调光原理可知,在对第一电源端和像素通断时长进行灵活控制的前提下,可以确保在显示面板需要显示低灰阶画面时像素也能可靠发光。进而,有效改善了显示面板出现的低灰阶展开不良现象。

83.结合上述实施例记载、图2和图3可知,像素02可以包括:像素电路021和发光元件022。像素电路021与发光元件022耦接,像素电路021用于向发光元件022传输驱动电流,以驱动发光元件022发光。

84.在此基础上,作为一种可选的实现方式,参考图2,开关电路03可以与像素电路021耦接。像素电路021还可以分别与栅极驱动端g1、数据信号端d1和发光元件022的第一极耦接。发光元件022的第二极可以与第二电源端v2耦接。即,像素电路021可以通过开关电路03与第一电源端v1间接耦接。

85.其中,开关电路03可以用于响应于第一控制信号,控制第一电源端v1与像素电路021之间的通断。像素电路021可以用于响应于栅极驱动信号,数据信号和第一电源信号向发光元件022的第一极传输驱动信号。发光元件022可以用于基于驱动信号和第二电源端v2提供的第二电源信号发光。

86.例如,开关电路03可以在第一控制信号的电位为第一电位时,控制第一电源端v1与像素电路021导通。此时,第一电源端v1提供的第一电源信号可以传输至像素电路021。像素电路021可以响应于该第一电源信号,以及栅极驱动信号和数据信号向发光元件022传输驱动信号。发光元件022在该驱动信号与第二电源信号的压差作用下发光。以及,开关电路03可以在第一控制信号的电位为第二电位时,控制第一电源端v1与像素电路021断开连接。此时,像素电路021无法向发光元件022传输驱动电流,发光元件022无法发光,即不发光。

87.作为另一种可选的实现方式,参考图3,开关电路03可以与发光元件022的第二极耦接。像素电路021可以分别与栅极驱动端g1、数据信号端d1、第二电源端v2和发光元件022的第一极耦接。即,发光元件022可以通过开关电路03与第一电源端v1间接耦接。

88.其中,开关电路03可以用于响应于第一控制信号,控制第一电源端v1与发光元件022的第二极之间的通断。像素电路021可以用于响应于栅极驱动信号,数据信号和第二电源信号向发光元件022的第一极传输驱动信号。发光元件022可以用于基于驱动信号和第一电源信号发光。

89.例如,开关电路03可以在该第一控制信号的电位为第一电位时,控制第一电源端v1与发光元件022的第二极导通。此时,第一电源端v1提供的第一电源信号可以传输至该发光元件022的第二极。当像素电路021响应于第二电源信号,以及栅极驱动信号和数据信号向发光元件022传输驱动信号时,发光元件022即可在该驱动信号与第一电源信号的压差作用下发光。以及,开关电路03可以在第一控制信号的电位为第二电位时,控制第一电源端v1与发光元件022的第二极断开连接。此时,第一电源端v1无法向发光元件022传输第一电源信号。相应的,即便像素电路021向发光元件022传输驱动信号,发光元件022也无法发光,即不发光。

90.作为又一种可选的实现方式,参考图4,开关电路03可以分别与像素电路021和发光元件022的第二极耦接,且开关电路03还可以与第二电源端v2耦接。

91.其中,开关电路03可以用于响应于第一控制信号,控制第一电源端v1与像素电路021之间的通断,以及响应于第二控制信号,控制第二电源端v2与发光元件022的第二极之间的通断。基于此可以确定,该实现方式下,像素电路021是通过开关电路03与第一电源端v1间接耦接。发光元件022是通过开关电路03与第二电源端v2间接耦接。像素电路021可以用于响应于栅极驱动信号,数据信号和第一电源信号向发光元件022的第一极传输驱动信号。发光元件022可以用于基于该驱动信号和第二电源信号发光。

92.例如,开关电路03可以在该第一控制信号的电位为第一电位时,控制第一电源端v1与像素电路021导通,且控制第二电源端v2与发光元件022的第二极导通。此时,第一电源端v1提供的第一电源信号可以传输至该像素电路021,且第二电源端v2提供的第二电源信号可以传输至发光元件022的第二极。像素电路021可以响应于该第一电源信号,栅极驱动信号以及数据信号向发光元件022传输驱动信号。发光元件022可以在该驱动信号与第二电源信号的压差作用下发光。以及,开关电路03可以在第一控制信号的电位为第二电位时,控制第一电源端v1与像素电路021断开连接,且控制第二电源端v2与发光元件022的第二极断开连接。此时,像素电路021无法向发光元件022传输驱动电流,且第二电源端v2无法向发光元件022传输第二电源信号。进而,发光元件022无法发光,即不发光。

93.可选的,在该实现方式基础上,可以设置两个开关电路03分别与像素电路021和发光元件022耦接,且设置每个开关电路03与不同的第一控制端g_h耦接。如此,可以通过灵活设置各个开关电路03耦接的第一控制端g_h提供的第一控制信号,使得每个开关电路03独立工作。例如,可以在无需发光元件022发光时,仅设置一个开关电路03响应于其所耦接的第一控制端g_h提供的第一控制信号,控制第一电源端v1与像素电路021断开连接,或控制第二电源端v2与发光元件022的第二极断开连接即可,该实现方式可以降低功耗。

94.可选的,本公开实施例提供的第一电源端v1和第二电源端v2可以均为直流电源端。即,第一电源信号的电位和第二电源信号的电位均保持不变。

95.可选的,参考图2至图4,在本公开实施例中,发光元件022的第一极可以为阳极,相应的,发光元件022的第二极即为阴极。当然,在一些实施例中,发光元件022的第一极可以为阴极,相应的,发光元件022的第二极即为阳极。

96.此外,参考图2至图4还可以看出,像素电路021还可以分别与检测扫描端g2和检测信号线s1耦接。像素电路021还可以用于响应于检测扫描端g2提供的检测扫描信号,控制发光元件022的第一极与检测信号线s1之间的通断。

97.例如,像素电路021可以在检测扫描信号的电位为第一电位时,控制发光元件022的第一极与检测信号线s1导通。此时,检测信号线s1提供的检测信号可以传输至该发光元件022的第一极,或者发光元件022的第一极的电位可以传输至检测信号线s1。以及,像素电路021可以在检测扫描信号的电位为第二电位时,控制发光元件022的第一极与检测信号线s1断开连接。

98.需要说明的是,检测信号线s1还可以与外部补偿电路耦接,检测信号线s1可以将发光元件022的第一极的电位传输至外部补偿电路,以供外部补偿电路对数据信号进行外部补偿,确保发光元件的发光效果较好。

99.可选的,以图2所示结构为例,图5示出了又一种显示面板的结构示意图。以图3所示结构为例,图6示出了再一种显示面板的结构示意图。结合图5和图6可以看出,开关电路

03可以包括:第一开关晶体管k1。

100.其中,第一开关晶体管k1的栅极可以与第一控制端g_h耦接,第一开关晶体管k1的第一极可以与第一电源端v1耦接,第一开关晶体管k1的第二极可以与至少一个像素02耦接。

101.需要说明的是,结合图2可知,对于图5所示结构而言,第一开关晶体管k1的第二极其实是与像素02中的像素电路021耦接。结合图3可知,对于图6所示结构而言,第一开关晶体管k1的第二极其实是与像素02中发光元件022的第二极耦接。

102.以图4所示结构为例,图7示出了再一种显示面板的结构示意图。结合图4,因开关电路03与像素电路021和发光元件022均耦接,故结合图7可以看出,开关电路03可以包括:两个第一开关晶体管k1。

103.其中,该两个第一开关晶体管k1的栅极可以均与第一控制端g_h耦接。该两个第一开关晶体管k1中,一个第一开关晶体管k1的第一极可以与第一电源端v1耦接,且该一个第一开关晶体管k1的第二极可以与像素02中像素电路021耦接。另一个第一开关晶体管k1的第一极可以与第二电源端v2耦接,且该另一个第一开关晶体管k1的第二极可以与像素02中发光元件022的第二极耦接耦接。

104.此外,参考图5至图7还可以看出,像素电路021可以包括:数据写入晶体管t1、驱动晶体管t2、补偿晶体管t3和存储电容c1。

105.其中,数据写入晶体管t1的栅极与栅极驱动端g1耦接,数据写入晶体管t1的第一极与数据信号端d1耦接,数据写入晶体管t1的第二极与驱动晶体管t2的栅极耦接。

106.驱动晶体管t2的第一极与驱动电源端vdd耦接,驱动晶体管t2的第二极与发光元件022的第一极耦接。发光元件022的第二极与下拉电源端vss耦接。

107.如此,对于图5和图7所示结构而言,第一电源端v1即为驱动电源端vdd,第二电源端v2即为下拉电源端vss。且,对于图5所示结构而言,驱动晶体管t2的第一极可以通过开关电路03与驱动电源端vdd间接耦接。发光元件022的第二极可以与下拉电源端vss直接耦接。在此基础上,开关电路03可以响应于第一控制信号,控制驱动电源端vdd与驱动晶体管t2的第一极之间的通断。对于图7所示结构而言,驱动晶体管t2的第一极可以通过开关电路03与驱动电源端vdd间接耦接,且发光元件022的第二极可以通过开关电路03与下拉电源端vss间接耦接。在此基础上,开关电路03可以响应于第一控制信号,控制驱动电源端vdd与驱动晶体管t2的第一极之间的通断,以及控制下拉电源端vss与发光元件022的第二极之间的通断。

108.对于图6所示结构而言,第一电源端v1即为下拉电源端vss,第二电源端v2即为驱动电源端vdd。发光元件022的第二极可以通过开关电路03与下拉电源端vss间接耦接,驱动晶体管t2的第一极可以与驱动电源端vdd直接耦接。在此基础上,开关电路03可以响应于第一控制信号,控制下拉电源端vss与发光元件022的第二极之间的通断。

109.此外,因驱动电源端vdd提供的驱动电源信号的电位一般大于下拉电源端vss提供的下拉电源信号的电位,故对于图5和图7所示结构而言,其第一电源端v1提供的第一电源信号的电位可以大于第二电源端v2提供的第二电源信号的电位。对于图6所示结构而言,其第一电源端v1提供的第一电源信号的电位可以小于第二电源端v2提供的第二电源信号的电位。

110.继续参考图5至图7可以看出,存储电容c1的一端可以与驱动晶体管t2的栅极耦接,存储电容c1的另一端可以与驱动晶体管t2的第二极耦接。

111.补偿晶体管t3的栅极可以与检测扫描端g2耦接,补偿晶体管t3的第一极可以与检测信号线s1耦接,补偿晶体管t3的第二极可以与发光元件022的第一极(即,驱动晶体管t2的第二极)耦接。

112.结合图5至图7所示像素电路结构,且以像素电路包括的各晶体管为n型晶体管,且第一电位相对于第二电位为高电位为例,对像素电路的工作原理进行如下介绍。示例的,图8示出了一种像素电路所耦接的各信号端的时序图。参考图8可以看出,像素电路的驱动过程包括:显示阶段t1和消隐阶段t2。其中,显示阶段t1包括:第一复位阶段t11、第一充电阶段t12和发光阶段t13,消隐阶段t2包括:第二复位阶段t21、第二充电阶段t22和检测阶段t23。

113.其中,参考图8可以看出,在第一复位阶段t11和第二复位阶段t21,栅极驱动端g1提供的栅极驱动信号的电位和检测扫描端g2提供的检测扫描信号的电位均为第一电位。数据写入晶体管t1和补偿晶体管t3均开启。相应的,数据信号端d1可以通过开启的数据写入晶体管t1向驱动晶体管t2的栅极提供第二电位的数据信号,从而实现对驱动晶体管t2的栅极的复位。检测信号线s1可以通过开启的补偿晶体管t3向驱动晶体管t2的第二极传输第二电位的检测信号,从而实现对驱动晶体管t2的第二极的复位。

114.在第一充电阶段t12和第二充电阶段t21,栅极驱动信号的电位保持为第一电位,此时,数据写入晶体管t1保持开启。相应的,数据信号端d1可以通过开启的数据写入晶体管t1向驱动晶体管t2的栅极提供第一电位的数据信号,以实现对驱动晶体管t2的栅极的充电,驱动晶体管t2弱开启。且,在第二充电阶段t21中,检测扫描信号的电位保持为第一电位,补偿晶体管t3保持开启,数据信号还通过驱动晶体管t2和开启的补偿晶体管t3向检测信号线s1充电。

115.在发光阶段t13,栅极驱动信号的电位和检测扫描信号的电位均为第二电位,数据写入晶体管t1和补偿晶体管t3均关断。且,在存储电容c1的自举作用下,驱动晶体管t2的栅极的电位可以保持为上一阶段(即,第一充电阶段t12)的第一电位,驱动晶体管t2充分开启。驱动晶体管t2基于其栅极被写入的信号和其第一极接收到的驱动电源信号,通过其第二极向发光元件022的第一极传输驱动信号。此时,发光元件022的第一极的电位和发光元件022的第二极接收到的下拉电源信号的电位之间会形成压差,发光元件022发光。

116.在检测阶段t23,栅极驱动信号的电位和检测扫描信号的电位均为第二电位,数据写入晶体管t1和补偿晶体管t3均关断。检测信号线s1处于floating状态,即检测信号线s1仅采集信号不提供信号。此时,检测信号线s1上的电位会呈线性上升,外部补偿电路通过该检测信号线s1即可以感测到驱动晶体管t2第二极的电位。然后,在后续基于感测到的电位对数据信号进行外部补偿。

117.基于该像素电路021的工作原理可以进一步确定,当开关电路03控制第一电源端v1向像素电路021传输第一电源信号,或,开关电路03控制第一电源端v1向发光元件022的第二极传输第一电源信号,或,开关电路03控制第一电源端v1向像素电路021传输第一电源信号,且控制第二电源端v2向发光元件022的第二极传输第二电源信号时,发光元件022才会发光。

118.可选的,本公开实施例提供的显示面板中,像素电路021不限于附图中所示的3t1c(即,包括三个晶体管和一个电容)架构,也可以为其他架构,如6t1c。

119.可选的,以图2和图5所示结构为例,图9示出了再一种显示面板的结构示意图。以图3和图6所示结构为例,图10示出了再一种显示面板的结构示意图。以图4和图7所示结构为例,图11示出了再一种显示面板的结构示意图。参考图9至图11可以看出,开关电路03还可以分别与第二控制端g_l和降噪电源端耦接。在此基础上,开关电路03还可以用于响应于第二控制端g_l提供的第二控制信号,控制降噪电源端与至少一个像素02之间的通断。

120.例如,开关电路03可以在第二控制信号的电位为第一电位时,控制降噪电源端与像素02导通。此时,降噪电源端可以向像素02传输降噪电源信号。

121.对于图9所示结构而言,开关电路03与一个降噪电源端vref1耦接,开关电路03可以响应于第二控制信号,控制降噪电源端vref1与像素电路021导通,降噪电源端vref1向像素电路021传输降噪电源信号,可选的,可以是向像素电路021中驱动晶体管t2的第一极传输降噪电源信号。对于图10所示结构而言,关电路03与一个降噪电源端vref2耦接,开关电路03可以响应于第二控制信号,控制降噪电源端vref2与发光元件022的第二极导通,降噪电源端vref2向发光元件022的第二极传输降噪电源信号。对于图11所示结构而言,开关电路03与两个降噪电源端vref1和vref2耦接。且,开关电路03可以响应于第二控制信号,控制降噪电源端vref1与像素02中的像素电路021导通,以及控制降噪电源端vref2与像素02中发光元件022的第二极导通。降噪电源端vref1向像素电路021传输降噪电源信号,且降噪电源端vref2向发光元件022的第二极传输降噪电源信号。

122.其中,降噪电源信号的电位的绝对值可以小于第一电源信号的电位的绝对值。例如,结合图9至图11可知,降噪电源端vref1提供的降噪电源信号的电位可以为0伏特(v)或vss,vss是指上述实施例记载的下拉电源端vss提供的下拉电源信号的电位。降噪电源端vref2提供的降噪电源信号的电位可以为vdd或1/2vdd,vdd是指上述实施例记载的驱动电源端vdd提供的驱动电源信号的电位。

123.通过设置开关电路03还控制降噪电源端向像素02提供降噪电源信号,可以使得像素02复位至统一电位后再发光,确保像素02发光的稳定性较好。

124.可选的,以图5和图9所示结构为例,图12示出了再一种显示面板的结构示意图。以图6和图10所示结构为例,图13示出了再一种显示面板的结构示意图。如图12和图13所示,开关电路03还可以包括:第二开关晶体管k2。

125.其中,第二开关晶体管k2的栅极可以与第二控制端g_l耦接,第二开关晶体管k2的第一极可以与降噪电源端耦接,第二开关晶体管k2的第二极可以与至少一个像素02耦接。

126.需要说明的是,结合图5和图9可知,对于图12所示结构而言,第二开关晶体管k2的第一极其实是与降噪电源端vref1耦接,第二开关晶体管k2的第二极其实是与像素02中像素电路021包括的驱动晶体管t2的第一极耦接。结合图6和图10可知,对于图13所示结构而言,第二开关晶体管k2的第一极其实是与降噪电源端vref2耦接,第二开关晶体管k2的第二极其实是与像素02中发光元件022的第二极耦接。

127.以图11所示结构为例,图14示出了再一种显示面板的结构示意图。结合图11,因开关电路03与像素电路021和发光元件022均耦接,故结合图14可以看出,开关电路03可以包括:两个第二开关晶体管k2。

128.其中,该两个第二开关晶体管k2的栅极可以均与第二控制端g_l耦接。该两个第二开关晶体管k2中,一个第二开关晶体管k2的第一极可以与降噪电源端vref1耦接,且该一个第二开关晶体管k2的第二极可以与像素02中像素电路021包括的驱动晶体管t2的第一极耦接。另一个第二开关晶体管k2的第一极可以与降噪电源端vref2耦接,且该另一个第二开关晶体管k2的第二极可以与像素02中发光元件022的第二极耦接。

129.示例的,以第一电位用“1”表示,第二电位用“0”表示为例,表1示出了图12所示结构中,开关电路03可选的几种逻辑状态。表2示出了图13所示结构中,开关电路03可选的几种逻辑状态。其中,“vdd”是指第一电源端v1向驱动晶体管t2的第一极传输的驱动电源信号。“vss”是指第一电源端v1向发光元件022的第二极传输的下拉电源信号。“vref1”是指降噪电源端向驱动晶体管t2的第一极传输的降噪电源信号。“vref2”是指降噪电源端向发光元件022的第二极传输的降噪电源信号。“x禁止”是指禁止开关电路处于该状态下,“floating悬空”是指无输出。

130.表1

131.g_hg_l输出状态10vdd11x禁止01vref101floating悬空

132.表2

[0133][0134][0135]

结合表1,对图12所示电路的驱动原理进行如下说明:

[0136]

在第一控制端g_h提供的第一控制信号的电位为第一电位,且第二控制端g_l提供的第二控制信号的电位为第二电位时,第一开关晶体管k1可以开启,第二开关晶体管k2可以关断。第一电源端v1(即,驱动电源端vdd)可以通过开启的第一开关晶体管k1向驱动晶体管t2的第一极传输第一电源信号(即,驱动电源信号)。

[0137]

在第一控制端g_h提供的第一控制信号的电位为第二电位,且第二控制端g_l提供的第二控制信号的电位为第一电位时,第一开关晶体管k1可以关断,第二开关晶体管k2可以开启。降噪电源端vref1可以通过开启的第二开关晶体管k2向驱动晶体管t2的第一极传输降噪电源信号。

[0138]

结合表2,对图13所示电路的驱动原理进行如下说明:

[0139]

在第一控制端g_h提供的第一控制信号的电位为第一电位,且第二控制端g_l提供的第二控制信号的电位为第二电位时,第一开关晶体管k1可以开启,第二开关晶体管k2可

以关断。第一电源端v1(即,下拉电源端vss)可以通过开启的第一开关晶体管k1向发光元件022的第二极传输第一电源信号(即,下拉电源信号)。

[0140]

在第一控制端g_h提供的第一控制信号的电位为第二电位,且控制第二控制端g_l提供的第二控制信号的电位为第一电位时,第一开关晶体管k1可以关断,第二开关晶体管k2可以开启。降噪电源端vref2可以通过开启的第二开关晶体管k2向发光元件022的第二极传输降噪电源信号。

[0141]

可选的,显示面板可以仅包括:一个开关电路03。该一个开关电路03可以与多个像素02均耦接。如此,可以简化设计,节省成本。上述图2至图14示出的显示面板中,仅以一个开关电路03与两个像素02耦接为例进行说明。

[0142]

可选的,显示面板的尺寸可以大于等于7英寸(inch),且小于等于17inch。显示面板的分辨率可以大于等于250ppi,且小于等于350ppi。

[0143]

可选的,本公开实施例提供的显示面板中,各个晶体管(包括开关晶体管和像素电路中的晶体管)可以均为n型晶体管。且,材料可以为氧化物(oxide)材料。当然,在一些实施例中,各个晶体管也可以均为p型晶体管。或者,部分晶体管为n型晶体管,部分晶体管为p型晶体管。

[0144]

可选的,在本公开实施例记载的开关电路03可以称为功率复用开关(power mux switch),或功率模拟开关(power analog switch)。

[0145]

结合上述实施例可知,通过设置该开关电路03,可以在无需增加像素电路021中晶体管的数量、无需增加驱动晶体管t2的沟道长度、无需设置额外的驱动电路(如,发光控制栅极驱动电路em goa)的前提下,实现多脉冲的pwm调光,有效改善低灰阶展开不良现象。本公开实施例提供的显示面板的分辨率可以较高,边框可以较窄,且goa方案较为简洁。

[0146]

综上所述,本公开实施例提供了一种显示面板,该显示面板包括位于非显示区的开关电路,且该开关电路能够响应于第一控制端提供的第一控制信号,控制第一电源端与像素的通断,在第一电源端与像素导通时,像素能够响应于该第一电源端提供的电源信号发光。如此,可以在不受限于高分辨率的前提下,通过灵活设置第一控制信号的电位,实现对第一电源端和像素通断时长的控制。结合pwm调光原理可知,在对第一电源端和像素通断时长进行灵活控制的前提下,可以确保在显示面板需要显示低灰阶画面时像素也能可靠发光。进而,有效改善了显示面板出现的低灰阶展开不良现象。

[0147]

图15是本公开实施例提供的一种显示面板中开关电路的驱动方法流程图,该方法可以应用于如图1至图14任一所示的开关电路03中。如图15所示,该方法可以包括:

[0148]

步骤1501、在显示阶段,第一控制端提供的第一控制信号的电位为第一电位,开关电路响应于第一控制信号,控制第一电源端与至少一个像素导通。

[0149]

在第一电源端与至少一个像素导通的基础上,第一电源端可以向至少一个像素传输第一电源信号。至少一个像素可以用于响应于栅极驱动端提供的栅极驱动信号,数据信号端提供的数据信号,以及该第一电源端提供的第一电源信号发光。

[0150]

步骤1502、在插黑阶段,第一控制信号的电位为第二电位,开关电路响应于第一控制信号,控制第一电源端与至少一个像素断开连接。

[0151]

可选的,参考图16,方法还可以包括:

[0152]

步骤1503、在插黑阶段,第二控制端提供的第二控制信号的电位为第一电位,开关

电路响应于第二控制信号,控制降噪电源端与至少一个像素导通。

[0153]

在降噪电源端与至少一个像素导通的基础上,降噪电源端可以向至少一个像素传输降噪电源信号。

[0154]

以开关电路包括的开关晶体管均为n型晶体管,且第一电位相对于第二电位为高电位为例,图17示出了显示面板相邻两帧(frame)扫描过程的驱动时序图。参考图17可以看出,第1帧扫描和第2帧扫描均可以包括:显示(即,发光)阶段t01和插黑阶段t02。

[0155]

其中,在显示阶段t01,第一控制端g_h提供的第一控制信号的电位可以为第一电位,第二控制端g_l提供的第二控制信号的电位可以为第二电位。此时,第一开关晶体管k1开启,第二开关晶体管k2关断。

[0156]

在此基础上,对于图12所示结构而言,驱动电源端vdd可以通过开启的第一开关晶体管k1向驱动晶体管t2的第一极传输驱动电源信号。驱动晶体管t2基于该驱动电源信号以及接收到的数据信号,向发光元件022的第一极传输驱动电流,发光元件022响应于该驱动电流和其第二极耦接的下拉电源端vss提供的下拉电源信号发光。对于图13所示结构而言,下拉电源端vss可以通过开启的第一开关晶体管k1向发光元件022的第二极传输下拉电源信号。当驱动晶体管t2基于其第一极耦接的驱动电源端vdd提供的驱动电源信号以及其栅极接收到的数据信号,向发光元件022的第一极传输驱动电流时,发光元件022即可以响应于该驱动电流和下拉电源端vss提供的下拉电源信号发光。对于图14所示结构而言,驱动电源端vdd可以通过开启的第一开关晶体管k1向驱动晶体管t2的第一极传输驱动电源信号,且下拉电源端vss可以通过开启的第一开关晶体管k1向发光元件022的第二极传输下拉电源信号。当驱动晶体管t2基于该驱动电源信号以及其栅极接收到的数据信号,向发光元件022的第一极传输驱动电流时,发光元件022即可以响应于该驱动电流和下拉电源信号发光。

[0157]

在插黑阶段t02,第一控制信号的电位可以为第二电位,第二控制信号的电位可以为第一电位。此时,第一开关晶体管k1关断,第二开关晶体管k2开启。

[0158]

在此基础上,对于图12所示结构而言,降噪电源端vref1可以通过开启的第二开关晶体管k2向驱动晶体管t2的第一极传输降噪电源信号。且因第一开关晶体管k1关断,故驱动电源端vdd无法向驱动晶体管t2的第一极传输驱动电源信号,发光元件022无法发光,从而达到插黑效果。插黑可以理解为显示黑画面或是不显示。对于图13所示结构而言,降噪电源端vref1可以通过开启的第二开关晶体管k2向发光元件022的第二极传输降噪电源信号。且因第一开关晶体管k1关断,故下拉电源端vss无法向发光元件022的第二极传输下拉电源信号,发光元件022无法发光,从而达到插黑效果。对应图14所示结构而言,降噪电源端vref1可以通过开启的第二开关晶体管k2向驱动晶体管t2的第一极传输降噪电源信号,以及向发光元件022的第二极传输降噪电源信号。且因第一开关晶体管k1关断,故驱动电源端vdd无法向驱动晶体管t2的第一极传输驱动电源信号,且下拉电源端vss无法向发光元件022的第二极传输下拉电源信号,发光元件022无法发光,从而达到插黑效果。

[0159]

需要说明的是,图17仅示出了第一控制端g_h的时序。且,图17示出的每帧扫描均包括两次显示阶段t01,以及两次插黑阶段t02。此外,在每两帧扫描之间,还包括补偿阶段t03。该补偿阶段t03中,开关电路03的驱动原理与显示阶段t01相同。在该补偿阶段t03,像素电路021可以执行如上述实施例记载的对数据信号的外部补偿操作。

[0160]

还需要说明的是,对于多行像素02而言,显示阶段t03中,各行像素02可以逐行扫描实现显示,扫描原理可以参考上述对像素电路021工作原理的介绍。结合上述实施例可知,通过设置开关电路03,可以控制显示面板中的多个像素在一帧扫描时间内完成多次发光和不发光的操作。结合pwm调光原理可知,如此,可以通过控制发光的时长和次数,有效减少运动图像响应时间(moving picture response time,mprt),从而改善低灰阶的展开不良现象。

[0161]

综上所述,本公开实施例提供了一种显示面板的驱动方法,该方法中,位于非显示区的开关电路能够响应于第一控制端提供的第一控制信号,控制第一电源端与像素的通断,在第一电源端与像素导通时,像素能够响应于该第一电源端提供的电源信号发光。如此,可以在不受限于高分辨率的前提下,通过灵活设置第一控制信号的电位,实现对第一电源端和像素通断时长的控制。结合pwm调光原理可知,在对第一电源端和像素通断时长进行灵活控制的前提下,可以确保在显示面板需要显示低灰阶画面时像素也能可靠发光。进而,有效改善了显示面板出现的低灰阶展开不良现象。

[0162]

图18是本公开实施例提供的一种显示装置的结构示意图。如图18所示,该显示装置可以包括:驱动电路10,以及如图1至图14任一所示的显示面板00。

[0163]

其中,驱动电路10可以与显示面板00中的第一控制端g_h(图中未示出)耦接,用于向第一控制端g_h提供第一控制信号。此外,驱动电路10还可以与显示面板中的第二控制端g_l(图中未示出)耦接,用于向第二控制端g_l提供第二控制信号。

[0164]

可选的,在本公开实施例中,显示面板中的开关电路03与驱动电路可以集成设置。如此,可以简化布局,节省成本。

[0165]

可选的,显示装置还可以包括源极驱动电路和栅极驱动电路。其中,栅极驱动电路可以分别与显示面板00中,像素电路耦接的栅极驱动端和检测扫描端耦接,栅极驱动电路可以用于向栅极驱动端提供栅极驱动信号,以及向检测扫描端提供检测扫描信号。源极驱动电路可以与显示面板00中,像素电路耦接的数据信号端耦接,源极驱动电路可以用于向数据信号端提供数据信号。

[0166]

在此基础上,上述实施例记载的驱动电路10可以为源极驱动电路。当然,在一些实施例中,驱动电路10还可以为用于控制源极驱动电路工作的时序控制器。本公开实施例对此不做限定。

[0167]

可选的,该显示装置可以为:oled显示装置、有源矩阵有机发光二极管(active

‑

matrix organic light

‑

emitting diode,amoled)显示装置和液晶显示装置等任何具有显示功能的产品或部件。

[0168]

其中,amoled显示装置的功耗小、工作温度范围宽、成本低、对比度高、视角广、色域广且显示面板较薄,可以实现柔性显示,以逐渐成为下一代的显示“皇冠”。oled显示装置可以满足大多数当今信息时代对显示设备高性能和大容量的要求,可用于室内和户外照明,可作为壁纸装饰品,可制成折叠的电子报纸,且还可以应用于手机、平板电脑和可穿戴电子设备等便携式电子产品。

[0169]

可选的,本公开实施例记载的“第一”、“第二”、“第三”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”或者“一”等类似词语也不表示数量限制,而是表示存在至少一个。“包括”或者“包含”等类似的词语意指出

现在“包括”或者“包含”前面的元件或者物件涵盖出现在“包括”或者“包含”后面列举的元件或者物件及其等同,并不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则所述相对位置关系也可能相应地改变。

[0170]

以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1