像素单元及其驱动方法、液晶显示面板与流程

1.本技术涉及显示面板技术领域,特别是涉及一种像素单元及其驱动方法、液晶显示面板。

背景技术:

2.目前,液晶显示器正在向更高解析度,更高显示画质,更大尺寸的方向发展。而tft-lcd(薄膜晶体管液晶显示器)的驱动方式具体为 one-by-one(逐行扫描),扫描信号为高电平时,对应本行tft(薄膜晶体管)被打开,列方向上的数据可写入像素。其中,用于显示的每个子像素包括薄膜晶体管、液晶电容、储存电容以及负责传输开关信号的扫描线和负责传输显示信号的数据线,液晶电容和储存电容的一端为像素电极,而另一端为公共电极。

3.而液晶具体是依靠液晶电容两端的电压不同,以进行不同的旋转,进而使液晶层的透光量不一样的方式进行工作。但在像素中,由于薄膜晶体管的栅极与像素电极的部分区域相对,因此在薄膜晶体管从打开到关断的状态转变过程中,就会在薄膜晶体管的栅极与像素电极之间产生寄生电容,而由于寄生电容的存在,将产生电容耦合效应,进而使像素电极上的实际电压将小于数据理论值,也即像素电极上的像素电压将随之发生一定程度的变化,从而导致相应显示面板的品味下降。

技术实现要素:

4.本技术主要解决的技术问题是提供一种像素单元及其驱动方法、液晶显示面板,以能够解决现有技术中的像素单元由于寄生电容的存在,将产生电容耦合效应,以致相应显示面板的品味下降的问题。

5.为解决上述技术问题,本技术采用的一个技术方案是:提供一种像素单元,包括薄膜晶体管、像素电极以及公共电极,薄膜晶体管的栅极连接一条对应的扫描线以接收对应的扫描信号,其漏极连接一条对应的数据线以接收对应的数据信号,像素电极连接薄膜晶体管的源极,公共电极用于接收公共电压,像素电极、公共电极和两者之间的液晶构成液晶电容,其中,像素单元还包括存储电容,存储电容的第一端连接像素电极,其第二端连接一条对应的辅助扫描线以接收辅助扫描信号,利用辅助扫描信号消除薄膜晶体管的栅极与源极之间的寄生电容引起的像素电极上的像素电压的变化。

6.其中,扫描信号包括表征逻辑高电平的第一电压和表征逻辑低电平的第二电压;辅助扫描信号包括表征逻辑高电平的第三电压和表征逻辑低电平的第四电压;其中,当扫描信号处于表征逻辑高电平的第一电压时,辅助扫描信号处于表征逻辑低电平的第四电压;当扫描信号处于表征逻辑低电平的第二电压时,辅助扫描信号处于表征逻辑高电平的第三电压。

7.其中,辅助扫描信号中第三电压与第四电压之间的差值等于扫描信号中第一电压与第二电压之间的差值乘以寄生电容与存储电容的容值之比,以使寄生电容引起的像素电压的变化趋向于零。

8.其中,当寄生电容的容值与存储电容的容值不相等时,辅助扫描信号中第三电压与第四电压之间的差值不等于扫描信号中第一电压与第二电压之间的差值。

9.其中,当寄生电容的容值与存储电容的容值相等时,辅助扫描信号中第三电压与第四电压之间的差值等于扫描信号中第一电压与第二电压之间的差值。

10.其中,当寄生电容的容值与存储电容的容值相等时,第三电压等于第一电压,第四电压等于第二电压。

11.其中,当寄生电容的容值与存储电容的容值相等时,辅助扫描线通过反相器连接扫描线,以根据扫描信号中的第一电压和第二电压而产生对应的第三电压和第四电压。

12.其中,扫描信号中表征逻辑低电平的第二电压和辅助扫描信号中表征逻辑低电平的第四电压均为公共电压。

13.为解决上述技术问题,本技术采用的又一个技术方案是:提供一种像素单元的驱动方法,像素单元包括薄膜晶体管、像素电极、公共电极以及存储电容,薄膜晶体管的栅极连接一条对应的扫描线,其漏极连接一条对应的数据线以接收对应的数据信号,像素电极连接薄膜晶体管的源极,像素电极、公共电极和两者之间的液晶构成液晶电容,存储电容的第一端连接像素电极,其第二端连接一条对应的辅助扫描线,其中,驱动方法包括:接收扫描线对应发送的扫描信号,以导通薄膜晶体管;接收对应的公共电压和数据线对应发送的数据信号,以基于数据信号分别向像素电极、存储电容、液晶电容以及薄膜晶体管的栅极与源极之间的寄生电容写入相应的电压;接收辅助扫描线对应发送的辅助扫描信号,以利用辅助扫描信号消除寄生电容引起的像素单元中的像素电极上的像素电压的变化,并基于像素电压驱动液晶进行相应的偏转。

14.为解决上述技术问题,本技术采用的又一个技术方案是:提供一种液晶显示面板,包括彩膜基板、阵列基板以及位于彩膜基板与阵列基板之间的液晶盒,其中,该阵列基板上设置有如上任一项所述的像素单元。

15.本技术的有益效果是:区别于现有技术,本技术提供的像素单元包括薄膜晶体管、像素电极、公共电极以及存储电容,其中,存储电容的第一端连接像素电极,其第二端连接一条对应的辅助扫描线,以能够接收辅助扫描信号,并利用辅助扫描信号消除薄膜晶体管的栅极与源极之间的寄生电容引起的像素电极上的像素电压的变化,从而能够有效改善电容耦合效应,进而增加相应液晶显示面板的品味,保证更优质的显示效果,以使该液晶显示面板更具有产品竞争力。

附图说明

16.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,其中:

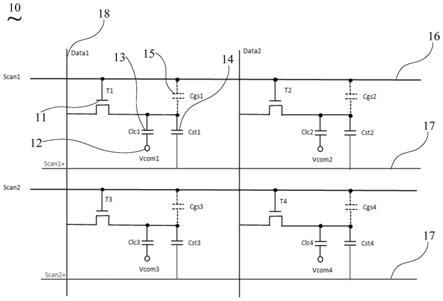

17.图1是本技术像素单元第一实施方式的结构示意图;

18.图2是图1中像素单元中的扫描线和辅助扫描线分别对应接收的扫描信号和辅助扫描信号的波形时序图;

19.图3是本技术像素单元第二实施方式的结构示意图;

20.图4是本技术像素单元的驱动方法一实施方式的流程示意图;

21.图5是本技术液晶显示面板一实施方式的结构示意图。

22.附图标记说明:10/20/311、像素单元;11/21、薄膜晶体管;12/22、公共电极;13/23、液晶电容;14/24、存储电容;15/25、寄生电容;16/26、扫描线;17/27、辅助扫描线;18/28、数据线;29、反相器;31/411、液晶显示面板;41、液晶显示器。

具体实施方式

23.发明人经长期研究发现,液晶显示器与传统的crt和等离子显示器相比的一大优势是省电,通常情况下,液晶显示器只有同尺寸的crt显示器的一半功耗,而相较等离子显示器更是低上很多,与传统crt显示器相比,液晶显示器在环保方面也具有较佳的表现,这是因为液晶显示器内部不存在像crt显示器中的高压元器件,因而将不致于出现由于高压元件所导致的放射性射线超标的情况,液晶显示器的显示区本身根本没有辐射可言,而仅有来自驱动电路的少量电磁波,且只要将外壳严格密封即可有效降低emi(电磁干扰),所以其辐射指标普遍比crt要低一些。

24.液晶显示器可视面积大,且具体是通过显示屏上的电极控制液晶分子的状态来达到显示目的,即使屏幕加大,它的体积也不会成正比的增加,而且在重量上比相同显示面积的传统显示器要轻得多,通常情况下,同尺寸的液晶电视的重量大约是传统电视的1/3,因此液晶显示器又被称为冷显示器或环保显示器,目前lcd(liquid crystal display,液晶显示器)正在向更高解析度,更高显示画质,更大尺寸的方向发展。

25.其中,tft-lcd的驱动方式具体为one-by-one(逐行扫描),比如,以相应的像素单元具体包括多条数据线和多条扫描线为例,进行说明,其中,以扫描线具体用于接收扫描信号,以在该扫描信号为高电平时,对应本行薄膜晶体管tft被打开,而列方向上的数据便可通过相应的数据线写入像素。

26.进一步地,该像素单元还包括有多个子像素单元,而每一子像素单元具体包括控制开关,也即薄膜晶体管t、液晶电容clc、储存电容cst 以及负责传输开关信号的g线(也即扫描线)和负责传输数据信号的s 线(也即数据线),储存电容cst和液晶电容clc的一端为像素电极,而另一端为公共极(vcom)。可理解的是,因为液晶充、放电是电容的基本架构,而如果用dc(直流)电路去驱动,那么电容两端必然会产生遗留电荷,体现在显示上就会有图像残影出现,而为了避免这种现象,便需要将dc电路改为ac(交流)电路,而液晶具体是依靠液晶电容两端的电压不同,以进行不同的旋转,进而使液晶层的透光量不一样的方式进行工作。

27.在每一子像素单元中,由于其中的薄膜晶体管t的栅极与像素电极的部分区域相对,因此在薄膜晶体管t从打开到关断的状态转变过程中,便会在薄膜晶体管t的栅极与像素电极之间产生寄生电容cgs。

28.可理解的是,由于寄生电容cgs的存在,将产生电容耦合效应,比如,在扫描线打开和关闭前后,像素电极上的电压将发生以下变化:

29.当扫描线打开时:电压vg=vgh,q=(vgh-vs)*cgs+

30.(vcom-vs)*(cst+clc);

31.当扫描线关闭时:电压vg=vgl,q=(vgl-vs’)*cgs+

32.(vcom-vs’)*(cst+clc)。

33.其中,vg为薄膜晶体管t的栅极电压,vgh为扫描线接收到的高电平扫描信号的电压,q为像素电极连接的电容cst、clc以及cgs上的总电荷量,vs为高电平扫描信号对应的像素电极电压,vcom为公共电极电压,vgl为扫描线接收到的低电平扫描信号的电压,vs’为低电平扫描信号对应的像素电极电压。

34.由此可知,在不考虑漏电的情况下,薄膜晶体管t关闭之后,像素电极连接的电容cst、clc以及cgs的电荷应该满足电荷守恒原理,因此,若δv=vs-vs’,则由上述计算公式可计算得到:δv=(vgh-vgl)*cgs /(cgs+cst+clc)。

35.因此,像素电极上的实际电压将小于数据理论值,从而导致图像显示品质下降,而发生这个变化根本的原因在于scan线打开关闭前后,电压vg由vgh

→

vgl的变化,而cgs不为零,进而导致δv也不为零。

36.为了改善电容耦合效应,以增加液晶显示面板的品味,保证更优质的显示效果,本技术提供了一种像素单元、液晶显示面板及液晶显示器。下面结合附图和实施例,对本技术作进一步的详细描述。特别指出的是,以下实施例仅用于说明本技术,但不对本技术的范围进行限定。同样的,以下实施例仅为本技术的部分实施例而非全部实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

37.在本技术中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

38.请参阅图1,图1是本技术像素单元第一实施方式的结构示意图。在本实施方式中,该像素单元10包括:薄膜晶体管11、像素电极(图未示出)、公共电极12以及存储电容14。

39.可理解的是,该像素单元10具体包括有多个呈阵列排布的子像素单元,而子像素单元即为相应显示面板中用于实现图像显示的基本功能单元,其中,图1示出的具体为像素单元10中的一部分,而对应包括有4个子像素单元,以方便进行说明。

40.具体地,像素单元10中的薄膜晶体管11的栅极连接有一条对应的扫描线16,以能够通过该扫描线16接收相应显示面板中的驱动电路(图未示出)对应发送的扫描信号,进而能够基于该扫描信号打开或关闭薄膜晶体管11;薄膜晶体管11的漏极进一步连接有一条对应的数据线18,以能够通过该数据线18接收相应显示面板中的驱动电路对应发送的数据信号,进而能够基于该数据信号进行相应的内容显示。

41.其中,像素电极进一步连接薄膜晶体管11的源极,而公共电极12 用于接收公共电压,且像素电极、公共电极12和两者之间的液晶(图未示出)共同构成液晶电容13。

42.可理解的是,由于薄膜晶体管11的栅极与像素电极的部分区域相对,因此在薄膜晶体管11从打开到关断的状态转变过程中,便会在薄膜晶体管11的栅极与像素电极,也即薄膜晶体管11的栅极与其源极之间将产生寄生电容15,而该寄生电容15不可避免的会产生电容耦合效应,从而导致相应显示面板品味的下降。

43.需说明的是,通过对液晶电容13、寄生电容15以及存储电容14的连接关系进行分析可知,液晶电容13两端连接公共电极12和像素电极,两者之间的电压差决定液晶旋转,进而决定显示面板的亮度,而不能进而更改;寄生电容15两端连接扫描线16和像素电极,相应

电压也不能更改;而存储电容14两端对应连接的像素电极和公共电极12,其中与像素电极实现连接的一端的电压不可更改,但是与公共电极12连接的另一端对应的电压却可以进行更改,且当相应进行的更改能够抵消前述提到的δv,也即高电平扫描信号和低电平扫描信号分别对应的像素电极电压vs和vs’之间的差值时,则因扫描线16打开、关闭前后电压变化所造成的电容耦合效应便能够得以改善,甚至直接消除。

44.在本实施例中,具体是将存储电容14的第一端连接像素电极,并将其第二端连接一条对应设置的辅助扫描线17,以能够通过该辅助扫描线17接收对应的辅助扫描信号,并利用该辅助扫描信号消除薄膜晶体管11的栅极与源极之间的寄生电容15所引起的像素电极上的像素电压的变化,也便能够有效改善相应的电容耦合效应。

45.上述方案,通过使存储电容14的第二端连接一条对应的辅助扫描线17,以能够接收辅助扫描信号,并利用辅助扫描信号消除薄膜晶体管 11的栅极与源极之间的寄生电容15引起的像素电极上的像素电压的变化,也即用存储电容14上的电压变化低消寄生电容15上产生的压差变化,从而能够有效改善扫描线16打开、关闭前后电压变化所造成的电容耦合效应,以能够增加相应液晶显示面板的品味,保证更优质的显示效果,以使该液晶显示面板更具有产品竞争力。

46.在一实施例中,如图2所示,图2是图1中像素单元10中的扫描线16和辅助扫描线17分别对应接收的扫描信号和辅助扫描信号的波形时序图,则可知,扫描线16对应接收的扫描信号具体包括表征逻辑高电平(“1”)的第一电压(vgh)和表征逻辑低电平(“0”)的第二电压(vgl),而辅助扫描信号具体包括表征逻辑高电平的第三电压 (vgh’)和表征逻辑低电平的第四电压(vgl’)。

47.其中,扫描信号和辅助扫描信号还满足特定的对应关系,比如,当扫描信号处于表征逻辑高电平的第一电压时,辅助扫描信号处于表征逻辑低电平的第四电压;而当扫描信号处于表征逻辑低电平的第二电压时,辅助扫描信号处于表征逻辑高电平的第三电压。

48.可理解的是,为方便理解,如图1所示,以数据线18为data1,扫描线16对应接收的扫描信号为scan1,而辅助扫描线17对应接收的辅助扫描信号为scan1+,薄膜晶体管11具体为t1,液晶电容13为clc1,存储电容14为cst1,寄生电容15为cgs1为例,进行说明:

49.当scan1为vgh的时候,t1将打开,而data1将给clc1充电;则 scan1+此时为vgl’,scan1与scan1+时序如图2所示,其电压高低时序刚好相反;

50.当scan1为vgl的时候,t1关闭,cst1、clc1以及cgs1满足电荷共享;此时scan1+为vgh’;

51.且scan1在由vgh转变为vgl的整个阶段,cgs1两端的电压差δvg=vgh-vgl;而cst1两端的电压差δv=vgh

’‑

vgl’;

52.当假设scan1为vgh时,像素电极的电压为vs,而scan1为vgl 时,像素电极的电压为vs’;

53.则scan1为vgh时,q=(vgh-vs)*cgs1+(vcom-vs)*clc1+ (vgl

’‑

vs)cst1;

54.而scan1为vgl时,q=(vgl-vs’)*cgs1+(vcom-vs’)*clc1+ (vgh

’‑

vs’)cst1;

55.其中,q为像素电极连接的电容cst1、clc1以及cgs1上的总电荷量,vcom为公共电极12的电压;

56.基于电荷守恒原理对上述计算等式进行分析,则可知,若需要vs=vs’时,也即

scan1在由vgh转变为vgl,相应的像素电极的电压不发生变化时,则δv=vgh

’‑

vgl’=(vgh-vgl)cgs1/cst1,而相应的电容耦合效应也将得以解决。

57.可理解的是,上述逻辑推导过程具体可对应像素单元10中的一个子像素单元,而其他子像素单元均与之类同,在此不再一一赘述。

58.通过上述分析可知,在辅助扫描信号中第三电压与第四电压之间的差值具体等于扫描信号中第一电压与第二电压之间的差值乘以寄生电容15与存储电容14的容值之比时,便能够对应使寄生电容15引起的像素电压的变化,也即vs与vs’的差值趋向于零,而有效改善,甚至消除寄生电容15所产生的电容耦合效应。

59.在一实施例中,当寄生电容15的容值与存储电容14的容值不相等时,则相应的辅助扫描信号中第三电压与第四电压之间的差值不等于扫描信号中第一电压与第二电压之间的差值,比如,当cgs1≠cst1时, vgh-vgl将也不等于vgh

’‑

vgl’。

60.在一实施例中,扫描信号中表征逻辑低电平的第二电压和辅助扫描信号中表征逻辑低电平的第四电压均为公共电压。

61.请参阅图3,图3是本技术像素单元第二实施例的结构示意图。本实施方式与本技术提供的像素单元第一实施方式的区别在于,像素单元 20中的寄生电容25的容值与存储电容24的容值相等。

62.同样地,如图3所示,以数据线28为data1,扫描线26对应接收的扫描信号为scan1,而辅助扫描线27对应接收的辅助扫描信号为 scan1+,薄膜晶体管21为t1,液晶电容23为clc1,存储电容24为cst1,寄生电容25为cgs1为例,则可知,

63.当scan1为vgh的时候,t1将打开,而data1将给clc1充电;则 scan1+此时为vgl’,scan1与scan1+时序如图2所示,其电压高低时序刚好相反;

64.当scan1为vgl的时候,t1关闭,cst1、clc1以及cgs1满足电荷共享;此时scan1+为vgh’;

65.且scan1在由vgh转变为vgl的整个阶段,cgs1两端的电压差δvg=vgh-vgl;而cst1两端的电压差δv=vgh

’‑

vgl’;

66.当假设scan1为vgh时,像素电极的电压为vs,而scan1为vgl 时,像素电极的电压为vs’;

67.则scan1为vgh时,q=(vgh-vs)*cgs1+(vcom-vs)*clc1+ (vgl

’‑

vs)cst1;

68.而scan1为vgl时,q=(vgl-vs’)*cgs1+(vcom-vs’)*clc1+ (vgh

’‑

vs’)cst1;

69.其中,q为像素电极连接的电容cst1、clc1以及cgs1上的总电荷量,vcom为公共电极22的电压;

70.基于电荷守恒原理对上述计算等式进行分析,则可知,当寄生电容 25的容值与存储电容24的容值相等,也即cgs1=cst1时,则对应有: vgh-vgl-2vs=vgh

’‑

vgh

’‑

2vs’,也即在辅助扫描信号中第三电压与第四电压之间的差值等于扫描信号中第一电压与第二电压之间的差值时,便可得到vs=vs’,也即scan1在由vgh转变为vgl,相应的像素电极的电压将不发生变化,而由寄生电容25对应产生的电容耦合效应也将得以改善,甚至消除。

71.在一实施例中,当寄生电容25的容值与存储电容24的容值相等时,第三电压具体是等于第一电压,而第四电压等于第二电压。

72.在一实施例中,当寄生电容25的容值与存储电容24的容值相等时,辅助扫描线27

具体是通过反相器29,也即非门连接扫描线26,以能够通过对扫描信号中的第一电压和第二电压进行反相处理后,使辅助扫描线27对应产生第三电压和第四电压,而无需另外再单独在相应的驱动电路为辅助扫描线27增加设置一路辅助扫描信号的输送回路,从而能够尽可能的降低相应显示面板的制造成本。

73.需说明的是,非门又称非电路、反相器29、倒相器、逻辑否定电路,简称非门,是逻辑电路的基本单元。非门有一个输入和一个输出端。当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。也就是说,输入端和输出端的电平状态总是反相的。非门的逻辑功能相当于逻辑代数中的非电路功能相当于反相,这种运算亦称非运算。

74.可理解的是,在本实施例中,薄膜晶体管21、公共电极22、液晶电容23、扫描线26、辅助扫描线27以及数据线28分别与薄膜晶体管 11、公共电极12、液晶电容13、扫描线16、辅助扫描线17以及数据线 18相同,具体请参阅图1和图2及相关文字内容,在此不再赘述。

75.本技术还提供了一种像素单元的驱动方法,请参阅图4,图4是本技术像素单元的驱动方法一实施方式的流程示意图。本实施方式包括如下步骤:

76.s31:接收扫描线对应发送的扫描信号,以导通薄膜晶体管。

77.可理解的是,该驱动方法具体是一像素单元所对应的驱动方法,其中,该像素单元具体包括薄膜晶体管、像素电极、公共电极以及存储电容,薄膜晶体管的栅极连接一条对应的扫描线,其漏极连接一条对应的数据线以接收对应的数据信号,像素电极连接薄膜晶体管的源极,像素电极、公共电极和两者之间的液晶构成液晶电容,存储电容的第一端连接像素电极,其第二端连接一条对应的辅助扫描线。

78.具体地,像素单元接收相应显示面板的驱动电路通过扫描线对应发送的扫描信号,以在该扫描信号为高电平时,导通像素单元中的薄膜晶体管。

79.s32:接收对应的公共电压和数据线对应发送的数据信号,以基于数据信号分别向像素电极、存储电容、液晶电容以及薄膜晶体管的栅极与源极之间的寄生电容写入相应的电压。

80.进一步地,像素单元通过其公共电极接收对应的公共电压,并相应显示面板的驱动电路通过数据线对应发送的数据信号,以基于该数据信号分别向像素单元中的像素电极、存储电容、液晶电容以及薄膜晶体管的栅极与源极之间的寄生电容写入相应的电压。

81.s33:接收辅助扫描线对应发送的辅助扫描信号,以利用辅助扫描信号消除寄生电容引起的像素单元中的像素电极上的像素电压的变化,并基于像素电压驱动液晶进行相应的偏转。

82.又进一步地,像素单元接收辅助扫描线对应发送的辅助扫描信号,以利用辅助扫描信号消除寄生电容引起的像素单元中的像素电极上的像素电压的变化,并基于像素电压驱动液晶进行相应的偏转。

83.可理解的是,该辅助扫描信号具体可以与扫描信号同时发送给像素单元,以在通过辅助扫描信号消除寄生电容相应产生的电容耦合效应时,便能够增加相应液晶显示面板的品味,保证其具有更优质的显示效果,并使该液晶显示面板更具有产品竞争力。

84.需说明的是,本实施方式所阐述的像素单元具体可以为上述实施例中任一项所阐述的像素单元10或像素单元20,并由此还能够衍生出其他更具体的驱动方法,具体请参阅

图1-图3及相关文字内容,在此就不再赘述。

85.本技术还提供了一种液晶显示面板,请参阅图5,图5是本技术液晶显示面板一实施方式的结构示意图。在本实施方式中,该液晶显示面板包括彩膜基板411、阵列基板412以及位于彩膜基板411与阵列基板 412之间的液晶盒413,其中,该阵列基板412上还设置有像素单元414。

86.需说明的是,本实施方式所阐述的像素单元414为上述实施例中任一项所阐述的像素单元10或像素单元20,具体请参阅图1-图3及相关文字内容,在此就不再赘述。

87.本技术的有益效果是:区别于现有技术,本技术提供的像素单元包括薄膜晶体管、像素电极、公共电极以及存储电容,其中,存储电容的第一端连接像素电极,其第二端连接一条对应的辅助扫描线,以能够接收辅助扫描信号,并利用辅助扫描信号消除薄膜晶体管的栅极与源极之间的寄生电容引起的像素电极上的像素电压的变化,从而能够有效改善电容耦合效应,进而增加相应液晶显示面板的品味,保证更优质的显示效果,以使该液晶显示面板更具有产品竞争力。

88.以上所述仅为本技术的实施方式,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1