移位寄存器、扫描驱动电路及其驱动方法和显示装置与流程

1.本发明涉及显示技术领域,尤其涉及一种移位寄存器、扫描驱动电路及其驱动方法和显示装置。

背景技术:

2.扫描驱动电路为显示装置中的重要组成部分。扫描驱动电路可以包括多级级联的移位寄存器,每一级移位寄存器可以与显示装置中的至少一行走线电连接电连接。扫描驱动电路可以向显示装置中的多条走线(例如栅线或使能信号线等)中逐行输入扫描信号,以使得显示装置能够进行画面显示。

3.在显示装置中设置扫描驱动电路,能够有效降低成本、提高良率。

技术实现要素:

4.本发明提供一种移位寄存器、扫描驱动电路及其驱动方法和显示装置,可以解决显示画面亮度不均的问题。

5.为达到上述目的,本发明采用如下技术方案:

6.本发明的第一方面提供了一种移位寄存器,移位寄存器包括第一扫描单元和插黑电路。

7.所述第一扫描单元包括第一输入电路和第一输出电路。所述第一输入电路与显示输入信号端及第一上拉节点电连接;所述第一输入电路被配置为,响应于在所述显示输入信号端处接收的显示输入信号,将所述显示输入信号传输至所述第一上拉节点;所述第一输出电路与所述第一上拉节点、第一时钟信号端及第一扫描信号端电连接;所述第一输出电路被配置为,在所述第一上拉节点的电压的控制下,将在所述第一时钟信号端处接收的第一时钟信号传输至所述第一扫描信号端。

8.所述插黑电路包括第一插黑子电路和第二插黑子电路。所述第一插黑子电路与第一控制信号端、第一插黑级联信号端、第二控制信号端、第一插黑输入信号端、所述第一上拉节点及第一电压信号端电连接。所述第一插黑子电路被配置为,在所述第一控制信号端所传输的第一控制信号、所述第一插黑级联信号端所传输的第一插黑级联信号及所述第二控制信号端所传输的第二控制信号的控制下,将在所述第一插黑输入信号端处接收的第一插黑输入信号传输至所述第一上拉结点。所述第二插黑子电路与第五控制信号端、第二插黑级联信号端、第六控制信号端、第二插黑输入信号端、所述第一上拉节点及第一电压信号端电连接;所述第二插黑子电路被配置为,在所述第五控制信号端所传输的第五控制信号、所述第二插黑级联信号端所传输的第二插黑级联信号及所述第六控制信号端所传输的第六控制信号的控制下,将在所述第二插黑输入信号端处接收的第二插黑输入信号传输至所述第一上拉结点。

9.在一些实施例中,所述第一插黑子电路包括第一插黑控制子电路、第一插黑输入子电路和第一插黑传输子电路。所述第一插黑控制子电路与所述第一控制信号端、所述第

一插黑级联信号端、所述第一电压信号端及第一插黑节点电连接;所述第一插黑控制子电路被配置为,在所述第一控制信号的控制下,将所述第一插黑级联信号传输至所述第一插黑节点;所述第一插黑输入子电路与所述第一插黑节点、所述第一插黑输入信号端及第二插黑节点电连接;所述第一插黑输入子电路被配置为,在所述第一插黑节点的电压的控制下,将所述第一插黑输入信号传输至所述第二插黑节点;所述第一插黑传输子电路与所述第二控制信号端、所述第二插黑节点及所述第一上拉结点电连接;所述第一插黑传输子电路被配置为,在所述第二控制信号的控制下,将来自所述第二插黑节点的所述第一插黑输入信号传输至所述第一上拉结点。

10.所述第二插黑子电路包括第二插黑控制子电路、第二插黑输入子电路和第二插黑传输子电路;所述第二插黑控制子电路与所述第五控制信号端、所述第二插黑级联信号端、所述第一电压信号端及所述第一插黑节点电连接;所述第二插黑控制子电路被配置为,在所述第五控制信号的控制下,将所述第二插黑级联信号传输至所述第一插黑节点;所述第二插黑输入子电路与所述第一插黑节点、第二插黑输入信号端及第三插黑节点电连接;所述第二插黑输入子电路被配置为,在所述第一插黑节点的电压的控制下,将所述第二插黑输入信号传输至所述第三插黑节点;所述第二插黑传输子电路与所述第六控制信号端、所述第三插黑节点及所述第一上拉结点电连接;所述第二插黑传输子电路被配置为,在所述第六控制信号的控制下,将来自所述第三插黑节点的所述第二插黑输入信号传输至所述第一上拉结点。

11.在一些实施例中,所述移位寄存器还包括第二扫描单元。所述第二扫描单元包括第二输入电路和第二输出电路。所述第二输入电路与所述显示输入信号端及第二上拉节点电连接;所述第二输入电路被配置为,响应于所述显示输入信号,将所述显示输入信号传输至所述第二上拉节点。所述第二输出电路与所述第二上拉节点、第二时钟信号端及第二扫描信号端电连接;所述第二输出电路被配置为,在所述第二上拉节点的电压控制下,将在所述第二时钟信号端处接收的第二时钟信号传输至所述第二扫描信号端。所述第一插黑子电路还与所述第二上拉节点电连接;所述第一插黑子电路还被配置为,在将所述第一插黑输入信号传输至所述第一上拉结点的同时,将所述第一插黑输入信号传输至所述第二上拉节点。所述第二插黑子电路还与所述第二上拉节点电连接;所述第二插黑子电路还被配置为,在将所述第二插黑输入信号传输至所述第一上拉结点的同时,将所述第二插黑输入信号传输至所述第二上拉节点。

12.在一些实施例中,所述第一插黑子电路还包括第三插黑传输子电路。所述第三插黑传输子电路与所述第二控制信号端、所述第二插黑节点及所述第二上拉结点电连接;所述第三插黑传输子电路被配置为,在所述第二控制信号的控制下,将来自所述第二插黑节点的所述第一插黑输入信号传输至所述第二上拉结点。所述第二插黑子电路还包括第四插黑传输子电路。所述第四插黑传输子电路与所述第六控制信号端、所述第三插黑节点及所述第二上拉结点电连接;所述第四插黑传输子电路被配置为,在所述第六控制信号的控制下,将来自所述第三插黑节点的所述第二插黑输入信号传输至所述第二上拉结点。

13.在一些实施例中,所述第一插黑输入子电路和所述第二插黑输入子电路为同一子电路,所述第一插黑输入信号端与所述第二插黑输入信号端为同一信号端,所述第二插黑节点与所述第三插黑节点为同一节点。所述第一插黑传输子电路和所述第二插黑传输子电

路为同一子电路,所述第二控制信号端与所述第六控制信号端为同一信号端。所述第三插黑传输子电路和所述第四插黑传输子电路为同一子电路。

14.在一些实施例中,所述第一输入电路包括第一晶体管。所述第一晶体管的控制极与所述显示输入信号端电连接,所述第一晶体管的第一极与所述显示输入信号端电连接,所述第一晶体管的第二极与所述第一上拉节点电连接。所述第一输出电路包括第二晶体管和第一电容。所述第二晶体管的控制极与所述第一上拉节点电连接,所述第二晶体管的第一极与第一时钟信号端电连接,所述第二晶体管的第二极与所述第一扫描信号端电连接。所述第一电容的第一端与所述第一上拉节点电连接,所述第一电容的第二端与所述第一扫描信号端电连接。所述第一插黑子电路包括第一插黑控制子电路、第一插黑输入子电路和第一插黑传输子电路,所述第一插黑控制子电路包括第三晶体管和第二电容。所述第三晶体管的控制极与所述第一控制信号端电连接,所述第三晶体管的第一极与所述第一插黑级联信号端电连接,所述第三晶体管的第二极与所述第一插黑节点电连接。所述第二电容的第一端与所述第一插黑节点电连接,所述第二电容的第二端与所述第一电压信号端电连接。所述第一插黑输入子电路包括第四晶体管。所述第四晶体管的控制极与所述第一插黑节点电连接,所述第四晶体管的第一极与所述第一插黑输入信号端电连接,所述第四晶体管的第二极与所述第二插黑节点电连接。所述第一插黑传输子电路包括第五晶体管。所述第五晶体管的控制极与所述第二控制信号端电连接,所述第五晶体管的第一极与所述第二插黑节点电连接,所述第五晶体管的第二极与所述第一上拉结点电连接。所述第二插黑子电路包括第二插黑控制子电路、第二插黑输入子电路和第二插黑传输子电路,所述第二插黑控制子电路包括第七晶体管和所述第二电容。所述第七晶体管的控制极与所述第五控制信号端电连接,所述第七晶体管的第一极与所述第二插黑级联信号端电连接,所述第七晶体管的第二极与所述第一插黑节点电连接。所述第二插黑输入子电路包括第八晶体管。所述第八晶体管的控制极与所述第一插黑节点电连接,所述第八晶体管的第一极与所述第二插黑输入信号端电连接,所述第八晶体管的第二极与所述第三插黑节点电连接。所述第二插黑传输子电路包括第九晶体管。所述第九晶体管的控制极与所述第六控制信号端电连接,所述第九晶体管的第一极与所述第三插黑节点电连接,所述第九晶体管的第二极与所述第一上拉结点电连接。所述移位寄存器还包括第二扫描单元,所述第二扫描单元的第二输入电路与所述显示输入信号端及第二上拉节点电连接。所述第二输入电路包括第十晶体管。所述第十晶体管的控制极与所述显示输入信号端电连接,所述第十晶体管的第一极与所述显示输入信号端电连接,所述第十晶体管的第二极与所述第二上拉节点电连接。所述第二输出电路包括第十一晶体管和第三电容。所述第十一晶体管的控制极与所述第二上拉节点电连接,所述第十一晶体管的第一极与所述第二时钟信号端电连接,所述第十一晶体管的第二极与所述第二扫描信号端电连接。所述第三电容的第一端与所述第二上拉节点电连接,所述第三电容的第二端与所述第二时钟信号端电连接;所述第一插黑子电路还包括第三插黑传输子电路,所述第三插黑传输子电路包括第十二晶体管。所述第十二晶体管的控制极与所述第二控制信号端电连接,所述第十二晶体管的第一极与所述第二插黑节点电连接,所述第十二晶体管的第二极与所述第二上拉结点电连接。所述第二插黑子电路还包括第四插黑传输子电路,所述第四插黑传输子电路包括第十三晶体管。所述第十三晶体管的控制极与所述第六控制信号端电连接,所述第十三晶体管的第一极与所述第三插黑节点

电连接,所述第十三晶体管的第二极与所述第二上拉结点电连接。

15.在一些实施例中,所述第一输出电路还与第五时钟信号端及第一移位信号端电连接;所述第一输出电路还被配置为,在所述第一上拉节点的电压控制下,将在所述第五时钟信号端处接收的第五时钟信号传输至所述第一移位信号端。所述移位寄存器还包括第二扫描单元,所述第二扫描单元的第二输入电路与所述显示输入信号端及第二上拉节点电连接;所述第二输出电路还与第六时钟信号端及第二移位信号端电连接;所述第二输出电路还被配置为,在所述第二上拉节点的电压控制下,将在所述第六时钟信号端处接收的第六时钟信号传输至所述第二移位信号端。

16.在一些实施例中,所述第一输出电路还包括第十六晶体管。所述第十六晶体管的控制极与所述第一上拉节点电连接,所述第十六晶体管的第一极与所述第五时钟信号端电连接,所述第十六晶体管的第二极与所述第一移位信号端电连接。所述第二输出电路还包括第十七晶体管。所述第十七晶体管的控制极与所述第二上拉节点电连接,所述第十七晶体管的第一极与所述第六时钟信号端电连接,所述第十七晶体管的第二极与所述第二移位信号端电连接。

17.在一些实施例中,所述第一输出电路还与第三时钟信号端及第一感测信号端电连接;所述第一输出电路还被配置为,在所述第一上拉节点的电压控制下,将在所述第三时钟信号端处接收的第三时钟信号传输至所述第一感测信号端。所述第二输出电路还与第四时钟信号端及第二感测信号端电连接;所述第二输出电路还被配置为,在所述第二上拉节点的电压控制下,将在所述第四时钟信号端处接收的第四时钟信号传输至所述第二感测信号端。

18.在一些实施例中,所述第一输出电路还包括第十四晶体管和第四电容。所述第十四晶体管的控制极与所述第一上拉节点电连接,所述第十四晶体管的第一极与所述第三时钟信号端电连接,所述第十四晶体管的第二极与所述第一感测信号端电连接。所述第四电容的第一端与所述第一上拉节点电连接,所述第四电容的第二端与所述第一感测信号端电连接。所述第二输出电路还包括第十五晶体管和第五电容。所述第十五晶体管的控制极与所述第二上拉节点电连接,所述第十五晶体管的第一极与所述第四时钟信号端电连接,所述第十五晶体管的第二极与所述第二感测信号端电连接。所述第五电容的第一端与所述第二上拉节点电连接,所述第五电容的第二端与所述第二感测信号端电连接。

19.在一些实施例中,所述第一扫描单元还包括第一复位电路和第二复位电路。所述第一复位电路与第一复位信号端、所述第一上拉节点及所述第一电压信号端电连接;所述第一复位电路被配置为,在所述第一复位信号端所传输的第一复位信号的控制下,将在所述第一电压信号端处接收的第一电压信号传输至所述第一上拉节点。所述插黑电路包括第一插黑控制子电路和第二插黑控制子电路,所述第二复位电路与第二复位信号端、所述第一插黑节点、所述第一上拉节点及所述第一电压信号端电连接;所述第二复位电路被配置为,在所述第一插黑节点的电压及所述第二复位信号端所传输的第二复位信号的控制下,将所述第一电压信号传输至所述第一上拉节点。所述移位寄存器还包括第二扫描单元,所述第二扫描单元的第二输入电路与所述显示输入信号端及第二上拉节点电连接。所述第二扫描单元还包括第三复位电路和第四复位电路;所述第三复位电路与所述第一复位信号端、所述第二上拉节点及所述第一电压信号端电连接;所述第三复位电路被配置为,在所述

第一复位信号的控制下,将所述第一电压信号传输至所述第二上拉节点。所述第四复位电路与所述第二复位信号端、所述第一插黑节点、所述第二上拉节点及所述第一电压信号端电连接;所述第四复位电路被配置为,在所述第一插黑节点的电压及所述第二复位信号的控制下,将所述第一电压信号传输至所述第二上拉节点。

20.在一些实施例中,所述第一复位电路包括第十八晶体管。所述第十八晶体管的控制极与所述第一复位信号端电连接,所述第十八晶体管的第一极与所述第一上拉节点电连接,所述第十八晶体管的第二极与所述第一电压信号端电连接。所述第二复位电路包括第十九晶体管和第二十晶体管。所述第十九晶体管的控制极与所述第一插黑节点电连接,所述第十九晶体管的第一极与所述第一上拉节点电连接,所述第十九晶体管的第二极与所述第二十晶体管的第一极电连接。所述第二十晶体管的控制极与所述第二复位信号端电连接,所述第二十晶体管的第二极与第一电压信号端电连接。所述第三复位电路包括第二十一晶体管。所述第二十一晶体管的控制极与所述第一复位信号端电连接,所述第二十一晶体管的第一极与所述第二上拉节点电连接,所述第二十一晶体管的第二极与所述第一电压信号端电连接。所述第四复位电路包括第二十二晶体管和第二十三晶体管。所述第二十二晶体管的控制极与所述第一插黑节点电连接,所述第二十二晶体管的第一极与所述第二上拉节点电连接,所述第二十二晶体管的第二极与所述第二十三晶体管的第二极电连接。所述第二十三晶体管的控制极与所述第二复位信号端电连接,所述第二十三晶体管的第二极与所述第一电压信号端电连接。

21.在一些实施例中,所述第一扫描单元还包括第一控制电路,与所述第一上拉节点、第一下拉节点、所述第一电压信号端及第二电压信号端电连接;所述第一控制电路被配置为,响应于在所述第二电压信号端处接收的第二电压信号,将所述第二电压信号传输至所述第一下拉节点,并且,在所述第一上拉节点的电压的控制下,将所述第一电压信号端处接收的第一电压信号传输至所述第一下拉节点。所述移位寄存器还包括第二扫描单元,所述第二扫描单元的第二输入电路与所述显示输入信号端及第二上拉节点电连接。所述第二扫描单元还包括第二控制电路,与所述第二上拉节点、第二下拉节点、所述第一电压信号端及第三电压信号端电连接;所述第二控制电路被配置为,响应于在所述第三电压信号端处接收的第三电压信号,将所述第三电压信号传输至所述第二下拉节点,并且,在所述第二上拉节点的电压的控制下,将所述第一电压信号传输至所述第二下拉节点。

22.在一些实施例中,所述第一控制电路包括第二十四晶体管、第二十五晶体管、第二十六晶体管和第二十七晶体管。所述第二十四晶体管的控制极与所述第二电压信号端电连接,所述第二十四晶体管的第一极与所述第二电压信号端电连接,所述第二十四晶体管的第二极与所述第二十五晶体管的控制极及所述第二十六晶体管的第一极电连接。所述第二十五晶体管的第一极与所述第二电压信号端电连接,所述第二十五晶体管的第二极与所述第一下拉节点电连接。所述第二十六晶体管的控制极与所述第一上拉节点电连接,所述第二十六晶体管的第二极与所述第一电压信号端电连接。所述第二十七晶体管的控制极与所述第一上拉节点电连接,所述第二十七晶体管的第一极与所述第一下拉节点电连接,所述第二十七晶体管的第二极与所述第一电压信号端电连接;所述第二控制电路包括第二十八晶体管、第二十九晶体管、第三十晶体管和第三十一晶体管。所述第二十八晶体管的控制极与所述第三电压信号端电连接,所述第二十八晶体管的第一极与所述第三电压信号端电连

接,所述第二十八晶体管的第二极与所述第二十九晶体管的控制极及所述第三十晶体管的第一极电连接。所述第二十九晶体管的第一极与所述第三电压信号端电连接,所述第二十九晶体管的第二极与所述第二下拉节点电连接。所述第三十晶体管的控制极与所述第二上拉节点电连接,所述第三十晶体管的第二极与所述第一电压信号端电连接。所述第三十一晶体管的控制极与所述第二上拉节点电连接,所述第三十一晶体管的第一极与所述第二下拉节点电连接,所述第三十一晶体管的第二极与所述第一电压信号端电连接。

23.在一些实施例中,所述第一扫描单元还包括第五复位电路和第六复位电路。所述第五复位电路与所述第一上拉节点、所述第一下拉节点及所述第一电压信号端电连接;所述第五复位电路被配置为,在所述第一下拉节点的电压的控制下,将所述第一电压信号传输至所述第一上拉节点。所述第六复位电路与所述第一下拉节点、所述第一扫描信号端及第四电压信号端电连接;所述第六复位电路被配置为,在所述第一下拉节点的电压的控制下,将所述第四电压信号端处接收的第四电压信号传输至所述第一扫描信号端。所述第一输出电路还与第三时钟信号端及第一感测信号端电连接,所述第六复位电路还与所述第一感测信号端电连接;所述第六复位电路还被配置为,在所述第一下拉节点的电压的控制下,将所述第四电压信号传输至所述第一感测信号端。所述第一输出电路还与第五时钟信号端及第一移位信号端电连接,所述第六复位电路还与所述第一移位信号端及所述第一电压信号端电连接;所述第六复位电路还被配置为,在所述第一下拉节点的电压的控制下,将所述第一电压信号传输至所述第一移位信号端。所述移位寄存器还包括第二扫描单元,所述第二扫描单元的第二输入电路与所述显示输入信号端及第二上拉节点电连接。所述第二扫描单元还包括:第七复位电路和第八复位电路。所述第七复位电路与所述第二上拉节点、所述第二下拉节点及所述第一电压信号端电连接;所述第七复位电路被配置为,在所述第二下拉节点的电压的控制下,将所述第一电压信号传输至所述第二上拉节点。所述第八复位电路与所述第二下拉节点、所述第二扫描信号端及第四电压信号端电连接;所述第八复位电路被配置为,在所述第二下拉节点的电压的控制下,将所述第四电压信号传输至所述第二扫描信号端。所述第二输出电路还与第四时钟信号端及第二感测信号端电连接,所述第八复位电路还与所述第二感测信号端电连接;所述第八复位电路还被配置为,在所述第二下拉节点的电压的控制下,将所述第四电压信号传输至所述第二感测信号端。所述第二输出电路还与第六时钟信号端及第二移位信号端电连接,所述第八复位电路还与所述第二移位信号端及所述第一电压信号端电连接;所述第八复位电路还被配置为,在所述第二下拉节点的电压的控制下,将所述第一电压信号传输至所述第二移位信号端。

24.在一些实施例中,所述第五复位电路包括第三十二晶体管。所述第三十二晶体管的控制极与所述第一下拉节点电连接,所述第三十二晶体管的第一极与所述第一上拉节点电连接,所述第三十二晶体管的第二极与所述第一电压信号端电连接。所述第六复位电路包括第三十三晶体管、第三十四晶体管和第三十五晶体管。所述第三十三晶体管的控制极与所述第一下拉节点电连接,所述第三十三晶体管的第一极与所述第一扫描信号端电连接,所述第三十三晶体管的第二极与所述第四电压信号端电连接。所述第三十四晶体管的控制极与所述第一下拉节点电连接,所述第三十四晶体管的第一极与所述第一感测信号端电连接,所述第三十四晶体管的第二极与所述第四电压信号端电连接。所述第三十五晶体管的控制极与所述第一下拉节点电连接,所述第三十五晶体管的第一极与所述第一移位信

号端电连接,所述第三十五晶体管的第二极与所述第一电压信号端电连接。所述第七复位电路包括第三十六晶体管。所述第三十六晶体管的控制极与所述第二下拉节点电连接,所述第三十六晶体管的第一极与所述第二上拉节点电连接,所述第三十六晶体管的第二极与所述第一电压信号端电连接。所述第八复位电路包括第三十七晶体管、第三十八晶体管和第三十九晶体管。所述第三十七晶体管的控制极与所述第二下拉节点电连接,所述第三十七晶体管的第一极与所述第二扫描信号端电连接,所述第三十七晶体管的第二极与第四电压信号端电连接。所述第三十八晶体管的控制极与所述第二下拉节点电连接,所述第三十八晶体管的第一极与所述第二感测信号端电连接,所述第三十八晶体管的第二极与所述第四电压信号端电连接。所述第三十九晶体管的控制极与所述第二下拉节点电连接,所述第三十九晶体管的第一极与所述第二移位信号端电连接,所述第三十九晶体管的第二极与所述第一电压信号端电连接。

25.本发明的第二方面提供了一种扫描驱动电路,所述扫描驱动电路包括如上所述的多级级联的移位寄存器。

26.在一些实施例中,多级所述移位寄存器包括多个移位寄存器组。所述移位寄存器包括第一扫描单元和第二扫描单元,所述第一插黑输入子电路和所述第二插黑输入子电路非同一子电路,所述第一插黑传输子电路和所述第二插黑传输子电路非同一子电路,所述第三插黑传输子电路和所述第四插黑传输子电路非同一子电路,每个移位寄存器组包括2级移位寄存器。第一个移位寄存器组所包括的2级移位寄存器为虚设移位寄存器。从第一个移位寄存器组开始,每相邻两个移位寄存器组为一对移位寄存器组,多个移位寄存器组被划分为交替排列的多个第一对移位寄存器组和多个第二对移位寄存器组。从第二个移位寄存器组开始,每相邻两个移位寄存器组为一对移位寄存器组,多个移位寄存器组被划分为交替排列的多个第三对移位寄存器组和多个第四对移位寄存器组。所述扫描驱动电路还包括第一控制信号线组,包括第一子控制信号线和第三子控制信号线;所述第一子控制信号线与所述第三对移位寄存器组中各移位寄存器的第一控制信号端电连接,第三子控制信号线与所述第四对移位寄存器组中各移位寄存器的第一控制信号端电连接。第二控制信号线组包括第二子控制信号线和第四子控制信号线;所述第二子控制信号线与所述第三对移位寄存器组中各移位寄存器的第二控制信号端电连接,第四子控制信号线与所述第四对移位寄存器组中各移位寄存器的第二控制信号端电连接。第三控制信号线组包括第五子控制信号线和第七子控制信号线;所述第五子控制信号线与所述第一对移位寄存器组中各移位寄存器的第五控制信号端电连接,第七子控制信号线与所述第二对移位寄存器组中各移位寄存器的第五控制信号端电连接。第四控制信号线组包括第六子控制信号线和第八子控制信号线;所述第六子控制信号线与所述第一对移位寄存器组中各移位寄存器的第六控制信号端电连接,第八子控制信号线与所述第二对移位寄存器组中各移位寄存器的第六控制信号端电连接。第一时钟信号线组包括十六个第一时钟信号线;所述十六个第一时钟信号线分别与所述第三对移位寄存器组中各移位寄存器的第一时钟信号端及第二时钟信号端、所述第四对移位寄存器组中各移位寄存器的第一时钟信号端及第二时钟信号端电连接。第一虚设时钟信号线组包括四个第一虚设时钟信号线;所述四个第一虚设时钟信号线分别与第一个移位寄存器组中的各虚设移位寄存器的第一时钟信号端及第二时钟信号端电连接。

27.在一些实施例中,所述第二子控制信号线还与所述第三对移位寄存器组中各移位

寄存器的第一插黑输入信号端电连接。所述第四子控制信号线还与所述第四对移位寄存器组中各移位寄存器的第一插黑输入信号端电连接。所述第六子控制信号线还与所述第一对移位寄存器组中各移位寄存器的第二插黑输入信号端电连接。所述第八子控制信号线还与所述第二对移位寄存器组中各移位寄存器的第二插黑输入信号端电连接。

28.在一些实施例中,所述移位寄存器的第一输出电路还与第三时钟信号端及第一感测信号端电连接、第二输出电路还与第四时钟信号端及第二感测信号端电连接,所述扫描驱动电路还包括第二时钟信号线组。所述第二时钟信号线组,包括十六个第二时钟信号线;所述十六个第二时钟信号线分别与所述第三对移位寄存器组中各移位寄存器的第三时钟信号端及第四时钟信号端、所述第四对移位寄存器组中各移位寄存器的第三时钟信号端及第四时钟信号端电连接。所述扫描驱动电路还包括第二虚设钟信号线组。所述第二虚设钟信号线组包括四个第二虚设钟信号线;所述四个第二虚设钟信号线分别与第一个移位寄存器组中的各虚设移位寄存器的第三时钟信号端及第四时钟信号端电连接。所述移位寄存器的第一输出电路还与第五时钟信号端及第一移位信号端电连接、第二输出电路还与第六时钟信号端及第二移位信号端电连接,所述扫描驱动电路还包括第三时钟信号线组。所述第三时钟信号线组包括十六个第三时钟信号线;所述十六个第三时钟信号线分别与所述第三对移位寄存器组中各移位寄存器的第五时钟信号端及第六时钟信号端、所述第四对移位寄存器组中各移位寄存器的第五时钟信号端及第六时钟信号端电连接。所述扫描驱动电路还包括第三虚设时钟信号线组。第三虚设时钟信号线组,包括四个第三虚设时钟信号线,所述四个第三虚设时钟信号线分别与第一个移位寄存器组中的各虚设移位寄存器的第五时钟信号端及第六时钟信号端电连接。

29.在一些实施例中,多级所述移位寄存器中,除前两级移位寄存器外,其余级移位寄存器的显示输入信号端,与比该级移位寄存器靠前两级的移位寄存器的第二移位信号端电连接。除前四级移位寄存器外,其余级移位寄存器的所述第一插黑级联信号端、所述第二插黑级联信号端,与比该级移位寄存器靠前四级的移位寄存器的第一移位信号端电连接。其中,前六级移位寄存器的所述第一插黑级联信号端、所述第二插黑级联信号端与第二起始信号线电连接。或者,第一级至第四级的移位寄存器的所述第一插黑级联信号端、所述第二插黑级联信号端与第二起始信号线电连接;第三级至第六级的移位寄存器的所述第一插黑级联信号端、第所述二插黑级联信号端与第三起始信号线电连接。

30.在一些实施例中,以所述第一时钟信号线组的十六个第一时钟信号线,以及与该第一时钟信号线组相连接的相邻的第三对移位寄存器组和第四对移位寄存器组为一个连接周期,在一个连接周期内,所述第一时钟信号线组的十六个第一时钟信号线与其连接的各级移位寄存器之间的连接线逐渐缩短。除第三对移位寄存器组中第一个移位寄存器与第一时钟信号线连接的连接线外,第三对移位寄存器组中的各移位寄存器与对应的第一时钟信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与对应的第一时钟信号线连接的连接线上分别连接有补偿电阻。所述扫描驱动电路还包括第二时钟信号线组,所述第二时钟信号线组包括十六个第二时钟信号线。以所述第二时钟信号线组的十六个第二时钟信号线,以及与该第二时钟信号线组相连接的相邻的第三对移位寄存器组和第四对移位寄存器组相连接为一个连接周期,在一个连接周期内,所述第二时钟信号线组的十六个第二时钟信号线与其连接的各移位寄存器之间的连接线逐渐缩短。除第三对移位寄存器

组中第一级移位寄存器与第二时钟信号线连接的连接线外,第三对移位寄存器组中的各移位寄存器与对应的第二时钟信号线连接的连接线上、第四对移位寄存器组中的各移位寄存器与对应的第二时钟信号线连接的连接线上分别连接有补偿电阻。

31.在一些实施例中,第三对移位寄存器组中的各移位寄存器与第一时钟信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与第一时钟信号线连接的连接线上的补偿电阻的电阻值依次增大。第三对移位寄存器组中的各移位寄存器与第二时钟信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与第二时钟信号线连接的连接线上的补偿电阻的电阻值依次增大。

32.在一些实施例中,以所述第一时钟信号线组的十六个第一时钟信号线,以及与该第一时钟信号线组相连接的相邻的第三对移位寄存器组和第四对移位寄存器组相连接为一个连接周期,在一个连接周期内,所述第一时钟信号线组的十六个第一时钟信号线与其连接的各级移位寄存器之间的连接线逐渐缩短。除第三对移位寄存器组中第一级移位寄存器与第一扫描信号线连接的连接线外,第三对移位寄存器组中的各移位寄存器与对应的第一扫描信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与对应的第一扫描信号线连接的连接线上分别连接有补偿电阻。所述扫描驱动电路还包括第二时钟信号线组,所述第二时钟信号线组包括十六个第二时钟信号线。以所述第二时钟信号线组的十六个第二时钟信号线,以及与该第二时钟信号线组相连接的相邻的第三对移位寄存器组和第四对移位寄存器组相连接为一个连接周期,在一个连接周期内,所述第二时钟信号线组的十六个第二时钟信号线与其连接的各级移位寄存器之间的连接线逐渐缩短。除第三对移位寄存器组中第一级移位寄存器与第二扫描信号线连接的连接线外,第三对移位寄存器组中的各移位寄存器与对应的第二扫描信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与对应的第二扫描信号线连接的连接线上分别连接有补偿电阻。

33.在一些实施例中,第三对移位寄存器组中的各移位寄存器与第一扫描信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与第一扫描信号线连接的连接线上的补偿电阻的电阻值依次增大。第三对移位寄存器组中的各移位寄存器与第二扫描信号线连接的连接线上、以及第四对移位寄存器组中的各移位寄存器与第二扫描信号线连接的连接线上的补偿电阻的电阻值依次增大。

34.在一些实施例中,所述扫描驱动电路还包括多个第一补偿电容,每个第一补偿电容的一端,与一级移位寄存器连接第一时钟信号线的连接线,电连接,所述第一补偿电容的另一端接地。所述多个第一补偿电容的电容值大致相等。所述扫描驱动电路还包括第二时钟信号线组,所述第二时钟信号线组包括十六个第二时钟信号线。所述扫描驱动电路还包括多个第二补偿电容,每个第二补偿电容的一端,与一级移位寄存器连接第二时钟信号线的连接线,电连接,所述第二补偿电容的另一端接地。所述多个补偿电容的电容值大致相等。

35.在一些实施例中,所述扫描驱动电路还包括多个第三补偿电容,每个第三补偿电容的一端,与一级移位寄存器连接第一扫描信号线的连接线电连接,所述第三补偿电容的另一端接地。所述多个第三补偿电容的电容值大致相等。所述扫描驱动电路还包括第二时钟信号线组,所述第二时钟信号线组包括十六个第二时钟信号线。所述扫描驱动电路还包括多个第四补偿电容,每个第四补偿电容的一端,与一级移位寄存器连接第二扫描信号线

的连接线电连接,所述第四补偿电容的另一端接地。所述多个第四补偿电容的电容值大致相等。

36.本发明的第三方面提供了一种扫描驱动电路的驱动方法,应用于上述的扫描驱动电路,扫描驱动电路的驱动过程包括交替设置的第一帧扫描周期和第二帧扫描周期。在所述第一帧扫描周期中,第三对移位寄存器组和第四对移位寄存器组在所述第一上拉结点和所述第二上拉结点接收所述第一插黑输入信号的控制下,交替输出显示黑画面的扫描驱动信号;所述显示黑画面的扫描驱动信号包括第三对移位寄存器组中的各移位寄存器同时输出的一组扫描驱动信号,以及第四对移位寄存器组中的各移位寄存器同时输出的一组扫描驱动信号。在第二帧显示图像中,第一对移位寄存器组和第二对移位寄存器组在所述第一上拉结点和所述第二上拉结点接收所述第二插黑输入信号的控制下,交替输出显示黑画面的扫描驱动信号;所述显示黑画面的扫描驱动信号包括第一对移位寄存器组中的各移位寄存器同时输出的一组扫描驱动信号,以及第二对移位寄存器组中的各移位寄存器同时输出的一组扫描驱动信号。

37.本发明的第四方面提供了一种显示装置,所述显示装置包括多行子像素,以及上述的扫描驱动电路。其中,所述扫描驱动电路中的一级移位寄存器与至少一行子像素电连接。

38.本发明所提供的移位寄存器、扫描驱动电路及其驱动方法和显示装置,通过设置第一插黑子电路和第二插黑子电路,控制相邻显示的两帧图像采用不同的插黑级联方式,实现缩小相邻行显示时长差的目的,使得相邻行显示时间差肉眼不可见,消除亮度差异产生的横纹问题,提高产品的良率。

附图说明

39.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

40.图1为本发明一些实施例所提供的一种显示装置的结构图;

41.图2为本发明一些实施例所提供的另一种显示装置的结构图;

42.图3为本发明一些实施例所提供的又一种显示装置的结构图;

43.图4为本发明一些实施例所提供的一种子像素的电路图;

44.图5为本发明一些实施例所提供的一种对应于图4所示子像素的时序图;

45.图6为本发明一些实施例所提供的另一种对应于图4所示子像素的时序图;

46.图7为相关技术中的扫描驱动电路的插黑的时序控制图;

47.图8为本发明一些实施例所提供的扫描驱动电路的插黑的时序控制图;

48.图9为本发明一些实施例所提供的一种移位寄存器的结构图;

49.图10为本发明一些实施例所提供的另一种移位寄存器的结构图;

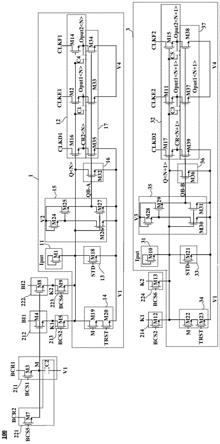

50.图11为本发明一些实施例所提供的一种移位寄存器的电路图;

51.图12a为本发明一些实施例所提供的又一种移位寄存器的结构图;

52.图12b为本发明一些实施例所提供的又一种移位寄存器的结构图;

53.图13a为本发明一些实施例所提供的另一种移位寄存器的电路图;

54.图13b为本发明一些实施例所提供的又一种移位寄存器的电路图;

55.图14为本发明一些实施例所提供的又一种移位寄存器的结构图;

56.图15为本发明一些实施例所提供的又一种移位寄存器的电路图;

57.图16为本发明一些实施例所提供的又一种移位寄存器的结构图;

58.图17为本发明一些实施例所提供的又一种移位寄存器的电路图;

59.图18为本发明一些实施例所提供的又一种移位寄存器的结构图;

60.图19a为本发明一些实施例所提供的又一种移位寄存器的电路图;

61.图19b为本发明一些实施例所提供的又一种移位寄存器的电路图;

62.图20为本发明一些实施例所提供的一种扫描驱动电路的第一对移位寄存器组、第二对移位寄存器组、第三对移位寄存器组和第四对移位寄存器组的结构图;

63.图21为本发明一些实施例所提供的一种扫描驱动电路的部分结构图;

64.图22为本发明一些实施例所提供的另一种扫描驱动电路的部分结构图;

65.图23为本发明一些实施例所提供的又一种扫描驱动电路的部分结构图;

66.图24为本发明一些实施例所提供的又一种扫描驱动电路的部分结构图;

67.图25为本发明一些实施例所提供的又一种扫描驱动电路的部分结构图;

68.图26为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

69.图27为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

70.图28为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

71.图29为本发明一些实施例所提供的对应于图26所示的扫描驱动电路的时序控制图;

72.图30为本发明一些实施例所提供的另一种对应于图26所示的扫描驱动电路的时序控制图;

73.图31为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

74.图32为本发明一些实施例所提供的另一种子像素的电路图;

75.图33为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

76.图34为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

77.图35为本发明一些实施例所提供的对应图33和图34所示的扫描驱动电路的一种移位寄存器的电路图;

78.图36为本发明一些实施例所提供的对应图33和图34所示的扫描驱动电路的又一种移位寄存器的电路图;

79.图37为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

80.图38为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

81.图39为本发明一些实施例所提供的对应图37和图38所示的扫描驱动电路的一种移位寄存器的电路图;

82.图40为本发明一些实施例所提供的对应图37和图38所示的扫描驱动电路的又一种移位寄存器的电路图;

83.图41为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

84.图42为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

85.图43为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

86.图44为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

87.图45为本发明一些实施例所提供的又一种扫描驱动电路的结构图;

88.图46为本发明一些实施例所提供的对应图45所示的扫描驱动电路的一种移位寄存器的电路图。

具体实施方式

89.为使本发明的上述目的、特征和优点能够更加明显易懂,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,均属于本发明保护的范围。

90.术语“第一”、“第二”等可以用于描述各种部件,但是部件不受限于该术语。术语仅用于将一个部件与其它部件进行区分。

91.在描述一些实施例时,可能使用了“连接”及其衍伸的表达。例如,描述一些实施例时可能使用了术语“连接”以表明两个或两个以上部件彼此间有物理接触或电接触。这里所公开的实施例并不必然限制于本文内容。

92.另外,在一些实施例中,“电连接”可以表示为直接电连接,也可以表示为间接电连接。

93.本文中“适用于”或“被配置为”的使用意味着开放和包容性的语言,其不排除适用于或被配置为执行额外任务或步骤的设备。

94.本公开的实施例提供的电路中所采用的晶体管可以为薄膜晶体管、场效应晶体管(例如氧化物薄膜晶体管)或其他特性相同的开关器件,本公开的实施例中均以薄膜晶体管为例进行说明。

95.在一些实施例中,移位寄存器所采用的各晶体管的控制极为晶体管的栅极,第一极为晶体管的源极和漏极中一者,第二极为晶体管的源极和漏极中另一者。由于晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的,也就是说,本公开的实施例中的晶体管的第一极和第二极在结构上可以是没有区别的。示例性的,在晶体管为p型晶体管的情况下,晶体管的第一极为源极,第二极为漏极;示例性的,在晶体管为n型晶体管的情况下,晶体管的第一极为漏极,第二极为源极。

96.在本公开的实施例提供的电路中,上拉节点和下拉节点等节点并非表示实际存在的部件,而是表示电路图中相关电连接的汇合点,也就是说,这些节点是由电路图中相关电连接的汇合点等效而成的节点。

97.在本公开的实施例中,术语“上拉”表示对一个节点或一个晶体管的一个电极进行充电,以使得该节点或该电极的电平的绝对值升高,从而实现相应晶体管的操作(例如导通)。术语“下拉”表示对一个节点或一个晶体管的一个电极进行放电,以使得该节点或该电极的电平的绝对值降低,从而实现相应晶体管的操作(例如截止)。

98.下面,在本公开的实施例提供的电路中,以晶体管均以n型晶体管为例进行说明。

99.本公开的一些实施例提供了一种移位寄存器100、扫描驱动电路1000及其驱动方

法和显示装置2000。以下对移位寄存器100、扫描驱动电路1000及其驱动方法和显示装置2000分别进行介绍。

100.本公开的一些实施例提供一种显示装置2000,如图1所示,该显示装置2000可以是显示不论运动(例如,视频)还是固定(例如,静止图像)的且不论文字还是图像的任何装置。更明确地说,预期所述实施例可实施在多种电子装置中或与多种电子装置关联,所述多种电子装置例如(但不限于)移动电话、无线装置、个人数据助理(pda)、手持式或便携式计算机、gps接收器/导航器、相机、mp4视频播放器、摄像机、游戏控制台、手表、时钟、计算器、电视监视器、平板显示器、计算机监视器、汽车显示器(例如,里程表显示器等)、导航仪、座舱控制器和/或显示器、相机视图的显示器(例如,车辆中后视相机的显示器)、电子相片、电子广告牌或指示牌、投影仪、建筑结构、包装和美学结构(例如,对于一件珠宝的图像的显示器)等。

101.在一些示例中,上述显示装置2000可以包括框架、设置于框架内的显示面板、电路板、显示驱动ic(integrated circuit,集成电路)以及其他电子配件等。

102.上述显示面板的类型包括多种,可以根据实际需要选择设置。

103.示例性的,上述显示面板可以为:有机发光二极管(organic light emitting diode,简称oled)显示面板、量子点发光二极管(quantum dot light emitting diodes,简称qled)显示面板、微发光二极管(micro light emitting diodes,简称micro led)显示面板等,本公开对此不做具体限定。

104.下面以上述显示面板为oled显示面板(也即显示装置2000为oled显示装置)为例,对本公开的一些实施例进行示意性说明。

105.在一些实施例中,如图2和图3所示,上述显示装置2000的显示面板具有显示区a,以及设置在显示区a旁侧的边框区b。其中,“旁侧”指的是显示区a的一侧、两侧、三侧或者周侧等,也即,边框区b可以位于显示区a的一侧、两侧或三侧,或者,边框区b可以围绕显示区a设置。

106.在一些实施例中,如图2和图3所示,上述显示装置2000可以包括:衬底200、多个子像素p及扫描驱动电路1000。该衬底200用于承载该多个子像素p和扫描驱动电路1000。

107.示例性的,如图2所示,扫描驱动电路1000可以位于边框区b。当然,扫描驱动电路1000也可以设置在其他位置,本公开对此不做限定。

108.此处,扫描驱动电路1000例如可以为发光控制电路,也可以为栅极驱动电路。其中,本公开以扫描驱动电路1000为栅极驱动电路为例进行示意性说明。

109.上述衬底200的类型包括多种,可以根据实际需要选择设置。

110.示例性的,衬底200可以为刚性衬底。该刚性衬底例如可以为玻璃衬底或pmma(polymethyl methacrylate,聚甲基丙烯酸甲酯)衬底等。

111.示例性的,衬底200可以为柔性衬底。该柔性衬底例如可以为pet(polyethylene terephthalate,聚对苯二甲酸乙二醇酯)衬底、pen(polyethylene naphthalate two formic acid glycol ester,聚萘二甲酸乙二醇酯)衬底或pi(polyimide,聚酰亚胺)衬底等。此时,显示装置2000可以为柔性显示面板。

112.示例性的,如图2和图3所示,上述多个子像素p可以位于显示区a内。其中,该多个子像素p例如可以沿第一方向x排列为多行,沿第二方向y排列为多列。其中,每行子像素p可

以包括多个子像素p,每列子像素p可以包括多个子像素p。

113.此处,第一方向x和第二方向y相互交叉。第一方向x和第二方向y之间的夹角可以根据实际需要选择设置。示例性的,第一方向x和第二方向y之间的夹角可以为85

°

、89

°

或90

°

等。

114.在一些示例中,如图2和图3所示,上述显示装置2000还可以包括:设置在衬底200的一侧、且位于显示区a的多条栅线gl以及多条数据线dl。其中,该多条栅线gl沿第一方向x延伸,该多条数据线dl沿第二方向y延伸。

115.示例性的,如图2所示,可以将沿第一方向x排列成一行的子像素p称为同一行子像素p,将沿第二方向y排列成一列的子像素p称为同一列子像素p。同一行子像素p可以与两条栅线gl(第一扫描信号线gl1和第二扫描信号线gl2)电连接,同一列子像素p可以与一条数据线dl电连接。

116.示例性的,如图3所示,同一行子像素p可以与一条栅线gl(第一扫描信号线gl1)电连接,同一列子像素p可以与一条数据线dl电连接。

117.在一些示例中,如图4所示,上述多个子像素p中,每个子像素p可以包括像素驱动电路p1及与该像素驱动电路p1电连接的发光器件p2。该发光器件可以为oled。

118.上述像素驱动电路p1的结构包括多种,可以根据实际需要选择设置。例如,像素驱动电路p1的结构可以包括“3t1c”、“6t1c”、“7t1c”、“6t2c”或“7t2c”等结构。其中,“t”表示为晶体管,位于“t”前面的数字表示为晶体管的数量,“c”表示为存储电容器,位于“c”前面的数字表示为存储电容器的数量。

119.此处,在显示装置2000使用的过程中,像素驱动电路p1中的晶体管及发光器件p2的稳定性可能会下降(例如驱动晶体管的阈值电压漂移),影响显示装置2000的显示效果,这样便需要对子像素p进行补偿。

120.对子像素p进行补偿的方式可以包括多种,可以根据实际需要选择设置。例如,可以在子像素p中设置像素补偿电路,以利用该像素补偿电路对子像素p进行内部补偿。又如,可以通过子像素p内部的晶体管对驱动晶体管或发光器件进行感测,并将感测到的数据传输到外部感应电路,以利用该外部感应电路计算需要补偿的驱动电压值并进行反馈,从而实现对子像素p的外部补偿。

121.本公开以采用外部补偿的方式(对驱动晶体管进行感测),且像素驱动电路采用“3t1c”的结构为例,对子像素p的结构及工作过程进行示意性说明。

122.示例性的,如图4所示,像素驱动电路p1可以包括:开关晶体管t1、驱动晶体管t2、感测晶体管t3和存储电容器cst。

123.例如,如图4所示,开关晶体管t1的控制极与第一栅极信号端g1电连接,开关晶体管t1的第一极与数据信号端data电连接,开关晶体管t1的第二极与第一节点g电连接。其中,开关晶体管t1被配置为,响应于在第一栅极信号端g1处接收的第一扫描信号线gl1传输的第一扫描信号,将在数据信号端data处接收的数据信号传输至第一节点g。

124.此处,数据信号例如包括插黑数据信号和显示数据信号。其中,插黑数据信号用在插黑时段,显示数据信号用在显示时段。关于显示时段和插黑时段,可以参照下面一些实施例中的说明,此处不再赘述。

125.例如,如图4所示,驱动晶体管t2的控制极与第一节点g电连接,驱动晶体管t2的第

一极与第六电压信号端elvdd电连接,驱动晶体管t2的第二极与第二节点s电连接。其中,驱动晶体管t2被配置为,在第一节点g的电压的控制下导通,根据所述第一节点g的电压及在第六电压信号端elvdd处接收的第六电压信号,生成驱动信号,并将所述驱动信号传输至第二节点s。

126.例如,如图4所示,存储电容器cst的第一端与第一节点g电连接,存储电容器cst的第二端与第二节点s电连接。其中,开关晶体管t1在对第一节点g进行充电的过程中,同时对存储电容器cst进行充电。

127.例如,如图4所示,发光器件p2的阳极与第二节点s电连接,发光器件p2的阴极与第七电压信号端elvss电连接。发光器件p2被配置为,在所述驱动信号的驱动下,进行发光。

128.例如,如图4所示,感测晶体管t3的控制极与第二栅极信号端g2电连接,感测晶体管t3的第一极与第二节点s电连接,感测晶体管t3的第二极与感测信号端sense电连接。其中,感测晶体管t3被配置为,响应于在第二栅极信号端g2处接收第二扫描信号线gl2传输的第二扫描信号,检测驱动晶体管t2的电特性以实现外部补偿。

129.需要说明的是,一帧的显示阶段1f例如可以包括依次进行的显示时段1f1和插黑时段1f2。

130.在一帧显示阶段1f中的显示时段1f1,如图5所示,子像素p的工作过程例如可以包括:复位阶段t1、数据写入阶段t2和发光阶段t3。

131.在复位阶段t1中,第一扫描信号的电平为高电平,数据信号端的电平例如为低电平,第二扫描信号的电平为高电平,感测信号端sense提供复位信号的电平为低电平。开关晶体管t1在第一扫描信号的控制下导通,接收数据信号,并将该数据信号传输至第一节点g,对第一节点g进行复位。感测晶体管t3在第二扫描信号的控制下导通,接收复位信号,并将该复位信号传输至第二节点s,对第二节点s进行复位。

132.在数据写入阶段t2中,第一扫描信号的电平为高电平,数据信号(也即显示数据信号)的电平为高电平。开关晶体管t1在第一扫描信号的控制下保持导通状态,接收显示数据信号,并将该显示数据信号传输至第一节点g,同时对存储电容器cst进行充电。

133.在发光阶段t3中,第一扫描信号的电平为低电平,第二扫描信号的电平为低电平,第六电压信号的电平为高电平。开关晶体管t1在第一扫描信号的控制下关断,感测晶体管t3在第二扫描信号的控制下关断。存储电容器cst开始放电,使得第一节点g的电压保持为高电平。驱动晶体管t2在第一节点g的电压的控制下导通,接收第六电压信号,并生成驱动信号,将该驱动信号传输至第二节点s,驱动发光器件p2进行发光。

134.在一帧显示阶段1f中的插黑时段1f2,子像素p的工作过程例如可以包括插黑数据写入的第一阶段t4和插黑显示的第二阶段t5。

135.在第一阶段t4中,第一扫描信号的电平可以为高电平,开关晶体管t1在第一扫描信号的控制下导通,将低电平或较低电平的数据信号传输至第一节点g,第二扫描信号的电平可以为高电平,感测晶体管t3传输低电平或较低电平的数据信号传输至第二节点s,使得vgs小于vth,进而使得驱动晶体管t2关断,使得子像素p停止发光,切换为黑画面。

136.或者,如图6所示,第一扫描信号的电平可以为高电平,开关晶体管t1在第一扫描信号的控制下导通,将低电平或较低电平的数据信号传输至第一节点g,而第二扫描信号的电平可以为低电平,感测晶体管t3关断,使得vgs小于vth,进而使得驱动晶体管t2关断,使

得子像素p停止发光,切换为黑画面。

137.在第二阶段t5中,为黑画面显示的保持阶段。

138.在相关技术中,通过将一帧的显示阶段1f划分为显示时段1f1和插黑时段1f2,消除动态画面切换的过程中产生的图像拖影现象,避免观看者感受到上一帧的画面拖影。然而,发明人发现,将栅线进行分组进行插黑显示的过程中,会引起不同组的栅线控制的子像素的显示时长存在较大时间差,进而导致显示画面亮度不均的问题。

139.在一些示例中,如图7所示,以八条栅线作为一组进行说明,g1《1》~g1《8》表示第一条至第八条第一扫描信号线gl1传输的扫描信号,每组栅线控制的八行子像素在对应的八条第一扫描信号线gl1的控制下逐行打开(g1《1》~g1《8》的扫描信号的电平依次出现高电平),写入显示数据信号,进而子像素中发光器件发光,实现显示,在该八行子像素显示过程中,在同一时刻,八条第一扫描信号线gl1控制八行子像素同时再次打开(g1《1》~g1《8》的扫描信号的电平同时为高电平,同时,对于g1《1》~g1《8》控制的八行子像素称为输入了插黑信号),该八行子像素同时切换为黑画面,称为八行子像素同时插黑。例如,同时插黑的子像素的行为1-8八行子像素、9-16八行子像素、17-24八行子像素

……

。第一组的第1行至第8行子像素相比,其显示时长是逐行减少一行写入显示数据的时长,显示时长为自显示数据信号写入之后发光器件的发光时长,即每个扫描信号的显示数据信号写入的高电平与相邻的下一个高电平之间的时段。假设第8行子像素的显示时长为t,每一行子像素的写入显示数据的时长为a,则在第一帧显示图像中,第一行至第八行子像素显示时长依次为t+7a、t+6a、t+5a、t+4a、t+3a、t+2a、t+1a、t,而在第二帧显示图像时,第一行至第八行子像素显示时长依然是依次为t+7a、t+6a、t+5a、t+4a、t+3a、t+2a、t+1a、t,那么,在两帧图像中,第8行子像素显示时长为2t,而第9行子像素显示时长与第1行子像素显示时长相同,均为2t+14a,这就导致相邻的两行子像素即第9行子像素比第8行子像素显示时长大14a,相邻两行子像素在显示时长上的差值较大会引起肉眼可见的图像亮度不均的问题,这样每隔8行子像素就会出现一个分界形成全屏横纹,影响产品的良率。

140.本公开所提供的显示装置2000中扫描驱动电路采用两级插黑控制电路,即第一插黑子电路21和第二插黑子电路22,将相邻两帧图像显示采用不同的插黑级联方式来实现,示例性的,将原本固定的8行插黑进行拆分每隔一帧出现一次,在第二帧图像中同时插黑的栅线组与第一帧图像中同时插黑的栅线组不一致,缩小相邻行显示时长差,使得相邻行显示时间差肉眼不可见,消除亮度差异产生的横纹。

141.在一些实施例中,如图8所示,以八行栅线控制的八行子像素作为一组进行说明,在第一帧图像中,同时输入插黑信号的八行子像素为1-8八行子像素、9-16八行子像素、17-24八行子像素

……

,在第二帧图像中,同时输入插黑信号的八行子像素为1-4四行子像素(及前四行dum子像素,具体内容如下所述,此处不再赘述)、5-12八行子像素、13-20八行子像素

……

。在第一帧显示图像中,第一组中第1行至第8行子像素相比,其显示时长是逐行减少一行写入显示数据的时长,假设第8行子像素的显示时长为t,每一行写入显示数据的时长为a,则在第一帧显示图像中,第一行至第八行子像素显示时长依次为t+7a、t+6a、t+5a、t+4a、t+3a、t+2a、t+1a、t。而在第二帧显示图像时,第4行子像素的显示时长为t,第一组子像素中第1行至第8行子像素显示时长依次为t+3a、t+2a、t+a、t、t+7a、t+6a、t+5a、t+4a,这样第一组子像素的1-8行子像素两帧叠加后显示时长依次为t+10a、t+8a、t+6a、t+4a、t+10a、t

+8a、t+6a、t+4a,相邻行子像素(第四行子像素和第五行子像素)显示时长差最大为6a,6a远小于传统架构的14a,实现缩小相邻行子像素显示时长差的目的。

142.在一些实施例中,上述扫描驱动电路1000与上述多个子像素p位于衬底200的同一侧。该扫描驱动电路1000可以包括多级级联的移位寄存器100。一级移位寄存器100例如可以与至少一行子像素p(也即子像素p中的像素驱动电路p1)电连接。

143.需要说明的是,在一帧的显示阶段中,第一栅极信号端g1所传输的第一扫描信号和第二栅极信号端g2所传输的第二扫描信号均由扫描驱动电路1000提供。也即,扫描驱动电路1000中的每个移位寄存器100可以通过第一扫描信号线与第一栅极信号端g1电连接,通过该第一扫描信号线向第一栅极信号端g1传输第一扫描信号,并通过第二扫描信号线与第二栅极信号端g2电连接,通过该第二扫描信号线向第二扫描信号端g2传输第二扫描信号。

144.在一些示例中,如图3所示,同一行子像素p中的多个像素驱动电路p1也可以与同一条栅线gl电连接。在此情况下,上述第一扫描信号和第二扫描信号相同。扫描驱动电路1000中的每个移位寄存器1可以通过相应的栅线gl与第一栅极信号端g1及第二栅极信号端g2电连接,并通过该栅线gl向第一栅极信号端g1及第二栅极信号端g2传输扫描信号。

145.基于此,如图20~图30所示,本公开的一些实施例提供一种扫描驱动电路1000,该扫描驱动电路1000包括多级级联的移位寄存器100。其中,该移位寄存器100应用于上述显示装置2000中,每级移位寄存器100与至少一行子像素p电连接。

146.在一些实施例中,如图9所示,移位寄存器包括第一扫描单元1和插黑电路2。

147.在一些示例中,如图9所示,第一扫描单元1包括第一输入电路11和第一输出电路12,第一输入电路11与显示输入信号端iput及第一上拉节点q《n》电连接;第一输入电路11被配置为,响应于在显示输入信号端iput处接收的显示输入信号,将显示输入信号传输至第一上拉节点q《n》。

148.示例性的,在显示输入信号的电平为高电平的情况下,第一输入电路11可以在显示输入信号的作用下导通,接收并传输显示输入信号至第一上拉节点q《n》,对第一上拉节点q《n》进行充电,使得第一上拉节点q《n》的电压升高。

149.在一些示例中,如图9所示,第一输出电路12与第一上拉节点q《n》、第一时钟信号端clke1及第一扫描信号端oput1《n》电连接。第一输出电路12被配置为,在第一上拉节点q《n》的电压的控制下,将在第一时钟信号端clke1处接收的第一时钟信号传输至第一扫描信号端oput1《n》,驱动上述至少一行子像素p进行图像显示。

150.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通,将在第一时钟信号端clke1处接收的第一时钟信号传输至第一扫描信号端oput1《n》,并将第一时钟信号作为第一扫描信号,从第一扫描信号端oput1《n》输出。

151.在此情况下,相同行子像素p中的多个像素驱动电路p1可以与同一条第一扫描信号线gl1电连接。一个移位寄存器100的第一扫描信号端oput1《n》则可以通过该第一扫描信号线gl1与相应行子像素p中多个像素驱动电路p1的第一栅极信号端g1电连接。第一扫描信号端oput1《n》所输出的第一扫描信号也便可以经该第一扫描信号线gl1传输至该多个像素驱动电路p1的第一栅极信号端g1。

152.在一些实施例中,如图9所示,插黑电路2包括第一插黑子电路21和第二插黑子电路22。

153.在一些示例中,如图9所示,第一插黑子电路21与第一控制信号端bcs1、第一插黑级联信号端bcr1、第二控制信号端bcs2、第一插黑输入信号端bi1、第一上拉节点q《n》及第一电压信号端v1电连接,第一插黑子电路21被配置为,在第一控制信号端bcs1所传输的第一控制信号、第一插黑级联信号端bcr1所传输的第一插黑级联信号及第二控制信号端bcs2所传输的第二控制信号的控制下,将在第一插黑输入信号端bi1处接收的第一插黑输入信号传输至第一上拉结点q《n》。

154.示例性的,在第一控制信号的电平为高电平、第一插黑级联信号的电平为高电平且第二控制信号的电平为高电平的情况下,第一插黑子电路21可以在第一控制信号、第一插黑级联信号及第二控制信号的控制下导通,接收第一插黑输入信号,并将该第一插黑输入信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行充电,使得第一上拉节点q《n》的电压升高。

155.示例性的,输出电路12还被配置为,在第一插黑子电路21将第一插黑输入信号传输至第一上拉节点q《n》的情况下,在第一上拉节点q《n》的电压的控制下,将第一时钟信号传输至第一扫描信号端oput1《n》,驱动上述至少一行子像素p进行黑画面显示。

156.在一些示例中,如图9所示,第二插黑子电路22与第五控制信号端bcs5、第二插黑级联信号端bcr2、第六控制信号端bcs6、第二插黑输入信号端bi2、第一上拉节点q《n》及第一电压信号端v1电连接。第二插黑子电路22被配置为,在第五控制信号端bcs5所传输的第五控制信号、第二插黑级联信号端bcr2所传输的第二插黑级联信号及第六控制信号端bcs6所传输的第六控制信号的控制下,将在第二插黑输入信号端bi2处接收的第二插黑输入信号传输至第一上拉结点q《n》。

157.示例性地,在第五控制信号的电平为高电平、第二插黑级联信号的电平为高电平且第六控制信号的电平为高电平的情况下,第二插黑子电路22可以在第五控制信号、第二插黑级联信号及第六控制信号的控制下导通,接收第二插黑输入信号,并将该第二插黑输入信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行充电,使得第一上拉节点q《n》的电压升高。

158.示例性的,输出电路12还被配置为,在第二插黑子电路22将第二插黑输入信号传输至第一上拉节点q《n》的情况下,在第一上拉节点q《n》的电压的控制下,将第一时钟信号传输至第一扫描信号端oput1《n》,驱动上述至少一行子像素p进行黑画面显示。

159.例如,在第一上拉节点q《n》的电压为高电平的情况下,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通,将在第一时钟信号端clke1处接收的第一时钟信号传输至第一扫描信号端oput1《n》,并将第一时钟信号作为第一扫描信号,从第一扫描信号端oput1《n》输出。

160.需要说明的是,第一电压信号端v1例如被配置为传输直流低电平信号(例如低于或等于时钟信号的低电平部分)。示例性的,该第一电压端v1接地。

161.需要说明的是,在本公开的实施例中,在一帧显示阶段中,第一输入电路11、第一插黑子电路21和第二插黑子电路22分别在不同的时间导通。

162.在第一帧图像的显示阶段中,第一上拉节点q《n》的电压首先由第一输入电路11传

输的显示输入信号进行抬升,第一输入电路11导通并对第一上拉节点q《n》进行充电后,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通,将第一时钟信号输出为第一扫描信号,从第一扫描信号端oput1《n》输出。如图5所示,在复位阶段t1和数据写入阶段t2中,第一输入电路11导通,第一上拉节点q《n》的电压保持为高电平,第一输出电路12在第一上拉节点q《n》的电压的作用下保持导通状态。由于第一时钟信号的电平为高电平,因此,第一输出电路12输出的第一扫描信号的电平为高电平。在发光阶段t3中,第一上拉节点q《n》的电压为低电平,第一输出电路12关断,第一扫描信号的电平为低电平;驱动晶体管t2在第一节点g的电压(存储电容器cst进行放电)的控制下导通,驱动发光器件p2发光。相对应的,与移位寄存器100相对应的至少一行子像素p进行图像显示。

163.在发光器件p2发光过程中的某一时刻(也即图5所示中发光阶段t3和插黑写入阶段t4交替的时刻),第一插黑子电路21导通并对第一上拉节点q《n》进行充电,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通。此时,第一时钟信号输出为第一插黑信号从第一扫描信号端oput1《n》输出,并传输至相应行像素驱动电路p1的第一栅极信号端g1和第二栅极信号端g2。由于第一插黑信号的电平为高电平,开关晶体管t1可以在该第一插黑信号的控制下导通,将低电平或较低电平的数据信号(也可以称为第一插黑数据信号)传输至第一节点g;感测晶体管t3也可以在第一插黑信号的控制下导通,将低电平的复位信号传输至第二节点s。此时vgs(也即第一节点g和第二节点s之间的压差)小于vth(也即驱动晶体管t2的阈值电压),使得子像素p停止发光,切换为黑画面。在插黑保持阶段t5中,子像素p持续显示为黑画面。

164.在第二帧图像的显示阶段中,第一上拉节点q《n》的电压首先由第一输入电路11传输的显示输入信号进行抬升,重复上述子像素p进行图像显示的过程,此处不再赘述。

165.发光器件p2在第二帧图像发光过程中的某一时刻(也即图5所示中发光阶段t3和插黑写入阶段t4交替的时刻),第二插黑子电路22导通并对第一上拉节点q《n》进行充电,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通。此时,第一时钟信号可以作为第二插黑信号从第一扫描信号端oput1《n》输出,并传输至相应行像素驱动电路p1的第一栅极信号端g1和第二栅极信号端g2。由于第二插黑信号的电平为高电平,开关晶体管t1可以在该第二插黑信号的控制下导通,将低电平或较低电平的数据信号(也可以称为第二插黑数据信号)传输至第一节点g;感测晶体管t3也可以在第二插黑信号的控制下导通,将低电平的复位信号传输至第二节点s。此时vgs小于vth,使得子像素p停止发光,切换为黑画面。在插黑保持阶段t5中,子像素p持续显示为黑画面。

166.由此,本公开一些实施例做提供的移位寄存器100,通过设置第一插黑子电路21和第二插黑子电路22,通过第一插黑子电路21控制相邻两帧显示图像中第一帧显示图像的插黑,控制一组栅线进行同时插黑显示;通过第二插黑子电路22控制相邻两帧显示图像中第二帧显示图像的插黑,控制另一组栅线进行同时插黑显示,实现第一帧显示图像的插黑分组与第二帧显示图像的插黑分组不同,从而控制子像素p在第一帧显示阶段和第二帧显示阶段的显示时段的时间不同,调节相邻帧图像的显示时段的时间总和,实现缩小相邻行显示时间差的目的,避免不同栅线组控制的像素驱动电路的显示时间存在的时间差较大而导致显示画面亮度不均的问题。

167.在一些实施例中,如图10和图11所示,第一插黑子电路21包括第一插黑控制子电

路211、第一插黑输入子电路212和第一插黑传输子电路213。

168.在一些示例中,如图10和图11所示,第一插黑控制子电路211与第一控制信号端bcs1、第一插黑级联信号端bcr1、第一电压信号端v1及第一插黑节点m电连接。第一插黑控制子电路211被配置为,在第一控制信号的控制下,将第一插黑级联信号传输至第一插黑节点m。

169.示例性的,在第一控制信号的电压为高电平的情况下,第一插黑控制子电路211可以在第一控制信号的控制下导通,将在第一插黑级联信号端bcr1处接收的第一插黑级联信号传输至第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m的电压升高。

170.在一些示例中,如图10和图11所示,第一插黑输入子电路212与第一插黑节点m、第一插黑输入信号端bi1及第二插黑节点k1电连接。第一插黑输入子电路212被配置为,在第一插黑节点m的电压的控制下,将第一插黑输入信号传输至第二插黑节点k2。

171.示例性的,在第一插黑节点m电压为高电平的情况下,第一插黑输入子电路212可以在第一插黑节点m电压的控制下导通,将在第一插黑输入信号端bi1处接收的第一插黑输入信号传输至第二插黑节点k1,对第二插黑节点k1进行充电,使得第二插黑节点k1的电压升高。

172.在一些示例中,如图10和图11所示,第一插黑传输子电路213与第二控制信号端bcs2、第二插黑节点k1及第一上拉结点q《n》电连接;第一插黑传输子电路213被配置为,在第二控制信号的控制下,将来自第二插黑节点k1的第一插黑输入信号传输至第一上拉结点q《n》。

173.示例性的,在第二控制信号的电压为高电平的情况下,第一插黑传输子电路213可以在第二控制信号的控制下导通,接收并传输第一插黑输入信号至第一上拉结点q《n》,对第一上拉结点q《n》进行充电,使得第一上拉结点q《n》的电压升高。

174.在一些示例中,第二控制信号端bcs2和第一插黑输入信号端bi1为相同的信号端。第二控制信号端bcs2和第一插黑输入信号端bi1接收相同的信号,并传输相同的信号。也就是说,第二控制信号和第一插黑输入信号的时序相同。

175.示例性的,第二控制信号和第一插黑输入信号均为时钟信号,或者,第二控制信号和第一插黑输入信号为某个移位信号。这样有利于简化移位寄存器100和扫描驱动电路1000的结构,有利于提高移位寄存器100和扫描驱动电路1000的良率。

176.在一些实施例中,如图10和图11所示,第二插黑子电路22包括第二插黑控制子电路221、第二插黑输入子电路222和第二插黑传输子电路223。

177.在一些示例中,如图10和图11所示,第二插黑控制子电路221与第五控制信号端bcs5、第二插黑级联信号端bcr2、第一电压信号端v1及第一插黑节点m电连接;第二插黑控制子电路221被配置为,在第五控制信号的控制下,将第二插黑级联信号传输至第一插黑节点m。

178.示例性的,在第五控制信号的电压为高电平的情况下,第二插黑控制子电路221可以在第五控制信号的控制下导通,将在第二插黑级联信号端bcr2处接收的第二插黑级联信号传输至第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m的电压升高。

179.在一些示例中,如图10和图11所示,第二插黑输入子电路222与第一插黑节点m、第二插黑输入信号端bi2及第三插黑节点k2电连接;第二插黑输入子电路222被配置为,在第

一插黑节点m的电压的控制下,将第二插黑输入信号传输至第三插黑节点k2。

180.示例性的,在第一插黑节点m电压为高电平的情况下,第二插黑输入子电路222可以在第一插黑节点m电压的控制下导通,将在第二插黑输入信号端bi2处接收的第二插黑输入信号传输至第三插黑节点k2,对第三插黑节点k2进行充电,使得第三插黑节点k2的电压升高。

181.在一些示例中,如图10和图11所示,第二插黑传输子电路223与第六控制信号端bcs6、第三插黑节点k2及第一上拉结点q《n》电连接;第二插黑传输子电路223被配置为,在第六控制信号的控制下,将来自第三插黑节点k2的第二插黑输入信号传输至第一上拉结点q《n》。

182.示例性的,在第六控制信号的电压为高电平的情况下,第二插黑传输子电路223可以在第六控制信号的控制下导通,接收并传输第二插黑输入信号至第一上拉结点q《n》,对第一上拉结点q《n》进行充电,使得第一上拉结点q《n》的电压升高。

183.在一些示例中,第六控制信号端bcs6和第二插黑输入信号端bi2为相同的信号端。第六控制信号端bcs6和第二插黑输入信号端bi2接收相同的信号,并传输相同的信号。也就是说,第六控制信号端bcs6和第二插黑输入信号端bi2的时序相同。

184.示例性的,第六控制信号和第二插黑输入信号均为时钟信号,或者,第六控制信号和第二插黑输入信号为某个移位信号。

185.在一些实施例中,如图12a和图13a所示,移位寄存器100还包括第二扫描单元3。其中,第二扫描单元3包括第二输入电路31和第二输出电路32。

186.在一些示例中,如图12a和图13a所示,第二输入电路31与显示输入信号端iput及第二上拉节点q《n+1》电连接;第二输入电路31被配置为,响应于显示输入信号,将显示输入信号传输至第二上拉节点q《n+1》。

187.示例性的,在显示输入信号的电平为高电平的情况下,第二输入电路31可以在显示输入信号的作用下导通,接收并传输显示输入信号至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行充电,使得第二上拉节点q《n+1》的电压升高。

188.在一些示例中,如图12a和图13a所示,第二输出电路32与第二上拉节点q《n+1》、第二时钟信号端clke2及第二扫描信号端oput1《n+1》电连接;第二输出电路32被配置为,在第二上拉节点q《n+1》的电压控制下,将在第二时钟信号端clke2处接收的第二时钟信号传输至第二扫描信号端oput1《n+1》,驱动上述至少一行子像素p进行图像显示。

189.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第二输出电路32可以在第二上拉节点q《n+1》的电压的控制下导通,将在第二时钟信号端clke2处接收的第二时钟信号传输至第二扫描信号端oput1《n+1》,并将第二时钟信号作为第二扫描信号,从第二扫描信号端oput1《n+1》输出。

190.由于第一输入电路11和第二输入电路31均与显示输入信号端iput电连接,因此,在显示输入信号的电平为高电平的情况下,第一输入电路11和第二输入电路31可以同时导通,并同时对第一上拉节点q《n》和第二上拉节点q《n+1》进行充电,进而可以使得第一输出电路12和第二输出电路32同时导通。

191.其中,在显示阶段中的显示时段,第一输出电路12输出的第一扫描信号和第二输出电路32输出的第二扫描信号,例如可以不同。这样便于驱动不同行子像素p进行逐行扫描

及逐行进行图像显示。

192.在一些实施例中,如图12a和图13a所示,第一插黑子电路21还与第二上拉节点q《n+1》电连接;第一插黑子电路21还被配置为,在将第一插黑输入信号传输至第一上拉结点q《n》的同时,将第一插黑输入信号传输至第二上拉节点q《n+1》。

193.需要说明的是,第二输出电路32还被配置为,在第一插黑子电路21将第一插黑输入信号传输至第二上拉节点q《n+1》的情况下,在第二上拉节点q《n+1》的电压的控制下,将第二时钟信号传输至第二扫描信号端oput1《n+1》,驱动上述至少一行子像素p进行黑画面显示。

194.示例性的,在第一控制信号的电平为高电平、第一插黑级联信号的电平为高电平且第二控制信号的电平为高电平的情况下,第一插黑子电路21可以在第一控制信号、第一插黑级联信号及第二控制信号的控制下导通,接收第一插黑输入信号,并将该第一插黑输入信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行充电,使得第二上拉节点q《n+1》的电压升高。第二输出电路32可以在第二上拉节点q《n+1》的电压的控制下导通,将在第二时钟信号端clke2处接收的第二时钟信号传输至第二扫描信号端oput1《n+1》,并将第二时钟信号作为第二扫描信号,从第二扫描信号端oput1《n+1》输出。

195.由于第一插黑子电路21不仅与第一上拉节点q《n》电连接,还与第二上拉节点q《n+1》电连接,也就意味着,第一插黑子电路21同时与第一扫描单元1和第二扫描单元3电连接。这样在第一插黑子电路21导通的情况下,可以将高电平的第一插黑输入信号,同时传输至第一上拉节点q《n》和第二上拉节点q《n+1》,进而使得第一输出电路12和第二输出电路32同时导通,在第一输出电路12将第一时钟信号作为第一扫描信号输出的过程中,第二输出电路32将第二时钟信号作为第一扫描信号输出,可以驱动与第一扫描信号端oput1《n》电连接的相应行子像素p及与第二扫描信号端oput1《n+1》电连接的相应行子像素p,同时显示黑画面。

196.在一些实施例中,如图12a和图13a所示,第二插黑子电路22还与第二上拉节点q《n+1》电连接;第二插黑子电路22还被配置为,在将第二插黑输入信号传输至第一上拉结点q《n》的同时,将第二插黑输入信号传输至第二上拉节点q《n+1》。

197.需要说明的是,第二输出电路32还被配置为,在第二插黑子电路22将第二插黑输入信号传输至第二上拉节点q《n+1》的情况下,在第二上拉节点q《n+1》的电压的控制下,将第二时钟信号传输至第二扫描信号端oput1《n+1》,驱动上述至少一行子像素p进行黑画面显示。

198.示例性的,在第五控制信号的电平为高电平、第二插黑级联信号的电平为高电平且第六控制信号的电平为高电平的情况下,第二插黑子电路22可以在第五控制信号、第二插黑级联信号及第六控制信号的控制下导通,接收第二插黑输入信号,并将该第二插黑输入信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行充电,使得第二上拉节点q《n+1》的电压升高。第二输出电路32将第二时钟信号作为第二扫描信号从第二扫描信号端oput1《n+1》输出,此处不再赘述。

199.由于第二插黑子电路22不仅与第一上拉节点q《n》电连接,还与第二上拉节点q《n+1》电连接,也就意味着,第二插黑子电路22同时与第一扫描单元1和第二扫描单元3电连接。这样在第二插黑子电路22导通的情况下,可以将高电平的第二插黑输入信号,同时传输至

第一上拉节点q《n》和第二上拉节点q《n+1》,进而使得第一输出电路12和第二输出电路32同时导通,在第一输出电路12将第一时钟信号作为第一扫描信号输出的过程中,第二输出电路32将第二时钟信号作为第一扫描信号输出,可以驱动与第一扫描信号端oput1《n》电连接的相应行子像素p及与第二扫描信号端oput1《n+1》电连接的相应行子像素p,同时显示黑画面。

200.本公开的移位寄存器100设置两级插黑子电路,即第一插黑子电路21和第二插黑子电路22,可以控制相应行子像素p在相邻两帧图像显示阶段中,实现不同的级联插黑,从而控制子像素p在第一帧显示阶段和第二帧显示阶段的显示时段的时间不同,调节相邻帧图像的显示时段的时间总和,实现缩小相邻行显示时间差的目的。

201.在移位寄存器100包括第一扫描单元1和第二扫描单元3的情况下,每个移位寄存器100可以与至少两行子像素p电连接,其中,第一扫描单元1所连接的至少一行子像素p与第二扫描单元3所连接的至少一行子像素p不同。这样可以驱动与移位寄存器100所电连接的至少两行子像素p,同时进行黑画面显示,有利于减少插入黑画面所需的时间,提高图像显示的效果。

202.在一些实施例中,如图12a和图13a所示,在移位寄存器100包括第二扫描单元3的情况下,第一插黑子电路21还包括第三插黑传输子电路214。

203.在一些示例中,如图12a和图13a所示,第三插黑传输子电路214与第二控制信号端bcs2、第二插黑节点k1及第二上拉结点q《n+1》电连接;第三插黑传输子电路214被配置为,在第二控制信号的控制下,将来自第二插黑节点k1的第一插黑输入信号传输至第二上拉结点q《n+1》。

204.示例性的,在第二控制信号的电压为高电平的情况下,第三插黑传输子电路214可以在第二控制信号的控制下导通,接收并传输第一插黑输入信号至第二上拉结点q《n+1》,对第二上拉结点q《n+1》进行充电,使得第二上拉结点q《n+1》的电压升高。

205.在一些实施例中,如图12a和图13a所示,第二插黑子电路22还包括第四插黑传输子电路224。

206.在一些示例中,如图12a和图13a所示,第四插黑传输子电路224与第六控制信号端bcs6、第三插黑节点k2及第二上拉结点q《n+1》电连接;第四插黑传输子电路224被配置为,在第六控制信号的控制下,将来自第三插黑节点k2的第二插黑输入信号传输至第二上拉结点q《n+1》。

207.示例性的,在第六控制信号的电压为高电平的情况下,第四插黑传输子电路224可以在第六控制信号的控制下导通,接收并传输第二插黑输入信号至第二上拉结点q《n+1》,对第二上拉结点q《n+1》进行充电,使得第二上拉结点q《n+1》的电压升高。

208.在一些实施例中,如图12b和图13b所示,本发明还提供一种子电路共用的设计,第一插黑输入子电路212和第二插黑输入子电路222为同一子电路,第一插黑输入信号端bi1与第二插黑输入信号端bi2为同一信号端,第二插黑节点k1与第三插黑节点k2为同一节点。第一插黑传输子电路213和第二插黑传输子电路223为同一子电路,第二控制信号端bcs2与第六控制信号端bcs6为同一信号端。第三插黑传输子电路214和第四插黑传输子电路224为同一子电路。

209.将第一插黑输入子电路212和第二插黑输入子电路222设置为同一子电路,第一插

黑传输子电路213和第二插黑传输子电路223设置为同一子电路,将第三插黑传输子电路214和第四插黑传输子电路224设置为同一子电路,可以实现子电路共用,简化电路设计,节省空间,更有利于显示面板的窄边框化。

210.需要说明的是,上述子电路共用的设计,在一帧显示阶段中,第一插黑子电路21和第二插黑子电路22分别在不同的时间导通,并且,在第一帧图像的显示阶段中,第一插黑子电路21导通,第一插黑控制子电路211导通,第一插黑输入子电路212和第一插黑传输子电路213导通,对第一上拉节点q《n》进行充电,在第二帧图像的显示阶段中,第二插黑子电路22导通,第二插黑控制子电路221导通,第一插黑输入子电路212和第一插黑传输子电路213(即第二插黑输入子电路222和第二插黑传输子电路223)导通,对第一上拉节点q《n》进行充电,也就是说,共用的子电路在相邻两帧图像的显示阶段中均工作。

211.在一些实施例中,如图11和图13a所示,第一输入电路11包括第一晶体管m1。

212.在一些示例中,如图11和图13a所示,第一晶体管m1的控制极与显示输入信号端iput电连接,第一晶体管m1的第一极与显示输入信号端iput电连接,第一晶体管m1的第二极与第一上拉节点q《n》电连接。

213.示例性的,在显示输入信号的电平为高电平的情况下,第一晶体管m1可以在显示输入信号的作用下导通,接收显示输入信号,并将显示输入信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行充电,使得第一上拉节点q《n》的电压升高。

214.在一些实施例中,如图11和图13a所示,第一输出电路12包括第二晶体管m2和第一电容c1。

215.在一些示例中,如图11和图13a所示,第二晶体管m2的控制极与第一上拉节点q《n》电连接,第二晶体管m2的第一极与第一时钟信号端clke1电连接,第二晶体管m2的第二极与第一扫描信号端oput1《n》电连接。

216.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第二晶体管m2可以在第一上拉节点q《n》的控制下导通,将从第一时钟信号端clke1处接收的第一时钟信号从第一扫描信号端oput1《n》输出。其中,在不同的时段导通,第一扫描信号端oput1《n》输出的第一扫描信号的作用不同,具体可以参照上述一些示例中的说明,此处不再赘述。

217.在一些示例中,如图11和图13a所示,第一电容器c1的第一端与第一上拉节点q《n》电连接,第一电容器c1的第二端与第一扫描信号端oput1《n》电连接。

218.示例性的,在第一输入电路12中的第一晶体管m1导通、并对第一上拉节点q《n》进行充电的过程中,还会对第一电容器c1进行充电。在第一晶体管m1关断后,第一电容器c1可以进行放电,使得第一上拉节点q《n》的电压保持为高电平。

219.在一些实施例中,如图10、图11、图12a和图13a所示,第一插黑子电路21包括第一插黑控制子电路211、第一插黑输入子电路212和第一插黑传输子电路213,第一插黑控制子电路211包括第三晶体管m3和第二电容c2。

220.在一些示例中,如图11和图13a所示,第三晶体管m3的控制极与第一控制信号端bcs1电连接,第三晶体管m3的第一极与第一插黑级联信号端bcr1电连接,第三晶体管m3的第二极与第一插黑节点m电连接。

221.示例性的,在第一控制信号的电压为高电平的情况下,第三晶体管m3可以在第一控制信号的控制下导通,将在第一插黑级联信号端bcr1处接收的第一插黑级联信号传输至

第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m的电压升高。

222.在一些示例中,如图11和图13a所示,第二电容c2的第一端与第一插黑节点m电连接,第二电容c2的第二端与第一电压信号端v1电连接。

223.示例性的,第三晶体管m3导通、并对第一插黑节点m进行充电的过程中,还会对第二电容c2进行充电。在第三晶体管m3关断后,第二电容c2可以进行放电,使得第一插黑节点m的电压保持高电平。

224.在一些实施例中,如图11和图13a所示,第一插黑输入子电路212包括第四晶体管m4。

225.在一些示例中,如图11和图13a所示,第四晶体管m4的控制极与第一插黑节点m电连接,第四晶体管m4的第一极与第一插黑输入信号端bi1电连接,第四晶体管m的第二极与第二插黑节点k1电连接。

226.示例性的,在第三晶体管m3导通、并对第一插黑节点m进行充电,使得第一插黑节点m电压为高电平的情况下,第四晶体管m4可以在第一插黑节点m电压的控制下导通,接收并传输第一插黑输入信号至第二插黑节点k1。

227.在一些实施例中,如图11和图13a所示,第一插黑传输子电路213包括第五晶体管m5。

228.在一些示例中,如图11和图13a所示,第五晶体管m5的控制极与第二控制信号端bcs2电连接,第五晶体管m5的第一极与第二插黑节点k1电连接,第五晶体管m5的第二极与第一上拉结点电连接q《n》。

229.示例性的,在第二控制信号的电压为高电平的情况下,第五晶体管m5可以在第二控制信号的控制下导通,接收并传输第一插黑输入信号至第一上拉结点q《n》,对第一上拉结点q《n》进行充电,使得第一上拉结点q《n》的电压升高。

230.在一些实施例中,如图11和图13a所示,第二插黑子电路22包括第二插黑控制子电路221、第二插黑输入子电路222和第二插黑传输子电路223,第二插黑控制子电路221包括第七晶体管m7。

231.在一些示例中,如图11和图13a所示,第七晶体管m7的控制极与第五控制信号端bcs5电连接,第七晶体管m7的第一极与第二插黑级联信号端bcr2电连接,第七晶体管m7的第二极与第一插黑节点m电连接。

232.示例性的,在第五控制信号的电压为高电平的情况下,第七晶体管m7可以在第五控制信号的控制下导通,将在第二插黑级联信号端bcr2处接收的第二插黑级联信号传输至第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m的电压升高。

233.需要说明的是,第七晶体管m7导通、并对第一插黑节点m进行充电的过程中,还会对第二电容c2进行充电。在第七晶体管m7关断后,第二电容c2可以进行放电,使得第一插黑节点m的电压保持高电平。因此可以说,第二插黑控制子电路221还包括第二电容c2。

234.在一些实施例中,如图11和图13a所示,第二插黑输入子222电路包括第八晶体管m8。

235.在一些示例中,如图11和图13a所示,第八晶体管m8的控制极与第一插黑节点m电连接,第八晶体管m8的第一极与第二插黑输入信号端bi2电连接,第八晶体管m8的第二极与第三插黑节点k2电连接。

236.示例性的,第七晶体管m7导通、并对第一插黑节点m进行充电,使得第一插黑节点m电压为高电平的情况下,第八晶体管m8可以在第一插黑节点m电压的控制下导通,接收并传输第二插黑输入信号至第三插黑节点k2。

237.在一些实施例中,如图11和图13a所示,第二插黑传输子电路223包括第九晶体管m9。

238.在一些示例中,如图11和图13a所示,第九晶体管m9的控制极与第六控制信号端bcs6电连接,第九晶体管m9的第一极与第三插黑节点k2电连接,第九晶体管m9的第二极与第一上拉结点q《n》电连接。

239.示例性的,在第六控制信号的电压为高电平的情况下,第九晶体管m9可以在第六控制信号的控制下导通,接收并传输第二插黑输入信号至第一上拉结点q《n》,对第一上拉结点q《n》进行充电,使得第一上拉结点q《n》的电压升高。

240.在一些示例中,如图13b所示,在第一插黑输入子电路212和第二插黑输入子电路222为同一子电路、第一插黑输入信号端bi1与第二插黑输入信号端bi2为同一信号端、第二插黑节点k1与第三插黑节点k2为同一节点的情况下,第一插黑输入子电路212与第二插黑输入子电路222包括第四晶体管m4。在第一插黑传输子电路213和第二插黑传输子电路223为同一子电路、第二控制信号端bcs2与第六控制信号端bcs6为同一信号端的情况下,第一插黑传输子电路213和第二插黑传输子电路223包括第五晶体管m5。

241.关于第四晶体管m4和第五晶体管m5的连接结构如上所述,此处不再赘述。

242.在一些实施例中,如图13a所示,在移位寄存器100还包括第二扫描单元3的情况下,第二扫描单元3的第二输入电路31与显示输入信号端iput及第二上拉节点q《n+1》电连接。第二输入电路31包括第十晶体管m10。

243.在一些示例中,如图13a所示,第十晶体管m10的控制极与显示输入信号端iput电连接,第十晶体管m10的第一极与显示输入信号端iput电连接,第十晶体管m10的第二极与第二上拉节点q《n+1》电连接。

244.示例性的,在显示输入信号的电平为高电平的情况下,第十晶体管m10可以在显示输入信号的作用下导通,接收并传输显示输入信号至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行充电,使得第二上拉节点q《n+1》的电压升高。

245.在一些实施例中,如图13a所示,第二输出电路32包括第十一晶体管m11和第三电容c3。

246.在一些示例中,如图13a所示,第十一晶体管m11的控制极与第二上拉节点q《n+1》电连接,第十一晶体管m11的第一极与第二时钟信号端clke2电连接,第十一晶体管m11的第二极与第二扫描信号端oput1《n+1》。

247.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第十一晶体管m11可以在第二上拉节点q《n+1》的电压的控制下导通,将在第二时钟信号端clke2处接收的第二时钟信号传输至第二扫描信号端oput1《n+1》,并将第二时钟信号作为第二扫描信号,从第二扫描信号端oput1《n+1》输出。其中,在不同的时段导通,第二扫描信号端oput1《n+1》输出的第二扫描信号的作用不同,具体可以参照上述一些示例中的说明,此处不再赘述。

248.在一些示例中,如图13a所示,第三电容c3的第一端与第二上拉节点q《n+1》电连接,第三电容c3的第二端与第二时钟信号端clke2电连接。

249.示例性的,在第二输入电路31中的第十晶体管m10、并对第二上拉节点q《n+1》进行充电的过程中,还会对第三电容c3进行充电。在第十晶体管m10关断后,第三电容c3可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

250.示例性的,第一插黑子电路21导通、并对第二上拉节点q《n+1》进行充电的过程中,还会对第三电容c3进行充电。在第一插黑子电路21关断后,第三电容c3可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

251.同理,第二插黑子电路22导通、并对第二上拉节点q《n+1》进行充电的过程中,还会对第三电容c3进行充电。在第二插黑子电路22关断后,第三电容c3可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

252.在一些实施例中,如图13a所示,第一插黑子电路21还包括第三插黑传输子电路214的情况下,第三插黑传输子电路214包括第十二晶体管m12。

253.在一些示例中,如图13a所示,第十二晶体管m12的控制极与第二控制信号端bcs2电连接,第十二晶体管m12的第一极与第二插黑节点k1电连接,第十二晶体管m12的第二极与第二上拉结点q《n+1》电连接。

254.示例性的,在第二控制信号的电压为高电平的情况下,第十二晶体管m12可以在第二控制信号的控制下导通,接收并传输第一插黑输入信号至第二上拉结点q《n+1》,对第二上拉结点q《n+1》进行充电,使得第二上拉结点q《n+1》的电压升高。

255.在一些实施例中,如图13a所示,第二插黑子电路22还包括第四插黑传输子电路224的情况下,第四插黑传输子电路224包括第十三晶体管m13。

256.在一些示例中,如图13a所示,第十三晶体管m13的控制极与第六控制信号端bcs6电连接,第十三晶体管m13的第一极与第三插黑节点k2电连接,第十三晶体管m13的第二极与第二上拉结点q《n+1》电连接。

257.示例性的,在第六控制信号的电压为高电平的情况下,第十三晶体管m13可以在第六控制信号的控制下导通,接收并传输第二插黑输入信号至第二上拉结点q《n+1》,对第二上拉结点q《n+1》进行充电,使得第二上拉结点q《n+1》的电压升高。

258.在一些示例中,如图13b所示,在第三插黑传输子电路214和第四插黑传输子电路224为同一子电路、第二插黑节点k1与第三插黑节点k2为同一节点及第二控制信号端bcs2与第六控制信号端bcs6为同一信号端的情况下,第三插黑传输子电路214和第四插黑传输子电路224包括第十二晶体管m12。

259.关于第十二晶体管m12的连接结构如上所述,此处不再赘述。

260.在一些实施例中,如图14和图15所示,第一输出电路12还与第五时钟信号端clkd1及第一移位信号端cr2《n》电连接。第一输出电路12还被配置为,在第一上拉节点q《n》的电压控制下,将在第五时钟信号端clkd1处接收的第五时钟信号传输至第一移位信号端cr2《n》。

261.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通,将在第五时钟信号端clkd1处接收的第五时钟信号作为第一移位信号,从第一移位信号端cr2《n》输出。

262.在一些实施例中,如图14和图15所示,移位寄存器100还包括第二扫描单元3的情况下,第二扫描单元3的第二输入电路31与显示输入信号端iput及第二上拉节点q《n+1》电

连接。第二输出电路32还与第六时钟信号端clkd2及第二移位信号端cr《n+1》电连接。第二输出电路32还被配置为,在第二上拉节点q《n+1》的电压控制下,将在第六时钟信号端clkd2处接收的第六时钟信号传输至第二移位信号端cr《n+1》。

263.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第二输出电路32可以在第二上拉节点q《n+1》的电压的控制下导通,将在第六时钟信号端clkd2处接收的第六时钟信号作为第二移位信号,从第二移位信号端cr《n+1》输出。

264.在一些实施例中,如图15所示,第一输出电路12还包括第十六晶体管m16。

265.在一些示例中,如图15所示,第十六晶体管m16的控制极与第一上拉节点q《n》电连接,第十六晶体管m16的第一极与第五时钟信号端clkd1电连接,第十六晶体管m16的第二极与第一移位信号端cr2《n》电连接。

266.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,十六晶体管m16可以在第一上拉节点q《n》的电压的控制下导通,将在第五时钟信号端clkd1处接收的第五时钟信号作为第一移位信号,从第一移位信号端cr2《n》输出。

267.在一些实施例中,如图15所示,第二输出电路32还包括第十七晶体管m17。

268.在一些示例中,如图15所示,第十七晶体管m17的控制极与第二上拉节点q《n+1》电连接,第十七晶体管m17的第一极与第六时钟信号端clkd2电连接,第十七晶体管m17的第二极与第二移位信号端cr《n+1》电连接。

269.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第十七晶体管m17可以在第二上拉节点q《n+1》的电压的控制下导通,将在第六时钟信号端clkd2处接收的第六时钟信号作为第二移位信号,从第二移位信号端cr《n+1》输出。

270.需要说明的是,上述第一移位信号端cr2《n》和第二移位信号端cr《n+1》均用于级联,以便于简化扫描驱动电路1000的结构,减小扫描驱动电路1000在边框区b的占据面积。也就是说,在采用移位信号端进行级联的情况下,第一输出电路12或第二输出电路32可以与相应的移位信号端电连接。

271.在本公开中,级联的方式可以参见下面一些实施例中的说明,此处不再赘述。

272.其中,在显示输入信号端iput与某一移位信号端电连接、且第一插黑级联信号端bcr1、第二插黑级联信号端bcr2与某一移位信号端电连接的情况下,所电连接的移位信号端分别属于不同的扫描单元。这样可以避免出现同一移位寄存器100的第一输入电路11、第二输入电路31及第一插黑子电路21和第二插黑子电路22因连接同一移位信号端而同时导通的情况,进而可以避免出现图像正常显示的过程和插入黑画面的过程相冲突的情况。

273.在一些实施例中,如图14和图15所示,第一输出电路12还与第三时钟信号端clkf1及第一感测信号端oput2《n》电连接。第一输出电路12还被配置为,在第一输入电路11将显示输入信号传输至第一上拉节点q《n》的情况下,在第一上拉节点q《n》的电压控制下,将在第三时钟信号端clkf1处接收的第三时钟信号传输至第一感测信号端oput2《n》,驱动上述至少一行子像素p进行复位。

274.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通,将在第三时钟信号端clkf1处接收的第三时钟信号传输至第一感测信号端oput2《n》,并将第三时钟信号作为第一感测信号,从第一感测信号端oput2《n》输出。

275.或者,在第一插黑子电路21将第一插黑输入信号传输至第一上拉节点q《n》的情况下,在第一上拉节点q《n》的电压的控制下,将第三时钟信号传输至第一感测信号端oput2《n》,驱动上述至少一行子像素p进行黑画面显示。

276.又或者,在第二插黑子电路22将第二插黑输入信号传输至第一上拉节点q《n》的情况下,在第一上拉节点q《n》的电压的控制下,将第三时钟信号传输至第一感测信号端oput2《n》,驱动上述至少一行子像素p进行黑画面显示。

277.在此情况下,同一行子像素p中的多个像素驱动电路p1与两条栅线gl电连接。一个移位寄存器100的第一扫描信号端oput1《n》可以通过其中一条栅线gl(第一扫描信号线gl1)与相应行子像素p中多个像素驱动电路p的第一栅极信号端g1电连接,第一扫描信号端oput1《n》所输出的第一扫描信号可以经该栅线gl传输至该多个像素驱动电路p1的第一栅极信号端g1。该移位寄存器100的第一感测信号端oput2《n》可以通过另一条栅线gl(第二扫描信号线gl2)与相应行子像素p中多个像素驱动电路p1的第二栅极信号端g2电连接,第一感测信号端oput2《n》所输出的第一感测信号可以作为第二扫描信号经该栅线gl传输至该多个像素驱动电路p1的第二栅极信号端g2。

278.例如,在一帧显示阶段中的显示时段1f1中,如图4、图5和图15所示,在复位阶段t1和数据写入阶段t2中,第一输入电路11开启,第一上拉节点q《n》的电压保持为高电平,第一输出电路12在第一上拉节点q《n》的电压的作用下保持导通状态。由于第一时钟信号的电平和第三时钟信号的电平均为高电平,因此,第一输出电路12输出的第一扫描信号的电平和第一感测信号的电平均为高电平。开关晶体管t1在第一扫描信号(来自第一扫描信号端oput1《n》)的控制下导通,接收并传输数据信号至第一节点g;感测晶体管t3在第二扫描信号(来自第一感测信号端oput2《n》)的控制下导通,接收并传输复位信号至第二节点s,对第二节点s进行复位。这样可以对后续的发光阶段t3(也即图像显示)做准备。

279.在发光器件p2发光过程中的某一时刻(也即图5所示中发光阶段t3和插黑写入阶段t4交替的时刻),第一插黑子电路21或者第二插黑子电路22导通并对第一上拉节点q《n》进行充电,第一输出电路12可以在第一上拉节点q《n》的电压的控制下导通。此时,第一时钟信号可以作为插黑信号从第一扫描信号端oput1《n》输出,并传输至相应行像素驱动电路p1的第一栅极信号端g1,第三时钟信号可以作为插黑信号从第一感测信号端oput2《n》输出,并传输至相应行像素驱动电路p1的第二栅极信号端g2,以便于后续子像素p显示黑画面。

280.在一些实施例中,如图14和图15所示,第二输出电路32还与第四时钟信号端clkf2及第二感测信号端oput2《n+1》电连接电连接。第二输出电路32还被配置为,在第二上拉节点q《n+1》的电压控制下,将在第四时钟信号端clkf2处接收的第四时钟信号传输至第二感测信号端oput2《n+1》。

281.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第二输出电路32可以在第二上拉节点q《n+1》的电压的控制下导通,将在第四时钟信号端clkf2处接收的第四时钟信号传输至第二感测信号端oput2《n+1》,并将第四时钟信号作为第二感测信号,从第二感测信号端oput2《n+1》输出,驱动上至少一行子像素p进行复位。

282.或者,在第一插黑子电路21将第一插黑输入信号传输至第二上拉节点q《n+1》的情况下,在第二上拉节点q《n+1》的电压的控制下,将第四时钟信号传输至第二感测信号端oput2《n+1》,驱动上述至少一行子像素p进行黑画面显示。

283.又或者,在第二插黑子电路22将第二插黑输入信号传输至第二上拉节点q《n+1》的情况下,在第二上拉节点q《n+1》的电压的控制下,将第四时钟信号传输至第二感测信号端oput2《n+1》,驱动上述至少一行子像素p进行黑画面显示。

284.需要说明的是,利用第二扫描单元3驱动相应行子像素p进行图像显示或黑画面显示的过程,与利用第一扫描单元1驱动相应行子像素p进行图像显示或黑画面显示的过程相同,具体可以参照上述一些实施例中的说明,此处不再赘述。

285.在一些实施例中,如图15所示,第一输出电路12还包括第十四晶体管m14和第四电容c4。

286.在一些示例中,如图15所示,第十四晶体管m14的控制极与第一上拉节点q《n》电连接,第十四晶体管m14的第一极与第三时钟信号端clkf1电连接,第十四晶体管m14的第二极与第一感测信号端oput2《n》电连接。

287.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第十四晶体管m14可以在第一上拉节点q《n》的电压的控制下导通,将在第三时钟信号端clkf1处接收的第三时钟信号传输至第一感测信号端oput2《n》,并将第三时钟信号作为第一感测信号,从第一感测信号端oput2《n》输出。其中,在不同的时段导通,第一感测信号端oput2《n》输出的第一感测信号的作用不同,具体可以参照上述一些示例中的说明,此处不再赘述。

288.在一些示例中,如图15所示,第四电容c4的第一端与第一上拉节点q《n》电连接,第四电容c4的第二端与第一感测信号端oput2《n》电连接。

289.示例性的,在第一输入电路12中的第一晶体管m1导通、并对第一上拉节点q《n》进行充电的过程中,还会对第四电容器c4进行充电。在第一晶体管m1关断后,第四电容器c4可以进行放电,使得第一上拉节点q《n》的电压保持为高电平。

290.示例性的,在第一插黑子电路21导通、并对第一上拉节点q《n》进行充电的过程中,还会对第四电容器c4进行充电。在第一插黑子电路21关断后,第四电容器c4可以进行放电,使得第一上拉节点q《n》的电压保持为高电平。

291.又如,在第二插黑子电路22导通、并对第一上拉节点q《n》进行充电的过程中,还会对第四电容器c4进行充电。在第二插黑子电路22关断后,第四电容器c4可以进行放电,使得第一上拉节点q《n》的电压保持为高电平。

292.在一些实施例中,如图15所示,第二输出电路32还包括第十五晶体管m15和第五电容c5。

293.在一些示例中,如图15所示,第十五晶体管m15的控制极与第二上拉节点q《n+1》电连接,第十五晶体管m15的第一极与第四时钟信号端clkf2电连接,第十五晶体管m15的第二极与第二感测信号端oput2《n+1》电连接。

294.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第十五晶体管m15可以在第二上拉节点q《n+1》的电压的控制下导通,将在第四时钟信号端clkf2处接收的第四时钟信号传输至第二感测信号端oput2《n+1》,并将第四时钟信号作为第二感测信号,从第二感测信号端oput2《n+1》输出,驱动上至少一行子像素p进行复位。其中,在不同的时段导通,第二感测信号端oput2《n+1》输出的第二感测信号的作用不同,具体可以参照上述一些示例中的说明,此处不再赘述。

295.在一些实施例中,如图15所示,第五电容c5的第一端与第二上拉节点q《n+1》电连

接,第五电容c5的第二端与第二感测信号端oput2《n+1》电连接。

296.示例性的,在第二输入电路31中的第十晶体管m10导通、并对第二上拉节点q《n+1》进行充电的过程中,还会对第五电容c5进行充电。在第十晶体管m10关断后,第五电容c5可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

297.示例性的,在第一插黑子电路21导通、并对第二上拉节点q《n+1》进行充电的过程中,还会对第五电容c5进行充电。在第一插黑子电路21关断后,第五电容c5可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

298.或者,在第二插黑子电路22导通、并对第二上拉节点q《n+1》进行充电的过程中,还会对第五电容c5进行充电。在第一插黑子电路21关断后,第五电容c5可以进行放电,使得第二上拉节点q《n+1》的电压保持为高电平。

299.在一些实施例中,如图16和图17所示,移位寄存器100中的第一扫描单元1还包括第一复位电路13和第二复位电路14。

300.在一些示例中,如图16和图17所示,第一复位电路13与第一复位信号端std、第一上拉节点q《n》及第一电压信号端v1电连接。第一复位电路13被配置为,在第一复位信号端std所传输的第一复位信号的控制下,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》。

301.示例性的,在第一复位信号的电平为高电平的情况下,第一复位电路13可以在第一复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

302.需要说明的是,在将多个移位寄存器100级联构成扫描驱动电路1000后,除了前几级移位寄存器100(例如第一级移位寄存器100和第二级移位寄存器100等)外,其余各级移位寄存器100的第一复位信号端std可以与其后某级移位寄存器100的第一移位信号端cr2《n》电连接,进而该移位寄存器100输出的第一移位信号,可以作为相应移位寄存器100的第一复位信号。

303.相应的,部分移位寄存器100的第一复位信号端std可以与显示复位信号线电连接,示例性的,部分移位寄存器100的第一复位信号端std与比该级移位寄存器靠后三级的显示复位信号线电连接,从而接收该显示复位信号线所传输的显示复位信号作为第一复位信号。其中,该部分移位寄存器100例如可以为扫描驱动电路1000中的最后两级移位寄存器100等。这样便可以实现级联复位。

304.在一些实施例中,如图16和图17所示,在插黑电路2包括第一插黑控制子电路21和第二插黑控制子电路22的情况下,第二复位电路14与第二复位信号端trst、第一插黑节点m、第一上拉节点q《n》及第一电压信号端v1电连接。第二复位电路14被配置为,在第一插黑节点m的电压及第二复位信号端trst所传输的第二复位信号的控制下,将第一电压信号传输至第一上拉节点q《n》。

305.示例性的,在第一插黑节点m的电压为高电平、且第二复位信号的电平为高电平的情况下,第二复位电路14可以在第一插黑节点m的电压及第二复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

306.此处,第二复位电路14例如可以在显示黑画面后,对第一上拉节点q《n》进行复位。

307.在一些实施例中,如图16和图17所示,在移位寄存器100还包括第二扫描单元3的情况下,第二扫描单元3的第二输入电路31与显示输入信号端iput及第二上拉节点q《n+1》电连接。第二扫描单元3还包括第三复位电路33和第四复位电路34。

308.在一些示例中,如图16和图17所示,第三复位电路33与第一复位信号端std、第二上拉节点q《n+1》及第一电压信号端v1电连接。第三复位电路33被配置为,在第一复位信号的控制下,将第一电压信号传输至第二上拉节点q《n+1》。

309.示例性的,在第一复位信号的电平为高电平的情况下,第三复位电路33可以在第一复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

310.由于第三复位电路33和第一复位电路13均与第一复位信号端std电连接,因此,在第一复位信号的电平为高电平的情况下,第三复位电路33和第一复位电路13可以均导通,同时对第一上拉节点q《n》和第二上拉节点q《n+1》进行下拉复位。

311.在一些实施例中,如图16和图17所示,第四复位电路34与第二复位信号端trst、第一插黑节点m、第二上拉节点q《n+1》及第一电压信号端v1电连接。第四复位电路34被配置为,在第一插黑节点m的电压及第二复位信号的控制下,将第一电压信号传输至第二上拉节点q《n+1》。

312.示例性的,在第一插黑节点m的电压为高电平、且第二复位信号的电平为高电平的情况下,第四复位电路34可以在第一插黑节点m的电压及第二复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

313.由于第四复位电路34和第二复位电路14均与第一插黑节点m及第二复位信号端trst电连接,因此,在第一插黑节点m的电压为高电平、且第二复位信号的电平为高电平的情况下,第四复位电路34和第二复位电路14可以均导通,进而可以在黑画面显示后,同时对第一上拉节点q《n》和第二上拉节点q《n+1》进行下拉复位。

314.在一些实施例中,如图17所示,第一复位电路13包括第十八晶体管m18。

315.在一些示例中,如图17所示,第十八晶体管m18的控制极与第一复位信号端std电连接,第十八晶体管m18的第一极与第一上拉节点q《n》电连接,第十八晶体管m18的第二极与第一电压信号端v1电连接。

316.示例性的,在第一复位信号的电平为高电平的情况下,第十八晶体管m18可以在第一复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

317.在一些实施例中,如图17所示,第二复位电路14包括第十九晶体管m19和第二十晶体管m20。

318.在一些示例中,如图17所示,第十九晶体管m19的控制极与第一插黑节点m电连接,第十九晶体管m19的第一极与第一上拉节点q《n》电连接,第十九晶体管m19的第二极与第二十晶体管m20的第一极电连接。第二十晶体管m20的控制极与第二复位信号端trst电连接,第二十晶体管m20的第二极与第一电压信号端v1电连接。

319.示例性的,在第一插黑节点m的电压为高电平、且第二复位信号的电平为高电平的情况下,第十九晶体管m19可以在第一插黑节点m的电压控制下导通,第二十晶体管m20可以

在第二复位信号的控制下导通,第二十晶体管m20可以接收并传输第一电压信号至第十九晶体管m19的第二极,然后第十九晶体管m19将第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

320.在一些实施例中,如图17所示,第三复位电路33包括第二十一晶体管m21。

321.在一些示例中,如图17所示,第二十一晶体管m21的控制极与第一复位信号端std电连接,第二十一晶体管m21的第一极与第二上拉节点q《n+1》电连接,第二十一晶体管m21的第二极与第一电压信号端v1电连接。

322.示例性的,在第一复位信号的电平为高电平的情况下,第二十一晶体管m21可以在第一复位信号的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

323.在一些实施例中,如图17所示,第四复位电路34包括第二十二晶体管m22和第二十三晶体管m23。

324.在一些示例中,如图17所示,第二十二晶体管m22的控制极与第一插黑节点m电连接,第二十二晶体管m22的第一极与第二上拉节点q《n+1》电连接,第二十二晶体管m22的第二极与第二十三晶体管m23的第二极电连接。第二十三晶体管m23的控制极与第二复位信号端trst电连接,第二十三晶体管m23的第二极与第一电压信号端v1电连接。

325.示例性的,在第一插黑节点m的电压为高电平、且第二复位信号的电平为高电平的情况下,第二十二晶体管m22可以在第一插黑节点m的电压控制下导通,第二十三晶体管m23可以在第二复位信号的控制下导通,第二十三晶体管m23可以接收第一电压信号传输至第二十二晶体管m22的第二极,然后第二十二晶体管m22将第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

326.在一些实施例中,如图18和图19a所示,第一扫描单元1还包括第一控制电路15。

327.在一些示例中,如图18和图19a所示,第一控制电路15与第一上拉节点第一上拉结点q《n》、第一下拉节点qb-a、第一电压信号端v1及第二电压信号端v2电连接。第一控制电路15被配置为,响应于在第二电压信号端v2处接收的第二电压信号,将第二电压信号传输至第一下拉节点qb-a,并且,在第一上拉节点q《n》的电压的控制下,将第一电压信号端v1处接收的第一电压信号传输至第一下拉节点qb-a。

328.示例性的,第一控制电路15可以在第二电压信号的控制下,接收并传输第二电压信号至第一下拉节点qb-a。在第一上拉节点q《n》的电压为高电平的情况下,第一控制电路15可以在第一上拉节点q《n》的电压的控制下,接收并传输第一电压信号至第一下拉节点qb-a,对第一下拉节点qb-a进行下拉复位。

329.在一些实施例中,如图18和图19a所示,在移位寄存器100还包括第二扫描单元3的情况下,第二扫描单元3的第二输入电路31与显示输入信号端iput及第二上拉节点q《n+1》电连接,第二扫描单元3还包括第二控制电路35。

330.在一些示例中,如图18和图19a所示,第二控制电路35与第二上拉节点q《n+1》、第二下拉节点qb-b、第一电压信号端v1及第三电压信号端v3电连接。第二控制电路35被配置为,响应于在第三电压信号端v3处接收的第三电压信号,将第三电压信号传输至第二下拉节点qb-b,并且,在第二上拉节点qb-b的电压的控制下,将第一电压信号传输至第二下拉节点qb-b。

331.示例性的,第二控制电路35可以在第三电压信号的控制下,接收并传输第三电压信号至第二下拉节点qb-b。在第二上拉节点q《n+1》的电压为高电平的情况下,第二控制电路35可以在第二上拉节点q《n+1》的电压的控制下,接收并传输第一电压信号传输至第二下拉节点qb-b,对第二下拉节点qb-b进行下拉复位。

332.需要说明的是,第二电压信号端v2例如可以被配置为传输直流高电平信号(例如高于或等于时钟信号的高电平部分)。第三电压信号端v3例如可以被配置为传输直流高电平信号(例如高于或等于时钟信号的高电平部分)。本文中提及的“高电平”和“低电平”是相对而言的。示例性的,第二电压信号的电压值大于第一电压信号的电压值。

333.在一些实施例中,如图19a所示,第一控制电路15包括第二十四晶体管m24、第二十五晶体管m25、第二十六晶体管m26和第二十七晶体管m27。

334.在一些示例中,如图19a所示,第二十四晶体管m24的控制极与第二电压信号端v2电连接,第二十四晶体管m24的第一极与第二电压信号端v2电连接,第二十四晶体管m24的第二极与第二十五晶体管m25的控制极及第二十六晶体管m26的第一极电连接。第二十五晶体管m25的第一极与第二电压信号端v2电连接,第二十五晶体管m25的第二极与第一下拉节点qb-a电连接。

335.示例性的,第二十四晶体管m24可以在第二电压信号的控制下导通,接收并传输第二电压信号至第二十五晶体管m25的控制极。第二十五晶体管m25可以在该第二电压信号的控制下导通,接收并传输第二电压信号至第一下拉节点qb-a,对第一下拉节点qb-a进行充电,使得第一下拉节点qb-a的电压抬升。

336.在一些示例中,如图19a所示,第二十六晶体管m26的控制极与第一上拉节点电q《n》连接,第二十六晶体管m26的第二极与第一电压信号端v1电连接。

337.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第二十六晶体管m26可以在第一上拉节点q《n》的电压的控制下导通,接收并传输第一电压信号至第二十五晶体管m25的控制极,第二十五晶体管m25可以在第一电压信号的控制下关断。

338.在一些示例中,如图19a所示,第二十七晶体管m27的控制极与第一上拉节点q《n》电连接,第二十七晶体管m27的第一极与第一下拉节点qb-a电连接,第二十七晶体管m27的第二极与第一电压信号端v1电连接。

339.示例性的,在第一上拉节点q《n》的电压为高电平的情况下,第二十七晶体管m27可以在第一上拉节点q《n》的控制下导通,接收并传输第一电压信号至第一下拉节点qb-a,对第一下拉节点qb-a进行下拉复位。

340.在一些实施例中,如图19a所示,第二控制电路35包括:第二十八晶体管m28、第二十九晶体管m29、第三十晶体管m30和第三十一晶体管m31。

341.在一些示例中,如图19a所示,第二十八晶体管m28的控制极与第三电压信号端v3电连接,第二十八晶体管m28的第一极与第三电压信号端v3电连接,第二十八晶体管m28的第二极与第二十九晶体管m29的控制极及第三十晶体管m30的第一极电连接。第二十九晶体管m29的第一极与第三电压信号端v3电连接,第二十九晶体管m29的第二极与第二下拉节点qb-b电连接。

342.示例性的,第二十八晶体管m28可以在第三电压信号的控制下导通,接收并传输第三电压信号至第二十九晶体管m29的控制极。第二十九晶体管m29可以在该第三电压信号的

控制下导通,接收并传输第三电压信号至第二下拉节点qb-b,对第二下拉节点qb-b进行充电,使得第二下拉节点qb-b的电压抬升。

343.在一些示例中,如图19a所示,第三十晶体管m30的控制极与第二上拉节点q《n+1》电连接,第三十晶体管m30的第二极与第一电压信号端v1电连接。

344.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第三十晶体管m30可以在第二上拉节点q《n+1》的电压的控制下导通,接收并传输第一电压信号至第二十九晶体管m29的控制极,第二十九晶体管m29可以在第一电压信号的控制下关断。

345.在一些示例中,如图19a所示,第三十一晶体管m31的控制极与第二上拉节点q《n+1》电连接,第三十一晶体管m31的第一极与第二下拉节点qb-b电连接,第三十一晶体管m31的第二极与第一电压信号端v1电连接。

346.示例性的,在第二上拉节点q《n+1》的电压为高电平的情况下,第三十一晶体管m31可以在第二上拉节点q《n+1》的电压的控制下导通,接收并传输第一电压信号第二下拉节点qb-b,对第二下拉节点qb-b进行下拉复位。

347.在一些实施例中,如图18和图19a所示,第一扫描单元1还包括第五复位电路16和第六复位电路17。

348.在一些示例中,如图18和图19a所示,第五复位电路16与第一上拉节点q《n》、第一下拉节点qb-a及第一电压信号端v1电连接;第五复位电路16被配置为,在第一下拉节点qb-a的电压的控制下,将第一电压信号传输至第一上拉节点q《n》。

349.示例性的,在第一下拉节点qb-a的电压为高电平的情况下,第五复位电路16可以在第一下拉节点qb-a的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

350.在一些示例中,如图18和图19a所示,第六复位电路17与第一下拉节点qb-a、第一扫描信号端oput1《n》及第四电压信号端v4电连接;第六复位电路17被配置为,在第一下拉节点qb-a的电压的控制下,将第四电压信号端v4处接收的第四电压信号传输至第一扫描信号端oput1《n》。

351.示例性的,在第一下拉节点qb-a的电压高电平的情况下,第六复位电路17可以在第一下拉节点qb-a的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第一扫描信号端oput1《n》,并对第一扫描信号端oput1《n》进行下拉复位。

352.此处,第四电压信号端v4例如可以被配置为传输直流低电平信号(例如低于或等于时钟信号的低电平部分)。示例性的,该第四电压信号端v4接地。其中,第一电压信号的电压值和第四电压信号的电压值可以相等,也可以不相等。

353.在一些实施例中,如图18和图19a所示,在第一输出电路12还与第三时钟信号端clkf1及第一感测信号端oput2《n》电连接的情况下,第六复位电路17还与第一感测信号端oput2《n》电连接;第六复位电路17还被配置为,在第一下拉节点qb-a的电压的控制下,将第四电压信号传输至第一感测信号端oput2《n》。

354.示例性的,在第一下拉节点qb-a的电压高电平的情况下,第六复位电路17可以在第一下拉节点qb-a的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第一感测信号端oput2《n》,并对第一感测信号端oput2《n》进行下拉复位。

355.在一些实施例中,如图18和图19a所示,第一输出电路12还与第五时钟信号端

clkd1及第一移位信号端cr2《n》电连接的情况下,第六复位电路17还与第一移位信号端clkd1及第一电压信号端v1电连接;第六复位电路17还被配置为,在第一下拉节点qb-a的电压的控制下,将第一电压信号传输至第一移位信号端cr2《n》。

356.示例性的,在第一下拉节点qb-a的电压为高电平的情况下,第六复位电路17可以在第一下拉节点qb-a的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一移位信号端cr2《n》,对第一移位信号端cr2《n》进行下拉复位。

357.在一些实施例中,如图18和图19a所示,移位寄存器100还包括第二扫描单元3的情况下,第二扫描单元3的第二输入电路31与显示输入信号端iput及第二上拉节q《n+1》点电连接。第二扫描单元3还包括第七复位电路36和第八复位电路37。

358.在一些示例中,如图18和图19a所示,第七复位电路36与第二上拉节点q《n+1》、第二下拉节点qb-b及第一电压信号端v1电连接;第七复位电路36被配置为,在第二下拉节点qb-b的电压的控制下,将第一电压信号传输至第二上拉节点q《n+1》。

359.示例性的,在第二下拉节点qb-b的电压的为高电平的情况下,第七复位电路36可以在第二下拉节点qb-b的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

360.在一些示例中,如图18和图19a所示,第八复位电路37与第二下拉节点qb-b、第二扫描信号端oput1《n+1》及第四电压信号端v4电连接;第八复位电路37被配置为,在第二下拉节点qb-b的电压的控制下,将第四电压信号传输至第二扫描信号端oput1《n+1》。

361.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第八复位电路37可以在第二下拉节点qb-b的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第二扫描信号端oput1《n+1》,对第二扫描信号端oput1《n+1》进行下拉复位。

362.在一些示例中,如图18和图19a所示,在第二输出电路32还与第四时钟信号端clkf2及第二感测信号端oput2《n+1》电连接的情况下,第八复位电路37还与第二感测信号端oput2《n+1》电连接;第八复位电路37还被配置为,在第二下拉节点qb-b的电压的控制下,将第四电压信号传输至第二感测信号端oput2《n+1》。

363.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第八复位电路37可以在第二下拉节点qb-b的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第二感测信号端oput2《n+1》,对第二感测信号端oput2《n+1》进行下拉复位。

364.在一些示例中,如图18和图19a所示,在第二输出电路32还与第六时钟信号端clkd2及第二移位信号端cr《n+1》电连接的情况下,第八复位电路37还与第二移位信号端cr《n+1》及第一电压信号端v1电连接;第八复位电路37还被配置为,在第二下拉节点qb-b的电压的控制下,将第一电压信号传输至第二移位信号端cr《n+1》。

365.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第八复位电路37可以在第二下拉节点qb-b的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二移位信号端cr《n+1》,对第二移位信号端cr《n+1》进行下拉复位。

366.在一些实施例中,如图19a所示,第五复位电路16包括第三十二晶体管m32。

367.在一些示例中,如图19a所示,第三十二晶体管m32的控制极与第一下拉节点qb-a电连接,第三十二晶体管m32的第一极与第一上拉节点q《n》电连接,第三十二晶体管m32的第二极与第一电压信号端v1电连接。

368.示例性的,在第一下拉节点qb-a的电压为高电平的情况下,第三十二晶体管m32可以在第一下拉节点qb-a的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一上拉节点q《n》,对第一上拉节点q《n》进行下拉复位。

369.在一些实施例中,如图19a所示,第六复位电路17包括第三十三晶体管m33、第三十四晶体管m34和第三十五晶体管m35。

370.在一些示例中,如图19a所示,第三十三晶体管m33的控制极与第一下拉节点qb-a电连接,第三十三晶体管m33的第一极与第一扫描信号端oput1《n》电连接,第三十三晶体管m33的第二极与第四电压信号端v4电连接。

371.示例性的,在第一下拉节点qb-a的电压高电平的情况下,第三十三晶体管m33可以在第一下拉节点qb-a的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第一扫描信号端oput1《n》,并对第一扫描信号端oput1《n》进行下拉复位。

372.在一些示例中,如图19a所示,第三十四晶体管m34的控制极与第一下拉节点qb-a电连接,第三十四晶体管m34的第一极与第一感测信号端oput2《n》电连接,第三十四晶体管m34的第二极与第四电压信号端v4电连接。

373.示例性的,在第一下拉节点qb-a的电压高电平的情况下,第三十四晶体管m34可以在第一下拉节点qb-a的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第一感测信号端oput2《n》,并对第一感测信号端oput2《n》进行下拉复位。

374.在一些示例中,如图19a所示,第三十五晶体管m35的控制极与第一下拉节点qb-a电连接,第三十五晶体管m35的第一极与第一移位信号端cr2《n》电连接,第三十五晶体管m35的第二极与第一电压信号端v1电连接。

375.示例性的,在第一下拉节点qb-a的电压为高电平的情况下,第三十五晶体管m35可以在第一下拉节点qb-a的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第一移位信号端cr2《n》,对第一移位信号端cr2《n》进行下拉复位。qb-b

376.在一些实施例中,如图19a所示,第七复位电路36包括第三十六晶体管m36。

377.在一些示例中,如图19a所示,第三十六晶体管m36的控制极与第二下拉节点qb-b电连接,第三十六晶体管m36的第一极与第二上拉节点q《n+1》电连接,第三十六晶体管m36的第二极与第一电压信号端v1电连接。

378.示例性的,在第二下拉节点qb-b的电压的为高电平的情况下,第三十六晶体管m36可以在第二下拉节点qb-b的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二上拉节点q《n+1》,对第二上拉节点q《n+1》进行下拉复位。

379.在一些实施例中,如图19a所示,第八复位电路37包括第三十七晶体管m37、第三十八晶体管m38和第三十九晶体管m39。

380.在一些示例中,如图19a所示,第三十七晶体管m37的控制极与第二下拉节点qb-b电连接,第三十七晶体管m37的第一极与第二扫描信号端oput1《n+1》电连接,第三十七晶体管m37的第二极与第四电压信号端v4电连接。

381.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第三十七晶体管m37可以在第二下拉节点qb-b的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第二扫描信号端oput1《n+1》,对第二扫描信号端oput1《n+1》进行下拉复位。

382.在一些示例中,如图19a所示,第三十八晶体管m38的控制极与第二下拉节点qb-b

电连接,第三十八晶体管m38的第一极与第二感测信号端oput2《n+1》电连接,第三十八晶体管m38的第二极与第四电压信号端v4电连接。

383.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第三十八晶体管m38可以在第二下拉节点qb-b的电压的控制下导通,将在第四电压信号端v4处接收的第四电压信号传输至第二感测信号端oput2《n+1》,对第二感测信号端oput2《n+1》进行下拉复位。

384.在一些示例中,如图19a所示,第三十九晶体管m39的控制极与第二下拉节点qb-b电连接,第三十九晶体管m39的第一极与第二移位信号端cr《n+1》电连接,第三十九晶体管m39的第二极与第一电压信号端v1电连接。

385.示例性的,在第二下拉节点qb-b的电压为高电平的情况下,第三十九晶体管m39可以在第二下拉节点qb-b的电压的控制下导通,将在第一电压信号端v1处接收的第一电压信号传输至第二移位信号端cr《n+1》,对第二移位信号端cr《n+1》进行下拉复位。

386.在一些实施例中,本发明所提供的移位寄存器100中子电路共用的设计的整体结构图如图19b所示,该移位寄存器100中除共用子电路(第一插黑输入子电路212和第二插黑输入子电路222、第一插黑传输子电路213和第二插黑传输子电路223及第三插黑传输子电路214和第四插黑传输子电路224)之外,其他子电路的结构可参见对于图19a中子电路结构的相关描述,此处不再赘述。

387.本公开的一些实施例提供的扫描驱动电路1000中,如图20~图30所示,该扫描驱动电路1000包括多级级联的移位寄存器100。多级移位寄存器100包括多个移位寄存器组c。

388.在一些实施例中,上述移位寄存器100可以包括第一扫描单元1。

389.在另一些实施例中,如图20~图30所示,上述移位寄存器100包括第一扫描单元1和第二扫描单元3。

390.下面以各级移位寄存器100包括第一扫描单元1和第二扫描单元3为例,且第一插黑输入子电路212和第二插黑输入子电路222非同一子电路,第一插黑传输子电路213和第二插黑传输子电路223非同一子电路,第三插黑传输子电路214和第四插黑传输子电路224非同一子电路,对扫描驱动电路1000的结构进行示意性说明。

391.在一些示例中,如图20~图25所示,每个移位寄存器组c包括2级移位寄存器,也就是说,各移位寄存器组c所包括的移位寄存器100的数量相同。其中,每级移位寄存器100包括第一扫描单元1和第二扫描单元3。相应的,每个移位寄存器组c可以有四个扫描信号端,例如与四行子像素p分别电连接。

392.需要说明的是,如图20所示,移位寄存器组c包括五类移位寄存器组c,第一类移位寄存器组c为c0(dum1-dum4),移位寄存器组c0连接四行dum子像素,移位寄存器组c0(dum1-dum4)也称为第一个移位寄存器组c0(dum1-dum4);第二类移位寄存器组c为移位寄存器组c1,移位寄存器组c1包括两级移位寄存器100,每级移位寄存器100包括第一扫描单元1和第二扫描单元3,即每级移位寄存器100连接两行子像素,那么,移位寄存器组c1连接四行子像素,第二个移位寄存器组c1(1-4)为移位寄存器组c1的其中一组;第三类移位寄存器组c为移位寄存器组c2,同理,移位寄存器组c2包括两级移位寄存器100,此处不再赘述,第三个移位寄存器组c2(5-8)为移位寄存器组c2的其中一组;第四类移位寄存器组c为移位寄存器组c3,同理,移位寄存器组c3包括两级移位寄存器100,此处不再赘述,第四个移位寄存器组c3(9-12)为移位寄存器组c3的其中一组;第五类移位寄存器组c为移位寄存器组c4,同理,移

位寄存器组c4包括两级移位寄存器100,此处不再赘述,第五个移位寄存器组c4(13-16)为移位寄存器组c4的其中一组。其中,除移位寄存器组c0外,移位寄存器组c1、移位寄存器组c2、移位寄存器组c3和移位寄存器组c4为一个周期,交替设置。

393.在一些实施例中,如图21所示,第一个移位寄存器组c0所包括的2级移位寄存器为虚设移位寄存器100。

394.需要说明的是,2级虚设移位寄存器100用于连接显示装置2000边框区b的四行dum子像素,该四行dum子像素不用于实际显示。

395.示例性的,第一个移位寄存器组c0包括两级虚设移位寄存器100,每级虚设移位寄存器100包括第一扫描单元1和第二扫描单元3,也即,第一个移位寄存器组c0有四个扫描信号端,例如与四行dum子像素p分别电连接。

396.在一些实施例中,如图20所示,从第一个移位寄存器组c0开始,每相邻两个移位寄存器组为一对移位寄存器组,多个移位寄存器组被划分为交替排列的多个第一对移位寄存器组cc1和多个第二对移位寄存器组cc2。

397.需要说明的是,第一个移位寄存器组c0之后的四个移位寄存器组依次为第二个移位寄存器组c1、第三个移位寄存器组c2、第四个移位寄存器组c3和第五个移位寄存器组c4,且之后的移位寄存器组依然以四个为一个周期设置,例如,依次为第六个移位寄存器组c1、第七个移位寄存器组c2、第八个移位寄存器组c3和第九个移位寄存器组c4,以此类推。

398.示例性的,第一个移位寄存器组c0和第二个移位寄存器组c1为第一对移位寄存器组cc1,第三个移位寄存器组c2和第四个移位寄存器组c3为第二对移位寄存器组cc2,第五个移位寄存器组c4和第六个移位寄存器组c1为第一对移位寄存器组cc1,第七个移位寄存器组c2和第八个移位寄存器组c3为第二对移位寄存器组cc2,如此交替设置。

399.在一些实施例中,如图20所示,从第二个移位寄存器组c1开始,每相邻两个移位寄存器组为一对移位寄存器组,多个移位寄存器组被划分为交替排列的多个第三对移位寄存器组cc3和多个第四对移位寄存器组cc4。

400.示例性的,第二个移位寄存器组c1和第三个移位寄存器组c2为第三对移位寄存器组cc3,第四个移位寄存器组c3和第五个移位寄存器组c4为第四对移位寄存器组cc4,第六个移位寄存器组c1和第七个移位寄存器组c2为第三对移位寄存器组cc3,如此交替设置。

401.需要说明的是,第三对移位寄存器组cc3和第四对移位寄存器组cc4均包括四级移位寄存器100,即第三对移位寄存器组cc3包括:第一级移位寄存器100、第二级移位寄存器100、第三级移位寄存器100和第四级移位寄存器100,第四对移位寄存器组cc4包括:第一级移位寄存器100、第二级移位寄存器100、第三级移位寄存器100和第四级移位寄存器100。

402.在一些实施例中,如图22~图26所示,扫描驱动电路1000还包括第一控制信号线组,第一控制信号线组包括第一子控制信号线bck1和第三子控制信号线bck3。第一子控制信号线bck1与第三对移位寄存器组cc3中各移位寄存器100的第一控制信号端bcs1电连接,第三子控制信号线bck3与第四对移位寄存器组cc4中各移位寄存器100的第一控制信号端bcs1电连接。

403.示例性的,在扫描驱动电路1000进行工作的过程中,可以通过第一子控制信号线bck1向各第三对移位寄存器组cc3中的第一控制信号端bcs1传输第一控制信号,控制各第三对移位寄存器组cc3中的第一插黑子电路21中的第一插黑控制子电路211导通,并对所接

收的第一插黑级联信号进行存储;可以通过第三子控制信号线bck3向各第四对移位寄存器组cc4中的第一控制信号端bcs1传输第一控制信号,控制各第四对移位寄存器组cc4中的第一插黑子电路21中的第一插黑控制子电路211导通,并对所接收的第一插黑级联信号进行存储。

404.此处,在第一插黑输入信号的电平为高电平的情况下,则可以使得相应的第一插黑输入子电路212导通,将第一插黑输入信号传输至第二插黑节点k1。在第一插黑输入信号的电平为低电平的情况下,则可以使得相应的第一插黑输入子电路212关断。

405.在一些实施例中,如图22~图26所示,扫描驱动电路1000还包括第二控制信号线组,第二控制信号线组包括第二子控制信号线bck2和第四子控制信号线bck4。第二子控制信号线bck2与第三对移位寄存器组cc3中各移位寄存器100的第二控制信号端bcs2电连接,第四子控制信号线bck4与第四对移位寄存器组cc4中各移位寄存器100的第二控制信号端bcs2电连接。

406.示例性的,第三对移位寄存器组cc3中各移位寄存器100的第二控制信号端bcs2可以同时接收第二控制信号。第四对移位寄存器组cc4中各移位寄存器100的第二控制信号端bcs2同时接收第二控制信号。

407.在一些实施例中,如图22~图26所示,第二子控制信号线bck2还与第三对移位寄存器组cc3中各移位寄存器100的第一插黑输入信号端bi1电连接。第四子控制信号线bck4还与所述第四对移位寄存器组cc4中各移位寄存器100的第一插黑输入信号端bi1电连接。

408.也就是说,第二控制信号端bcs2和第一插黑输入信号端bi1为相同的信号端。

409.此时,第三对移位寄存器组cc3中各移位寄存器100的第二控制信号端bcs2和第一插黑输入信号端bi1接收来自同一条第二子控制信号线bck2的信号。第四对移位寄存器组cc4中各移位寄存器100的第二控制信号端bcs2和第一插黑输入信号端bi1接收来自同一条第四子控制信号线bck4的信号。这样有利于减少信号线的数量,简化扫描驱动电路1000的结构。

410.在扫描驱动电路1000进行工作的过程中,可以通过第二子控制信号线bck2向各第三对移位寄存器组cc3中的第二控制信号端bcs2及第一插黑输入信号端bi1传输相同的信号,控制各第三对移位寄存器组cc3中的第一插黑传输子电路213和第三插黑传输子电路214导通。在第二子控制信号线bck2所传输的第二子控制信号为高电平的情况下,上述的第一插黑传输子电路213导通,并将高电平的第二子控制信号传输至第一上拉结点q《n》,抬高第一上拉结点q《n》的电压,上述第三插黑传输子电路214导通,并将高电平的第二子控制信号传输至第二上拉结点q《n+1》,抬高第二上拉结点q《n+1》的电压。之后便可以通过第一时钟信号端clke1所传输的第一时钟信号及第二时钟信号端clke2所传输的第二时钟信号,控制与第三对移位寄存器组cc3相对应的八行子像素p同时显示黑画面。

411.同理,对于第四对移位寄存器组cc4的工作过程参照上述说明,此处不再赘述。

412.需要说明的是,在第三对移位寄存器组cc3相对应的八行子像素p显示黑画面的过程中,第四对移位寄存器组cc4相对应的八行子像素p可以进行图像显示。

413.在一些实施例中,如图21~图26所示,扫描驱动电路1000还包括第三控制信号线组,第三控制信号线组包括第五子控制信号线bck5和第七子控制信号线bck7。第五子控制信号线bck5与第一对移位寄存器组cc1中各移位寄存器100的第五控制信号端bcs5电连接,

第七子控制信号线bck7与第二对移位寄存器组cc2中各移位寄存器100的第五控制信号端bck5电连接。

414.示例性的,在扫描驱动电路1000进行工作的过程中,可以通过第五子控制信号线bck5向各第一对移位寄存器组cc1中的第五控制信号端bck5传输第五控制信号,控制各第一对移位寄存器组cc1中的第二插黑子电路22中的第二插黑控制子电路221导通,并对所接收的第二插黑级联信号进行存储;可以通过第七子控制信号线bck7向各第二对移位寄存器组cc2中第五控制信号端bck5传输第五控制信号,控制各第二对移位寄存器组cc2中的第二插黑子电路22中的第二插黑控制子电路221导通,并对所接收的第二插黑级联信号进行存储。

415.此处,在第二插黑输入信号的电平为高电平的情况下,则可以使得相应的第二插黑输入子电路222导通,将第二插黑输入信号传输至第三插黑节点k3。在第二插黑输入信号的电平为低电平的情况下,则可以使得相应的第二插黑输入子电路222关断。

416.在一些实施例中,如图21~图26所示,扫描驱动电路1000还包括第四控制信号线组,第四控制信号线组包括第六子控制信号线bck6和第八子控制信号线bck8。第六子控制信号线bck6与第一对移位寄存器组cc1中各移位寄存器100的第六控制信号端bcs6电连接,第八子控制信号线bck8与第二对移位寄存器组cc2中各移位寄存器100的第六控制信号端bcs6电连接。

417.示例性的,第一对移位寄存器组cc1中各移位寄存器100的第六控制信号端bcs6可以同时接收第六控制信号。第二对移位寄存器组cc2中各移位寄存器100的第六控制信号端bcs6可以同时接收第六控制信号。

418.在一些实施例中,如图21~图26所示,第六子控制信号线bck6还与第一对移位寄存器组cc1中各移位寄存器100的第二插黑输入信号端bi2电连接。第八子控制信号线bck8还与第二对移位寄存器组cc2中各移位寄存器100的第二插黑输入信号端bi2电连接。

419.也就是说,第六控制信号端bcs6和第二插黑输入信号端bi2为相同的信号端。

420.此时,第一对移位寄存器组cc1中各移位寄存器100的第六控制信号端bcs6和第二插黑输入信号端bi2接收来自同一条第六子控制信号线bck6的信号。第二对移位寄存器组cc2中各移位寄存器100的第六控制信号端bcs6和第二插黑输入信号端bi2接收来自同一条第八子控制信号线bck8的信号。这样有利于减少信号线的数量,简化扫描驱动电路1000的结构。

421.在扫描驱动电路1000进行工作的过程中,可以通过第六子控制信号线bck6向各第一对移位寄存器组cc1中的第六控制信号端bcs6及第二插黑输入信号端bi2传输相同的信号,控制各第一对移位寄存器组cc1中的第二插黑传输子电路223和第四插黑传输子电路224导通。在第六子控制信号线bck6所传输的第六子控制信号为高电平的情况下,上述的第二插黑传输子电路223导通,并将高电平的第六子控制信号传输至第一上拉结点q《n》,抬高第一上拉结点q《n》的电压,上述第四插黑传输子电路224导通,并将高电平的第六子控制信号传输至第二上拉结点q《n+1》,抬高第二上拉结点q《n+1》的电压。之后便可以通过第一时钟信号端clke1所传输的第一时钟信号及第二时钟信号端clke2所传输的第二时钟信号,控制与第一对移位寄存器组cc1相对应的八行子像素p同时显示黑画面。

422.同理,对于第二对移位寄存器组cc2的工作过程参照上述说明,此处不再赘述。

423.需要说明的是,在第一对移位寄存器组cc1相对应的八行子像素p显示黑画面的过程中,第二对移位寄存器组cc2相对应的八行子像素p可以进行图像显示。

424.由此,如图27所示,可以在一帧图像显示的过程中,通过第一控制信号线组和第二控制信号线组控制交替设置的第三对移位寄存器组cc3和第四对移位寄存器组cc4中的一对移位寄存器组进行插黑显示,示例性的,在一帧显示图像中,控制同时插黑的八行子像素为1-8子像素、9-16子像素、17-24子像素

……

。如图28所示,可以在下一帧图像显示的过程中,通过第三控制信号线组和第四控制信号线组控制交替设置的第一对移位寄存器组cc1和第二对移位寄存器组cc2中的一对移位寄存器组进行插黑显示,示例性的,在一帧显示图像中,控制同时插黑的八行子像素为1-4四行子像素和前四行dum子像素、5-12八行子像素、13-20八行子像素

……

。实现缩小相邻行显示时长差的目的,避免出现横纹,提高产品的良率。

425.需要说明的是,如图27和图28所示,图中1、2分别表示控制第一行子像素的第一级移位寄存器100的第一扫描单元1、控制第二行子像素的第一级移位寄存器100的第二扫描单元3、图中3、4分别表示控制第三行子像素的第三行子像素的第二级移位寄存器100的第一扫描单元1、控制第四行子像素的第二级移位寄存器100的第二扫描单元3

……

以此类推,此处不再赘述。图中dum1、dum2分别表示控制第一行dum子像素的第一级移位寄存器100的第一扫描单元1、控制第二行dum子像素的第一级移位寄存器100的第二扫描单元3,dum1、dum2以此类推。

426.在一些实施例中,如图22~图26所示,扫描驱动电路1000还包括第一时钟信号线组,第一时钟信号线组包括十六个第一时钟信号线cke。十六个第一时钟信号线cke分别与第三对移位寄存器组cc3中各移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2、第四对移位寄存器组cc4中各移位寄存器的第一时钟信号端clke1及第二时钟信号端电连接clke2。

427.示例性的,该十六个第一时钟信号线cke可以包括:分别与各第三对移位寄存器组cc3中的第一级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之一cke_1和第一子时钟信号线之二cke_2;分别与各第三对移位寄存器组cc3中的第二级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之三cke_3和第一子时钟信号线之四cke_4;分别与各第三对移位寄存器组cc3中的第三级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之五cke_5和第一子时钟信号线之六cke_6;分别与各第三对移位寄存器组cc3中的第四级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之七cke_7和第一子时钟信号线之八cke_8;分别与各第四对移位寄存器组cc4中的第一级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之九cke_9和第一子时钟信号线之十cke_10;分别与各第四对移位寄存器组cc4中的第二级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之十一cke_11和第一子时钟信号线之十二cke_12;分别与各第四对移位寄存器组cc4中的第三级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子时钟信号线之十三cke_13和第一子时钟信号线之十四cke_14;分别与各第四对移位寄存器组cc4中的第四级移位寄存器100的第一时钟信号端clke1

及第二时钟信号端clke2电连接的第一子时钟信号线之十五cke_15和第一子时钟信号线之十六cke_16。

428.当然,上述第一子时钟信号线cke的连接顺序可以调换,并不局限于上述连接方式。

429.在一些实施例中,如图21和图26所示,扫描驱动电路1000还包括第一虚设时钟信号线组,第一虚设时钟信号线组包括四个第一虚设时钟信号线cke_d;四个第一虚设时钟信号线分别与第一个移位寄存器组c0中的各虚设移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接。

430.示例性的,该四个第一虚设时钟信号线cke_d可以包括:分别与第一个移位寄存器组c0中的第一级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子虚设时钟信号线之一cke_d1和第一子虚设时钟信号线之二cke_d2;分别与第一个移位寄存器组c0中的第二级移位寄存器100的第一时钟信号端clke1及第二时钟信号端clke2电连接的第一子虚设时钟信号线之三cke_d3和第一子虚设时钟信号线之四cke_d4。

431.当然,上述第一子虚设时钟信号线cke_d的连接顺序可以调换,并不局限于上述连接方式。

432.在一些实施例中,如图22~图26所示,在移位寄存器100的第一输出电路12还与第三时钟信号端clkf1及第一感测信号端oput2《n》电连接、第二输出电路32还与第四时钟信号端clkf2及第二感测信号端oput2《n+1》电连接的情况下,扫描驱动电路1000还包括第二时钟信号线组,第二时钟信号线组包括十六个第二时钟信号线ckf,该十六个第二时钟信号线ckf分别与第三对移位寄存器组cc3中各移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2、第四对移位寄存器组cc2中各移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接。

433.示例性的,该十六个第二时钟信号线ckf可以包括:分别与各第三对移位寄存器组cc3中的第一级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之一ckf_1和第二子时钟信号线之二ckf_2;分别与各第三对移位寄存器组cc3中的第二级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之三ckf_3和第二子时钟信号线之四ckf_4;分别与各第三对移位寄存器组cc3中的第三级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之五ckf_5和第二子时钟信号线之六ckf_6;分别与各第三对移位寄存器组cc3中的第四级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之七ckf_7和第二子时钟信号线之八ckf_8;分别与各第四对移位寄存器组cc4中的第一级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之九ckf_9和第二子时钟信号线之十ckf_10;分别与各第四对移位寄存器组cc4中的第二级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之十一ckf_11和第二子时钟信号线之十二ckf_12;分别与各第四对移位寄存器组cc4中的第三级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之十三ckf_13和第二子时钟信号线之十四ckf_14;分别与各第四对移位寄存器组cc4中的第四级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子时钟信号线之十五ckf_15和第二子时钟信号线之

十六ckf_16。

434.当然,上述第二子时钟信号线ckf的连接顺序可以调换,并不局限于上述连接方式。

435.在一些实施例中,如图21和图26所示,扫描驱动电路1000还包括第二虚设钟信号线组。第二虚设钟信号线组包括四个第二虚设钟信号线ckf_d。四个第二虚设钟信号线ckf_d分别与第一个移位寄存器组c0中的各虚设移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接。

436.示例性的,该四个第二虚设钟信号线ckf_d可以包括:分别与第一个移位寄存器组c0中的第一级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子虚设钟信号线之一ckf_d1和第二子虚设钟信号线之二ckf_d2;分别与第一个移位寄存器组c0中的第二级移位寄存器100的第三时钟信号端clkf1及第四时钟信号端clkf2电连接的第二子虚设钟信号线之三ckf_d3和第二子虚设钟信号线之四ckf_d4。

437.当然,上述第二子虚设钟信号线ckf_d的连接顺序可以调换,并不局限于上述连接方式。

438.在一些实施例中,如图22~图26所示,在移位寄存器100的第一输出电路12还与第五时钟信号端clkd1及第一移位信号端cr2《n》电连接、第二输出电路32还与第六时钟信号端clkd2及第二移位信号端cr《n+1》电连接。

439.在此情况下,多级移位寄存器100中,除前两级移位寄存器100外,其余级移位寄存器100的显示输入信号端iput,与比该级移位寄存器100靠前两级的移位寄存器100的第二移位信号端cr《n+1》电连接。

440.除前四级移位寄存器100外,其余级移位寄存器100的第一插黑级联信号端bcr1、第二插黑级联信号端bcr2,与比该级移位寄存器100靠前四级的移位寄存器100的第一移位信号端cr2《n》电连接。

441.也即,奇数行的移位信号端所传输的移位信号作为插黑级联信号,偶数行的移位信号端所传输的移位信号作为显示级联信号。

442.需要说明的是,前两级移位寄存器100的显示输入信号端iput可以与第一起始信号线stu1电连接。

443.其中,如图26所示,前六级移位寄存器100的第一插黑级联信号端bcr1、第二插黑级联信号端bcr2与第二起始信号线stu2电连接。

444.示例性的,如图26所示,在进行第一帧图像插黑显示的过程中,前两级dum的第一插黑子电路21和第二插黑子电路22关断,不进行插黑级联信号的导通,具体控制过程如前所述,此处不再赘述;第三级至第六级的移位寄存器100的第一插黑级联信号端bcr1和第二插黑级联信号端bcr2接收第二起始信号线stu2所传输的插黑信号,进行黑图像的显示,实现在第一帧图像中第三对移位寄存器组cc3或者第四对移位寄存器组cc4的插黑显示。在进行第二帧图像插黑显示的过程中,前两级dum的第一插黑子电路21和第二插黑子电路22、及第三级和第四级的移位寄存器100的第一插黑级联信号端bcr1和第二插黑级联信号端bcr2接收第二起始信号线stu2所传输的插黑信号,进行黑图像的显示,实现在第二帧图像中第一对移位寄存器组cc1或者第二对移位寄存器组cc2的插黑显示,如此交替进行,实现在相邻帧图像显示中,不同的组进行插黑级联,实现缩小相邻行显示时间差的目的。

445.或者,如图27和图28所示,第一级至第四级的移位寄存器100的第一插黑级联信号端bcr1、第二插黑级联信号端bcr2与第二起始信号线电stu2连接。第三级至第六级的移位寄存器100的第一插黑级联信号端bcr1、第二插黑级联信号端bcr2与第三起始信号线stu3电连接。

446.示例性的,如图27和图28所示,对起始插黑级联信号的输入通过第二起始信号线电stu2和第三起始信号线stu3分别控制。在第一帧显示图像中,通过第三级至第六级的移位寄存器100的第一插黑级联信号端bcr1、第二插黑级联信号端bcr2接收第三起始信号线stu3实现黑图像的显示,实现在第一帧图像中第三对移位寄存器组cc3或者第四对移位寄存器组cc4的插黑显示。在第二帧显示图像中,前两级dum的第一插黑子电路21和第二插黑子电路22、及第三级和第四级的移位寄存器100的第一插黑级联信号端bcr1和第二插黑级联信号端bcr2接收第二起始信号线stu2所传输的插黑信号,实现在第二帧图像中第一对移位寄存器组cc1或者第二对移位寄存器组cc2的插黑显示,如此交替进行,实现在相邻帧图像显示中,不同的组进行插黑级联,实现缩小相邻行显示时间差的目的。

447.需要说明的是,第一起始信号线stu1、第二起始信号线stu2和第三起始信号线stu3所传输的起始信号的电平为高电平。

448.基于上述示例,如图22~图26所示,扫描驱动电路1000还包括第三时钟信号线组。第三时钟信号线组包括十六个第三时钟信号线ckd。十六个第三时钟信号线ckd分别与第三对移位寄存器组cc3中各移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2、第四对移位寄存器组cc4中各移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接。

449.示例性的,该十六个第三时钟信号线ckd可以包括:分别与各第三对移位寄存器组cc3中的第一级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之一ckd_1和第三子时钟信号线之二ckd_2;分别与各第三对移位寄存器组cc3中的第二级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之三ckd_3和第三子时钟信号线之四ckd_4;分别与各第三对移位寄存器组cc3中的第三级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之五ckd_5和第三子时钟信号线之六ckd_6;分别与各第三对移位寄存器组cc3中的第四级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之七ckd_7和第三子时钟信号线之八ckd_8;分别与各第四对移位寄存器组cc3中的第一级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之九ckd_9和第三子时钟信号线之十ckd_10;分别与各第四对移位寄存器组cc3中的第二级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之十一ckd_11和第三子时钟信号线之十二ckd_12;分别与各第四对移位寄存器组cc3中的第三级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之十三ckd_13和第三子时钟信号线之十四ckd_14;分别与各第四对移位寄存器组cc3中的第四级移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子时钟信号线之十五ckd_15和第三子时钟信号线之十六ckd_16。

450.当然,上述第三子时钟信号线ckd的连接顺序可以调换,并不局限于上述连接方

式。

451.在一些实施例中,如图21和图26所示,扫描驱动电路1000还包括:第三虚设时钟信号线组。第三虚设时钟信号线组包括四个第三虚设时钟信号线ckd_d,四个第三虚设时钟信号线ckd_d分别与第一个移位寄存器组c0中的各虚设移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接。

452.示例性的,该四个第三虚设时钟信号线ckd_d可以包括:分别与第一个移位寄存器组c0中的第一级虚设移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子虚设时钟信号线之一ckd_d1和第三子虚设时钟信号线之二ckd_d2;分别与第一个移位寄存器组c0中的第二级虚设移位寄存器100的第五时钟信号端clkd1及第六时钟信号端clkd2电连接的第三子虚设时钟信号线之三ckd_d3和第三子虚设时钟信号线之四ckd_d2。

453.当然,上述第三子虚设时钟信号线ckd_d的连接顺序可以调换,并不局限于上述连接方式。

454.下面结合图26、图29和图30,对图21~图25所示的扫描驱动电路1000的驱动方法进行示意性说明。其中,一个扫描信号端与一行子像素p电连接。

455.扫描驱动电路1000的驱动过程包括交替设置的第一帧扫描周期ff1和第二帧扫描周期ff2。

456.需要说明的是,上述的第一帧图像对应此处的第一帧扫描周期ff1,上述的第二帧图像对应此处的第二帧扫描周期ff2。

457.在第一帧扫描周期ff1中,第三对移位寄存器组cc3和第四对移位寄存器组cc4在第一上拉结点q《n》和第二上拉结点q《n+1》接收第一插黑输入信号的控制下,交替输出显示黑画面的扫描驱动信号。显示黑画面的扫描驱动信号包括第三对移位寄存器组cc3中的各移位寄存器100同时输出的一组扫描驱动信号,以及第四对移位寄存器组cc4中的各移位寄存器100同时输出的一组扫描驱动信号。

458.在第二帧显示图像ff2中,第一对移位寄存器组cc1和第二对移位寄存器组cc2在第一上拉结点q《n》和第二上拉结点q《n+1》接收第二插黑输入信号的控制下,交替输出显示黑画面的扫描驱动信号;显示黑画面的扫描驱动信号包括第一对移位寄存器组cc1中的各移位寄存器100同时输出的一组扫描驱动信号,以及第二对移位寄存器组cc2中的各移位寄存器100同时输出的一组扫描驱动信号。

459.在第一帧扫描周期ff1中:

460.在第一阶段t1中,第二起始信号线stu2所传输的第二起始信号的电平及第一子控制信号线bck1所传输的第一控制信号的电平,均为高电平。

461.第一个第三对移位寄存器组cc3中,各移位寄存器100的第一插黑控制子电路211导通。其中,第一插黑控制子电路211中的第三晶体管m3,可以接收并传输第二起始信号至第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m《1/3/5/7》的电压为高电平。

462.在第二阶段t2中,第二复位信号端trst所传输的第二复位信号的电平为高电平。

463.此时,可以将第一插黑节点m的电压为高电平的各扫描单元的上拉节点,进行下拉复位。

464.在第三阶段t3中,第25行~28行各输出电路导通,并依次传输高电平的第一时钟信号至第25行~28行子像素p,使得第25行~28行子像素p依次进行显示操作。在第28行子像素p写入数据后,第二个第四对移位寄存器组cc4中的插黑电路导通,并对各第一插黑节点m《25/27/29/31》进行充电。

465.在此阶段,第二个第四对移位寄存器组cc4中的各上拉结点q《25/27/29/31》的电压也抬高为高电平。

466.同时,第二子控制信号线bck2所传输的第二控制信号的电平为高电平。

467.第一个第三对移位寄存器组cc3中,各移位寄存器100的第一插黑传输子电路213和第三插黑传输子电路214导通,其中,第一插黑传输子电路213的第五晶体管m5可以将高电平的第一插黑输入信号传输至第一上拉结点q《n》,第三插黑传输子电路214的第十二晶体管m12可以将高电平的第一插黑输入信号传输至第二上拉结点q《n+1》。从而,可以抬高第一个第三对移位寄存器组cc3中上拉结点q《1-8》的电压。

468.在第四阶段t4中,第三子控制信号线bck3所传输的第一控制信号的电平为高电平,cke_1~cke_8所传输的第一时钟信号的电平为高电平,ckd_1/3/5/7所传输的第三时钟信号的电平变为高电平。

469.第一个第三对移位寄存器组cc3中,各输出电路输出的扫描信号均为高电平。此时,数据信号的电平为低电平,使得相应子像素p的驱动晶体管t2关断,进而使得第1~8行子像素p显示黑画面,实现插黑。

470.在此阶段,第一个第三对移位寄存器组cc3中的第一移位信号端cr2《1/3/5/7》将高电平的第一移位信号输出。

471.第一个第四对移位寄存器组cc4中,各移位寄存器100的第一插黑控制子电路211在第一控制信号的控制下导通,接收并存储上述各第一移位信号端cr2《1/3/5/7》所输出的高电平的第三时钟信号,对各第一插黑节点m《9/11/13/15》的高电平保持到下一个插黑阶段。

472.在此过程中,上拉结点q《25/27/29/31》的电压为高电平,相应的输出电路的相应的第一移位信号端cr2《25/27/29/31》会输出第一移位信号,但是由于c《33-40》中第一插黑控制子电路211所接收的第一控制信号的电平为低电平,因此并不会影响显示行。

473.第五阶段t5中,第二复位信号端trst所传输的第二复位信号的电平为高电平。

474.由于第一插黑节点m《1/3/5/7》的电压为高电平,第一个第三对移位寄存器组cc3中,各第二复位电路14和各第四复位电路34在第二复位信号及第一插黑节点m《1/3/5/7》的电压的控制下导通,将第一电压信号传输至各上拉节点q《1-8》和下拉结点q《1-8》,对各上拉节点q《1-8》进行下拉复位。

475.由于第一插黑节点m《25/27/29/31》的电压为低电平,因此,上拉节点q《25/27/29/31》的电压保持为高电平。

476.在第六阶段t6中,第一子控制信号线bck1所传输的第一控制信号的电平为高电平。

477.第一个第三对移位寄存器组cc3中,各移位寄存器100的第一插黑控制子电路211导通,将低电平的第二起始信号传输至各第一插黑节点m进行充电,使得各第一插黑节点m《1/3/5/7》的电压为低电平。

478.在第七阶段t7和第八阶段t8中,第29~32行各输出电路导通,并依次传输高电平的时钟信号至第29~32行子像素p,使得第29~32行子像素p依次进行显示操作。

479.这样不断的进行循环,即可实现第一帧扫描周期ff1中显示和插黑的结合。当然本方案设置第25~32行子像素p进行显示的中间过程中,第1-8行子像素p进行插黑只是一种实施方案,也可以设置任意第三对移位寄存器组cc3和第四对移位寄存器组cc4所对应的子像素p进行显示和插黑方式。

480.在第二帧扫描周期ff2中:

481.在第一阶段t1中,第二起始信号线stu2所传输的第二起始信号的电平及第五子控制信号线bck5所传输的第五控制信号的电平,均为高电平。

482.第一个第一对移位寄存器组cc1中,各移位寄存器100的第二插黑控制子电路221导通。其中,第二插黑控制子电路221中的第七晶体管m7,可以接收并传输第二起始信号至第一插黑节点m,对第一插黑节点m进行充电,使得第一插黑节点m《d1/d2/1/3》的电压为高电平。

483.在第二阶段t2中,第二复位信号端trst所传输的第二复位信号的电平为高电平。

484.此时,可以将第一插黑节点m的电压为高电平的各扫描单元的上拉节点,进行下拉复位。

485.在第三阶段t3中,第21行~24行各输出电路导通,并依次传输高电平的第一时钟信号至第21行~24行子像素p,使得第21行~24行子像素p依次进行显示操作。在第24行子像素p写入数据后,第二个第二对移位寄存器组cc2中的插黑电路导通,并对各第一插黑节点m《21/23/25/27》进行充电。

486.在此阶段,第二个第二对移位寄存器组cc2中的各上拉结点q《21/23/25/27》的电压也抬高为高电平。

487.同时,第六子控制信号线bck6所传输的第六控制信号的电平为高电平。

488.第一个第一对移位寄存器组cc1中,各移位寄存器100的第二插黑传输子电路223和第四插黑传输子电路224导通,其中,第二插黑传输子电路223的第九晶体管m9可以将高电平的第二插黑输入信号传输至第一上拉结点q《n》,第四插黑传输子电路224的第十三晶体管m13可以将高电平的第二插黑输入信号传输至第二上拉结点q《n+1》。从而,可以抬高第一个第一对移位寄存器组cc1中上拉结点q《1-8》的电压。

489.在第四阶段t4中,第七子控制信号线bck7所传输的第五控制信号的电平为高电平,cke_d1~cke_d4及cke_1cke_4所传输的第一时钟信号的电平为高电平(在第一对移位寄存器组cc1不包含第一组移位寄存器组c0时,cke_1cke_4及cke_13cke_16所传输的第一时钟信号的电平为高电平),ckd_d1/d3/1/3所传输的第三时钟信号的电平变为高电平。

490.第一个第一对移位寄存器组cc1中,各输出电路输出的扫描信号均为高电平。此时,数据信号的电平为低电平,使得相应子像素p的驱动晶体管t2关断,进而使得第1~4行子像素p显示黑画面,实现插黑。

491.在此阶段,第一个第一对移位寄存器组cc1中的第一移位信号端cr2《d1/d3/1/3》将高电平的第一移位信号输出。

492.第一个第二对移位寄存器组cc2中,各移位寄存器100的第二插黑控制子电路221在第一控制信号的控制下导通,接收并存储上述各第一移位信号端cr2《d1/d3/1/3》所输出

的高电平的第三时钟信号,对各第一插黑节点m《5/7/9/11》的高电平保持到下一个插黑阶段。

493.在此过程中,上拉结点q《21/23/25/27》的电压为高电平,相应的输出电路的相应的第一移位信号端cr2q《21/23/25/27》会输出第一移位信号,但是由于c《29-36》中第二插黑控制子电路221所接收的第五控制信号的电平为低电平,因此并不会影响显示行。

494.第五阶段t5中,第二复位信号端trst所传输的第二复位信号的电平为高电平。

495.由于第一插黑节点m《d1/d3/1/3》的电压为高电平,第一个第一对移位寄存器组cc1中,各第二复位电路14和各第四复位电路34在第二复位信号及第一插黑节点m《d1/d3/1/3》的电压的控制下导通,将第一电压信号传输至各上拉节点q《d1-4》,对各上拉节点q《d1-4》进行下拉复位。

496.由于第一插黑节点m《21/23/25/27》的电压为低电平,因此,上拉节点q《21/23/25/27》的电压保持为高电平。

497.在第六阶段t6中,第五子控制信号线bck5所传输的第五控制信号的电平为高电平。

498.第一个第一对移位寄存器组cc1中,各移位寄存器100的第二插黑控制子电路221导通,将低电平的第二起始信号传输至各第一插黑节点m进行充电,使得各第一插黑节点m《d1/d3/1/3》的电压为低电平。

499.在第七阶段t7和第八阶段t8中,第25~28行各输出电路导通,并依次传输高电平的时钟信号至第25~28行子像素p,使得第25~28行子像素p依次进行显示操作。

500.这样不断的进行循环,即可实现第二帧扫描周期ff2中显示和插黑的结合。当然本方案设置第21~28行子像素p进行显示的中间过程中,dum1-dum4及第1-4行子像素p进行插黑只是一种实施方案,也可以设置任意第一对移位寄存器组cc1和第二对移位寄存器组cc2所对应的子像素p进行显示和插黑方式。

501.另外,发明人发现,如图31所示,移位寄存器100的电路和时钟信号线之间的连接线会因为布线空间的问题导致电阻

△

r不同,及产生寄生电容,进而会在显示屏幕上出现横纹,影响显示效果。

502.在一些示例中,如图31所示,以第一时钟信号线组的十六个第一时钟信号线cke,以及与该第一时钟信号线组相连接的相邻的第三对移位寄存器组cc3和第四对移位寄存器组cc4为一个连接周期,在一个连接周期内,第一时钟信号线组的十六个第一时钟信号线cke与其连接的各级移位寄存器100(或者goa unit)之间的连接线(第一组连接线al1-al16)逐渐缩短。由于连接线的电阻和其长度有关,因此在布线空间上存在的差异,导致十六个第一时钟信号线cke存在电阻

△

r和寄生电容(第二寄生电容ca2)的不同。

503.示例性的,如图31所示,第一子时钟信号线之一cke_1与第一子时钟信号线之六cke_6之间相差了5*

△

r,这样第一子时钟信号线之一cke_1与第一子时钟信号线之六cke_6之间对应的栅线行交界处会产生一条因亮度差异带来的分界线。

504.在一些实施例中,传统的3t1c电路图如图32所示,g1和g2打开后在data端和sense端分别写入vdata和vref电压,接着g1和g2关断,g和s电位差为v

gs

,t2有电流通过,oled发光。

505.在此过程中,在g1关断(g1电位变化为

△

v1)过程有一个第一寄生电容ca1和cst之

间的耦合过程,使得g点电位有一个变化量

△

vp=

△

v1*cst/(cst+ca)。但是,

△

vp同时还受到g1下降沿的影响,g1的下降沿越大

△

vp越小。在时钟信号线数目较多时,例如上述的十六个第一时钟信号线cke,由于十六个第一时钟信号线cke与移位寄存器100的电路的连接线导致的电阻

△

r和第二寄生电容ca2的不同,使得g1的下降沿发生差异,进而影响

△

vp,在显示装置的显示屏端表现为与时钟信号线相关的横纹。

506.为了解决上述问题,在一些实施例中,如图33所示,除第三对移位寄存器组cc3中第一个移位寄存器100与第一时钟信号线cke连接的第一连接线al1外,第三对移位寄存器组cc3中的各移位寄存器100与对应的第一时钟信号线cke连接的连接线上、以及第四对移位寄存器组cc4中的各移位寄存器100与对应的第一时钟信号线cke连接的连接线上分别连接有补偿电阻(第一组补偿电阻ar),连接线al2~al16上的补偿电阻分别为ar2~ar16。

507.通过第一组补偿电阻ar的设置,避免下降沿不一致的影响,消除移位寄存器100的电路和第一时钟信号线cke之间的连接线之间由于布线空间的问题而导致电阻

△

r不同而在显示屏幕上出现横纹的问题。

508.在一些示例中,如图33所示,第三对移位寄存器组cc3中的各移位寄存器100与对应的第一时钟信号线cke连接的连接线上、以及第四对移位寄存器组cc4中的各移位寄存器100与对应的第一时钟信号线cke连接的连接线上的补偿电阻的电阻值依次增大。

509.示例性的,ar2为

△

r,ar3为2

△

r,ar4为3

△

r,ar5为4

△

r,ar6为5

△

r,ar7为6

△

r,ar8为7

△

r,ar9为8

△

r,ar10为9

△

r,ar11为10

△

r,ar12为11

△

r,ar13为12

△

r,ar14为13

△

r,ar15为14

△

r,ar16为15

△

r。

510.在一些实施例中,如图34所示,在扫描驱动电路1000还包括第二时钟信号线组,第二时钟信号线组包括十六个第二时钟信号线ckf,以第二时钟信号线组的十六个第二时钟信号线ckf,以及与该第二时钟信号线组相连接的相邻的第三对移位寄存器组cc3和第四对移位寄存器组cc4相连接为一个连接周期,在一个连接周期内,第二时钟信号线组的十六个第二时钟信号线ckf与其连接的各移位寄存器100之间的连接线(第二组连接线bl1~bl16)逐渐缩短。除第三对移位寄存器组中第一级移位寄存器100与第二时钟信号线ckf连接的连接线外,第三对移位寄存器组cc3中的各移位寄存器100与对应的第二时钟信号线ckf连接的连接线上、第四对移位寄存器组cc4中的各移位寄存器100与对应的第二时钟信号线连接的连接线上分别连接有补偿电阻(第二组补偿电阻br),连接线bl2~bl16上的补偿电阻分别为br2~br16。

511.通过在移位寄存器100的电路和不同种类的时钟信号线之间的连接线之间设置补偿电阻,消除因为布线空间的问题引起的电阻

△

r不同而导致的显示屏幕上出现横纹的问题。

512.在一些示例中,如图34所示,第三对移位寄存器组cc3中的各移位寄存器100与对应的第二时钟信号线ckf连接的连接线上、第四对移位寄存器组cc4中的各移位寄存器100与对应的第二时钟信号线连接的连接线上的补偿电阻的电阻值依次增大。

513.示例性的,br2为

△

r,br3为2

△

r,br4为3

△

r,br5为4

△

r,br6为5

△

r,br7为6

△

r,br8为7

△

r,br9为8

△

r,br10为9

△

r,br11为10

△

r,br12为11

△

r,br13为12

△

r,br14为13

△

r,br15为14

△

r,br16为15

△

r。

514.通过对连接线长度的补偿,实现对不同大小的电阻的补偿,从而实现对布线空间

的补偿问题。

515.在一些示例中,如图35所示,移位寄存器100的第一时钟信号端clke1与第二晶体管m2的第一极的连接线上设置补偿电阻,示例性的补偿电阻ar3;在一些示例中,如图36所示,移位寄存器100的第二时钟信号端clke2与第十一晶体管m11的第一极的连接线上设置补偿电阻,示例性的补偿电阻ar4。

516.在一些示例中,如图35所示,移位寄存器100的第三时钟信号端clkf1与第十四晶体管m14的第一极的连接线上设置补偿电阻,示例性的补偿电阻br3;在一些示例中,如图36所示,移位寄存器100的第四时钟信号端clke2与第十五晶体管m15的第一极的连接线上设置补偿电阻,示例性的补偿电阻br4。

517.在一些实施例中,如图37所示,以第一时钟信号线组的十六个第一时钟信号线cke,以及与该第一时钟信号线组相连接的相邻的第三对移位寄存器组cc3和第四对移位寄存器组cc4相连接为一个连接周期,在一个连接周期内,第一时钟信号线组的十六个第一时钟信号线cke与其连接的各级移位寄存器100之间的连接线(第一组连接线al1-al16)逐渐缩短。

518.在一些示例中,如图37所示,除第三对移位寄存器组cc3中第一级移位寄存器100与第一扫描信号线gl1连接的连接线(连接线cl1)外,第三对移位寄存器组cc3中的各移位寄存器100与对应的第一扫描信号线gl1连接的连接线上、以及第四对移位寄存器组中cc4的各移位寄存器100与对应的第一扫描信号线gl1(栅线)连接的连接线(第三组连接线cl1-cl16中的连接线cl2-cl16)上分别连接有补偿电阻r(第三组补偿电阻cr),连接线cl2~cl16上的补偿电阻分别为cr2~cr16。

519.通过补偿电阻设置位置的调整,依然可以实现,消除移位寄存器100的电路和时钟信号线之间的连接线之间由于布线空间的问题而导致电阻

△

r不同而在显示屏幕上出现横纹的问题。

520.在一些示例中,如图37所示,第三对移位寄存器组cc3中的各移位寄存器100与第一扫描信号线gl1连接的连接线上、以及第四对移位寄存器组cc4中的各移位寄存器100与第一扫描信号线gl1连接的连接线上的补偿电阻的电阻值依次增大。

521.示例性的,cr2为

△

r,cr3为2

△

r,cr4为3

△

r,cr5为4

△

r,cr6为5

△

r,cr7为6

△

r,cr8为7

△

r,cr9为8

△

r,cr10为9

△

r,cr11为10

△

r,cr12为11

△

r,cr13为12

△

r,cr14为13

△

r,cr15为14

△

r,cr16为15

△

r。

522.在一些实施例中,如图38所示,扫描驱动电路1000还包括第二时钟信号线组,第二时钟信号线组包括十六个第二时钟信号线ckf的情况下,以第二时钟信号线组的十六个第二时钟信号线ckf,以及与该第二时钟信号线组相连接的相邻的第三对移位寄存器组cc3和第四对移位寄存器组cc4相连接为一个连接周期,在一个连接周期内,第二时钟信号线组的十六个第二时钟信号线ckf与其连接的各级移位寄存器100之间的连接线(第二组连接线bl1~bl16)逐渐缩短。除第三对移位寄存器组中第一级移位寄存器100与第二扫描信号线gl2连接的连接线(连接线dl1)外,第三对移位寄存器组cc3中的各移位寄存器与对应的第二扫描信号线连接gl2的连接线上、以及第四对移位寄存器组cc4中的各移位寄存器100与对应的第二扫描信号线gl2连接的连接线(第四组连接线dl1-dl16中的连接线dl2-dl16)上分别连接有补偿电阻(第四组补偿电阻dr),连接线dl2~dl16上的补偿电阻分别为dr2~

dr16。

523.在一些示例中,如图38所示,第三对移位寄存器组cc3中的各移位寄存器100与第二扫描信号线gl2连接的连接线上、以及第四对移位寄存器组cc4中的各移位寄存器100与第二扫描信号线gl2连接的连接线上的补偿电阻的电阻值依次增大。

524.示例性的,dr2为

△

r,dr3为2

△

r,dr4为3

△

r,dr5为4

△

r,dr6为5

△

r,dr7为6

△

r,dr8为7

△

r,dr9为8

△

r,dr10为9

△

r,dr11为10

△

r,dr12为11

△

r,dr13为12

△

r,dr14为13

△

r,dr15为14

△

r,dr16为15

△

r。

525.在一些示例中,如图39所示,移位寄存器100第二晶体管m2的第二极与第一扫描信号端oput1《n》的连接线上设置补偿电阻,示例性的补偿电阻cr3;在一些示例中,如图40所示,移位寄存器100第十一晶体管m11的第二极与第二扫描信号端oput1《n+1》的连接线上设置补偿电阻,示例性的补偿电阻cr4。

526.在一些示例中,如图39所示,移位寄存器100第十四晶体管m14的第二极与第一感测信号端oput2《n》的连接线上设置补偿电阻,示例性的补偿电阻dr3;在一些示例中,如图40所示,移位寄存器100第十五晶体管m15的第二极与第二感测信号端oput2《n+1》的连接线上设置补偿电阻,示例性的补偿电阻dr4。

527.在一些实施例中,如图41所示,扫描驱动电路1000还包括多个第一补偿电容c11,每个第一补偿电容c11的一端,与一级移位寄存器100连接第一时钟信号线cke的连接线(第一组连接线al1-al16),电连接,第一补偿电容c11的另一端接地,多个第一补偿电容c11的电容值大致相等。

528.通过第一补偿电容c11的设置,消除移位寄存器100的电路和第一时钟信号线cke之间的连接线之间所产生的寄生电容的存在而导致的在显示屏幕上出现横纹的问题。

529.在一些实施例中,如图42所示,在扫描驱动电路1000还包括第二时钟信号线组,第二时钟信号线组包括十六个第二时钟信号线ckf的情况下,扫描驱动电路1000还包括多个第二补偿电容c22,每个第二补偿电容c22的一端,与一级移位寄存器100连接第二时钟信号线ckf的连接线,电连接,第二补偿电容的c22另一端接地,多个补偿电容的电容值大致相等。

530.通过第二补偿电容c11的设置,消除移位寄存器100的电路和第二时钟信号线ckf连接线之间所产生的寄生电容的存在而导致的在显示屏幕上出现横纹的问题。

531.在一些实施例中,如图43所示,扫描驱动电路1000还包括多个第三补偿电容c33,每个第三补偿电容c33的一端,与一级移位寄存器100连接第一扫描信号线oput1《n》的连接线,电连接,第三补偿电容c33的另一端接地,多个第三补偿电容c33的电容值大致相等。

532.通过补偿电容设置位置的调整,依然可以实现,消除移位寄存器100的电路和第二时钟信号线ckf连接线之间所产生的寄生电容的存在而导致的在显示屏幕上出现横纹的问题。

533.在一些实施例中,如图44所示,扫描驱动电路1000还包括第二时钟信号线组,第二时钟信号线组包括十六个第二时钟信号线ckf。扫描驱动电路1000还包括多个第四补偿电容c44,每个第四补偿电容c44的一端,与一级移位寄存器100连接第二扫描信号线gl2的连接线,电连接,第四补偿电容c44的另一端接地,多个第四补偿电容的电容值大致相等。

534.设置第四补偿电容c44的有益效果同上,此处不再赘述。