显示驱动器集成电路、图像处理器及其操作方法与流程

1.本发明涉及一种数据传输,且特别涉及一种显示驱动器集成电路、图像处理器及其操作方法。

背景技术:

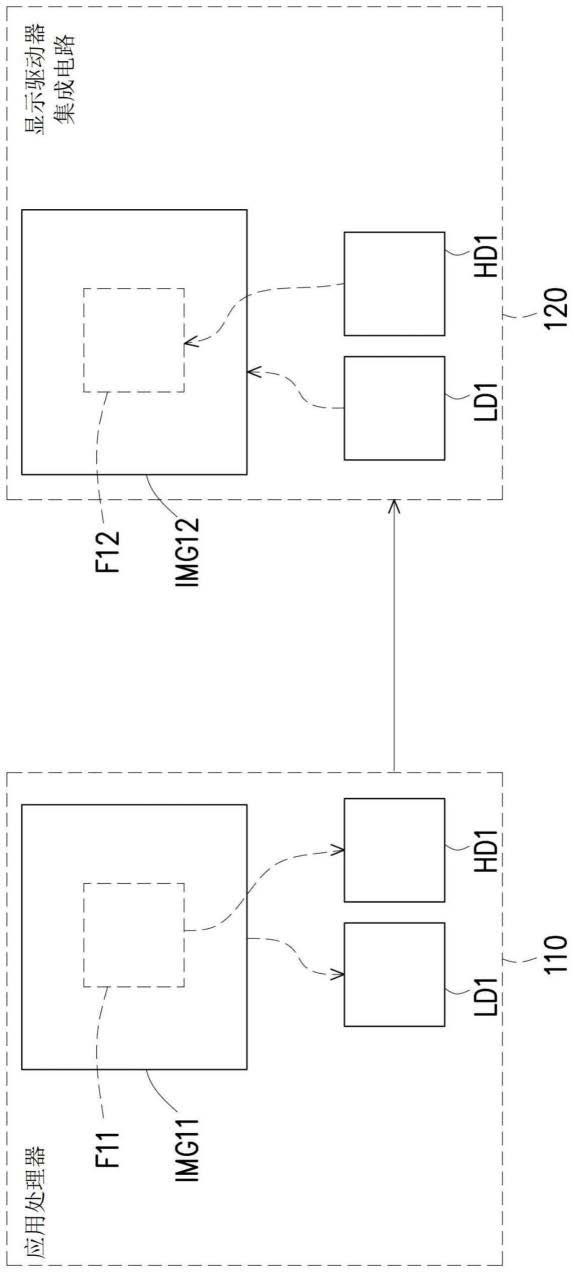

2.注视点渲染(foveated rendering)是一种新型图像计算技术,用来减少没有被用户注视的图像细节的数据量。人眼在看东西时,并不会整个视野范围都一样清晰,而是中心点清晰,越往两旁越模糊。因此,在屏幕上显示图像时,仅有人眼注视的注视点区域(foveated area)需要有最高图像分辨率而注视点区域以外的其他区域的分辨率可以被降低,注视点区域通常是屏幕的中心区域或依眼动追踪(eye-tracking)信号而决定的动态改变区域。因此,可凭借降低注视点周围图像的分辨率来大幅降低屏幕和提供图像数据的主装置之间的传输数据量与数据运算量。注视点渲染技术主要应用在整合了眼动追踪技术的增强现实(augmented reality,ar)装置或虚拟现实(virtual reality,vr)装置中。

3.图1是使用注视点渲染技术的显示系统的示意图。如图1的显示系统包括应用处理器(application processor,ap)110和用来驱动显示面板的显示驱动器集成电路120。应用处理器(application processor,ap)110可以在原始图像(original image)img11中定义一个注视区域(foveated area)f11。应用处理器110可以从所述注视区域f11裁剪出一个经裁剪图像(cropped image)hd1。应用处理器110还可以缩小(scale down)所述原始图像img11,亦即降低原始图像img11的分辨率,以产生一个经缩小图像ld1。应用处理器110可以将经缩小图像ld1与经裁剪图像hd1传送给显示驱动器集成电路120。凭借降低原始图像帧img11的分辨率,传输数据量可以被大幅降低。

4.在接获经缩小图像ld1与经裁剪图像hd1后,显示驱动器集成电路120可以放大(scale up)经缩小图像ld1,亦即增加所述经缩小图像ld1的分辨率,以产生一个经放大图像img12。显示驱动器集成电路120可以将经裁剪图像hd1合并(merge)或混合(blend)至经放大图像img12的一个注视点区域f12,而产生待显示的输出图像。

5.应用处理器110发出图像写入命令给显示驱动器集成电路120,以将经裁剪图像hd1与经缩小图像ld1传送给显示驱动器集成电路120。一般而言,应用处理器110是将一个图像完全传送给显示驱动器集成电路120后,才开始传送另一个图像。举例来说,应用处理器110先将经裁剪图像hd1完全传送给显示驱动器集成电路120后,才开始传送经缩小图像ld1给显示驱动器集成电路120。每一个图像包括多条线(line),而每一条线包括多个像素(pixel)数据。在接获经缩小图像ld1的至少一条线后,显示驱动器集成电路120可以放大经缩小图像ld1的所述至少一线,以产生经放大图像img12的多个对应线。

6.从应用处理器110发出图像写入命令算起,显示驱动器集成电路120需要经过一段时间之后才能开始输出待显示的输出图像给显示面板(未绘示),该段时间即延迟时间(latency)。所述延迟时间至少包括:图像写入命令的传输时间、完整经裁剪图像hd1的传输时间、经缩小图像ld1的第一条线的传输时间以及处理经缩小图像ld1的第一条线的放大计

算时间。随着经裁剪图像hd1的尺寸越大,所述延迟时间越久。在经裁剪图像hd1与经缩小图像ld1的尺寸不改变的情况下,若要缩短所述延迟时间,应用处理器110与显示驱动器集成电路120之间的传输接口的传输速度需要被提升。

7.注视点渲染技术虽然可以减少传输数据量,但是所述延迟时间可能不符合ar产品或vr产品的应用需求。如果要减少所述延迟时间来符合ar(或vr)产品的应用需求,则应用处理器110与显示驱动器集成电路120之间的传输接口的传输速度(或带宽)需要被大幅提升。事实上,毫无限制地提升传输接口的传输速度(或带宽)是不切实际的。

8.须注意的是,“背景技术”段落的内容是用来帮助了解本发明。在“背景技术”段落所公开的部分内容(或全部内容)可能不是所属技术领域的技术人员所知道的已知技术。在“背景技术”段落所公开的内容,不代表该内容在本发明申请前已被所属技术领域的技术人员所知悉。

技术实现要素:

9.本发明提供一种显示驱动器集成电路、图像处理器及其操作方法,以有效缩减延迟(latency)时间。

10.在根据本发明的实施例中,上述的显示驱动器集成电路包括接收电路、存储器单元以及注视点渲染(foveated rendering)电路。接收电路被配置为从图像提供电路接收第一图像与第二图像。存储器单元用以存储第一图像与第二图像。注视点渲染电路耦接至存储器单元。注视点渲染电路被配置为基于第一图像与第二图像进行图像处理而产生待显示的输出图像。其中,第一图像相对于输出图像的注视区域(foveated area)。接收电路在第一图像与第二图像中的一个被完全接收之前,接收第一图像与第二图像中的另一个的至少一部分。

11.在根据本发明的实施例中,上述显示驱动器集成电路的操作方法包括:由显示驱动器集成电路的接收电路从图像提供电路接收第一图像与第二图像,其中接收电路在第一图像与第二图像中的一个被完全接收之前先接收第一图像与第二图像中的另一个的至少一部分;存储第一图像与该第二图像到存储器单元:以及基于第一图像与第二图像进行图像处理而产生待显示的输出图像。其中,第一图像相对于输出图像的注视区域。

12.在根据本发明的实施例中,上述的图像处理器包括数字信号处理电路、存储器单元以及传送电路。数字信号处理电路被配置为基于原始图像产生第一图像与第二图像,其中第一图像是原始图像的注视区域所相对的经裁剪图像(cropped image),以及第二图像是通过缩小(scale down)原始图像的经缩小图像。存储器单元耦接至数字信号处理电路。存储器单元用以存储第一图像与第二图像。传送电路耦接至存储器单元。传送电路被配置为将第一图像与第二图像传送至显示驱动器集成电路。其中,传送电路在第一图像与第二图像中的一个被完全传送之前,先传送第一图像与第二图像中的另一个的至少一部分。

13.在根据本发明的实施例中,上述图像处理器的操作方法包括:由位信号处理电路基于原始图像产生第一图像与第二图像,其中第一图像是原始图像的注视区域所相对的经裁剪图像,以及第二图像是通过缩小原始图像的经缩小图像;由存储器单元存储第一图像与第二图像;以及由图像处理器的传送电路将第一图像与第二图像传送至显示驱动器集成电路。其中,传送电路在第一图像与第二图像中的一个被完全传送之前,先传送第一图像与

第二图像中的另一个的至少一部分。

14.基于上述,本发明诸实施例所述图像提供电路(例如图像处理器)可以基于原始图像产生经裁剪图像(第一图像)与经缩小图像(第二图像)。在经裁剪图像与经缩小图像中的一个被完全传送给显示驱动器集成电路之前,图像处理器可以先传送经裁剪图像与经缩小图像中的另一个的至少一部分给显示驱动器集成电路。因此,所述延迟时间可以被有效缩减。

附图说明

15.图1是一种注视点渲染技术的示意图。

16.图2是依照本发明的一实施例的一种显示装置的电路方块(circuit block)示意图。

17.图3是依照本发明的一实施例的一种图像处理器的操作方法的流程示意图。

18.图4是依照本发明的一实施例所绘示,传送电路传送第一图像(经裁剪图像)与第二图像(经缩小图像)的时序示意图。

19.图5是依照本发明的另一实施例所绘示,传送电路传送第一图像与第二图像的时序示意图。

20.图6是依照本发明的一实施例的一种显示驱动器集成电路的操作方法的流程示意图。

21.图7是依照本发明的一实施例说明图2所示存储器单元与注视点渲染电路的电路方块示意图。

22.图8是依照本发明的另一实施例说明图2所示注视点渲染电路的电路方块示意图。

23.附图标记说明

24.110:应用处理器

25.120:显示驱动器集成电路

26.210:图像处理器

27.211:数字信号处理电路

28.212、222:存储器单元

29.213:传送电路

30.220:显示驱动器集成电路

31.221:接收电路

32.222a、222b:存储器空间

33.223:注视点渲染电路

34.bl7、bl8:混合电路

35.dec71、dec72、dec81、dec82:译码器电路

36.f11、f12:注视区域

37.hd1、hd2、hd2’:经裁剪图像

38.img11、img21:原始图像

39.img12、img22:经放大图像

40.imgout:输出图像

processing unit,cpu)、控制器、微控制器或微处理器可以从所述记录介质中读取并执行所述编程码,从而实现数字信号处理电路211以及(或是)传送电路213的相关功能。

51.数字信号处理电路211基于原始图像(original image)img21产生第一图像与第二图像,其中第一图像是原始图像img21的注视区域(foveated area)所相对的经裁剪图像(cropped image)hd2,以及第二图像是通过缩小(scale down)原始图像img21的经缩小图像ld2。数字信号处理电路211可以在原始图像img21中定义一个注视区域。数字信号处理电路211可以通过将原始图像img21的注视区域剪下以产生经裁剪图像hd。数字信号处理电路211还可以缩小原始图像img21以产生经缩小图像ld2。传送电路213可传送经缩小图像ld2和经裁剪图像hd2至显示驱动集成电路220。在显示驱动集成电路220的接收电路221接收并存储经缩小图像ld2和经裁剪图像hd2之后,注视点渲染电路223放大经缩小图像ld2以产生经放大图像。显示驱动集成电路220可合并或混合经裁剪图像hd2至经放大图像的注视点区域以产生待显示的输出图像imgout。

52.图3是依照本发明的一实施例的一种图像处理器的操作方法的流程示意图。请参照图2与图3。在步骤s310中,数字信号处理电路211可以基于原始图像img21产生第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)。举例来说,数字信号处理电路211可以在原始图像img21中定义一个注视区域。在原始图像img21中注视区域的位置与大小可以依照实际设计来定义。数字信号处理电路211可以从原始图像img21的注视点区域裁剪出一个经裁剪图像hd2。

53.此外,数字信号处理电路211在步骤s310中还可以缩小原始图像img21的数据量,亦即降低原始图像img21的分辨率,以产生一个经缩小图像ld2(第二图像)。经缩小图像ld2的分辨率可以依照实际设计来决定。举例来说(但不限于此),经缩小图像ld2(第二图像)的分辨率(又称为第二分辨率)可以相同于经裁剪图像hd2(第一图像)的分辨率(又称为第一分辨率)。换句话说,经缩小图像ld2的图像尺寸与经缩小图像ld2的图像尺寸相同。

54.所示存储器单元212耦接至数字信号处理电路211,以存储第一图像与第二图像(步骤s320)。传送电路213耦接至显示驱动器集成电路220的接收电路221。依照实际实施,传送电路213与接收电路221之间的连接可以包括移动产业处理器接口(mobile industry processor interface,mipi)、显示端口(displayport,dp)接口、嵌入式dp(embedded dp,edp)接口或是其他传输接口。在步骤s330中,传送电路213可以将第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)传送至显示驱动器集成电路220。传输数据量可通过传送第二图像而大幅减少,并且显示的图像细节可通过传送第一图像至显示驱动器集成电路220而尽可能地维持。

55.在图2所示实施例中,传送电路213在第一图像与第二图像中的一个被完全传送之前,先传送第一图像与第二图像中的另一个的至少一部分。举例来说,传送电路213可以交替传送通过分割第一图像(经裁剪图像hd2)而产生的第一图像的多个部分,又称为多个第一局部图像,和通过分割第二图像(经缩小图像ld2)而产生的第二图像的多个部分,又称为多个第二局部图像,其中第一图像的这些部分的数量和第二图像的这些部分的数量不少于两个。传送电路213耦接至存储器单元212,并且分时交替地从存储器单元212读取经裁剪图像hd2与经缩小图像ld2。举例来说,经裁剪图像hd2(第一图像)的多个部分的每一个包括经裁剪图像hd2的至少一条线,并且经缩小图像ld2(第二图像)的多个部分的每一个包括经缩

小图像ld2的至少一条线。

56.换句话说,传送电路213分别以多个第一传送时间单位传送经裁剪图像hd2(第一图像)的多个第一局部图像,以及分别以多个第二传送时间单位传送经缩小图像ld2(第二图像)的多个第二局部图像。其中,这些第一传送时间单位与这些第二传送时间单位交替排列。这些第一传送时间单位的每一个的长度足以传送经裁剪图像hd2(第一图像)的至少一条线,以及这些第二传送时间单位的每一个的长度足以传送经缩小图像ld2(第二图像)的至少一条线。因此,读取经裁剪图像hd2与经缩小图像ld2可以被分时传送给显示驱动器集成电路220。

57.图4是依照本发明的一实施例所绘示,传送电路213传送第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)的时序示意图。请参照图2与图4。数字信号处理电路211可以将经裁剪图像hd2与经缩小图像ld2存储到存储器单元212。存储器单元212的第一存储器空间专用于存储通过分割经裁剪图像hd2所产生的多个第一局部图像。存储器单元212的第二存储器空间专用于存储通过分割经缩小图像ld2所产生的多个第二局部图像。其中,这些第一局部图像的每一个包括经裁剪图像hd2的至少一条线,并且这些第二局部图像的每一个包括经缩小图像ld2的至少一条线。

58.传送电路213可以分时交替从存储器单元212读取经裁剪图像hd2的这些第一局部图像与经缩小图像ld2的这些第二局部图像。图4所示t4_1、t4_2、t4_3、t4_4、

…

、t4_n-1与t4_n表示传送时间单位。在传送时间单位t4_1中,传送电路213可以将经裁剪图像hd2的第一部分(例如第一条线)传送给显示驱动器集成电路220的接收电路221。在传送时间单位t4_1后的传送时间单位t4_2中,传送电路213可以将经缩小图像ld2的第一部分(例如第一条线)传送给接收电路221。在传送时间单位t4_2后的传送时间单位t4_3中,传送电路213可以将经裁剪图像hd2的第二部分(例如第二条线)传送给接收电路221。在传送时间单位t4_3后的传送时间单位t4_4中,传送电路213可以将经缩小图像ld2的第二部分(例如第二条线)传送给接收电路221。以此类推,传送电路213可以在传送时间单位t4_n-1中将经裁剪图像hd2的末部分(例如末条线)传送给接收电路221,以及传送电路213可以在传送时间单位t4_n中将经缩小图像ld2的末部分(例如末条线)传送给接收电路221。

59.因此,读取经裁剪图像hd2与经缩小图像ld2可以被分时传送给显示驱动器集成电路220。显示驱动器集成电路220在传送时间单位t4_2后便可实时地放大(scale up)经缩小图像ld2的第一条以产生经放大图像的多条对应线,进而开始输出待显示的输出图像imgout给显示面板(未绘示)。因此,在经裁剪图像hd2与经缩小图像ld2中的一个被完全传送给显示驱动器集成电路220之前,图像处理器210可以先传送经裁剪图像hd2与经缩小图像ld2中的另一个的至少一部分给显示驱动器集成电路220。基此,所述延迟时间可以被有效缩减。

60.图5是依照本发明的另一实施例所绘示,传送电路213传送第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)的时序示意图。请参照图2与图5。数字信号处理电路211可以将经裁剪图像hd2与经缩小图像ld2存储到存储器单元212。存储器单元212的多个连续存储器空间用于交替存储通过分割经裁剪图像hd2所产生的多个第一局部图像以及通过分割经缩小图像ld2所产生的多个第二局部图像,如图5所示。其中,这些第一局部图像的每一个包括经裁剪图像hd2的至少一条线,并且这些第二局部图像的每一个包括经缩小图像ld2

的至少一条线。

61.传送电路213可以分时交替从存储器单元212读取经裁剪图像hd2的这些第一局部图像与经缩小图像ld2的这些第二局部图像。图5所示t5_1、t5_2、

…

、t5_n表示传送时间单位。在传送时间单位t5_1中,传送电路213可以先传送经裁剪图像hd2的第一部分(例如第一条线)接着再传送经缩小图像ld2的第一部分(例如第一条线)给显示驱动器集成电路220的接收电路221。在传送时间单位t5_1后的传送时间单位t5_2中,传送电路213可以先传送经裁剪图像hd2的第二部分(例如第二条线)接着再传送经缩小图像ld2的第二部分(例如第二条线)给接收电路221。以此类推,传送电路213可以在传送时间单位t5_n中先传送经裁剪图像hd2的末部分(例如末条线)接着再传送经缩小图像ld2的末部分(例如末条线)传送给接收电路221。

62.因此,读取经裁剪图像hd2与经缩小图像ld2可以被分时传送给显示驱动器集成电路220。显示驱动器集成电路220在传送时间单位t5_1后便可实时地放大经缩小图像ld2的第一条线以产生经放大图像的多条对应线,进而开始输出待显示的输出图像imgout给显示面板(未绘示)。因此,在经裁剪图像hd2与经缩小图像ld2中的一个被完全传送给显示驱动器集成电路220之前,图像处理器210可以先传送经裁剪图像hd2与经缩小图像ld2中的另一个的至少一部分给显示驱动器集成电路220。基此,所述延迟时间可以被有效缩减。

63.在图2所示实施例中,显示驱动器集成电路220包括接收电路221、存储器单元222以及注视点渲染电路223。依照不同的设计需求,接收电路221以及(或是)注视点渲染电路223的实现方式可以是硬件(hardware)、固件(firmware)、软件(software,即程序)或是前述三者中的多个的组合形式。

64.以硬件形式而言,接收电路221以及(或是)注视点渲染电路223可以实现于集成电路上的逻辑电路。接收电路221以及(或是)注视点渲染电路223的相关功能可以利用硬件描述语言(例如verilog hdl或vhdl)或其他合适的编程语言来实现为硬件。举例来说,接收电路221以及(或是)注视点渲染电路223的相关功能可以被实现于一或多个控制器、微控制器、微处理器、特殊应用集成电路(asic)、数字信号处理器(dsp)、现场可编程逻辑门阵列(fpga)和/或其他处理单元中的各种逻辑区块、模块和电路。

65.以软件形式和/或固件形式而言,接收电路221以及(或是)注视点渲染电路223的相关功能可以被实现为编程码。例如,利用一般的编程语言(例如c、c++或汇编语言)或其他合适的编程语言来实现接收电路221以及(或是)注视点渲染电路223。所述编程码可以被记录/存放在“非临时的可读取介质”。举例来说,盘(disk)、卡(card)、半导体内存、可编程设计的逻辑电路等可以被使用来实现所述非临时的可读取介质。中央处理器(cpu)、控制器、微控制器或微处理器可以从所述记录介质中读取并执行所述编程码,从而实现接收电路221以及(或是)注视点渲染电路223的相关功能。

66.接收电路221可以从图像提供电路(例如图像处理器210)接收第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)。其中,接收电路221在第一图像与第二图像中的一个被完全接收之前,先接收第一图像与第二图像中的另一个的至少一部分。接收电路221从图像处理器210接收经裁剪图像hd2与经缩小图像ld2的时序是配合图像处理器210的传送时序,而图像处理器210的传送时序可以以参照图4或图5的相关说明。

67.图6是依照本发明的一实施例的一种显示驱动器集成电路的操作方法的流程示意

图。请参照图2与图6。在步骤s610中,接收电路221可以从图像提供电路(例如图像处理器210)接收第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2),其中接收电路221在经裁剪图像hd2与经缩小图像ld2中的一个被完全接收之前,先接收经裁剪图像hd2与经缩小图像ld2中的另一个的至少一部分。在一实施例中,接收电路221可以交替接收经裁剪图像hd2的多个部分和经缩小图像ld2的多个部分,其中经裁剪图像hd2的所述多个部分的数量和经缩小图像ld2的所述多个部分的数量不少于两个。举例来说,经裁剪图像hd2的这些部分的每一个包括经裁剪图像hd2的至少一条线,并且经缩小图像ld2的这些部分的每一个包括经缩小图像ld2的至少一条线。

68.接收电路221分别在多个第一接收时间单位接收第一图像(经裁剪图像hd2)的多个部分,又称为多个第一局部图像,以及分别在多个第二接收时间单位接收第二图像(经缩小图像ld2)的多个部分,又称为多个第二局部图像,其中这些第一接收时间单位与这些第二接收时间单位交替排列。这些第一接收时间单位的每一个的长度足以接收经裁剪图像hd2的至少一条线,以及这些第二接收时间单位的每一个的长度足以接收经缩小图像ld2的至少一条线。存储器单元222耦接至接收电路221,以存储第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)(步骤s620)。依照实际实施,在一些范例中,经裁剪图像hd2的分辨率(又称为第一分辨率)相同于经缩小图像ld2的分辨率(又称为第二分辨率)。在另一些范例中,经裁剪图像hd2的分辨率可以不同于经缩小图像ld2的分辨率。

69.注视点渲染电路223耦接至存储器单元222。在步骤s630中,注视点渲染电路223基于第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)进行图像处理,而产生待显示的输出图像imgout,其中,第一图像相对于输出图像imgout的注视区域。经裁剪图像hd2的分辨率不同于输出图像imgout的分辨率(又称为第三分辨率)。

70.注视点渲染电路223基于第一图像(经裁剪图像hd2)与第二图像(经缩小图像ld2)所进行的图像处理说明如下。首先,注视点渲染电路223可以放大经缩小图像ld2,以产生经放大图像。注视点渲染电路223可以混合经裁剪图像hd2和所述经放大图像(经裁剪图像hd2被混合到所述经放大图像的注视区域),以产生输出图像imgout。其中,所述经放大图像的分辨率相同于输出图像imgout的分辨率。输出图像imgout的注视点区域的图像数据可以相异于图像处理器侧的原始图像的注视点区域的图像数据。

71.图7是依照本发明的一实施例说明图2所示存储器单元222与注视点渲染电路223的电路方块示意图。图7所示接收电路221、存储器单元222与注视点渲染电路223可以参照图2所示接收电路221、存储器单元222与注视点渲染电路223的相关说明,故不再赘述。在图7所示实施例中,存储器单元222包括存储器空间222a和存储器空间222b。存储器空间222a和存储器空间222b是存储器单元222中的独立空间。接收电路221被配置为分别在多个第一接收时间单位中接收第一图像(经裁剪图像hd2)的多个第一局部图像并且存储多个第一局部图像到存储器单元222的存储器空间222a中,并且分别在多个第二接收时间单位中接收第二图像(经缩小图像ld2)的多个第二局部图像并且存储多个第二局部图像到存储器单元222的存储器空间222b中。

72.在图7所示实施例中,注视点渲染电路223包括译码器电路dec71、译码器电路dec72、缩放器电路sc7以及混合电路bl7。译码器电路dec71耦接至存储器单元222,以从存储器空间222a读取经裁剪图像hd2(第一图像)。译码器电路dec71可以解码经裁剪图像hd2,

而产生经裁剪图像hd2’。译码器电路dec72耦接至存储器单元222,以从存储器空间222b读取经缩小图像ld2(第二图像)。译码器电路dec72可以解码经缩小图像ld2,而产生经缩小图像ld2’。缩放器电路sc7可以放大(scale up)解码后的第二图像(经缩小图像ld2’),以产生经放大图像img22。混合电路bl7可以混合经裁剪图像hd2’和经放大图像img22,以产生输出图像imgout。

73.上述数据放大、混合及输出放大图像等操作可以是逐水平显示线进行。亦即,可以不须等待一个完整来源图像帧接收完毕才做数据放大/混合操作。在接获经缩小图像的第一条线后,显示驱动器集成电路220便可以开始产生欲显示的输出图像imgout的第一条线给显示面板(未绘示)。因此,延迟时间可以有效地缩短。

74.图8是依照本发明的另一实施例说明图2所示注视点渲染电路223的电路方块示意图。图8所示接收电路221、存储器单元222与注视点渲染电路223可以参照图2所示接收电路221、存储器单元222与注视点渲染电路223的相关说明,故不再赘述。在图8的实施例中,并无连续的内存空间供专用于存储多个第一局部图像或专用于存储多个第二局部图像。

75.在图8所示实施例中,接收电路221被配置为,将接收电路221分别在多个第一接收时间单位中接收到的第一图像(经裁剪图像hd2)的多个第一局部图像存储到存储器单元222,并且将接收电路221分别在多个第二接收时间单位中接收到的第二图像(经缩小图像ld2)的多个第二局部图像存储到存储器单元222。

76.图8所示注视点渲染电路223包括译码器电路dec81、译码器电路dec82、缩放器电路sc8以及混合电路bl8。图8所示译码器电路dec81、译码器电路dec82、缩放器电路sc8以及混合电路bl8可以参照图7所示译码器电路dec71、译码器电路dec72、缩放器电路sc7以及混合电路bl7的相关说明并且加以类推,故不再赘述。

77.译码器电路dec81与dec82耦接至存储器单元222。在图8所示实施例中,译码器电路dec81被配置为,存取在存储器单元222中分别存有第一图像(经裁剪图像hd2)的多个第一局部图像的多个第一指定空间。译码器电路dec81可以解码经裁剪图像hd2,并且在解码后输出经裁剪图像hd2’(第一图像)。译码器电路dec82被配置为,存取在存储器单元222中分别存有第二图像(经缩小图像ld2)的多个第二局部图像的多个第二指定空间。译码器电路dec82可以解码经缩小图像ld2,并且在解码后输出经缩小图像ld2’(第二图像)。

78.综上所述,上述诸实施例所述图像提供电路(例如图像处理器)可以基于原始图像产生经裁剪图像(第一图像)与经缩小图像(第二图像)。在经裁剪图像与经缩小图像中的一个被完全传送给显示驱动器集成电路之前,图像处理器可以先传送经裁剪图像与经缩小图像中的另一个的至少一部分给显示驱动器集成电路。因此,所述延迟时间可以被有效缩减。

79.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1