基于DSP和FPGA可调相位增量的数字下变频与多普勒补偿方法与流程

基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法

技术领域

1.本发明涉及一种数字下变频与多普勒补偿方法,具体是指一种利用dsp和fpga协同处理,实现可调相位增量的数字下变频与多普勒补偿方法,可应用于航天领域的雷达信号处理领域。

背景技术:

2.作为中频信号处理的关键技术,数字下变频可在保留原始信号的特性的前提下,降低采样信号的速率。为解决雷达分辨率与作用距离之间的矛盾,中频信号经数字下变频后需要进行脉冲压缩处理。二相编码信号具有良好的自相关特性,但是对运动目标的多普勒频率较为敏感。目标运动速度较大时,脉冲压缩效果急剧恶化,因此有效补偿多普勒频移对二相编码雷达信号处理具有重要意义。随着中频信号处理技术的发展以及可编程硬件fpga性能的提高,对数字下变频和多普勒补偿快速实现的需求日益迫切。

3.数字下变频和多普勒补偿处理的输入为速率较高的中频信号,且输入的数据量较大,其实现一般依托于fpga芯片。近些年,随着信号处理技术的发展,相关学者提出了很多数字下变频和多普勒补偿的方法。

4.专利《fpga中实现超高速数字正交下变频及抽取滤波的方法与系统》(专利申请号:201610227770.9;专利公开号:cn105915241a)中,对两组adc(模/数转换)数据信号和一组adc时钟信号进行跨时域同步化处理,两组同步化后的adc数据信号分别通过四个乘法器与本地数控振荡器输出的四路数字本振信号分别相乘,完成数字域的频率搬移功能。

5.专利《基于相同fpga乘法器资源实现的任意抽取数字下变频方法》(专利申请号:cn201210590839.6;专利公开号:cn103078592a)中,利用移位寄存器改变数据顺序,将两路一倍数据率的数据变换成一路两倍数据率的数据,按照系数对称的原则进行预加处理,在不同抽取率条件下复用乘法器,实现任意抽取数字下变频。

6.专利《矢量信号分析中高速并行下变频fpga数据处理系统及方法》(专利申请号:cn201810574092.2;专利公开号:cn108762154a)中,借助模拟前端设备将输入的中频信号进行多路并行数据采集,通过fpga接收并行数据,采用多路并行交叉混频方法完成多路高速并行信号的下变频。

7.文献《数字下变频ddc的设计与fpga实现》(刊载于“中国集成电路”,no.1,2017)中,详细介绍了数字下变频的各种滤波器设计,包括cic滤波器、hb滤波器、fir滤波器,并编写verilog hdl程序实现各个模块。

8.文献《数字下变频与脉冲压缩系统的设计与实现》(刊载于“雷达科学与技术”,no.2,2010)中,在单片fpga上实现了对实际采集的中频chirp信号进行8k点或2k点可变点数的数字下变频与脉冲压缩处理。

9.文献《二相编码信号的多普勒特性及其补偿算法研究》(刊载于“电子科技”,no.9,2013)中,提出基于mtd的二相编码多普勒补偿方法,对相同距离单元的数据做dft,然后在

频域各多普勒通道内对信号进行相应的相位补偿,然后对各个脉冲做脉压求模运算。

10.由上述专利和文献可知,从中频信号到频率变化的低频信号的转换,目前尚无适用的数字下变频方法。而现有的多普勒补偿方法都需对复数矩阵内的各个数据进行修正,运算量较大。

11.基于上述,本发明提出一种基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,通过dsp与fpga协同处理,同时实现可调增量的数字下变频与多普勒补偿,具有很强的实时性且系统易于维护和扩展。

技术实现要素:

12.本发明的目的是提供一种基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,计算量小,设备易于实现,具有很强的实时性且易于维护和扩展。

13.为实现上述目的,本发明提供一种基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,包含以下步骤:

14.s1、dsp与fpga利用单脉冲信号,进行参差重频处理,求解高速运动目标速度模糊,得到目标真实速度;

15.s2、dsp根据目标真实速度,计算需补偿的多普勒频率,对雷达发射后经目标反射的回波信号进行多普勒补偿;

16.s3、dsp实时计算相位增量;

17.s4、通过dsp的外部存储器接口,将s3中更新的相位增量传输至fpga的内部ram;

18.s5、fpga根据本帧信号处理完成标志,从内部ram中读取更新的相位增量;

19.s6、调用fpga内的dds ip核,向dds ip核输入参考时钟和更新的相位增量,合成所需频率的信号;

20.s7、fpga将多普勒补偿后的回波信号与dds ip核生成的信号进行混频,将回波信号频谱搬移到低频基带位置,并进行滤波处理;通过dsp与fpga协同工作,实时获得数字下变频和多普勒补偿后的低频基带信号。

21.所述的s2中,根据目标的真实速度,dsp实时计算补偿多普勒频率f

d

,对雷达发射后经目标反射的回波信号进行实时多普勒补偿;具体为:

22.f

d

=2

×

v_real/λ

23.其中,v_real为目标的真实速度;λ为回波信号的波长。

24.所述的s3中,根据当前需要达到的dds ip输出信号的输出频率,实时计算对应的频率控制字,即相位增量k;具体为:

[0025][0026]

其中,clk为dds ip的参考时钟频率;n为相位数据位宽;f

out

为当前需要达到的dds ip输出信号的输出频率。

[0027]

所述的s5中,具体包含以下步骤:

[0028]

s51、在fpga内设置本帧信号处理完成标志;

[0029]

s52、fpga判断本帧信号处理是否完成;如是,本帧信号处理完成标志翻转;如否,本帧信号处理完成标志保持不变;

[0030]

s53、fpga根据本帧信号处理完成标志选择相位增量。

[0031]

所述的s53中,具体为:当本帧信号处理完成标志翻转时,fpga从内部ram中读取更新的相位增量并使用;当本帧信号处理完成标志保持不变时,fpga继续使用当前相位增量。

[0032]

所述的s6中,具体包含以下步骤:

[0033]

s61、设置dds ip核的系统时钟、通道数、无杂散动态范围和频率分辨率的参数;

[0034]

s62、向dds ip核输入参考时钟和更新的相位增量,使dds ip核以参考时钟作为参考,对相位进行可控间隔采样,合成所需频率的正余弦信号。

[0035]

所述的s7中,具体包含以下步骤:

[0036]

s71、混频处理:将经过多普勒补偿后的回波信号经adc离散化采样后得到中频信号;调用乘法器,将中频信号与dds ip核生成的正余弦信号相乘,将回波信号的频谱搬移至低频基带位置;

[0037]

s72、滤波处理:通过fir滤波器,对混频处理过程中产生的谐波分量进行滤波,得到包含目标信息的低频基带信号。

[0038]

综上所述,本发明提供的基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,与现有技术相比,具有以下优点和有益效果:

[0039]

1、本发明不需要对fpga处理得到的复数矩阵中每个数据逐个修正,整体计算量小;

[0040]

2、本发明调用fpga内部的dds ip核,不需专用的dds芯片等器件,对硬件设备要求较低,易于实现;

[0041]

3、本发明通过调用dds ip核和少量乘法器,实现实时变化的数控频率合成和多普勒补偿;

[0042]

4、本发明通过调整相位增量,实现数字下变频和多普勒补偿的联合处理,操作灵活;

[0043]

5、本发明无需通过幅度/相位转换电路构建正弦信号查找表,占用内存更少,适用范围更广;

[0044]

6、本发明借助dsp芯片的强大计算能力,实现相位增量的快速更新,实时性强。

附图说明

[0045]

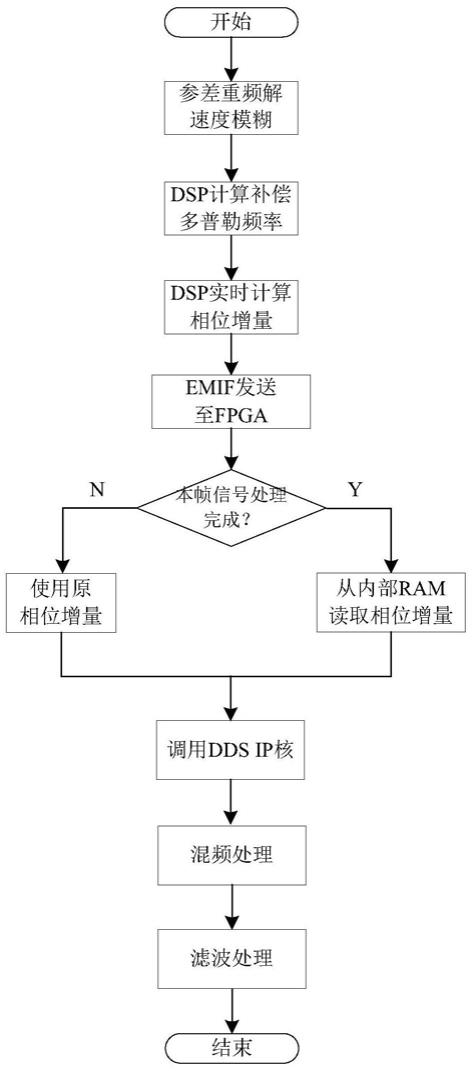

图1为本发明中的基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法的流程图;

[0046]

图2为本发明中的dsp与fpga的连接关系示意图;

[0047]

图3为本发明中的dds ip核的调用过程示意图。

具体实施方式

[0048]

以下结合图1~图3,通过优选实施例对本发明的技术内容、构造特征、所达成目的及功效予以详细说明。

[0049]

如图1所示,为本发明提供的基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,包含以下步骤:

[0050]

s1、dsp(数字信号处理)与fpga(现场可编程门阵列)利用单脉冲信号,进行参差重

频处理,求解高速运动目标速度模糊,得到目标真实速度;

[0051]

s2、dsp根据目标真实速度,计算需补偿的多普勒频率,对雷达发射后经目标反射的回波信号进行多普勒补偿;

[0052]

s3、dsp实时计算相位增量;

[0053]

s4、通过dsp的emif(external memory interface,外部存储器接口),将s3中更新的相位增量传输至fpga的内部ram(随机存取存储器);

[0054]

s5、fpga根据本帧信号处理完成标志,从内部ram中读取更新的相位增量;

[0055]

s6、调用fpga上设置的dds ip核,向dds ip核输入参考时钟和更新的相位增量,合成所需频率的信号;

[0056]

s7、fpga将多普勒补偿后的回波信号与dds ip核生成的信号进行混频,将回波信号频谱搬移到低频基带位置,并进行滤波处理;通过dsp与fpga协同工作,实时获得数字下变频和多普勒补偿后的低频基带信号。

[0057]

所述的s1中,由于高速运动目标的多普勒频率往往会超过单个prf(脉冲重复频率),其多普勒谱线在重频范围内折叠,即其速度会发生模糊。在这种情况下,基于孙子定理,dsp与fpga利用单脉冲信号,进行参差重频处理,采用余差查表法求解高速运动目标的速度模糊,计算出目标的真实速度。

[0058]

本实施例中,利用目标模拟器向dsp和fpga所在的信号处理板提供20mhz的中频信号;设定目标速度为50m/s;设定雷达频率为f=10ghz;设定3个重频分别是prf1=387hz,prf2=499hz,prf3=517hz。根据上述s1中所述的方法,dsp与fpga利用单脉冲信号,进行参差重频处理,采用余差查表法求解高速运动目标的速度模糊,进而计算出目标的真实速度为50m/s。

[0059]

二相编码信号对运动目标的多普勒频率较为敏感,尤其目标速度较大时更为明显。为避免接收信号与原匹配滤波器失配,因此在所述的s2中,需要对回波信号进行多普勒补偿。具体的:

[0060]

设置雷达发射信号s(t)为:

[0061]

s(t)=u(t)exp[j2πf

c

t]

[0062]

其中,u(t)为复包络信号;f

c

为载波频率;t为当前时间;

[0063]

雷达发射信号s(t)经目标反射的回波信号r0(t)为:

[0064][0065]

其中,δ为衰减因子;f

d

为目标的多普勒频率;为常数,代表目标反射产生的相移;

[0066]

对回波信号r0(t)进行下变频处理,得到信号r(t)为:

[0067][0068]

其中,f

d

为目标的多普勒频率;显然,信号r(t)的幅度经过了多普勒频率调制。

[0069]

根据上述,在步骤s2中,需要利用dsp快速处理能力,根据目标的真实速度,实时计算补偿多普勒频率f

d

,对雷达发射后经目标反射的回波信号进行实时多普勒补偿,具体为:

[0070]

f

d

=2

×

v_real/λ

[0071]

其中,v_real为目标的真实速度;λ为回波信号的波长。

[0072]

本实施例中,v_real为50m/s;根据雷达频率f=10ghz得到λ为0.03m;因此计算得到补偿多普勒频率f

d

为3333hz。

[0073]

传统的使用dds芯片设计信号发生器时,需要相位累加器、正弦rom幅度查找表、dac(数模转换器)和lpf(低通滤波器)等组成模块的配合,结构复杂且模块通用性较差。随着可编程逻辑器件fpga硬件水平的提高以及直接频率合成技术的不断发展,在fpga平台上已开发出dds ip核(信号发生器知识产权核)。经数控频率合成后,dds ip核的输出信号的输出频率f

out

为:

[0074][0075]

其中,k为频率控制字;clk为dds ip核的参考时钟频率;n为相位累加器中的相位数据位宽。

[0076]

因此,对于dds ip核中的单个通道,其频率控制字为:

[0077][0078]

由此可见,dds ip核的输出频率取决于频率控制字。因此,在本发明的步骤s3中,可利用dsp的快速计算优势,根据补偿多普勒频率f

d

和数字下变频频率f

c

,更新所需dds ip核的输出信号的输出频率f

out

,且f

out

=f

c

+f

d

,并实时计算对应的频率控制字k,即相位增量。

[0079]

本实施例中,设置dds ip核的参考时钟频率为clk=50mhz,相位累加器中相位数据位宽为n=16,根据数控频率合成后,希望使dds ip核输出信号的输出频率f

out

=20.0033mhz,因此dsp计算得到相位增量为

[0080]

dsp具有强大的emif,可访问sram、rom和flash等多种外部存储器。因此,在所述的s4中,可借助dsp所具有的emif,将s3中得到的更新的相位增量快速传输至fpga的内部ram。如图2所示,以型号为jfm4vsx55rt的fpga和型号为smj320c6415的dsp为例,为实现dsp对fpga的内部ram的访问,将emif通信所需的dsp管脚与fpga相应管脚对接。

[0081]

本实施例中,借助dsp的emif,可将更新的相位增量快速传输至fpga的内部ram。

[0082]

所述的s5中,具体包含以下步骤:

[0083]

s51、在fpga内设置本帧信号处理完成标志;

[0084]

s52、fpga判断本帧信号处理是否完成;如是,本帧信号处理完成标志翻转;如否,本帧信号处理完成标志保持不变;

[0085]

s53、fpga根据本帧信号处理完成标志选择相位增量;当本帧信号处理完成标志翻转时,fpga从内部ram中读取dsp更新的相位增量并使用;当本帧信号处理完成标志保持不变(未翻转)时,fpga继续使用当前相位增量(即fpga不从内部ram中读取dsp更新的相位增量)。

[0086]

本实施例中,在所述的s52中,设置脉冲积累数为m,单个脉冲采样n点。当fpga完成当前帧m个脉冲的处理后,即认为本帧信号处理完成,将本帧信号处理完成标志翻转;当fpga未完成当前帧m个脉冲的处理时,即认为本帧信号处理未完成,本帧信号处理完成标志

保持不变。在本发明中,只有当本帧信号处理完成之后,才可修改信号处理的相关参数,其中当然也包括相位增量。

[0087]

本实施例中,在所述的s53中,当本帧信号处理完成标志翻转时,fpga从内部ram中读取dsp更新的相位增量并使用。

[0088]

所述的s6中,具体包含以下步骤:

[0089]

s61、设置dds ip核的系统时钟、通道数、无杂散动态范围和频率分辨率等参数;使dds ip核能够按需求进行数控频率合成;

[0090]

s62、如图3所示,向dds ip核输入参考时钟和更新的相位增量,使dds ip核以参考时钟作为参考,对相位进行可控间隔采样,合成所需频率的正余弦信号。

[0091]

本实施例中,设置dds ip核的系统时钟为50mhz,通道数为1,无杂散动态范围为91,频率分辨率为461.4258。向dds ip核输入50mhz的参考时钟和更新的相位增量使dds ip核以参考时钟作为参考,对相位进行可控间隔采样,合成所需频率为20.0033mhz的正余弦信号。

[0092]

所述的s7中,具体包含以下步骤:

[0093]

s71、混频处理:将经过多普勒补偿后的回波信号经adc(模数转换器)离散化采样后得到中频信号;调用乘法器,将中频信号与dds ip核生成的正余弦信号相乘,将回波信号的频谱搬移至dsp所需的低频基带位置;

[0094]

s72、滤波处理:通过fir(有限脉冲响应)滤波器,对混频处理过程中产生的谐波分量进行滤波,得到包含目标信息的低频基带信号,并进行下采样抽取滤波,获得数字下变频和多普勒补偿后的低频基带信号。

[0095]

综上所述,本发明提供的基于dsp和fpga可调相位增量的数字下变频与多普勒补偿方法,与现有技术相比,具有以下优点和有益效果:

[0096]

1、本发明不需要对fpga处理得到的复数矩阵中每个数据逐个修正,整体计算量小;

[0097]

2、本发明调用fpga内部的dds ip核,不需专用的dds芯片等器件,对硬件设备要求较低,易于实现;

[0098]

3、本发明通过调用dds ip核和少量乘法器,实现实时变化的数控频率合成和多普勒补偿;本发明在实现过程占用内存较少,一般仅需要4块18k的bram(嵌入块ram);

[0099]

4、本发明通过调整相位增量,实现数字下变频和多普勒补偿的联合处理,操作灵活;

[0100]

5、本发明无需通过幅度/相位转换电路构建正弦信号查找表,占用内存更少,适用范围更广;

[0101]

6、本发明借助dsp芯片的强大计算能力,实现相位增量的快速更新,实时性强。

[0102]

尽管本发明的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本发明的限制。在本领域技术人员阅读了上述内容后,对于本发明的多种修改和替代都将是显而易见的。因此,本发明的保护范围应由所附的权利要求来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1