使用主机总线适配器在自动化测试设备中提供协议灵活性的制作方法

使用主机总线适配器在自动化测试设备中提供协议灵活性

1.相关申请的交叉引用

2.本技术是于2018年3月7日提交的标题为“a test architecture with a fpga based test board to simulate a dut or end

‑

point(具有用于仿真dut或端点的基于fpga的测试板的测试架构)”、发明人为duane champoux和mei

‑

mei su、代理人案卷号为atst

‑

jp0090.p1的美国专利申请号15/914,553的部分继续申请,而该美国专利申请又是于2013年2月21日提交的标题为“a test architecture having multiple fpga based hardware accelerator blocks for testing multiple duts independently(具有用于独立测试多个dut的多个基于fpga的硬件加速器块的测试架构)”、发明人为gerald chan、eric kushnick、mei

‑

mei su和andrew niemic、代理人案卷号为atst

‑

jp009的美国专利申请号13/773,569的部分继续申请0。这两个申请的全部内容通过引用并入本文以用于所有目的。

3.本技术还要求享有于2020年3月12日提交的标题为“use of host bus adapter to provide protocol flexibility used in combination with fpga with full acceleration for testing(使用与具有用于测试的全加速的fpga结合使用的主机总线适配器提供协议灵活性)”,其案卷号为atsy

‑

0090

‑

00.00us的美国临时申请62/988,612的优先权。将上面所列的每一项申请的全部内容通过引用并入本文以用于所有目的,就像它们的全部内容完全地在本文记载一样。

技术领域

4.本公开总体上涉及电子设备测试系统的领域,并且更具体地,涉及用于测试被测器件(dut)的电子设备测试设备的领域。

背景技术:

5.自动化测试设备(ate)可以是对半导体器件或电子组装件执行测试的任何测试组装件。ate组装件可用于执行快速进行测量并生成然后可被分析的测试结果的自动化测试。ate组装件可以是从与仪表耦合的计算机系统到复杂的自动化测试组装件的任何设备,该复杂的自动化测试组装件可以包括定制的专用计算机控制系统和能够自动地测试电子部件和/或进行半导体晶圆测试(例如,片上系统(soc)测试或集成电路测试)的许多不同测试仪器。ate系统既减少了为确保设备功能如设计那样运行而花费在测试设备上的时间量,又充当一种诊断工具,用以在给定设备到达消费者之前确定该设备内的故障组件的存在。

6.图1是用于一种类型的用于测试某些典型dut(例如,诸如dram之类的半导体存储器设备)的常规自动化测试设备(ate)主体100示意性框图。ate包括具有硬件总线适配器插槽110a

‑

110n的ate主体100。专用于特定通信协议(例如,pcie、usb、sata、sas等)的硬件总线适配器卡110a

‑

110n连接到设置在ate主体上的硬件总线适配器插槽并且通过专用于相应协议的电缆与dut的接口连接。ate主体100还包括测试器处理器101以及相关联的存储器108,该测试器处理器101用于控制内置在ate主体100中的硬件组件并生成通过硬件总线适

配器卡与被测dut进行通信所需的命令和数据。测试器处理器101通过系统总线130与硬件总线适配器卡进行通信。可以将测试器处理器编程以包括某些功能块,这些功能块包括图案生成器102和比较器106。替代地,图案生成器102和比较器106可以是安装在插入到ate主体100中的扩展卡或适配器卡上的硬件组件。

7.ate主体100通过插入到ate主体100的硬件总线适配器插槽中的硬件总线适配器来测试连接到ate主体100的dut 112a

‑

112n的电气功能。因此,测试器处理器101被编程以使用硬件总线适配器特有的协议来将需要运行的测试程序传送到dut。同时,内置在ate主体100中的其他硬件组件根据在测试器处理器101中操作的测试程序在彼此之间传送信号以及与dut传送信号。

8.由测试器处理器101运行的测试程序可以包括涉及下述步骤的功能测试:将由图案生成器102创建的输入信号写入到dut、从dut中读出被写入的信号、并且使用比较器106将输出与期望的图案进行比较。如果输出与输入不匹配,则测试器处理器101会将dut标识为有缺陷的。例如,如果dut是诸如dram之类的存储器设备,则测试程序会使用写入操作将由图案生成器102生成的数据写入到dut、使用读取操作从dram读取数据、并且使用比较器106将期望的位图案与读取的图案进行比较。

9.在常规系统中,测试器处理器101需要包含功能逻辑块(例如,图案生成器102和比较器106)以生成在测试dut中使用的命令和测试图案,这些功能逻辑块以软件直接编程在处理器上。然而,在一些情况下,诸如比较器106之类的某些功能块可以在现场可编程门阵列(fpga)上实现,fpga是可以根据用户的需求对逻辑电路进行编程的专用集成电路(asic)型半导体器件。

10.常规系统中使用的fpga可以是转发命令和测试图案的传递设备,其中,依靠测试器处理器101把命令和测试图案发送到fpga,fpga又把这些命令和测试图案转发到dut。因为测试器处理器而不是fpga负责生成命令和测试图案,所以可以使用给定ate主体测试的dut的数量和类型受到测试器处理器的处理能力和编程的限制。在测试器处理器生成所有命令和测试图案的情况下,将测试器处理器连接到各种硬件组件(包括任何fpga器件和硬件总线适配器插槽)的系统总线130上的带宽限制也对可以同时测试的dut的数量设置了上限。

11.此外,在常规系统中,用于与dut进行通信的通信协议是固定的,这是因为插入到ate主体100中的硬件总线适配器卡是被设计为仅以一种协议进行通信并且无法被重新编程为以不同的协议进行通信的单用途设备。例如,被配置为测试pcie设备的ate主体将具有仅支持pcie协议的插入到该主体中的硬件总线适配器卡。为了测试支持不同协议(例如,sata)的dut,用户通常需要用支持sata协议的总线适配器卡来替换pcie硬件总线适配器卡。除非用支持其他协议的卡来物理地替代pcie硬件总线适配器卡,否则这样的系统只能对支持pcie协议的dut进行测试。

12.在不同类型的常规ate中,fpga不仅是如上所述的传递设备。代替使用硬件总线适配器卡来实现与dut进行通信的协议,可以通过从系统控制器上的缓存中进行简单的位流下载,来将与dut进行通信的新协议直接下载并安装在测试器系统的fpga上。测试器中的fpga通常可以包括下述可配置接口核心(或ip核心):其可编程来为dut提供一个或多个基于协议的接口的功能并且可编程来与dut接口连接。另外,如果发布了新协议,则fpga可容

易地经由位流下载被配置有该协议,这比不得不物理地切换系统中的所有硬件总线适配器卡更方便。

13.通常,常规测试器仅允许单个ip核心编程到fpga上。由于现有的测试系统的fpga加速器只能支持单个ip核心,因此,如果需要将不同的第三方ip核心编程到fpga中,则需要对fpga进行重新编程。因此,如果需要将连接到fpga的dut换成其他类型的dut,则需要对fpga进行重新编程以支持不同的协议。在测试环境中,对fpga进行重新编程可能既耗时又麻烦。

14.此外,存储器和其他设备的上市时间越来越短。此外,协议ip越来越专有,因此fpga可能仅支持单个协议。此外,由于许多第三方ip核心是专有的,因此无法将它们编程到fpga上。

技术实现要素:

15.因此,需要一种能够解决上述系统的问题的测试器架构。需要下述测试架构:通过该架构,可以将命令和测试图案生成功能转移到fpga上,使得测试器处理器上的处理负载和对系统总线的带宽需求能被保持在最低。这将比现有的配置更高效,在现有的配置中,测试器处理器承担了全部处理工作负载,并且系统总线为连接到ate主体的所有dut传递测试数据和命令。

16.此外,需要下述测试架构:通过该架构,主机总线适配器可与fpga结合使用以提供协议灵活性。如上所述,由于协议ip越来越专有,使得fpga仅支持一种协议,而如果需要另一种协议,则可以使用主机总线适配器(hba)来桥接第三方ip协议。换句话说,fpga中的可配置接口核心(或ip核心)(其是可编程的)与主机总线适配器结合使用,以便与第三方协议接口连接以与支持不同于ip核心内编程的协议的dut进行通信。这允许工程师在测试环境中快速切换协议,而无需对fpga进行重新编程。

17.在一个实施例中,公开了一种自动化测试设备(ate)系统。该装置包括:系统控制器,该系统控制器通信地耦合到测试器处理器,其中,该系统控制器可操作来向测试器处理器发送指令,并且其中,该测试器处理器可操作来根据指令来生成命令和数据以协调对多个被测器件(dut)的测试。该装置还包括fpga,该fpga通信地耦合到测试器处理器,并且该fpga包括至少一个硬件加速器电路,该硬件加速器电路可操作来透明地从测试器处理器内部生成命令和数据以测试多个dut中的dut。此外,该装置还包括总线适配器,该总线适配器包括协议转换器模块,该协议转换器模块可操作来先将从fpga接收到的与第一协议相关联的信号转换为与第二协议相关联的信号,然后再向dut发送信号,其中,dut使用第二协议进行通信。在一个实施例中,第二协议是专有第三方协议。

18.在另一实施例中,自动化测试设备(ate)装置包括测试器处理器和通信地耦合到该测试器处理器的fpga,该测试器处理器可操作来生成命令和数据以协调对多个被测器件(dut)的测试,其中,该fpga包括硬件加速器电路,该硬件加速器电路可操作来透明地从所述测试器处理器内部生成命令和数据以测试所述多个dut中的dut,并且其中,fpga包括ip核心,该ip核心可操作来生成用于使用第一协议把命令和数据从fpga发送到dut的信号。该装置还包括总线适配器,该总线适配器包括协议转换器模块,该协议转换器模块可操作来先将从fpga接收到的与第一协议相关联的信号转换为与第二协议相关联的信号,然后再向

dut发送信号,其中,dut使用第二协议进行通信。

19.在一个实施例中,公开了一种用于测试dut的方法。该方法包括从系统控制器向测试器处理器发送指令,其中,包括fpga的测试器板和测试器处理器耦合到系统控制器,并且其中,测试器处理器可操作来协调对多个被测器件(dut)的测试。该方法还包括根据在fpga的ip核心中实现的第一协议并根据所选加速模式,生成命令和数据以测试多个dut中的dut,其中,所述生成是由包括在fpga内的硬件加速器电路执行的。此外,该方法包括使用第一协议从fpga向总线适配器发送与命令和数据相关联的信号。此外,该方法包括使用总线适配器和实现第二协议的协议ip核心,把使用第一协议传送的信号转换为第二协议的信号,其中,总线适配器通信地耦合到可操作来使用第二协议进行通信的dut。该方法还包括以第二协议来将信号转发到dut,以进行测试。

20.下面的详细描述以及附图将提供对本发明的性质和优点的更好的理解。

附图说明

21.在附图的各图中,通过示例但不通过限制来的方式图示本发明的实施例,并且在附图中,相似的附图标记指代相似的元件。

22.图1是用于测试典型的被测器件(dut)的常规自动化测试设备主体的示意框图。

23.图2是根据本发明的一个实施例的系统控制器、站点模块和dut之间的互连的高级示意框图。

24.图3是根据本发明的实施例的站点模块及其与系统控制器和dut的互连的详细示意框图。

25.图4是根据本发明的实施例的图2的实例化fpga测试器块的详细示意框图。

26.图5是根据本发明的实施例的测试dut的示例性方法的高级流程图。

27.图6是图5的继续并且是本发明的一个实施例中的在旁路模式下测试dut的示例性方法的流程图。

28.图7是图5的继续并且是本发明的一个实施例中的在硬件加速器图案生成器模式下测试dut的示例性方法的流程图。

29.图8是图5的继续并且是本发明的一个实施例中的在硬件加速器存储器模式下测试dut的示例性方法的流程图。

30.图9是图5的继续并且是本发明的一个实施例中的在硬件加速器分组构建器模式下测试dut的示例性方法的流程图。

31.图10根据本发明实施例示出了这样的一种方式,其中,包括协议转换器ip的hba可被用于将fpga连接到以与fpga被编程有的协议不同的协议进行通信的dut。

32.图11根据本发明实施例示出了包括一个或多个hba的夹心板可用于在fpga和dut之间进行接口连接的方式。

33.图12根据本发明实施例示出了示例性测试器配置,在该配置中每个dut连接有相应的加速器引擎。

34.图13根据本发明的实施例描绘了测试dut的示例性处理的流程图1300,该dut以与在测试器系统中的fpga上实现的协议不同的协议进行通信。

35.在附图中,具有相同标号的元件具有相同或类似的功能。

具体实施方式

36.现在将详细地参考实施例,这些实施例的示例被图示在附图中。虽然将结合附图描述实施例,但是应理解的是,这些附图不旨在对实施例进行限制。相反,实施例旨在涵盖替代方案、修改和等同物。此外,在以下具体实施方式中,为了提供透彻理解,阐述了许多具体细节。然而,本领域的普通技术人员应认识到,可以在没有这些具体细节的情况下实践实施例。在其他情况下,尚未详细地描述众所周知的方法、程序、组件和电路,以免不必要地模糊实施例的各方面。

37.注解及术语部分

38.以下具体实施方式的某些部分是根据计算机存储器内数据位操作的程序、逻辑块、处理和其他符号表示来呈现的。这些描述和表示是数据处理领域的技术人员用来最有效地将其工作的实质传达给本领域的其他技术人员的手段。在本技术中,程序、逻辑块、过程等被设想为导致期望结果的步骤或指令的自洽序列。这些步骤是要求对物理量进行物理操纵的步骤。通常,这些量采取能够在计算机系统中存储、传输、组合、比较和以其他方式操纵的电或磁信号的形式,但这并不是必须的。

39.然而,应该记住的是,所有这些和类似的术语将与适当的物理量相关联并且仅仅是应用于这些量的方便标签。除非明确指明,否则从下文的讨论中显而易见地看出,可以认识到,在本发明全文中,利用诸如“测试”、“通信”、“耦合”、“转换”、“转发”等术语的讨论,指的是计算机系统或类似电子计算设备的动作和进程,该计算机系统或类似电子计算设备操纵在该计算机系统的寄存器和存储器内表示为物理(电子)量的数据并将其转换成在该计算机系统存储器或寄存器或其他此类信息存储、传输或显示设备内类似地表示为物理量的其他数据。

40.以下描述提供对可以包括一个或多个模块的计算机和其他设备的讨论。如本文所使用的,术语“模块”或“块”可以被理解为指代软件、固件、硬件和/或其各种组合。注意,块和模块是示例性的。块或模块可以被组合、集成、分离和/或复制以支持各种应用。另外,代替或者除了在所描述的特定模块或块处执行的功能之外,还可以在一个或多个其他模块或块处和/或通过一个或多个其他设备来执行在本文中描述为在特定模块或块处执行的功能。此外,可以跨越彼此本地或远程的多个设备和/或其他组件来实现模块或块。附加地,模块或块可以被从一个设备移动并添加到另一设备,并且/或者可以被包括在两个设备中。本发明的任何软件实现方式可以被有形地具体实现在一个或多个存储介质中,例如存储器设备、软盘、紧致盘(cd)、数字通用盘(dvd)或可以存储计算机代码的其他设备中。

41.本文使用的术语仅用于描述特定实施例的目的,而不旨在限制本发明的范围。如贯穿本公开所使用的,除非上下文另外清楚地规定,否则单数形式“一”、“一个”和“该”包括复数形式。因此,例如,对“模块”的引用包括多个这样的模块以及单个模块,以及本领域的技术人员已知的等同物。

42.具有用于独立测试多个dut的多个基于fpga的硬件加速器块的测试架构

43.通常可以通过多种方式来提高测试吞吐量。减少dut的测试时间的一种方法是将以前在通用测试器处理器上的软件中执行的功能转移到在fpga器件上实现的硬件加速器。另一种方法是通过增加可在主要(prevailing)硬件和时间限制下进行测试的被测器件(dut)的数量和类型,例如,通过将硬件配置为使得支持许多不同类型的协议(例如,pcie、

sata)的dut可以利用相同的硬件进行测试而无需更换或重新配置任何硬件组件。本发明的实施例旨在改进自动化测试设备的硬件中的测试效率。

44.图2是根据本发明的实施例的自动化测试设备(ate)装置200的示例性高级框图,该装置在中测试器处理器通过具有内置功能模块的fpga器件连接到被测器件(dut)。在一个实施例中,可以在能够同时测试多个dut的任何测试系统内实现ate装置200。

45.参考图2,根据本发明的实施例的用于更高效地测试半导体器件的ate装置200包括:系统控制器201;网络交换机202,其将系统控制器连接到站点模块板230a

‑

230n;fpga器件211a

‑

211m,其包括实例化fpga测试器块210a

‑

210n;存储器块模块240a

‑

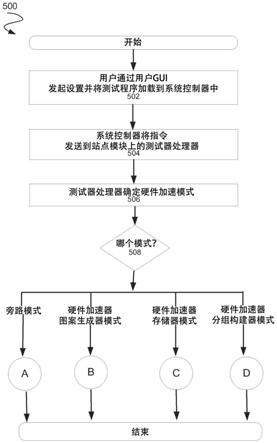

240m,其中这些存储器块中的每一者连接到fpga器件211a

‑

211m中的一者;以及被测器件(dut)220a

‑

220n,其中每个被测器件220a

‑

220n连接到实例化fpga测试器块210a

‑

210n中的一者。

46.在一个实施例中,系统控制器201可以是计算机系统,例如,为ate的用户提供用户界面以加载测试程序并运行对连接到ate 200的dut的测试的个人计算机(pc)。verigy stylus操作系统是通常在器件测试期间使用的测试软件的一个示例。它给用户提供了用来配置并控制测试的图形用户界面。它还可包括以下功能:控制测试流程、控制测试程序的状态、确定哪一个测试程序正在运行、并且记录测试结果和与测试流程有关的其他数据。在一个实施例中,系统控制器可连接到并控制多达512个dut。

47.在一个实施例中,系统控制器201可通过网络交换机(例如,以太网交换机)连接到站点模块板230a

‑

230n。在其他实施例中,网络交换机可以与诸如光纤通道、802.11或atm之类的不同协议兼容。

48.在一个实施例中,站点模块板230a

‑

230n中的每一者均可以是用于评估和开发目的的单独的独立板,其附接到加载有dut 220a

‑

220n的定制负载板固定装置,并且还附接到接收测试程序的系统控制器201。在其他实施例中,站点模块板可以被实现为插入式扩展卡或者直接插入系统控制器201的机箱中的子板。

49.在一个实现方式中,站点模块板230a

‑

230n可各自包括至少一个测试器处理器204和至少一个fpga器件。站点模块板上的测试器处理器204和fpga器件211a

‑

211m根据从系统控制器201接收到的测试程序指令针对每个测试用例运行测试方法。在一个实施例中,测试器处理器可以是市场上可买到的intel 8086cpu或任何其他公知的处理器。此外,测试器处理器可以在ubuntu os x64操作系统上进行操作并运行核心软件,该核心软件允许测试器处理器与在系统控制器上运行的stylus软件进行通信以运行测试方法。测试器处理器204基于从系统控制器接收到的测试程序来控制站点模块上的fpga器件和连接到站点模块的dut。

50.测试器处理器204通过总线212连接到fpga器件并可与之进行通信。在一个实施例中,测试器处理器204通过单独的专用总线与fpga器件211a

‑

211m中的每一者进行通信。在一个实施例中,测试器处理器204可通过fpga透明地控制对dut 220a

‑

220n的测试,其中,fpga器件分配有最低的处理功能。在此实现方式中,fpga器件充当传递设备。在此实施例中,因为由测试器处理器生成的所有命令和数据都需要通过总线被传送到fpga器件,所以总线212的数据流量容量可被迅速地耗尽。在其他实施例中,测试器处理器204可以通过将用于控制对dut的测试的功能分配给fpga器件来共享处理负载。在这些实施例中,因为fpga器件可以生成它们自己的命令和数据,所以减少了总线212上的流量。

51.在一个实施例中,fpga器件211a

‑

211m中的每一者均连接到它自己的专用存储器块240a

‑

240m。这些存储器块可用于存储被写出到dut的测试图案数据以及其他的事项。在一个实施例中,fpga器件中的每一者均可包括具有用于执行功能的功能模块(包括如本文进一步描述的通信协议引擎和硬件加速器的实现方式)的两个实例化fpga测试器块210a

‑

210b。存储器块240a

‑

240m可各自包含一个或多个存储器模块,其中存储器块内的每个存储器模块可专用于实例化fpga测试器块210a

‑

210b中的一者或多者。因此,实例化fpga测试器块210a

‑

210b中的每一者均可连接到存储器块240a内的它自己的专用存储器模块。在另一实施例中,实例化fpga测试器块210a和210b可共享存储器块240a内的存储器模块中的一者。

52.此外,系统中的dut 220a

‑

220n中的每一者均可按“每dut的测试器(tester per dut)”配置连接到专用的实例化fpga测试器块210a

‑

210n,其中每个dut获得它自己的测试器块。这允许针对每个dut执行单独的测试。这样的配置中的硬件资源是以用最小硬件共享支持个体dut的方式而设计的。此配置还允许并行测试许多dut,其中每个dut可连接到它自己的专用fpga测试器块并运行不同的测试程序。在一个实施方式中,两个或更多个dut也可以连接到每个fpga测试器块(例如,块210a)。

53.图2中描绘的本发明的实施例的架构具有若干优点。首先,它允许将通信协议模块直接编程在fpga器件内的实例化fpga测试器模块上。实例化测试器块可被配置为以dut支持的任何协议与dut进行通信。因此,如果需要测试具有不同的协议支持的dut,则可将它们连接到同一系统并且可将fpga重新编程以支持相关联的协议。其结果是,一个ate主体可被容易地配置为测试支持许多不同类型的协议的dut。

54.在一个实施例中,通过从系统控制器201上的缓存经由简单的位流下载可以直接在fpga上下载和安装新的协议,而不需要进行任何种类的硬件交互。fpga将通常包括可编程以为dut提供一个或多个基于协议的接口的功能并且可编程以与dut接口连接的可配置接口核心(或ip核心)。例如,ate装置200中的fpga 211a

‑

211m将包括可被配置有pcie协议的接口核心,以初始测试pcie设备并随后经由软件下载重新配置来测试sata设备。另外,如果发布了新协议,则可容易地经由位流下载用该协议来配置fpga。最后,如果需要实现非标准协议,则fpga可仍然被配置为实现这样的协议。

55.在另一实施例中,fpga 211a

‑

211m可被配置为运行多于一种通信协议,其中这些协议也可从系统控制器201下载并通过软件来配置。换句话说,每个fpga实现定制固件和软件映像以在单个芯片中实现一个或多个基于pc的测试器的功能。所需要的电信令和基于协议的信令是由fpga中的片上ip核心提供的。如上面所提及的,每个fpga可用经预验证的接口或ip核心来编程。这确保了根据给定接口标准的顺应性和兼容性。fpga的可编程性质用来为ssd、hdd和其他基于协议的存储设备的存储测试应用优化灵活性、成本、并行性和可升级性。

56.例如,实例化fpga测试器块210a可被配置为运行pcie协议,而实例化fpga测试器块210b可被配置为运行sata协议。这允许测试器硬件同时测试支持不同协议的dut。fpga 211a现在可被连接以测试支持pcie协议和sata协议两者的dut。替代地,它可被连接以测试两个不同的dut,一个dut支持pcie协议而另一个dut支持sata协议,其中每个实例化功能模块(例如210a、210b)被配置有用于测试它连接到的相应dut的协议。

57.在一个实施例中,fpga中的接口或ip核心可从第三方供应商获取,但是可能需要进行某一定制来与本文描述的实施例兼容。在一个实施例中,接口核心提供两个功能:a)将存储命令封装到标准协议中以便在物理信道上传输;以及2)是电信号生成器和接收器。

58.图2中呈现的架构的另一个主要优点是它通过将命令和测试图案生成功能分配给fpga器件来减少测试器处理器204上的处理负载,其中每个dut有运行特定于它的测试程序的专用fpga模块。例如,实例化fpga测试器块210a连接到dut 220a并运行特定于dut 220a的测试程序。这样的配置中的硬件资源是以用最小硬件共享支持个体dut的方式而设计的。这种“每dut的测试器”配置还允许针对每个处理器测试更多的dut并且允许并行测试更多的dut。此外,利用能够在某些模式下生成它们自己的命令和测试图案的fpga,也降低了将测试器处理器与其他硬件组件(包括fpga器件、器件电源(dps)和dut)连接的总线212的带宽要求。其结果是,与在现有的配置相比,可同时测试更多的dut。

59.图3根据本发明的实施例提供了站点模块及其与系统控制器和dut的互连的更详细示意框图。参考图3,在一个实施例中,ate装置的站点模块可被机械地配置在测试器切片340a

‑

340n上,其中每个测试器切片包括至少一个站点模块。在某些典型的实施例中,每个测试器切片可包括两个站点模块和两个器件电源板。例如,图3的测试器切片340a包括站点模块310a和310b以及器件电源板332a和332b。然而,可被配置到测试器切片上的器件电源板或站点模块的数量没有限制。测试器切片340通过网络交换机302连接到系统控制器301。系统控制器301和网络交换机302分别执行与图2中的元件201和202相同的功能。网络交换机302可用32位宽总线连接到站点模块中的每一者。

60.可以从站点模块310a

‑

310b之一控制每个器件电源板332a

‑

332b。在测试器处理器304上运行的软件可被配置为将器件电源分配给特定站点模块。在一个实施例中,例如,站点模块310a

‑

310b和器件电源332a

‑

332b被配置为使用高速串行协议(例如,外围组件互连快速(pcie)、串行at连接(sata)或串行连接scsi(sas))相互通信。

61.在一个实施例中,如图3所示,每个站点模块被配置有两个fpga。图3的实施例中的fpga 316和318中的每一者均由测试器处理器304控制并执行与图2中的fpga 211a

‑

211m类似的功能。测试器处理器304可使用8通道高速串行协议接口(诸如通过图3中的系统总线330和332所指示的pcie)与每个fpga进行通信。在其他实施例中,测试器处理器304还可以使用不同的高速串行协议(例如,串行at连接(sata)或串行连接scsi(sas))与fpga进行通信。

62.fpga 316和318分别连接到存储器模块308和304,其中这些存储器模块执行与图2中的存储器块240a

‑

240n类似的功能。这些存储器模块与fpga器件和测试器处理器304两者耦合并且可由fpga器件和测试器处理器304两者控制。

63.fpga 316和318可分别通过总线352和354连接到负载板380上的dut 372a

‑

372m。负载板380是下述物理器具:允许站点模块端(其不知晓用于向线路352和354上的dut通信的协议)处的通用高速连接的物理器具。然而,在dut端处,负载板需要被设计为具有特定于dut所使用的协议的连接器。

64.在本发明的一个实施例中,dut 372a

‑

372m被加载在被放置在热室390内的负载板380上以供测试。dut 372a

‑

372m和负载板380从器件电源332a和332b获得电力。

65.可连接到每个fpga的dut的数量取决于fpga中的收发器的数量以及每个dut所需

的i/o通道的数量。在一个实施例中,fpga 316和318可各自包括32个高速收发器并且总线352和354可各自是32位宽的,然而,可取决于应用实现更多的或更少的。例如,如果每个dut需要8个i/o通道,则在这样的系统中仅4个dut可连接到每个fpga。

66.图4是根据本发明的实施例的图2的实例化fpga测试器块的详细示意框图。参考图4,实例化fpga测试器块410通过pcie上游端口270连接到测试器处理器并且通过pcie下游端口480连接到dut。

67.实例化fpga块410可包括协议引擎模块430、逻辑块模块450和硬件加速器块440。硬件加速器块440可进一步地包括存储器控制模块444、比较器模块446、分组构建器模块445和算法图案生成器(apg)模块443。

68.在一个实施例中,逻辑块模块450包括:解码逻辑,用于对来自测试器处理器的命令进行解码;路由逻辑,用于将来自测试器处理器304的所有传入命令和数据以及由fpga器件生成的数据路由到适当的模块;以及仲裁逻辑,用于在实例化fpga测试器块410内的各种通信路径之间进行仲裁(arbitrate)。

69.在一个实现方式中,用于在测试器处理器与dut之间通信的通信协议可有利地是可重新配置的。这样的实现方式中的通信协议引擎被直接编程到实例化fpga测试器块410的协议引擎模块430中。因此,实例化fpga测试器块410可被配置为以dut支持的任何协议与dut进行通信。例如,可将上面提及的经预验证的接口或ip核心编程到协议引擎模块430中。这确保了根据给定接口标准的符合性和兼容性。进一步地,ip核心允许测试器实现灵活性,因为ip核心实现了基于软件的接口改变。实施例提供独立于硬件而测试多种类型的dut的能力。通过这种接口灵活性,可以将新接口加载到可编程芯片的ip核心中。

70.在一个实施例中,例如,对于存储装置/ssd/hdd,每个fpga包括下述可配置ic:其连接到ssd并且可编程以通过诸如sata或sas之类的存储专用接口来提供基于存储的图案。在一个实施例中,对于rf模块,fpga包括下述可配置的ic:其中的可配置接口核心被编程以提供使用当前rf模块的usb或pcie接口连接。

71.在一个实施例中,fpga可以是基于ssd或rf模块的测试器,其使用基于协议的通信来与dut或模块接口连接。在一个实施例中,可配置接口核心可以被编程以提供任何基于协议的标准化通信接口。例如,在一个实施例中,在基于ssd模块的测试的情况下,接口核心可以被编程以提供诸如sata、sas之类的基于协议的标准化通信接口。在一个实施例中,在基于rf模块的测试器的情况下,接口核心可以被编程以提供诸如usb、pcie之类的基于协议的标准化通信接口。在一个实施例中,在具有光学互连的模块的情况下,接口核心可以被编程以提供用于通过光学互连与模块进行通信的基于协议的标准化通信。

72.因此,从电气角度来看,fpga利用可配置的ip核心。通过对fpga的可编程芯片资源进行软件编程,给定ip核心可以被容易地重新编程并用另一ip核心替换,而无需物理地换掉fpga芯片或其他硬件组件。例如,如果给定的基于fpga的测试器当前支持sata,则仅需要将fpga重新编程以使用光纤通道ip核心而不是针对sata配置的现有ip核心,就能够连接到光纤通道dut。

73.在一个实施例中,协议可以是高速串行协议,包括但不限于sata、sas或pcie等。新的或修改的协议可以通过测试器处理器从系统控制器经由简单的位流下载而直接下载并安装在fpga上。另外,如果发布了新协议,则fpga可以经由软件下载很容易地配置有该协

议。

74.在图4中,如果耦合到pcie下游端口480的dut是pcie设备,则包含pcie协议的实例的比特文件可通过pcie上游端口470被下载并安装在协议引擎模块430上的ip核心中。每个fpga器件316或318可包括一个或多个实例化fpga测试器块,并且因此包括一个或多个协议引擎模块。任何一个fpga器件可支持的协议引擎模块的数量仅受fpga的大小和门计数的限制。

75.在本发明的一个实施例中,fpga器件内的协议引擎模块中的每一者均可被配置有不同的通信协议。因此,fpga器件可被连接以测试多个dut,每个dut同时支持不同的通信协议。替代地,fpga器件可连接到支持多种协议的单个dut并且同时测试在该器件上运行的所有模块。例如,如果fpga被配置为运行pcie协议和sata协议两者,则其可被连接以测试支持pcie协议和sata协议两者的dut。替代地,它可被连接以测试两个不同的dut,一个dut支持pcie协议而另一个dut支持sata协议。

76.图4的硬件加速器块440可用于加速(与在测试器处理器上的软件中可以实现的速度相比)fpga硬件上的某些功能。硬件加速器块440可提供在测试dut时使用的初始测试图案数据。它还可包含用于生成用于控制对dut的测试的某些命令的功能。为了生成测试图案数据,加速器块440使用算法图案生成器模块443。

77.硬件加速器块440可使用比较器模块446来将从dut读取的数据与在前一周期中被写入dut的数据进行比较。比较器模块446包括用于将失配向测试器处理器304标记的功能,以识别不符合的器件。更具体地,比较器模块446可包括跟踪失配并将它们传送到测试器处理器304的错误计数器。

78.硬件加速器块440可连接到本地存储器模块420。存储器模块420执行与存储器块240a

‑

240m中的任一者内的存储器模块类似的功能。存储器模块420可由硬件加速器块440和测试器处理器304两者控制。测试器处理器304可控制本地存储器模块420并将初始测试图案数据写入本地存储器模块420。

79.存储器模块420存储要写入dut的测试图案数据并且硬件加速器块440访问该模块以将存储的数据与在写入周期之后从dut读取的数据进行比较。本地存储器模块420还可用于记录故障。存储器模块将存储具有dut在测试期间经历的所有故障的记录的日志文件。在一个实施例中,加速器块440具有无法被任何其他实例化fpga测试器块访问的专用本地存储器模块块420。在另一实施例中,本地存储器模块块420与另一实例化fpga测试器块中的硬件加速器块共享。

80.硬件加速器块440还可包括存储器控制模块444。存储器控制模块444与存储器模块420交互并控制对存储器模块420的读取和写入访问。最后,硬件加速器块440包括分组构建器模块445。分组构建器模块由硬件加速器模块在某些模式下使用以构造要写出到dut的包括报头/命令数据和测试图案数据的分组。

81.在某些实施例中,硬件加速器块440可由测试器处理器304编程以在硬件加速的若干模式中的一种模式下进行操作。在旁路模式下,硬件加速器被旁路并且命令和测试数据由测试器处理器304通过路径472直接发送到dut。在硬件加速器图案生成器模式下,测试图案数据由apg模块443生成,而命令由测试器处理器304生成。测试分组通过路径474被发送到dut。在硬件加速器存储器模式下,从本地存储器模块420访问测试图案数据,而由测试器

处理器304生成命令。测试图案数据通过路径476被发送到dut。需要路由逻辑482以在路径472、474和476之间仲裁,以便控制数据到dut的流动。

82.站点模块可以包括通用连接器481。因为协议引擎模块430可被配置为运行任何数量的各种通信协议,所以在站点模块上需要通用高速连接器481。因此,如果需要改变在协议引擎模块430上实现的协议,则不需要在站点模块上进行附带的物理修改。站点模块使用负载板380连接到dut,该负载板380可连接到站点模块端上的通用连接器,但是该负载板380特定于在dut端上实现的协议。支持不同通信协议的dut将需要不同的配置。因此,如果协议被重新编程以适应需要不同配置的dut,则需要切换并替换负载板。

83.图5根据本发明的实施例描绘了测试dut的示例性过程的流程图500。然而,本发明不限于流程图500所提供的描述。而是,根据本文提供的教导,对于相关领域的技术人员而言显而易见的是,其他功能流程也在本发明的范围和精神内。将继续参考上面参考图2、图3和图4描述的示例性实施例来描述流程图500,但是方法不限于这些实施例。

84.现在参考图5,在块502处,用户发起设置并将测试程序加载到系统控制器中。发起设置可以包括从可用协议库中选择一种或多种协议以配置到ate装置200中的fpga器件上。这些协议被作为文件缓存在系统控制器301上并且可作为比特文件被下载到fpga上。用户可以通过图形用户界面从可用的版本列表中选择协议。在协议作为选项可用之前,必须对其进行构建、测试并集成到版本中。发布的fpga配置包含有关所支持的协议和可用于连接dut的收发器的数量的定义以及其他事项。然后,可以通过图形用户界面使版本库对用户可用。

85.在块502处,用户还通过图形用户界面将测试程序加载到系统控制器301中。测试程序定义了需要在dut上运行的测试的所有参数。在块504处,系统控制器将指令发送到站点模块310a上的测试器处理器。此步骤包括要编程到fpga上的用于协议引擎的比特文件的传输。系统控制器可以包括路由逻辑,用于将特定测试程序的指令路由到连接至测试程序所控制的dut的测试器处理器。

86.在块506处,在从系统控制器接收到指令之后,测试器处理器304可以确定用于对连接到站点模块310a的dut运行测试的硬件加速模式。

87.在一个实施例中,测试器处理器304可以在四种不同的硬件加速模式中的一个模式下进行操作。每种功能模式被配置为在测试器处理器304与fpga 316和318之间分配用于生成命令和测试数据的功能。在一个实施例中,测试器处理器可被编程以在旁路模式下进行操作,其中,用于测试dut的所有命令和测试数据都由测试器处理器304生成并且fpga 316和318被绕过。在另一实施例中,测试器处理器304可被编程以在硬件加速器图案生成器模式下进行操作,其中,由fpga 316和318生成用于测试dut的伪随机数据,并由fpga进行比较,但是测试器处理器处置命令生成。

88.在又一实施例中,测试器处理器304可被编程以在硬件加速器存储器模式下进行操作,其中,测试图案由测试器处理器在初始设置期间预先写入到连接至每个fpga 316和318的存储器模块上。在这种模式下,fpga访问专用存储器设备以取回要写入到dut的测试数据,从dut读取测试数据并将所读取的数据与在存储器设备上写入的数据进行比较。在这种模式下,fpga中的每一者响应于来自dut的读取和写入操作而控制存储器设备。然而,在这种模式下,测试器处理器仍然负责命令生成。在再一实施例中,测试器处理器304可被编

程以在硬件加速器分组构建器模式下进行操作,其中,数据和基本读取/写入/比较命令由fpga 316和318生成。

89.在块508处,测试器处理器分支到将运行测试的模式。

90.应该注意的是,图10的fpga 1002能够被编程为具有上述四种功能模式(即,旁路模式、硬件加速器图案生成器模式、硬件加速器存储器模式和硬件加速器分组构建器模式)中的任何一种。

91.图6根据本发明的实施例描绘了在旁路模式下测试dut的示例性过程的流程图600。然而,本发明不限于流程图600所提供的描述。而是,根据本文提供的教导,对于(一个或多个)相关领域的技术人员而言显而易见的是,其他功能流程也在本发明的范围和精神内。将继续参考上面参考图2、图3和图4描述的示例性实施例来描述流程图600,但是方法不限于这些实施例。

92.现在参考图6,在旁路模式下,在块602处,测试器处理器304为要路由到dut的测试分组生成命令和分组报头。在块604处,测试器处理器还为要路由到dut的分组生成测试图案数据。在这种模式下,因为测试器处理器生成它自己的命令和测试数据,所以没有硬件加速。

93.在块606处,测试器处理器与实例化fpga块410和下游端口480进行通信以将包含测试图案数据的测试分组路由到dut。旁路模式是传递模式,其中,除了一些有限的异常情况以外,命令和数据透明地通过实例化fpga块410直接传递到dut。在旁路模式下,测试器处理器304直接控制dut。虽然实例化fpga块可包括用于将分组路由到下游端口的逻辑,但是它不参与命令生成(也称为“信号告知(signaling)”)或数据生成。

94.在块608处,测试器处理器304与下游端口480进行通信以发起从dut对先前在块606处被写入dut的数据的读取操作。在块610处,测试器处理器将从dut读取的数据与在块606处写入的数据进行比较。如果在块606处写入的数据与在块610处读取的数据之间存在任何失配,则在块612处,由测试器处理器304向系统控制器301发送标志。系统控制器然后将向用户标记失配。

95.在旁路模式下,测试器处理器304在其可以支持的dut的数量方面受到限制,这是因为可以由于生成用于dut的所有命令和测试数据而快速地使测试器处理器304的处理能力增加到最大限度(maximized)。此外,站点模块310a可以支持的dut的数量还受到系统总线330和332上的带宽约束的限制。在旁路模式下,因为测试器处理器304通过总线330和332向dut发送大量数据,所以总线330和332的带宽相对较快地被耗尽。因此,提供了具有更多硬件加速的其他模式,其中,fpga器件具有用于生成测试数据和命令的更多功能。

96.图7根据本发明的实施例描绘了在硬件加速器图案生成器模式下测试dut的示例性过程的流程图700。然而,本发明不限于流程图700所提供的描述。而是,根据本文提供的教导,对于(一个或多个)相关领域的技术人员而言显而易见的是,其他功能流程也在本发明的范围和精神内。

97.将继续参考上面参考图2、图3和图4描述的示例性实施例来描述流程图700,但是方法不限于这些实施例。现在参考图7,示出了硬件加速的方法,其中,fpga器件共享数据生成功能以便减轻测试器处理器304上的处理负载以及系统总线330和332上的数据负载。在硬件加速器图案生成器模式的块702处,测试器处理器304为要路由到dut的分组生成命令

和分组报头。在这种模式下,测试器处理器保留信号告知的功能。在块704处,硬件加速器块440内的算法图案生成器模块443生成要写入到dut的伪随机测试数据。逻辑块模块450包括用于路由所生成的数据并将其添加到要写出到dut的分组的功能。

98.该模式被认为是“硬件加速的”,因为可通过fpga器件的算法图案生成器在硬件中更快地(与通过测试器处理器在软件中生成数据相比)完成用于生成数据的功能。另外,“每dut的测试器”架构允许dut直接连接到其自己的专用的实例化fpga测试器块,从而为dut生成测试图案数据,如图4所示,这相比测试器处理器304通过系统总线330和332将所有命令和数据提供给dut的旁路模式实现带宽显著增加。在fpga器件共享数据生成功能的情况下,系统总线330和332被释放,使得可以比在旁路模式下更快的速率将命令传送到fpga。进一步地,对于诸如需要多次测试迭代的固态驱动器之类的设备,具有通过实例化fpga测试器块的专用数据路径比其中测试器处理器的资源被多个dut共享的数据路径大大加速了测试。它还允许dut以接近全性能操作,因为它不必等待测试器处理器为其分配处理资源。

99.在一个实施例中,算法图案生成器模块443可被编程以及时(on the fly)生成数据。apg模块可生成增量图案、伪随机图案或某种类型的恒定图案。apg模块还可具有一定的选通(gating)能力以生成具有条带、对角条带或交替图案的测试图案。在一个实施例中,apg模块可使用有限状态机、计数器或线性反馈移位寄存器等来生成测试图案。在一些实现方式中,可以给apg模块提供起始种子以作为生成更复杂的图案的初始值。

100.在步骤706处,实例化fpga块410与下游端口480进行通信以根据由测试器处理器生成的命令和分组报头将测试图案数据路由到dut。在步骤708处,实例化fpga块410与下游端口进行通信以根据由测试器处理器生成的命令从dut读取测试图案数据。在块710处,硬件加速器块440的比较器模块446然后用于将所读取的数据与写入到dut的数据进行比较。apg模块443被设计为使得比较器模块能够利用用于生成伪随机数据的相同参数,来对apg模块443执行读取操作并且接收在块704处被写入到dut的相同数据。apg模块443及时重新生成被写入到dut的数据并将其传送到比较器模块446。在块712处,任何失配由存储器控制模块444记录在存储器模块420上或者由实例化fpga块传送到测试器处理器。在接收到错误日志之后,在块714处,测试器处理器随后向系统控制器标记失配。

101.图8根据本发明的实施例描绘了在硬件加速器存储器模式下测试dut的示例性过程的流程图800。然而,本发明不限于流程图800所提供的描述。而是,根据本文提供的教导,对于(一个或多个)相关领域的技术人员而言显而易见的是,其他功能流程也在本发明的范围和精神内。

102.将继续参考上面参考图2、图3和图4描述的示例性实施例来描述流程图800,但是方法不限于这些实施例。

103.现在参考图8,示出了硬件加速的方法,其中,fpga器件共享数据生成功能以便减轻测试器处理器304上的处理负载以及系统总线330和332上的数据负载。对比硬件加速器图案生成器模式,在硬件加速器存储器模式下,实例化fpga测试器块访问本地存储器模块420以获取要写入到dut的数据,而不使用apg模块443来得到。

104.在硬件加速器图案存储器模式的块800处,测试器处理器304为要路由到dut的分组生成命令和分组报头。测试器处理器保留用于在这种模式下信号告知的功能。在块802处,测试器处理器用要写出到dut的测试图案来初始化实例化fpga测试器块410的本地存储

器模块420。硬件加速器存储器模式的一个优点是与由apg模块443在硬件加速器图案生成器模式下生成的伪随机数据相反,由测试器处理器生成的测试图案可以构成真实随机数据。测试器处理器和实例化fpga测试器块都具有对本地存储器模块420的读取和写入访问。然而,测试器处理器仅在初始设置期间访问存储器模块420。在加速器模式期间,测试器处理器不访问存储器模块,因为测试器处理器304上的附加处理负载以及系统总线330和332上的附加数据负载显著减慢了加速。

105.在块804处,实例化fpga测试器块从存储器模块420读取要路由到dut的测试图案数据。因为存储器模块420专用于fpga测试器块或者与仅一个其他fpga测试器块共享,所以在这两者之间存在产生快速读取操作的高带宽连接。逻辑块模块450包括用于路由所生成的数据并将它添加到要写出到dut的分组的功能。

106.在将数据添加到分组之后,在块806处,实例化fpga测试器块与下游端口480进行通信以根据由测试器处理器生成的命令和分组报头将测试图案数据路由到dut。在块808处,实例化fpga块410与下游端口进行通信以根据由测试器处理器生成的命令从dut读取测试图案数据。在块810处,硬件加速器块440的比较器模块446然后用于将所读取的数据与写入到dut的数据进行比较。在块812处,任何失配被记录在存储器模块420上或者由实例化fpga块传送到测试器处理器。在接收到错误日志之后,在块814处,测试器处理器随后向系统控制器标记失配。

107.图9根据本发明的实施例描绘了在硬件加速器分组构建器模式下测试dut的示例性过程的流程图900。然而,本发明不限于通过流程图900提供的描述。而是,根据本文提供的教导,对于(一个或多个)相关领域的技术人员而言显而易见的是,其他功能流程也在本发明的范围和精神内。

108.将继续参考上面参考图2、图3和图4描述的示例性实施例来描述流程图900,但是方法不限于那些实施例。

109.现在参考图9,示出了硬件加速的方法,其中,fpga器件共享数据及命令生成功能以便减轻测试器处理器304上的处理负载以及系统总线330和332上的数据负载。这种模式也被称为“全加速”模式,这是因为用于运行器件测试的大多数控制被转移到fpga器件并且测试器处理器304仅保留用于对除读取和写入及比较以外的命令的控制。

110.在硬件加速器分组构建器模式的块902处,测试器处理器304生成要传送到实例化fpga块410以生成它自己的分组的命令。测试器处理器在这种模式下仅保留用于非读取/写入/比较命令的功能。针对诸如读取、写入和比较操作之类的命令的功能被输送到实例化fpga块。在块904处,实例化fpga测试器块的分组构建器模块445构建要传送到dut的具有报头和命令信息的分组。这些分组至少包括命令类型、器件的块地址和测试图案数据。

111.在块906处,硬件加速器块440内的算法图案生成器模块443生成要写入到dut的伪随机测试数据。逻辑块模块450包括用于路由由实例化fpga块生成的数据和命令并将它们合并到要写出到dut的分组中的功能。

112.在块908处,实例化fpga测试器块与下游端口480进行通信以将测试图案数据路由到dut。在步骤910处,实例化fpga块410与下游端口进行通信以从dut读取测试图案数据。在块912处,硬件加速器块440的比较器模块446然后用于将所读取的数据与写入到dut的数据进行比较。在块914处,任何失配被记录在存储器模块420上或者由实例化fpga块传送到测

试器处理器。测试器处理器在接收到错误日志之后随后在916处向系统控制器标记失配。

113.使用主机总线适配器以在自动化测试设备中提供协议灵活性

114.如上所述,可以通过从系统控制器上的缓存中进行简单的位流下载,来将用于与dut通信的新协议直接下载并安装在测试器系统的fpga上。fpga中的可配置接口核心(或ip核心)可以被编程以提供用于与dut通信的一个或多个基于协议的接口的功能。每个fpga实现定制固件和软件映像以在单个芯片中实现一个或多个基于pc的测试器的功能。所需要的电气信令和基于协议的信令由fpga中的片上ip核心提供。每个fpga可用经预验证的接口或ip核心来编程。这确保了根据给定接口标准的符合性和兼容性。

115.应该注意的是,尽管在某些情况下,可以将多种不同类型的内核编程到fpga上,但是某些常规测试器仅允许将单个ip核心编程到fpga上。换句话说,某些测试系统的fpga协议引擎模块(例如,图4的模块430)仅能够支持单个ip核心,并且如果需要将不同的第三方协议ip核心编程到fpga中,则将需要对fpga进行重新编程。此外,ip核心可能包括可能为专有的且是不能被篡改或复制的第三方ip协议。这会导致开发和测试环境两者中的延迟。对fpga进行重新编程有时可能会耗费大量时间,从而减缓了开发或测试过程的速度。

116.因此,在一些实施例中,具有可配置ip核心的fpga与主机总线适配器(hba)结合使用,以便加速开发或测试环境中的测试。使用hba将来自fpga的流量转换为特定于dut的协议,而非将新的位流下载到fpga中以对其进行重新编程。例如,fpga初始可以被编程以使用pcie协议进行通信。hba可以被配置为将传入的pcie信号转换为sata或sas信号,以便分别对sata或sas dut进行测试。替代地,hba可以被配置为将传入的pcie信号转换为只能通过hba“落入(dropped in)”到测试器系统中的某一第三方专有协议。

117.图10根据本发明实施例示出了这样的一种方式,其中,包括协议转换器ip的hba可被用于将fpga连接到以与fpga被编程有的协议不同的协议进行通信的dut。本发明的实施例调用对包括协议转换器ip 1004(例如,包括专有第三方协议)的hba 1008的使用以提供协议灵活性。协议转换器ip 1004将输入到输入hba接口1040的传入流量从一个协议转换为在hba输出接口1042上输出的不同协议。

118.在一个实施例中,具有协议转换器ip 1004的hba 1008与fpga1002上的硬件加速器和ip核心1010结合使用,以测试支持不同协议的dut。在一个实现方式中,硬件加速器(例如,图4的硬件加速器块440)可以是ip核心1010的一部分,但是在不同的实现方式中,硬件加速器可以是与ip核心1010分离的分立模块。

119.在图10的实施例中,使用hba将来自fpga的流量转换为dut所支持的协议,而非利用与耦合的dut匹配的协议对fpga进行重新编程。在某些测试环境中,这是必要的,因为对fpga进行重新编程需要时间。此外,在开发环境中可能存在一些情况,例如,fpga可能不支持特定协议。使用hba避免了与对fpga进行重新编程或为当前不支持的协议开发fpga固件相关联的延迟。此外,配置在fpga内的ip核心可能是某些第三方专有的,而使用hba避免了需要篡改来自第三方的专有核心。例如,第三方专有协议ip可能不允许到fpga中进行的集成,并且可能需要作为hba的一部分的孤立使用。

120.此外,随着测试器系统的上市时间越来越短,存在对下述灵活的测试器系统的需要:该系统允许测试工程师在支持不同协议的dut之间快速切换而无需对fpga进行重新配置。图10的实施例提供了下述测试器系统:该测试器系统将fpga ip核心和硬件加速器与

hba(例如,具有第三方ip协议)相结合,以在测试支持各种协议的dut之间灵活地切换。在一个实施例中,fpga 1002可通过输入接口1001从系统控制器(例如,图3的系统控制器301)或测试器处理器(例如,图3的测试器处理器304)接收输入信号。输入接口1001可以例如包括诸如pcie之类的高速串行协议接口。在fpga上实现的硬件加速器和ip核心1010可以被配置为利用特定协议(例如pcie)进行通信。因此,fpga 1002可以连接到pcie dut,但是其将不能与支持任何其他协议的dut通信。

121.在一个实施例中,在测试或开发环境中,如果需要测试支持除pcie之外的协议的dut,则可以使用具有协议转换器ip 1004(例如,带有第三方专有协议)的hba 1008利用相同的测试器来测试dut,而非对fpga进行重新编程。在一个实现方式中,hba 1008包括协议转换器1004(或第三方ip),该协议转换器1004用作协议转换器并将流量从一种协议转换为另一种协议。因此,hba 1008将接口1040上的传入信号(例如,pcie信号)转换为dut所支持的不同协议。以此方式,到dut1055的hba协议接口1042将支持与dut 1055相对应的协议。

122.本发明的实施例有利地允许fpga 1002快速使用第三方ip来实现其他协议,而无需对fpga进行重新编程。本发明的实施例还为测试器系统提供了更好的上市时间。通过允许协议ip核心能够互换,有利于为测试器系统客户加快上市时间。

123.在一个实施例中,可以将测试器系统运送到支持特定协议(例如,pcie)的测试器系统的客户端。在客户端站点处,客户端只需将hba添加到具有支持不同协议(例如,sata或一些其他专有协议)的第三方ip(或协议转换器ip)的测试器系统,而非在测试器中对fpga进行重新编程。以这种方式,客户端能够测试与不同协议相关联的dut,而无需对测试器系统进行重新配置。

124.在一个实施例中,hba 1008可以是具有交换机的总线扩展器。在一个实现方式中,到hba 1008的输入(通过接口1040)可以是pcie信号,并且输出包括sas信号。例如,通过接口1040输入到协议转换器ip块1004的pcie可以被转换成在接口1042上的不同的协议,例如用于测试sas dut 1055的sas。

125.在一个实现方式中,hba 1008与fpga的加速器引擎(例如,图4的硬件加速器块440)结合,以比通过将hba与处理器结合所支持的吞吐量更快的吞吐量来创建针对协议的流量。例如,在图1中,测试器处理器101与硬件总线适配器插槽110a结合使用。图1的测试器系统是低效的,因为hba被限制为以测试器处理器101产生数据的较慢速度接收和发送数据。

126.相比之下,在图10的实施例中,hba与fpga硬件加速器块440结合使用,以便为未在fpga上实现或无法在fpga上实现(例如,由于第三方的专有限制)的协议提供高速支持。在一个实现方式中,hba能够跟上fpga硬件加速器块440所支持的高速数据生成和发送速率。fpga能够驱动hba以与硬件加速器块440生成数据的速度一样快的速度接收和发送数据。因此,在数据事务期间,无论是测试器处理器(例如,图3的测试器处理器304)还是hba都不会成为瓶颈。

127.请注意,fpga可以布置在站点模块板1060上(类似于图3的站点模块310a),而dut 1055可以布置在设备接口板1064上(类似于图3的负载板380)。hba 1008可以布置在与站点模块板1060和设备接口板1064两者耦合的夹心板1062上。在一个实施例中,hba 1008可以位于站点模块板1060和设备接口板1064之间。

128.图11根据本发明实施例示出了包括一个或多个hba的夹心板可用于在fpga和dut之间接口连接的方式。如前所述,fpga 1104可以通信地耦合到测试器处理器1102,其中fpga 1104可以从测试器处理器1102接收用于测试一个或多个dut 1110的指令。fpga 1104和测试器处理器1102可以布置在站点模块板1102上。

129.fpga将测试信号(例如,pcie信号)发送到布置在夹心板1107上的一个或多个hba 1106,在该夹心板1107上,每个hba包括协议转换器ip。请注意,布置在夹心板上的hba的数量取决于所选的hba的类型。此外,连接到每个hba的dut 1110的数量也取决于所选择的hba。

130.在图11所示的实现方式中,每个hba内的协议转换器ip可以将来自fpga的pcie信号转换为另一协议(例如sas信号)以测试dut 1110。这允许测试器在无需对fpga进行重新编程的情况下通过直接使用未集成在fpga内的第三方协议来测试配置有不同协议的dut。应注意,fpga可以被配置为实现若干协议中的任何一种,并且不限于pcie。类似地,hba可以被配置具有用于任何数量协议的协议转换器ip,并且不限于sas。

131.在一个实施例中,每个dut被连接到相关联的fpga内的单个加速引擎(或硬件加速器块)。如结合图2所述的,每个fpga可以具有多个实例化fpga测试器块,其中每个块都包括自己的加速器引擎。在一个实现方式中,每个加速器引擎可以与其自己的相应dut耦合。在一个实现方式中,每个hba可以与n个实例化fpga测试器块耦合。因为每个实例化fpga测试器块都包括其自己的加速器引擎,所以每个hba都可以与n个加速器引擎耦合。

132.在一个实现方式中,每个hba还可以与n个dut连接,其中每个加速器引擎可以与其自己的相应dut连接。在一个实现方式中,n=4,并且每个hba可以连接到4个实例化fpga测试器块和4个dut,其中每个dut将与它自己的加速器核心相关联。然而,应当注意,本发明的实施例不限于此。每个加速器引擎可以与多于一个dut连接,并且每个hba可以与任何数量的dut连接。

133.图12根据本发明实施例示出了每个dut与相应的加速器引擎连接的示例性测试器配置。如图12所示,fpga包括多个加速器核心,例如1201、1202、1203和1204。如上所讨论,每个加速器核心可以在图案生成器模式(apg模式)或全加速器模式(fa模式)下进行操作。每个加速器核心与ip核心1205通信。加速器核心1201

‑

1204和ip核心1205共同执行与图10中的模块1010基本相同的功能。在图12所示的示例中,ip核心1205是pcie核心,因此,fpga实施pcie协议。

134.来自fpga的pcie信号被发送到夹心板1215。hba 1206可以是布置在夹心板1215上的若干hba之一。在此示例中,hba 1206接收pcie信号并将其转换为符合sas协议的信号。在一个实现方式中,可以将sas协议作为专有第三方协议ip来提供,可以将其丢弃到设计中而无需对其进行更改或检查。hba 1206与4个dut通信地耦合,其中每个dut对应于相应的加速器核心。例如,dut 1207可以对应于加速器核心1201,dut 1208可以对应于加速器核心1202,dut 1209可以对应于加速器核心1203,并且dut 1210可以对应于加速器核心1204。

135.图13根据本发明的实施例描绘了下述示例性过程的流程图1300:对以与在测试器系统中的fpga上实现(集成在fpga中)的协议不同的协议进行通信的dut进行测试。然而,本发明不限于流程图1300所提供的描述。而是,根据本文提供的教导,对于(一个或多个)相关领域的技术人员而言显而易见的,其他功能流程也在本发明的范围和精神内。

136.在块1310处,将系统控制器耦合到测试器处理器和fpga。系统控制器可以是如上所述的基于windows的操作系统。fpga通信地耦合到测试器处理器,并且fpga可操作来根据上述各种加速模式之一生成用于测试多个dut的命令和数据。

137.在块1312处,根据在fpga的ip核心中实现的第一协议并根据所选加速模式来生成命令和数据以测试多个dut。加速模式可以是标准模式或旁路模式,在该模式中,测试器处理器生成所有命令和数据,而fpga被绕过。替代地,加速模式可以是如上所述的pida、fa、或硬件加速器存储器模式。

138.在块1314处,通过hba将与使用第一协议传送的命令和数据相关联的信号转换为包括以第二协议传送的命令和数据的信号。在一个实施例中,hba包括协议转换器ip块1004,该协议转换器ip块1004把使用第一协议传送的命令和数据信号转换为第二协议。换句话说,使用hba内的第三方协议ip来替换编程到fpga中的协议。请注意,如上所述,hba被通信地耦合到可操作来使用第二协议进行通信的dut。

139.在块1316处,将与第二协议相关联的信号转发到dut,以进行测试。

140.出于说明的目的,已参考具体实施例描述了前面的描述。然而,以上说明性讨论不旨在是详尽无遗的或者将本发明限于所公开的精确形式。许多修改和变化鉴于以上教导是可能的。选择和描述这些实施例以便最好地阐明本发明的原理及其实际应用,从而使本领域的其他技术人员能够最好地利用本发明以及具有如可以适于设想的特定用途的各种修改的各种实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1