一种应用于非制冷红外焦平面读出电路的时序保护电路的制作方法

1.本发明属于微电子和光电子技术领域,具体涉及一种应用于非制冷红外焦平面读出电路的时序保护电路的设计。

背景技术:

2.本部分旨在为权利要求书中陈述的本发明的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是现有技术。

3.目前,非制冷红外成像技术在军事、工农业、医学、天文等领域有着重要应用。作为非制冷红外成像技术核心的红外焦平面阵列,包括红外探测器阵列和读出电路两个部分。其中,红外探测器阵列的基本组成单元是热敏像元。热敏像元在接受到目标红外辐射后,其自身的等效电阻会发生改变,等效阻值的改变量与接受到的红外辐射能量相关。读出电路的作用是将热敏像元接受到的红外辐射能量进行处理转换成电信号,并按照一定规律输出。

4.随着红外焦平面探测器技术的发展,用户的要求也越来越高,热敏像元的阵列规模不断扩大,同时,热敏像元的尺寸也在不断减小。为保证像元阵列能够正常工作,对读出电路中数字电路产生的关键时序信号进行检测,在保护热敏像元不被损坏的同时,也能确保后续模拟电路的正常工作。

技术实现要素:

5.在下文中给出了关于本发明的简要概述,以便提供关于本发明的某些方面的基本理解。应当理解,这个概述并不是关于本发明的穷举性概述。它并不是意图确定本发明的关键或重要部分,也不是意图限定本发明的范围。其目的仅仅是以简化的形式给出某些概念,以此作为稍后论述的更详细描述的前序。

6.本发明的目的是提出一种应用于非制冷红外焦平面读出电路的时序保护电路,当关键时序信号(如时钟信号、行选通信号等)出现异常时,进入保护状态,使所有数字电路复位,避免热敏像元被损坏,确保后续模拟电路正常工作。

7.本发明的提供了一种应用于非制冷红外焦平面读出电路的时序保护电路,其特征在于该电路包括:关键时序信号产生电路,所述关键时序信号产生电路用于产生主时钟信号(mclk)、行选通信息号的时钟信号(rowclk)及行选通信号(row_sel《0》)至(row_sel《n》);关键时序信号检测电路,所述关键时序信号检测电路用于检测关键时序信号产生电路所产生的关键时序信号;相关逻辑电路,所述逻辑电路用于对所述关键时序信号检测电路产生的结果进行运算以及输出该检测结果。

8.一个实施例为,所述关键时序信号检测电路包括:参考电压产生电路,所述参考电压产生电路用于产生比较器的参考电压(vref_comp);充电通路,所述充电通路用于对电路中的电容进行充电;控制开关,所述控制开关用于控制是否导通所述充电通路,包括控制开关(tg1)和(tg2);比较器电路,所述比较器电路用于比较输入电压与所述参考电压(vref_

comp)的大小。

9.另一个实施例为,所述参考电压(vref_comp)通过电阻(r3)和电阻(r4)在输入电压(vin)和地之间进行分压产生。

10.再一个实施例为,所述充电通路由电阻(r1)和电容(c1)以及电阻(r2)和电容(c2)组成。

11.又一个实施例为,所述控制开关可以为nmos开关、pmos开关或者cmos传输门中的一种或其组合。

12.又一个实施例为,所述比较器电路包括比较器(comp1)和比较器(comp2)。

13.又一个实施例为,所述关键时序信号检测电路还包括二输入或非门(nor2);所述控制开关(tg1)的一端连接所述电阻(r1),所述电阻(r1)的另一端连接所述输入电压(vin),所述控制开关(tg1)的另一端连接所述电容(c1)的一端和所述比较器(comp1)的正输入端,所述电容(c1)的另一端接地,所述比较器(comp1)的负输入端接所述参考电压(vref_comp),所述比较器(comp1)的输出接所述二输入或非门(nor2)的输入端(ina);所述控制开关(tg2)的一端连接所述电阻(r2),所述电阻(r2)的另一端连接所述输入电压(vin),所述控制开关(tg2)的另一端连接所述电容(c2)的一端和所述比较器(comp2)的正输入端,所述电容(c2)的另一端接地,所述比较器(comp2)的负输入端接所述参考电压(vref_comp),所述比较器(comp2)的输出接所述二输入或非门nor2的输入端(inb)。

14.又一个实施例为,所述控制门开关(tg1)由关键时序信号(clk)控制是否导通,当关键时序信号的高电平到来时,控制开关(tg1)导通;所述控制门开关(tg2)由关键时序信号(clk)经过反相器(inv)产生的信号控制是否导通,当关键时序信号的低电平到来时,控制开关(tg2)导通。

15.又一个实施例为,当所述控制开关(tg1)导通时,所述输入电压(vin)经过所述电阻(r1)给所述电容(c1)充电,当所述比较器(comp1)的正输入端电压逐渐增大高于所述参考电压(vref_comp)时,所述二输入或非门or2的输入端(ina)由低电平转换为高电平;当所述控制开关(tg2)导通时,所述输入电压(vin)经过所述电阻(r2)给所述电容(c2)充电,当所述比较器(comp2)的正输入端电压逐渐增大高于参考电压(vref_comp)时,所述二输入或非门or2的输入端(inb)由低电平转换为高电平。

16.又一个实施例为,所述相关逻辑电路包括四输入与门、缓冲器(buffe);所述四输入与门的输入端连接所述时序信号检测电路,用于接收所述关键时序信号检测电路产生的检测结果;所述四输入与门的输出端连接缓所述冲器(buffer)的输入端,所述缓冲器(buffer)的输出端为保护电路的输出信号(rstb_pro)。

17.又一个实施例为,当所述四输入与门的至少一个输入端任何一端为低电平信号时,所述保护电路的输出信号(rstb_pro)为低电平,所有数字电路进入复位状态。

18.本技术所述的技术方案通过采用关键时序信号检测电路对各个时序信号进行监测,可以对读出电路中数字电路产生的关键时序信号进行检测,在保护热敏像元不被损坏的同时,也能确保后续模拟电路的正常工作。

附图说明

19.通过参考附图阅读下文的详细描述,本发明示例性实施方式的上述以及其他目

的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本发明的若干实施方式,其中:

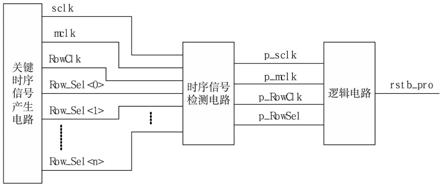

20.图1示意性地示出了根据本发明实施方式的应用于非制冷红外焦平面读出电路的时序保护电路;

21.图2示意性地示出了根据本发明另一实施例的关键时序信号示意图;

22.图3示意性地示出了根据本发明又一实施例的关键时序信号检测电路示意图;

23.图4示意性地示出了根据本发明再一实施例的相关逻辑电路示意图。

24.在附图中,相同或对应的标号表示相同或对应的部分。

具体实施方式

25.在下文中将结合附图对本发明的示范性实施例进行描述。为了清楚和简明起见,在说明书中并未描述实际实施方式的所有特征。然而,应该了解,在开发任何这种实际实施例的过程中必须做出很多特定于实施方式的决定,以便实现开发人员的具体目标,例如,符合与系统及业务相关的那些限制条件,并且这些限制条件可能会随着实施方式的不同而有所改变。此外,还应该了解,虽然开发工作有可能是非常复杂和费时的,但对得益于本公开内容的本领域技术人员来说,这种开发工作仅仅是例行的任务。

26.在此,还需要说明的一点是,为了避免因不必要的细节而模糊了本发明,在附图中仅仅示出了与根据本发明的方案密切相关的设备结构和/或处理步骤,而省略了与本发明关系不大的其他细节。

27.下面参考本发明的若干代表性实施方式,详细阐释本发明的原理和精神。

28.本发明的一个方面是提供一种应用于非制冷红外焦平面读出电路的时序保护电路,包括关键时序信号产生电路、关键时序信号检测电路、相关逻辑电路。关键时序信号产生电路,所述关键时序信号产生电路用于产生主时钟信号sclk和mclk、行选通信号的时钟信号rowclk及行选通信号row_sel《0》~row_sel《n》;关键时序信号检测电路,所述关键时序信号检测电路用于检测关键时序信号产生电路所产生的关键时序信号;逻辑电路,所述逻辑电路用于检测电路的结果的运算及输出。

29.以下结合附图对本发明的实施例进行详细说明。

30.图1是应用于非制冷红外焦平面读出电路的时序保护电路的结构示意图。主要包含三个部分,第一部分是关键时序信号产生电路,所述关键时序信号产生电路用于产生主时钟信号mclk、行选通信息号的时钟信号rowclk及行选通信号row_sel《0》至row_sel《n》;第二部分是关键时序信号检测电路,所述关键时序信号检测电路用于检测关键时序信号产生电路所产生的关键时序信号;第三部分是相关逻辑电路,所述逻辑电路用于对所述关键时序信号检测电路产生的结果进行运算以及输出该检测结果。

31.其中,如图2-3所示,所述关键时序信号检测电路包括:参考电压产生电路,所述参考电压产生电路用于产生比较器的参考电压vref_comp,参考电压是通过将电阻r3一端接输入电压vin,电阻r3的另一端接电阻r4的一端,电阻r4的另一端接地,参考电压vref_comp从电阻r3和r4的公共连接处引出,以使得参考电压由电阻r3和r4分压产生,具体由由电阻r1和电容c1以及电阻r2和电容c2组成;充电通路,所述充电通路用于对电路中的电容进行充电;控制开关,所述控制开关用于控制是否导通所述充电通路,包括控制开关tg1和tg2;

比较器电路,所述比较器电路用于比较输入电压与所述参考电压vref_comp的大小。

32.更具体地,控制开关tg1由关键时序信号clk控制是否导通,传控制开关tg1的一端连接电阻r1,电阻r1的另一端连接输入电压vin,传输门开关tg1的另一端连接电容c1的一端和比较器comp1的正输入端,电容c1的另一端接地,比较器comp1的负输入端接电压vref_comp,比较器comp1的输出接二输入或非门nor2的输入端ina。当关键时序信号的高电平到来时,控制开关tg1导通,输入电压vin经过电阻r1给电容c1充电,使比较器comp1的正输入端电压逐渐增大高于其负输入端电压vref_comp时,比较器comp1的输出(二输入或非门or2的输入端ina)由低电平转换为高电平,二输入或非门or2的输出端p_clk由高电平转换为低电平。控制开关tg2由关键时序信号clk经过反相器inv产生的信号控制是否导通,传输门开关tg2的一端连接电阻r2,电阻r2的另一端连接输入电压vin,传输门开关tg2的另一端连接电容c2的一端和比较器comp2的正输入端,电容c2的另一端接地,比较器comp2的负输入端接电压vref_comp,比较器comp2的输出接二输入或非门nor2的输入端inb。当关键时序信号的低电平到来时,传输门开关tg2导通,输入电压vin经过电阻r2给电容c2充电,使比较器comp2的正输入端电压逐渐增大高于其负输入端电压vref_comp时,比较器comp2的输出(二输入或非门or2的输入端inb)由低电平转换为高电平,二输入或非门or2的输出端p_clk由高电平转换为低电平。

33.如图4所示为相关逻辑电路示意图。四输入与门的输入端ina接关键时序信号sclk的检测结果p_sclk,输入端inb接关键时序信号mclk的检测结果p_mclk,输入端inc接关键时序信号rowclk的检测结果p_rowclk,输入端ind接关键时序信号rowsel的检测结果p_rowsel,其中在关键时序信号row_sel《0》~row_sel《n》之间安装有n端输入与门,该n端输入与门可以将row_sel《0》~row_sel《n》中输出的n个检测结果整合为一个检测结果p_rowsel。四输入与门的输出端接缓冲器buffer的输入端,缓冲器buffer的输出端为保护电路的输出信号rstb_pro。当四输入与门的四个输入端任何一端为低电平信号时,保护电路的输出信号rstb_pro为低电平,即,此时的电路状态异常,所有数字电路进入复位状态,从而保护热敏像元不被损坏,确保后端模拟电路正常工作。

34.具体地例子,如图2所示,由于不同的时序信号的电路图呈不认同规律周期性变化,因此,针对不同的时序信号在关键时序信号检测电路中的参考电压vref_comp可以不同,该参考电压具体可根据不同时序电路的周期进行改变。例如,以时序电路sclk为例,假设输入电压为5v,若该电路的变化周期为1s,也即该电路具有0.5s的高电压(1v)以及0.5s的低电压(0v),当输入到关键时序信号检测电路中的为高电压时,控制开关td1打开,为电容c1充电,若在比较器comp1的输入端输入的电压超过了参考电压vref_comp时(此时参考电压可设置为1.2v),则当比较器comp1的输入端的输入电压超过1.1v时,则比较器comp1的输出(二输入或非门or2的输入端ina)由低电平转换为高电平,二输入或非门or2的输出端p_clk由高电平转换为低电平,则输入到逻辑电路中的检测结果p_sclk为低电平,而经过与门之后保护电路的输出信号rstb_pro为低电平,所有数字电路进入复位状态。可见,由于若sclk的输出信号为按照正常周期输出时(即输出1v的电压持续0.5s),是不会出现比较器的输入端的电压大一参考电压这种情况的,如若出现这种情况,则可以证明sclk的输出信号出现了故障,如持续输出1v电压超过了0.5s。

35.以上通过具体的实施例对本发明进行了说明,但本发明并不限于这些具体的实施

例。本领域技术人员应该明白,还可以对本发明做各种修改、等同替换、变化等等,这些变换只要未背离本发明的精神,都应在本发明的保护范围之内。并且,在本发明的结构中,各部件是可以分解和/或重新组合的,这些分解和/或重新组合应该视为本发明的等效方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1