阻抗校准方法及系统与流程

1.本发明涉及阻抗校准技术领域,尤其涉及一种阻抗校准方法及系统。

背景技术:

2.由于高速信号在传输过程中存在反射,高速tx电路输出阻抗必须与外部传输线特征阻抗进行匹配。当传输线特征阻抗为50ohm时,高速tx电路输出阻抗也需要做到50ohm附近,以降低反射,提高信号质量。高速tx电路输出阻抗一般由mosfet和电阻构成,在芯片制作过程中,由于工艺误差的存在,该输出阻抗会发生偏差。mosfet的阻抗还会受到电源电压的影响,因此,芯片制作完成后由于电源电压和工艺的偏差会使得该输出阻抗会偏离50ohm,需要校准电路进行对其校准,将其校准到50ohm附近。

3.因此,有必要提供一种新型的阻抗校准方法及系统以解决现有技术中存在的上述问题。

技术实现要素:

4.本发明的目的在于提供一种阻抗校准方法及系统,有效提高了阻抗校准的精确度。

5.为实现上述目的,本发明的所述一种阻抗校准方法,用于对高速发射电路进行阻抗校准,所述方法包括:

6.提供阻抗校准电路,所述阻抗校准电路包括第一阻抗调节单元、第一电阻单元、第一开关单元、第二电阻单元、第三电阻单元、第二阻抗调节单元、第二开关单元、比较器单元和第十三电阻,所述第一阻抗调节单元、所述第一电阻单元、所述第十三电阻的一端和所述比较器单元的负向输入端均与所述第一开关单元连接,所述第十三电阻的另一端接工作电压,所述第二电阻单元、所述第三电阻单元、所述第二阻抗调节单元和所述比较器单元的正向输入端均与所述第二开关单元连接;

7.调节所述第一开关单元,以使所述第一电阻单元与所述比较器单元的负向输入端连通,调节所述第二开关单元,以使所述第二阻抗调节单元、第三电阻单元与所述比较器单元的正向输入端连通,并使所述第二电阻单元与所述比较器单元的正向输入端断开连接,调节所述第一阻抗调节单元的控制参数,以将所述第一阻抗调节单元的阻抗调节到最小阻抗,调节所述第一电阻单元的电阻和所述第三电阻单元的电阻,以将所述第一电阻单元的电阻和所述第三电阻单元的电阻均调节至最大电阻;

8.调节所述第二阻抗调节单元的控制参数,以调节所述第二阻抗调节单元的阻抗,直至所述比较器单元输出校准完成信号,将所述第二阻抗调节单元的控制参数作为第二调节控制参数;

9.调节所述第一开关单元,以使得所述第一阻抗调节单元与所述比较器单元的负向输入端连通,调节所述第二开关单元,以使得所述第二阻抗调节单元、所述第三电阻单元与所述比较器单元的正向输入端断开连接,并使得所述第二电阻单元与所述比较器单元的正

向输入端连通,调节所述第二阻抗调节单元的控制参数,以将所述第二阻抗调节单元的阻抗调节至最大阻抗;

10.调节所述第一阻抗调节单元的控制参数,以调节所述第一阻抗调节单元的阻抗,直至所述比较器单元输出校准完成信号,将所述第一阻抗调节单元的控制参数作为第一调节控制参数;

11.通过所述第一调节控制参数和所述第二调节控制参数调节所述高速发射电路,以实现对所述高速发射电路的阻抗校准。

12.本发明所述的阻抗校准方法的有益效果在于:通过上述阻抗校准方法依次对第一阻抗调节单元和第二阻抗调节单元进行校准,并分别获得第一调节控制参数和第二调节控制参数,在校准的过程中,分别以第一电阻单元、第二电阻单元、第三电阻单元这些阻值准确的外部精准电阻作为参考,有效消除了校准过程中累积误差的存在,从而使得校准后的结果更加准确。

13.可选的,所述第一电阻单元包括第一开关,所述第三电阻单元包括第六开关,所述第一开关和所述第六开关均内置电阻;

14.所述调节所述第一电阻单元的电阻和所述第三电阻单元的电阻,以将所述第一电阻单元的电阻和所述第三电阻单元的电阻均调节至最大电阻,包括:

15.接通所述第一开关,将所述第一开关内置的电阻接入所述第一电阻单元,以将所述第一电阻单元的电阻调节至最大电阻;

16.接通所述第六开关,将所述第二开关内置的电阻接入所述第三电阻单元,以将所述第三电阻单元的电阻调节至最大电阻。

17.可选的,所述第一开关的阻抗为所述第六开关的阻抗的两倍。

18.可选的,所述调节所述第一阻抗调节单元的控制参数,以将所述第一阻抗调节单元的阻抗调节到最小阻抗,包括:

19.所述第一阻抗调节单元的控制参数为四位的二进制数值,调节所述第一阻抗调节单元的控制参数为最小值,以将所述第一阻抗调节单元调节到最小阻抗。其有益效果在于:使得第一阻抗调节单元处于关闭状态,减少功耗。

20.可选的,所述调节所述第二阻抗调节单元的控制参数,以调节所述第二阻抗调节单元的阻抗,包括:

21.所述第二阻抗调节单元的控制参数为四位的二进制数值,将所述第二阻抗调节单元的控制参数自大到小调节,以调节所述第二阻抗调节单元的阻抗。其有益效果在于:通过将第二阻抗调节单元的控制参数设置为四位的二进制数值,便于实现对第二阻抗调节单元的控制,并提高校准精度。

22.可选的,所述调节所述第二阻抗调节单元的控制参数,以将所述第二阻抗调节单元的阻抗调节至最大阻抗,包括:

23.所述第二阻抗调节单元的控制参数为四位的二进制数值,调节所述第二阻抗调节单元的控制参数为最大值,以将所述第二阻抗调节单元调节到最大阻抗。

24.可选的,所述调节所述第一阻抗调节单元的控制参数,以调节所述第一阻抗调节单元的阻抗,包括:

25.所述第一阻抗调节单元的控制参数为四位的二进制数值,将所述第一阻抗调节单

元的控制参数自小到大调节,以调节所述第一阻抗调节单元的阻抗。其有益效果在于:通过将第一阻抗调节单元的控制参数设置为四位的二进制数值,便于实现对第一阻抗调节单元的控制,并提高校准精度。

26.本发明还提供了一种阻抗校准系统,包括阻抗校准电路和逻辑控制模块,所述阻抗校准电路包括第一阻抗调节单元、第一电阻单元、第一开关单元、第二电阻单元、第三电阻单元、第二阻抗调节单元、第二开关单元、比较器单元和第十三电阻,所述第一阻抗调节单元、所述第一电阻单元、所述第十三电阻的一端和所述比较器单元的负向输入端均与所述第一开关单元连接,所述第十三电阻的另一端接工作电压,所述第二电阻单元、所述第三电阻单元、所述第二阻抗调节单元和所述比较器单元的正向输入端均与所述第二开关单元连接,所述逻辑控制模块用于根据上述的阻抗调节方法调节所述第一开关单元、所述第二开关单元、所述第一阻抗调节单元的控制参数、所述第一电阻单元的控制参数、所述第二电阻单元的控制参数、所述第三电阻单元的控制参数、所述第二阻抗调节单元的控制参数和所述比较器单元的控制参数。

27.本发明所述的阻抗校准系统的有益效果在于:所述逻辑控制模块用于根据阻抗调节方法调节所述第一开关单元、所述第二开关单元、所述第一阻抗调节单元的控制参数、所述第一电阻单元的控制参数、所述第二电阻单元的控制参数、所述第三电阻单元的控制参数、所述第二阻抗调节单元的控制参数和所述比较器单元的控制参数,在对第一阻抗调节单元和第二阻抗调节单元进行校准的过程中,分别以第一电阻单元、第二电阻单元、第三电阻单元这些阻值准确的外部精准电阻作为参考,有效消除了校准过程中累积误差的存在,并分别获得第一调节控制参数和第二调节控制参数,从而使得校准后得到的结果更加准确。

附图说明

28.图1为现有技术中高速发射电路的电路图;

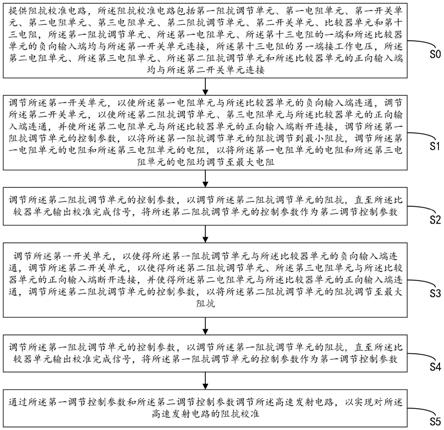

29.图2为本发明实施例所述阻抗校准方法的流程图;

30.图3为本发明实施例阻抗校准电路的电路图;

31.图4为本发明实施例所述第二阻抗调节子单元的电路示意图;

32.图5为本发明实施例所述第一阻抗调节子单元的电路示意图;

33.图6为发明实施例所述阻抗校准电路在经过步骤s1的调整之后的等效电路图;

34.图7为发明实施例所述阻抗校准电路在经过步骤s3的调整之后的等效电路图。

具体实施方式

35.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

36.图1为现有技术中高速发射电路的电路图。参照图1,所述高速发射电路包括工作电压单元100、接地电压单元200、变压器线圈300和输出端口400。

37.参照图1,所述工作电压单元100包括第一pmos管101、第二pmos管102、第三pmos管103、第四pmos管104、第五pmos管105、第六pmos管106、第七pmos管107、第八pmos管108、第十四电阻109、第十五电阻110、第十六电阻111和第十七电阻112。

38.参照图1,所述第一pmos管101的源极、所述第二pmos管102的源极、所述第三pmos管103的源极和所述第四pmos管104的源极均连接工作电压,所述第一pmos管101的栅极、所述第二pmos管102的栅极、所述第三pmos管103的栅极和所述第四pmos管104的栅极分别接相同或不同的工作电压单元控制信号,所述第一pmos管101的漏极连接所述第五pmos管105的源极,所述第五pmos管105的漏极连接所述第十四电阻109的一端,所述第二pmos管102的漏极连接所述第六pmos管106的源极,所述第六pmos管106的漏极连接所述第十五电阻110的一端,所述第三pmos管103的漏极连接所述第七pmos管107的源极,所述第七pmos管107的漏极连接所述第十六电阻111的一端,所述第四pmos管104的漏极连接所述第八pmos管108的源极,所述第八pmos管108的漏极连接所述第十七电阻112的一端,所述第五pmos管105的栅极、所述第六pmos管106的栅极、所述第七pmos管107的栅极和所述第八pmos管108的栅极分别接相同或不同的栅极电压,所述第十四电阻109的另一端、所述第十五电阻110的另一端、所述第十六电阻111的另一端和所述第十七电阻112的另一端均连接所述变压器线圈300的一端,所述变压器线圈300的另一端连接所述输出端口400。例如,所述工作电压单元控制信号为0011,则所述所述第一pmos管101的栅极接收高电平而导通,所述第二pmos管102的栅极接收高电平而导通,所述第三pmos管103的栅极接收低电平而关断,所述第四pmos管104的栅极接收低电平而关断。

39.参照图1,所述接地电压单元200包括第一nmos管201、第二nmos管202、第三nmos管203、第四nmos管204、第五nmos管205、第六nmos管206、第七nmos管207、第八nmos管208、第十八电阻209、第十九电阻210、第二十电阻211和第二十一电阻212。

40.参照图1,所述第一nmos管201的源极、所述第二nmos管202的源极、所述第三nmos管203的源极和所述第四nmos管204的源极均接地,所述第一nmos管201的栅极、所述第二nmos管202的栅极、所述第三nmos管203的栅极和所述第四nmos管204的栅极分别用于接相同或不同的接地电压单元控制信号,所述第一nmos管201的漏极连接所述第五nmos管205的源极,所述第五nmos管205的漏极连接所述第十八电阻209的一端,所述第二nmos管202的漏极连接所述第六nmos管206的源极,所述第六nmos管206的漏极连接所述第十九电阻210的一端,所述第三nmos管203的漏极连接所述第七nmos管207的源极,所述第七nmos管207的漏极连接所述第二十电阻211的一端,所述第四nmos管204的漏极连接所述第八nmos管208的源极,所述第八nmos管208的漏极连接所述第二十一电阻212的一端,所述第五nmso管的栅极、所述第六nmos管206的栅极、所述第七nmos管207的栅极和所述第八nmos管208的栅极分别用于接相同或不同的栅极电压,所述第十八电阻209的另一端、所述第十九电阻210的另一端、所述第二十电阻211的另一端和所述第二十一电阻212的另一端均连接所述变压器线圈300的一端,所述变压器线圈300的另一端连接所述输出端口。例如,所述接地电压单元控制信号为0011,则所述第一nmos管201的栅极接收高电平而导通,所述第二nmos管202的栅极接收高电平而导通,所述第三nmos管203的栅极接收低电平而关断,所述第四nmos管204

的栅极接收低电平而关断。

41.针对现有技术存在的问题,本发明的实施例提供了一种阻抗校准方法,用于对高速发射电路进行阻抗校准,如图2所示,所述方法包括如下步骤:

42.s0、提供阻抗校准电路,所述阻抗校准电路包括第一阻抗调节单元、第一电阻单元、第一开关单元、第二电阻单元、第三电阻单元、第二阻抗调节单元、第二开关单元、比较器单元和第十三电阻,所述第一阻抗调节单元、所述第一电阻单元、所述第十三电阻的一端和所述比较器单元的负向输入端均与所述第一开关单元连接,所述第十三电阻的另一端接工作电压,所述第二电阻单元、所述第三电阻单元、所述第二阻抗调节单元和所述比较器单元的正向输入端均与所述第二开关单元连接。

43.图3本发明实施例所述的阻抗校准电路的电路图,参照图3,所述阻抗校准电路500包括第一阻抗调节单元501、第一电阻单元502、第一开关单元503、第二电阻单元504、第三电阻单元505、第二阻抗调节单元506、第二开关单元507、比较器单元508和第十三电阻509,其中,所述第一阻抗调节单元501、所述第一电阻单元502、所述第十三电阻509的一端和所述比较器单元508的负向输入端均与所述第一开关单元503连接,所述第十三电阻509的另一端接工作电压,所述第二电阻单元504、所述第三电阻单元505、所述第二阻抗调节单元506和所述比较器单元508的正向输入端均与所述第二开关单元507连接。

44.参照图3,所述第一阻抗调节单元501包括第三电阻5011、第四电阻5012、第九电阻5013和第一阻抗调节子单元5014,所述第一阻抗调节子单元5014一端接地vss,另一端与所述第九电阻5013一端连接,所述第九电阻5013另一端与所述第四电阻5012一端连接,所述第四电阻5012另一端和所述第三电阻5011的一端均与所述第一开关单元503连接,所述第三电阻5011另一端还与所述第一电阻单元502、所述第十三电阻509的一端连接。

45.其中,所述第三电阻5011和所述第四电阻5012的阻抗为100ohm,所述第九电阻5013的阻抗为图1中变压器线圈300阻抗的一半。

46.参照图3,所述第一电阻单元502包括第一电阻5021、第二电阻5022和第一开关5023,所述第十三电阻509一端接工作电压vdd,所述第十三电阻509另一端与所述第一电阻5021一端连接,且所述第十三电阻509另一端还与第三电阻5011另一端、所述第一开关单元503连接,所述第一电阻5021另一端与所述第二电阻5022一端连接,所述第二电阻5022另一端与所述第一开关5023一端连接,所述第一开关5023另一端接地。

47.其中,所述第一开关5023为带有电阻的开关,其电阻记为ron1,当所述第一开关5023闭合之后,所述第一开关5023的电阻ron1接入所述第一电阻单元502。所述第十三电阻509的阻抗为100ohm,所述第一电阻5021和第二电阻5022的阻抗均为150ohm。

48.参照图3,所述第一开关单元503包括第二开关5031和第三开关5032,所述第二开关5031一端与所述地十三电阻5021另一端连接,所述第二开关另一端与所述比较器单元508的负向输入端连接,所述第三开关5032一端与所述第三电阻5011一端连接,所述第三开关5032另一端与所述比较器单元508的负向输入端连接。

49.参照图3,所述第二电阻单元504包括第五电阻5041、第六电阻5042、第七电阻5043和第八电阻5044,所述第五电阻5041一端接工作电压vdd,另一端与所述第六电阻5042一端连接,所述第六电阻5042另一端与所述第七电阻5043一端连接,所述第七电阻5043另一端与所述第八电阻5044一端连接,所述第八电阻5044另一端接地,且所述第六电阻5042另一

端还与所述第二开关单元507连接。

50.在一些实施例中,所述第五电阻5041、所述第六电阻5042、所述第七电阻5043和所述第八电阻5044的阻抗均为1kohm。

51.继续参照图3,所述第三电阻单元505包括第六开关5051、第十二电阻5052和第十一电阻5053,所述第六开关5051一端接地,另一端与所述第十二电阻5052一端连接,所述第十二电阻5052另一端与所述第十一电阻5053一端连接,所述第十一电阻5053另一端还与所述第二开关单元508、所述第二阻抗调节单元507连接,所述第六开关5051为带电阻的开关,所述第六开关5051的电阻记为ron2,当所述第六开关5051接通之后,第六开关5051的电阻ron2接入所述第三电阻单元506。

52.其中,所述第十一电阻5053和所述第十二电阻5052的阻抗均为75ohm。

53.需要说明的是,所述第一开关5023的阻抗为所述第六开关5051的阻抗的两倍。

54.参照图3,所述第二阻抗调节单元506包括第十电阻5061和第二阻抗调节子单元5062,所述第二阻抗调节子单元5062一端接工作电压vdd,另一端与所述第十电阻5061一端连接,所述第十电阻5061另一端与所述第十一电阻5053另一端、所述第二开关单元508连接。其中,所述第十电阻5061的阻抗与所述变压器线圈300阻抗相同。

55.参照图3,所述第二开关单元507包括第四开关5071和第五开关5072,所述第四开关5071一端与所述第十电阻5061另一端、所述第十一电阻5053另一端连接,所述第四开关5071另一端与所述比较器单元508的正向输入端连接,所述第五开关5072一端与所述第六电阻5042另一端连接,所述第五开关5072的另一端与所述比较器单元508的正向输入端连接。

56.图4为本发明所述第二阻抗调节子单元5062的电路示意图,参照图4,所述第二阻抗调节子单元5062包括第九pmos管50621、第十pmos管50622、第十一pmos管50623、第十二pmos管50624、第十三pmos管50625、第十四pmos管50626、第十五pmos管50627、第十六pmos管50628、第二十二电阻50629、第二十三电阻50630、第二十四电阻50631和第二十五电阻50632。

57.参照图4,所述第九pmos管50621的源极、第十pmos管50622的源极、第十一pmos管50623的源极和第十二pmos管50624的源极均接工作电压vdd,所述第九pmos管50621的栅极用于接第四控制信号zcal_calp《3》、第十pmos管50622的栅极用于接第三控制信号zcal_calp《2》、第十一pmos管50623的栅极用于接第二控制信号zcal_calp《1》和第十二pmos管50624的栅极用于接第一控制信号zcal_calp《0》,所述第九pmos管50621的漏极连接所述第十三pmos管50625的源极,所述第十三pmos管50625的漏极连接所述第二十二电阻50629的一端;所述第十pmos管50622的漏极连接所述第十四pmos管50626的源极,所述第十四pmos管50626的漏极连接所述第二十三电阻50630的一端;所述第十一pmos管50623的漏极连接所述第十五pmos管50627的源极,所述第十五pmos管50627的漏极连接所述第二十四电阻50631的一端;所述第十二pmos管50624的漏极连接所述第十六pmos管50628的源极,所述第十六pmos管50628的漏极连接所述第二十五电阻50632的一端,所述第十三pmos管50625的栅极、所述第十四pmos管50626的栅极、所述第十五pmos管50627的栅极和所述第十六pmos管50628的栅极均接地vss。

58.在一些实施例中,当zcal_calp《3》=1,即向所述第九pmos管50621栅极施加高电

平,所述第九pmos管50621关断,当zcal_calp《3》=0,即向所述第九pmos管50621栅极施加低电平,所述第九pmos管50621导通;当zcal_calp《2》=1,即向所述十pmos管50622栅极施加高电平,所述第十pmos管50621关断,当zcal_calp《2》=0,即向所述十pmos管50622栅极施加低电平,所述第十pmos管50622导通;当zcal_calp《1》=1,即向所述十一pmos管50623栅极施加高电平,所述第十一pmos管50623关断,当zcal_calp《1》=0,即向所述十一pmos管50623栅极施加低电平,所述第十一pmos管50623导通;当zcal_calp《0》=1,即向所述十二pmos管50624栅极施加高电平,所述第十二pmos管50624关断,当zcal_calp《0》=0,即向所述十二pmos管50624栅极施加低电平,所述第十二pmos管50624导通。

59.在一些实施例中,在所述第二阻抗调节子单元5062中,所述第二十二电阻50629的另一端、所述第二十三电阻50630的另一端、所述第二十四电阻50631的另一端和所述第二十五电阻50632的另一端均连接所述第十电阻5061的一端连接。

60.在一些实施例中,所述第二十二电阻50629的阻抗为50ohm,所述第二十三电阻50630的阻抗为100ohm,所述第二十四电阻50631的阻抗为200ohm,所述第二十五电阻50632的阻抗为400ohm。

61.在又一些实施例中,所述第二阻抗调节单元506的控制参数为zcal_calp《3:0》,所述第一控制信号、所述第二控制信号、所述第三控制信号和所述第四控制信号分别对应zcal_calp《3:0》中的一位。例如,当zcal_calp《3:0》为0000时,则zcal_calp《3》为0,zcal_calp《2》为0,zcal_calp《1》为0,zcal_calp《0》为0;当zcal_calp《3:0》为0010时,则zcal_calp《3》为0,zcal_calp《2》为1,zcal_calp《1》为0,zcal_calp《0》为0。

62.图5为本发明所述第一阻抗调节子单元5014的电路示意图,参照图5,所述第一阻抗调节子单元5014包括第九nmos管50141、第十nmos管50142、第十一nmos管50143、第十二nmos管50144、第十三nmos管50145、第十四nmos管50146、第十五nmos管50147、第十六nmos管50148、第二十六电阻50149、第二十七电阻50150、第二十八电阻50151和第二十九电阻50152。

63.参照图5,所述第九nmos管50141的源极、所述第十nmos管50142的源极、所述第十一nmos管50143的源极和所述第十二nmos管50144的源极均接地vss,所述所述第九nmos管50141的栅极用于接第八控制信号zcal_caln《3》,所述第十nmos管50142的栅极用于接第七控制信号zcal_caln《2》,所述第十一nmos管50143的栅极用于接第六控制信号zcal_caln《1》,所述第十二nmos管50144的栅极同于接第五控制信号zcal_caln《0》,所述第九nmos管50141的漏极连接所述第十三nmos管50145的源极,所述第十三nmos管50145的漏极连接所述第二十六电阻50149的一端;所述第十nmos管50142的漏极连接所述第十四nmos管50146的源极,所述第十四nmos管50146的漏极连接所述第二十七电阻50150的一端;所述第十一nmos管50143的漏极连接所述第十五nmos管50147的源极,所述第十五nmos管50147的漏极连接所述第二十八电阻50151的一端;所述第十二nmos管50144的漏极连接所述第十四nmos管50146的源极,所述第十四nmos管50146的漏极连接所述第二十九电阻50152的一端,所述第十三nmos管50145的栅极、所述第十四nmos管50146的栅极、所述第十五nmos管50147的栅极和所述第十六nmos管50148的栅极均连接工作电压vdd。

64.在一些实施例中,当zcal_caln《3》=1,即向所述第九nmos管50141栅极施加高电平,所述第九nmos管50141导通,当zcal_caln《3》=0,即向所述第九nmos管50141栅极施加

低电平,所述第九nmos管50141关断;当zcal_caln《2》=1,即向所述十nmos管50142栅极施加高电平,所述第十nmos管50142导通,当zcal_caln《2》=0,即向所述十nmos管50142栅极施加低电平,所述第十nmos管50142关断;当zcal_caln《1》=1,即向所述十一nmos管50143栅极施加高电平,所述第十一nmos管50143导通,当zcal_caln《1》=0,即向所述十一nmos管50143栅极施加低电平,所述第十一nmos管50143关断;当zcal_caln《0》=1,即向所述十二nmos管50144栅极施加高电平,所述第十二nmos管50144导通,当zcal_caln《0》=0,即向所述十二nmos管50144栅极施加低电平,所述第十二nmos管50144关断。

65.在一些实施例中,所述第一阻抗调节子单元5014中所述第二十六电阻50149的另一端、所述第二十七电阻50150的另一端、所述第二十八电阻50151的另一端和所述第二十九电阻50152的另一端均连接在所述第九电阻5013的一端。

66.在又一些实施例中,所述第二十六电阻50149的阻抗为50ohm,所述第二十七电阻50150的阻抗为100ohm,所述第二十八电阻50151的阻抗为200ohm,所述第二十九电阻50152的阻抗为400ohm。

67.在一些实施例中,所述第一阻抗调节单元501的控制参数为zcal_caln《3:0》,以所述第一阻抗控制单元501的控制参数为例,所述第五控制信号、所述第六控制信号、所述第七控制信号和所述第八控制信号分别对应zcal_caln《3:0》中的一位。例如,当zcal_caln《3:0》为0000时,则zcal_caln《3》为0,zcal_caln《2》为0,zcal_caln《1》为0,zcal_caln《0》为0;当zcal_caln《3:0》为0100时,则zcal_caln《3》为0,zcal_caln《2》为1,zcal_caln《1》为0,zcal_caln《0》为0。

68.s1、调节所述第一开关单元,以使所述第一电阻单元与所述比较器单元的负向输入端连通,调节所述第二开关单元,以使所述第二阻抗调节单元、第三电阻单元与所述比较器单元的正向输入端连通,并使所述第二电阻单元与所述比较器单元的正向输入端断开连接,调节所述第一阻抗调节单元的控制参数,以将所述第一阻抗调节单元的阻抗调节到最小阻抗,调节所述第一电阻单元的电阻和所述第三电阻单元的电阻,以将所述第一电阻单元的电阻和所述第三电阻单元的电阻均调节至最大电阻。

69.在一些可选的实施例中,所述调节所述第一阻抗调节单元501的控制参数,以将所述第一阻抗调节单元501的阻抗调节到最小阻抗,包括:

70.所述第一阻抗调节单元501的控制参数为四位的二进制数值,调节所述第一阻抗调节单元501的控制参数为最小值,以将所述第一阻抗调节单元501调节到最小阻抗。

71.具体的,参照图3,调节所述第一开关单元503,以使得第二开关5031导通,从而将第一电阻单元502与所述比较器单元508的负向输入端接通,同时将所述第三开关5032断开,并调节所述第一阻抗调节单元501的控制参数zcal_caln《3:0》=0000,从而将所述第一阻抗调节单元501的阻抗调节至最小阻抗,使得所述第一阻抗调节单元501与所述比较器单元508的负向输入端断开连接;调节所述第二开关单元507,将第四开关5071导通、第五开关5072断开,从而将所述第二电阻单元504与所述比较器单元508的正向输入端断开连接,将所述第三电阻单元505和所述第二阻抗调节单元506与所述比较器单元508的正向输入端接通。

72.在一些实施例中,所述调节所述第一电阻单元502的电阻和所述第三电阻单元505的电阻,以将所述第一电阻单元502的电阻和所述第三电阻单元505的电阻均调节至最大电

阻,包括:

73.接通所述第一开关,将所述第一开关5023内置的电阻接入所述第一电阻单元502,以将所述第一电阻单元502的电阻调节至最大电阻;

74.接通所述第六开关5051,将所述第二开关5051内置的电阻接入所述第三电阻单元505,以将所述第三电阻单元505的电阻调节至最大电阻。

75.具体的,调节所述第一电阻单元502中的所述第一开关5023,将所述第一开关5023导通,从而将所述第一开关5023的电阻ron1接入到所述第一电阻单元502之中,以使得所述第一电阻单元502的电阻调节至最大电阻;调节所述第三电阻单元505的第六开关5051,将所述第六开关5051接通,以使得所述第六开关5051的电阻ron2接入到所述第三电阻单元505之中,以使得所述第三电阻单元505的电阻调节至最大电阻。

76.s2、调节所述第二阻抗调节单元的控制参数,以调节所述第二阻抗调节单元的阻抗,直至所述比较器单元输出校准完成信号,将所述第二阻抗调节单元的控制参数作为第二调节控制参数。

77.在一些可选的实施例中,所述调节所述第二阻抗调节单元506的控制参数,以调节所述第二阻抗调节单元506的阻抗,包括:

78.所述第二阻抗调节单元506的控制参数为四位的二进制数值,将所述第二阻抗调节单元506的控制参数自大到小调节,以调节所述第二阻抗调节单元506的阻抗

79.具体的,所述比较器单元508的输出信号zcal_cmp_out包括校准完成信号和未完成校准信号,所述校准完成信号为二进制数值1,所述未完成校准信号为二进制数值0,图6为所述阻抗校准电路在经过步骤s1的调整之后的等效电路图,参照图6,将所述第一开关5023的电阻ron1等效为相同阻值的第三十电阻5024,先将所述第二阻抗调节单元506的控制参数zcal_calp《3:0》调节至最大值1111,以使得所述第二阻抗调节单元506的阻抗调节为最大值,若所述比较器单元508输出0,则将zcal_calp《3:0》减1,即zcal_calp《3:0》-1为1110,若所述比较器单元508还输出0,则再将zcal_calp《3:0》减1,即zcal_calp《3:0》-1为1100,直至所述比较器单元508输出1,并将此时的zcal_calp《3:0》作为所述第二调节控制参数,例如此时zcal_calp《3:0》为0110,则所述第二调节控制参数为0110,将所述第二调节控制参数zcal_calp《3:0》=0110记为第二阻抗调节子单元5062控制码codep。

80.s3、调节所述第一开关单元,以使得所述第一阻抗调节单元与所述比较器单元的负向输入端连通,调节所述第二开关单元,以使得所述第二阻抗调节单元、所述第三电阻单元与所述比较器单元的正向输入端断开连接,并使得所述第二电阻单元与所述比较器单元的正向输入端连通,调节所述第二阻抗调节单元的控制参数,以将所述第二阻抗调节单元的阻抗调节至最大阻抗。

81.在一些可选的实施例中,所述调节所述第二阻抗调节单元506的控制参数,以将所述第二阻抗调节单元506的阻抗调节至最大阻抗,包括:

82.所述第二阻抗调节单元506的控制参数为四位的二进制数值,调节所述第二阻抗调节单元506的控制参数为最大值,以将所述第二阻抗调节单元506调节到最大阻抗。

83.具体的,参照图3,首先调节第一开关单元503,将所述第二开关5031断开,并将第一电阻单元502中的第一开关5023断开,使得所述第一电阻单元502与所述比较器单元508的负向输入端断开连接,同时将所述第三开关5032接通,从而将所述第一阻抗调节单元501

与所述比较器单元508的负向输入端接通;调节所述第二开关单元507,将所述第四开关5071断开,同时将所述第六开关5051断开,使得所述第二阻抗调节单元506和所述第三电阻单元505均与所述比较器单元508的正向输入端接通,将所述第五开关5072接通,从而将所述第二电阻单元504与所述比较器单元508的正向输入端接通。

84.进一步的,将所述第二阻抗调节单元506的控制参数zcal_calp《3:0》调节为最大值1111,以使得所述第二阻抗调节单元506的阻抗调节至最大阻抗。

85.s4、调节所述第一阻抗调节单元的控制参数,以调节所述第一阻抗调节单元的阻抗,直至所述比较器单元输出校准完成信号,将所述第一阻抗调节单元的控制参数作为第一调节控制参数。

86.在一些可选的实施例中,所述调节所述第一阻抗调节单元501的控制参数,以调节所述第一阻抗调节单元501的阻抗,包括:

87.所述第一阻抗调节单元501的控制参数为四位的二进制数值,将所述第一阻抗调节单元501的控制参数自小到大调节,以调节所述第一阻抗调节单元501的阻抗。

88.具体的,图7为所述阻抗校准电路在经过步骤s3的调整之后的等效电路图,参照图7,将所述第六开关5051的电阻ron2等效为相同阻值的第三十一电阻5054,首先将所述第一阻抗调节单元501的控制参数zcal_caln《3:0》调整为最小值0000之后,根据所述比较器单元508的输出信号进行调整,若所述比较器单元508的输出信号zcal_cmp_out为0,则将zcal_caln《3:0》加1,即0000加1为0001,zcal_caln《3:0》加1变为0001;若所述比较器单元508还输出0,则再将zcal_caln《3:0》加1,即0001加1为0010,zcal_caln《3:0》加1变为0010,直至所述比较器单元508输出1,并将此时的zcal_caln《3:0》作为所述第一调节控制参数,例如此时zcal_caln《3:0》为0110,则所述第一调节控制参数为0110,也就是将所述第一调节控制参数zcal_caln《3:0》=0110作为控制码coden。

89.s5、通过所述第一调节控制参数和所述第二调节控制参数调节所述高速发射电路,以实现对所述高速发射电路的阻抗校准。

90.在完成上述校准过程之后,分别得到第一调节控制参数和第二调节控制参数后,将所述第一调节控制参数作为所述接地电压单元的控制信号调节所述接地电压单元,将所述第二调节控制参数作为所述工作电压单元的控制信号调节所述工作电压单元,从而完成对所述高速发射电路的阻抗校准。

91.在又一些实施例中,本发明还提供了一种阻抗校准系统,包括阻抗校准电路和逻辑控制模块,所述逻辑控制模块用于根据上述的阻抗调节方法调节所述第一开关单元、所述第二开关单元、所述第一阻抗调节单元的控制参数、所述第一电阻单元的控制参数、所述第二电阻单元的控制参数、所述第三电阻单元的控制参数、所述第二阻抗调节单元的控制参数和所述比较器单元的控制参数。

92.以上所述,仅为本技术实施例的具体实施方式,但本技术实施例的保护范围并不局限于此,任何在本技术实施例揭露的技术范围内的变化或替换,都应涵盖在本技术实施例的保护范围之内。因此,本技术实施例的保护范围应以所述权利要求的保护范围为准。

93.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的

实施方式,并且可通过多种方式实施或实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1