一种信号相位分析装置的制作方法

1.本实用新型涉及信号分析技术领域,尤其涉及一种信号相位分析装置。

背景技术:

2.在航空航天、石油探测、地质勘探等领域,通过声波、电磁波、光波对目标进行探测时,信号的相位分析显得尤为重要。通过信号相位分析,可以获取信号许多重要信息。

3.现有技术中,采集设备一直处于工作状态,实时进行数据的采集,当采集完成后,进行后期处理,得到信号相位进行分析。但采集设备产生的数据量往往不容小觑,同时带来的计算量也不可忽视的,导致此类方法通常只能采用事后处理的方式。因存储和传输需要消耗时间而难以保证信息提取的实时性,故难以使用于一些实时性高的应用场合。

技术实现要素:

4.有鉴于此,有必要提供一种信号相位分析装置,用以解决目前因存储和传输需要消耗时间而导致的无法在采集信号后实时进行相位分析的问题。

5.本实用新型提供一种信号相位分析装置,包括模数转换电路、比较电路、缓存电路、存储电路和相位分析电路,其中,所述模数转换电路、缓存电路、存储电路和相位分析电路依次电连接,所述比较电路与所述相位分析电路电连接,其中,

6.待测信号分两路输入至所述模数转换电路和比较电路,一路经过所述模数转换电路进行模数转换后输出至所述缓存电路中缓存,所述比较电路将另一路待测信号与阈值信号进行比较,输出高电平或低电平至所述相位分析电路,所述相位分析电路根据接收到的高电平或低电平发出存储信号或释放信号至所述缓存电路,当所述缓存电路接收所述存储信号后,将模数转换后的信号输出至所述存储电路和相位分析电路,当所述缓存电路接收所述释放信号时,将模数转换后的信号清除。。

7.优选的,所述的信号相位分析装置中,所述比较电路包括第一电阻、第二电阻和比较器,所述第一电阻的一端连接vcc电源,所述第一电阻的另一端连接比较器的反相输入端和第二电阻的一端,所述第二电阻的另一端接地,所述比较器的同相输入端输入待测信号,所述比较器的输出端连接所述相位分析电路。

8.优选的,所述的信号相位分析装置中,所述相位分析电路包括fpga芯片,所述fpga芯片分别通过若干个信号输入接口连接所述比较器的输出端、缓存电路和存储电路,所述fpga芯片还通过一信号输出接口连接所述缓存电路。

9.优选的,所述的信号相位分析装置中,所述缓存电路包括fifo缓存器,所述fifo缓存器的d-in端连接所述模数转换电路,所述fifo缓存器的q-out端连接所述存储电路和fpga芯片的一信号输入接口,所述fifo缓存器的rst端连接所述fpga芯片的信号输出接口。

10.优选的,所述的信号相位分析装置中,所述存储电路为一存储芯片,所述存储芯片的信号输入端连接所述fifo缓存器的q-out端,所述存储芯片的信号输出端连接所述fpga芯片。

11.优选的,所述的信号相位分析装置中,所述模数转换电路包括模数转换芯片,所述模数转换芯片的oeb1端输入待测信号,所述模数转换芯片的bit端连接所述fifo缓存器的d-in端。

12.优选的,所述的信号相位分析装置中,所述模数转换芯片的型号为ch1_ad9226。

13.相较于现有技术,本实用新型提供的信号相位分析装置,通过设置比较电路,通过比较电路进行信号比较后,可以根据输出的高低电平来判断出信号是否发生,当输出高电平时,信号发生,此时相位分析电路使缓存电路将缓存的信号输出至存储电路中存储,并发送至所述相位分析电路来进行相位分析,由于缓存电路的缓存作用,使得信号可以同时进行存储和分析,存储电路在进行信号的存储时,不会影响信号的分析,从而解决了因存储和传输需要消耗时间而导致的无法在采集信号后实时进行相位分析的问题;当输出低电平时,信号没有发生,此时缓存电路清除信号,可以避免缓存电路的存储空间被占用。

附图说明

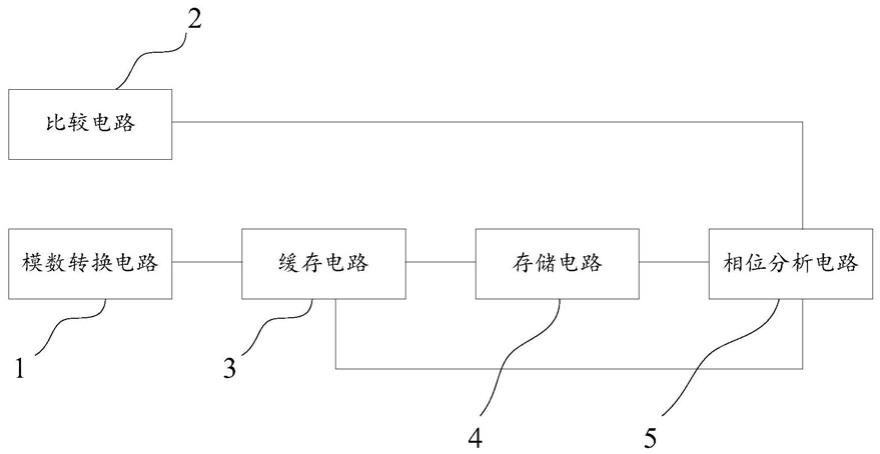

14.图1为本实用新型提供的信号相位分析装置的一较佳实施例的结构框图;

15.图2为本实用新型提供的信号相位分析装置中,所述比较电路的一较佳实施例的原理图;

16.图3为本实用新型提供的信号相位分析装置中,所述缓存电路的一较佳实施例的原理图;

17.图4为本实用新型提供的信号相位分析装置中,所述模数转换电路的一较佳实施例的原理图。

具体实施方式

18.下面结合附图来具体描述本实用新型的优选实施例,其中,附图构成本技术一部分,并与本实用新型的实施例一起用于阐释本实用新型的原理,并非用于限定本实用新型的范围。

19.请参阅图1,本实用新型实施例提供的信号相位分析装置,包括模数转换电路1、比较电路2、缓存电路3、存储电路4和相位分析电路5,其中,所述模数转换电路1、缓存电路3、存储电路4和相位分析电路5依次电连接,所述比较电路2与所述相位分析电路5电连接。

20.具体的,所述模数转换电路1用于对输入的待测信号进行模数转换。所述比较电路2用于将输入的待测信号与预设的阈值信号进行比较,并根据比较结果输出高低电平,当待测信号的幅值小于预设的阈值信号的幅值时,输出低电平,此时表示信号还没发生,当待测信号的幅值大于预设的阈值信号时,输出高电平,此时表示信号已经发生。所述缓存电路3用于对模数转换后的待测信号进行缓存,并根据高低电平来将信号发送至存储电路或者清除。所述存储电路4用于存储缓存电路3发送的信号。所述相位分析电路5用于根据比较电路输入的高低电平发出存储信号或释放信号至所述缓存电路3,还用于接收缓存电路3发送的信号,以实现相位分析,当所述相位分析电路5接收到高电平时,发出存储信号至所述缓存电路3,当所述相位分析电路5接收到低电平时,发出释放信号至所述缓存电路3。

21.换而言之,待测信号分两路输入至所述模数转换电路1和比较电路2,一路经过所述模数转换电路1进行模数转换后输出至所述缓存电路3中缓存,所述比较电路2将另一路

待测信号与阈值信号进行比较,输出高电平或低电平至所述相位分析电路5,所述相位分析电路5根据接收到的高电平或低电平发出存储信号或释放信号至所述缓存电路3,当所述缓存电路3接收所述存储信号后,将模数转换后的信号输出至所述存储电路4和相位分析电路5,当所述缓存电路3接收所述释放信号时,将模数转换后的信号清除。

22.本实用新型通过设置比较电路2,通过比较电路2进行信号比较后,可以根据输出的高低电平来判断出信号是否发生,当输出高电平时,信号发生,此时相位分析电路5使缓存电路3将缓存的信号输出至存储电路中存储,并发送至所述相位分析电路5来进行相位分析,由于缓存电路3的缓存作用,使得信号可以同时进行存储和分析,存储电路4在进行信号的存储时,不会影响信号的分析,从而解决了因存储和传输需要消耗时间而导致的无法在采集信号后实时进行相位分析的问题;当输出低电平时,信号没有发生,此时缓存电路3清除信号,可以避免缓存电路的存储空间被占用。

23.优选的实施例中,请参阅图2,所述比较电路2包括第一电阻r1、第二电阻r2和比较器u1,所述第一电阻r1的一端连接vcc电源,所述第一电阻r1的另一端连接比较器u1的反相输入端和第二电阻r2的一端,所述第二电阻r2的另一端接地,所述比较器u1的同相输入端输入待测信号,所述比较器u1的输出端连接所述相位分析电路5。

24.具体来说,所述第一电阻r1和第二电阻r2用于进行电压采集,从而产生阈值信号,将阈值信号输出至所述比较器u1的反相输入端,所述比较器u1将输入的待测信号的幅值与阈值信号进行比较,从而根据比较结果输出高低电平,当待测信号大于所述阈值信号时,所述比较器u1输出高电平,当待测信号小于所述阈值信号时,所述比较器u1输出低电平至所述相位分析电路5。所述阈值信号的大小根据vcc电源的大小而定,具体可根据实际情况设定。

25.优选的实施例中,所述相位分析电路5包括fpga芯片,所述fpga芯片分别通过若干个信号输入接口连接所述比较器u1的输出端、缓存电路3和存储电路4,例如data接口,所述fpga芯片还通过一信号输出接口连接所述缓存电路,例如使能接口。具体实施时,所述fpga芯片可采用xilinx芯片或altera芯片,本实用新型对此不做限定。所述fpga芯片根据接收到高低电平输出存储信号或释放信号至所述缓存电路。

26.优选的实施例中,请参阅图3,所述缓存电路3包括fifo缓存器u2,所述fifo缓存器u2的d-in端连接所述模数转换电路1,所述fifo缓存器u2的输出端连接所述存储电路4和fpga芯片的一信号输入接口,所述fifo缓存器u2的rst端连接所述fpga芯片的信号输出接口。具体实施时,所述fifo缓存器u2可采用型号为idt72v3680的芯片,当然,在其它的实施例中,所述fifo缓存器u2可采用其它型号的芯片,本实用新型对此不做限定。所述fifo缓存器u2可将输入的信号进行缓存,并且遵循fifo(first in first out即先进先出),该缓存空间满时,将最先进来的数据释放,释放一个后立刻读取这时的数据进行补充保证该缓存区内一直处于饱和状态。

27.优选的实施例中,所述存储电路4为一存储芯片,所述存储芯片的信号输入端连接所述fifo缓存器u2的q-out端,所述存储芯片的信号输出端连接所述fpga芯片。所述存储芯片可采用flash存储器等等,本实用新型对此不做限定。

28.优选的实施例中,请参阅图4,所述模数转换电路1包括模数转换芯片u3,所述模数转换芯片u3的oeb1端输入待测信号,所述模数转换芯片u3的bit端连接所述fifo缓存器u2

的d-in端。

29.具体来说,所述模数转换芯片的型号为ch1_ad9226,该模块供电端口3、4、31、34、43直接连接至硬件处理单元上,设备只需对硬件处理单元进行供电,即可驱动该模块。oeb1端口采用bnc口设计,通过射频线直接连接至信号发生装置上,连接简单,拆卸方便,造价低廉。模拟电信号经过ad_9226转化之后,得到十二位数字电信号,每一位依次通过12—27,进行输出,输出端口采用直插式设计,能够直接连接至硬件处理单元,避免了使用传统方式(杜邦线)连接导致的信号不稳定,又解决了传统方式连接的繁琐,插上即可使用。

30.综上所述,本实用新型提供的信号相位分析装置,通过设置比较电路,通过比较电路进行信号比较后,可以根据输出的高低电平来判断出信号是否发生,当输出高电平时,信号发生,此时相位分析电路使缓存电路将缓存的信号输出至存储电路中存储,并发送至所述相位分析电路来进行相位分析,由于缓存电路的缓存作用,使得信号可以同时进行存储和分析,存储电路在进行信号的存储时,不会影响信号的分析,从而解决了因存储和传输需要消耗时间而导致的无法在采集信号后实时进行相位分析的问题;当输出低电平时,信号没有发生,此时缓存电路清除信号,可以避免缓存电路的存储空间被占用。

31.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1