利用三模冗余实现高可靠光纤陀螺本征频率的系统和方法与流程

1.本发明涉及一种利用三模冗余实现高可靠数字合成光纤陀螺本征频率的系统和方法,属于惯性技术领域。

背景技术:

2.近年来,光纤陀螺在空间的应用技术日趋成熟,光纤陀螺成为越来越多卫星平台角度测量的首选产品。干涉式光纤陀螺中,光波在y波导和耦合器之间的两路光路的群传输时间之差的倒数的二分之一称为光纤陀螺的本征频率。光纤陀螺最小互易性结构的光功率响应是一个余弦函数,为了获得最大的灵敏度,需要给y波导施加一个偏执,使之工作在正弦函数的零位上,而y波导中的寄生非线性或振幅调制可能会削弱偏置的质量。在y波导非线性的情况下,一种简单的解决方法是使光纤陀螺工作在本征频率上,因此,光纤陀螺的信号处理装置通常都是基于其本征频率来设计其控制时序的,所以提高光纤陀螺工作频率的准确性是提高光纤陀螺性能的重要手段。

3.空间用光纤陀螺的数字闭环控制处理器,一般使用actel公司的反熔丝芯片,该芯片内没有锁相环,根据航天产品的研制特点,一般产品的技术状态确定后,晶振的频率就固定下来。由于国内目前的光纤环绕制技术无法做到非常精确,同一个批次的光纤环的环长相差十几米很正常,这就导致空间用光纤陀螺的固定的闭环频率和变化的光纤环本征频率之间存在矛盾,一旦光纤陀螺的闭环频率与本征频率相差较大(经常会出现和光纤环的本征频率相差几khz甚至十几khz)的情况,则会导致光纤陀螺噪声变大、陀螺零偏变大、陀螺死区变大等现象。

技术实现要素:

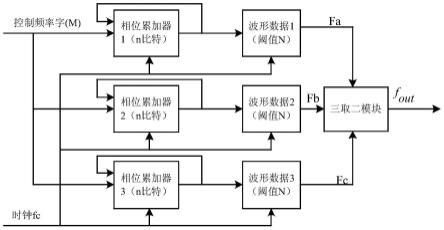

4.本发明的目的在于克服上述缺陷,提供一种利用三模冗余实现高可靠光纤陀螺本征频率的系统和方法,包括三个并列的改进型dds模块,三模冗余模块和校正模块;三个改进型dds模块中预设阈值n;三个改进型dds模块接收由外部输入的、具有预定数值的控制频率字m以及时钟信号,使控制频率字m按照时钟信号进行累加,根据累加值与阈值n的比较结果分别生成三路波形数据,并输出至三模冗余模块和校正模块;三模冗余模块对由三个改进型dds模块输入的三路波形数据进行逻辑运算得到输出波形数据f

out

,将输出波形数据f

out

输出至y波导和校正模块;校正模块根据由三模冗余模块输入的输出波形数据f

out

,以及由三个改进型dds模块输入的三路波形数据进行一致性判读,并根据一致性判读结果更新相应改进型dds模块中的阈值n。本发明利用三模冗余得到了高可靠的光纤陀螺的频率方波,使其能够工作在光纤环的本征频率上;同时,通过三模冗余模块和校正模块最大程度的增加了数字dds技术在空间应用的可靠性。

5.为实现上述发明目的,本发明提供如下技术方案:

6.一种利用三模冗余实现高可靠光纤陀螺本征频率的系统,包括三个并列的改进型dds模块,三模冗余模块和校正模块;

7.三个改进型dds模块中预设阈值n;三个改进型dds模块接收由外部输入的、具有预定数值的控制频率字m以及时钟信号,使控制频率字m按照时钟信号进行累加,根据累加值与阈值n的比较结果分别生成三路波形数据,并输出至三模冗余模块和校正模块;

8.三模冗余模块对由三个改进型dds模块输入的三路波形数据进行逻辑运算得到输出波形数据f

out

,将输出波形数据f

out

输出至y波导和校正模块;

9.校正模块根据由三模冗余模块输入的输出波形数据f

out

,以及由三个改进型dds模块输入的三路波形数据进行一致性判读,并根据一致性判读结果更新相应改进型dds模块中的阈值n。

10.进一步的,改进型dds模块包括相位累加器,输出的波形数据由基本元素1和0组成。

11.进一步的,每经过一个时钟信号周期,控制频率字m在相位累加器累加一次,并完成一次累加,所得累加值与阈值n比较一次。

12.进一步的,所述控制频率字m按照时钟信号进行累加后所得累加值超过阈值n时,波形输出反相;所述累加值使相位累加器溢出时,波形输出再次反相。

13.也可理解为,改进型dds模块包括相位累加器和隐含的波形数据存储器,其中波形数据存储器仅需存储1和0,假设相位累加器的数据宽度是n,当波形数据存储器的大小是2n,当累加值小于等于阈值n输出0,当累加值大于阈值n且小于等于2

n-1

输出1,当累加值大于2

n-1

输出0。

14.进一步的,输入三个改进型dds模块的控制频率字m和时钟信号fc为同步信号。

15.进一步的,所述三模冗余模块对三个改进型dds模块输入的三路波形数据进行逻辑运算得到输出波形数据的方法为三取二运算。

16.进一步的,所述三模冗余模块对三个改进型dds模块输入的三路波形数据进行逻辑运算得到输出波形数据的方法为:

17.记三路波形数据分别为fa、fb和fc,波形数据fa和波形数据fb做逻辑“与”运算得到信号s,波形数据fa和波形数据fc做逻辑“与”运算得到信号r,波形数据fb和波形数据fc做逻辑“与”运算得到信号t,信号r、信号s和信号t做逻辑“或”运算得到输出波形数据f

out

。

18.进一步的,所述校正模块进行一致性判读的方法为,记三个改进型dds模块分别为第一改进型dds模块、第二改进型dds模块和第三改进型dds模块,输出的三路波形数据分别为fa、fb和fc;

19.将输出波形数据f

out

与波形数据fa比较,如果相等,不做任何操作,如果不相等,则用第二改进型dds模块中的阈值更新第一改进型dds模块中的阈值;

20.将输出波形数据f

out

与波形数据fb比较,如果相等,不做任何操作,如果不相等,则用第三改进型dds模块中的阈值更新第二改进型dds模块中的阈值;

21.将输出波形数据f

out

与波形数据fc做比较,如果相等,不做任何操作,如果不相等,则用第一改进型dds模块的阈值更新第三改进型dds模块中的阈值n。

22.进一步的,通过更新控制频率字m实现输出波形数据f

out

频率的平滑调节。

23.一种利用三模冗余实现高可靠光纤陀螺本征频率的方法,采用上述一种利用三模冗余实现高可靠光纤陀螺本征频率的系统实现,包括如下步骤:

24.s1三个改进型dds模块中预设阈值n;三个改进型dds模块接收由外部输入的、具有

预定数值的控制频率字m以及时钟信号,使控制频率字m按照时钟信号进行累加,根据累加值与阈值n的比较结果分别生成三路波形数据,并输出至三模冗余模块和校正模块;

25.s2三模冗余模块对由三个改进型dds模块输入的三路波形数据进行逻辑运算得到输出波形数据f

out

,将输出波形数据f

out

输出至y波导和校正模块;

26.s3校正模块根据由三模冗余模块输入的输出波形数据f

out

,以及由三个改进型dds模块输入的三路波形数据进行一致性判读,并根据一致性判读结果更新相应改进型dds模块中的阈值n。

27.本发明与现有技术相比具有如下至少一种有益效果:

28.(1)本发明创新性利用三模冗余得到了高可靠的光纤陀螺的频率方波,实现光纤陀螺系统频率的调节,使其能够工作在光纤环的本征频率上;同时,通过三模冗余模块和校正模块最大程度的增加了数字dds技术在空间应用的可靠性;

29.(2)本发明针对光纤陀螺系统频率调节的需求,对现有dds模块的结构进行了改进,引入了阈值n,使dds模块在满足输出所需波形的同时,提高了波形生成的效率;

30.(3)本发明设计了校正模块,利用dds模块输出波形的一致性,对各dds模块的阈值实时更新,提高了数据的可靠性;

31.(4)本发明有利于提高光纤陀螺数字闭环频率的准确度,提高产品的性能,降低光纤陀螺噪声,降低光纤陀螺的零偏和死区。

附图说明

32.图1为现有技术中dds基本结构图;

33.图2为本发明改进型dds模块结构图;

34.图3为本发明改进型dds模块和三模冗余模块结构图;

35.图4为本发明三模冗余模块的基本逻辑图;

36.图5为本发明三模冗余模块和校正模块结构图。

具体实施方式

37.下面通过对本发明进行详细说明,本发明的特点和优点将随着这些说明而变得更为清楚、明确。

38.在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

39.直接数字合成(dds)是一种全数字频率合成技术,完全没有振荡元件和锁相环,而是用一连串数据流经过数模转换器产生出一个预先设定的模拟信号。它将先进的数字信号处理理论与方法引入信号合成领域,实现了合成信号的频率转换速度与频率准确度之间的统一。它具有相位变换连续、频率转换速度快、频率分辨率极高、相位噪声低、频率稳定度高(取决于所用的参考晶振的稳定度)、易于控制等多种优点。

40.本发明就是利用dds技术合成光纤陀螺的控制频率,并利用三模冗余对其算法进行改进,得到的一种适用于航天产品使用的高可靠数字合成技术。

41.如图2~图5,本发明提供一种利用带校正环节的三模冗余结构实现高可靠数字合

成光纤陀螺本征频率的系统,由改进型dds模块、三模冗余模块和校正模块组成。

42.通过改进型dds模块生成光纤陀螺的频率方波,三个dds模块结构相同,将三个dds模块输出的波形数据输入到三模冗余模块,在三模冗余模块中进行波形正确性判读,其输出即为高可靠的方波波形。校正模块完成三个dds模块输出的三路波形数据是否一致的判读,如果出现不一致,则对发生错误的dds模块进行重写或复位操作。

43.改进型dds模块包含一个相位累加器,输入相位累加器的控制频率字(m),每经过一个系统时钟周期,往累加器中加一次,另设一个阈值n,相位累加器内的数字每完成一次累加,所得累加值需要与阈值n比较一次,累加值一旦超过阈值n,则波形输出反相,然后累加值使寄存器输出溢出时波形输出再次反相,通过调整阈值n的值可以输出任意占空比的方波。

44.如图2,本发明改进型dds模块,是在如图1所示的基本dds模块基础上进行的简化,基本dds模块的核心为波形和频率,改进型dds模块由于输出为方波,所以其核心只为频率,简化后的dds模块主要包含一个相位累加器,输入包含系统时钟信号和控制频率字(m),其波形数据为基本元素1和0。

45.dds模块对输出波形频率的控制实质是:通过改变频率控制字,就改变了相位累加的速度,进而可以改变读取波形数据存储器中数据的速度,实质上也就是改变了输出波形的频率。假设相位累加器的数据宽度是n,波形数据存储器的大小是2n,并且系统时钟的频率是fc,如果频率控制字是m,则当m=1时dds的输出频率为f

out

。而波形数据存储器的全部数据读出一遍的频率正是dds模块输出波形的频率。

46.所以,dds模块输出波形信号频率与频率控制字和系统时钟频率之间的关系为:

47.f

out

=m

×

fc/2n(0《m《2

n-1)

48.其中:n=2

n-1

49.当系统时钟频率和相位累加器的数据宽度一定时,dds模块输出信号频率与频率控制字成正比。

50.实施例1:

51.本实施例系统包含3个如图2所示的并列的改进型dds模块,3个dds模块的输入信号包括控制频率字m和系统时钟信号fc,这两路信号通过fpga的程序保证高度的同步性,3个模块的输入控制频率字m和系统时钟fc保持同步,如图3和图4所示的三模冗余模块(即图中三取二模块)利用三模冗余算法对3个改进型dds输出的波形数据进行3取2设计。三模冗余模块同时完成三路改进型dds模块输出波形数据是否一致的判读,如果出现不一致,则说明存在某路dds波形数据被空间单粒子打翻或锁定的现象,则通过校正模块对发生错误的dds模块进行重写或复位操作。本发明通过三模冗余模块和校正模块最大程度的增加了数字dds技术在空间应用的可靠性。

52.记三个改进型dds模块输出的波形数据分别为fa、fb、fc,三模冗余模块中,波形数据fa和波形数据fb做逻辑“与”运算得到信号s,波形数据fa和波形数据fc做逻辑“与”运算得到信号r,波形数据fb和波形数据fc做逻辑“与”运算得到信号t,信号r、s和t做逻辑“或”运算得到输出波形数据f

out

。

53.如图5,校正模块是将输出波形数据f

out

,分别与三个改进型dds模块输出的波形数据fa、fb、fc做比较,如果相等,则说明没有阈值n被打翻,如果有不相等的情况,则需要更新

对应的阈值n。具体方法为,将输出波形数据f

out

,与dds模块1输出的波形数据fa做比较,如果相等,不做任何操作,如果不相等则需要用dds模块2中的阈值更新dds模块1中的阈值;将输出波形数据f

out

,与dds模块2输出的波形数据fb做比较,如果相等,不做任何操作,如果不相等则需要用dds模块3中的阈值更新dds模块2中的阈值;将输出波形数据f

out

,与dds模块3输出的波形数据fc做比较,如果相等,不做任何操作,如果不相等则需要用dds模块1中的阈值更新dds模块3中的阈值。

54.通过本发明可实现fpga的数字合成调频,通过更新控制频率字实现平滑调频的目的。

55.以上结合具体实施方式和范例性实例对本发明进行了详细说明,不过这些说明并不能理解为对本发明的限制。本领域技术人员理解,在不偏离本发明精神和范围的情况下,可以对本发明技术方案及其实施方式进行多种等价替换、修饰或改进,这些均落入本发明的范围内。本发明的保护范围以所附权利要求为准。

56.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1