过零检测电路的制作方法

过零检测电路

1.本技术是2018年7月25日提出的、申请号为2018800496802、名称为“过零检测电路”的发明申请的分案申请。

技术领域

2.本说明书中公开的发明涉及过零检测电路。

背景技术:

3.图57是示出过零检测电路的传统示例的图。该传统示例的过零检测电路det是用于检测施加在带电(l)端子和中性(n)端子之间的ac电压vac的过零(即ac电压vac和接地电位的交叉点)的电路,并且被安装在家用电器中作为基本上分立的组件(在该图的示例中,总共十一个组件,包括光电耦合器pc、pnp型双极晶体管qa、电阻器ra至rd、二极管da和db、齐纳二极管zd和电容器ca)。

4.注意,存在作为与上述描述相关的传统技术的示例的专利文献1。

5.现有技术文献

6.专利文献

7.专利文献1:jp特开2017-99178号公报

技术实现要素:

8.发明所要解决的课题

9.现在,该传统示例的过零检测电路det存在以下问题:(1)光电耦合器pc具有较大功耗;(2)存在大量离散组件;(3)由于光电耦合器pc的温度特性或其他因素,检测精度较低;以及(4)高压组件具有低的可靠性(在诸如洗衣机的应用中,电阻器ra的电腐蚀易于发生)。然而,该传统示例的过零检测电路det具有多年的操作经验,并且难以重新设计。因此,其像以前一样继续使用。

10.鉴于发明人发现的上述问题,本说明书中公开的本发明的目的是提供一种过零检测电路,该过零检测电路可以在不使用光电耦合器的情况下检测ac信号的过零。

11.解决课题所采取的手段

12.本说明书中公开的过零检测电路包括:峰值检测单元,该峰值检测单元用于检测通过二极管从ac信号输入端子输入的监测目标信号的峰值,从而生成峰值检测信号;以及过零检测单元,该过零检测单元用于用于根据所述峰值检测信号估计所述ac信号的过零,从而生成过零检测信号。

13.此外,本说明书中公开的所述过零检测电路包括:过零检测单元,该过零检测单元用于比较分别通过二极管从其间施加ac信号的第一节点和第二节点输入的第一监测目标信号和第二监测目标信号,从而生成第一比较信号;以及逻辑单元,该逻辑单元用于根据所述第一比较信号估计所述ac信号的过零,从而生成过零检测信号。

14.此外,本说明书中公开的所述过零检测电路包括:逻辑单元,该逻辑单元用于根据

分别通过二极管从其间施加ac信号的所述第一节点和所述第二节点输入的第一监测目标信号和第二监测目标信号中的至少一个来估计所述ac信号的过零,从而生成过零检测信号;以及输入停止检测单元,该输入停止检测单元用于在向所述第一监测目标信号和所述第二监测目标信号中的一个给出偏移之后将其进行比较以生成输入停止检测信号,其中,所述逻辑单元根据所述输入停止检测信号固定所述过零检测信号的逻辑电平。

15.注意,从以下实施方式的详细描述和与描述相关的附图中,其他特征、元件、步骤、优点和特征将变得清楚。

16.发明的效果

17.根据本说明书中公开的本发明,可以提供一种过零检测电路,其可以在不使用光电耦合器的情况下检测ac信号的过零。

附图说明

18.图1是示出电子设备的第一结构示例(正常整流)的图。

19.图2是示出电子设备的第二结构示例(倍压整流)的图。

20.图3是示出整流方法与各个部分处的电压之间的关系的图。

21.图4是示出半导体集成电路装置的第一实施方式的图。

22.图5是示出ac监测单元的一个结构示例的图。

23.图6是示出峰值检测单元的一个结构示例的图。

24.图7是示出第一输出单元的一个结构示例的图。

25.图8是示出过零检测过程的一个示例的时序图。

26.图9是示出噪声去除过程的一个示例的时序图。

27.图10是示出半导体集成电路装置的第二实施方式的图。

28.图11是示出ac波形确定过程的一个示例的时序图。

29.图12是示出ac监测信号的正常确定示例的图。

30.图13是示出半导体集成电路装置的第三实施方式的图。

31.图14是示出半导体集成电路装置的第四实施方式的图。

32.图15是示出半导体集成电路装置的封装的外部视图。

33.图16是示出封装布局的第一示例的图。

34.图17是示出第一芯片和第二芯片的内部结构的图。

35.图18是示意性地示出α-α'横截面的图。

36.图19是示出封装布局的第二示例的图。

37.图20是示出电子设备的第三结构示例(正常整流)的图。

38.图21是示出电子设备的第四结构示例(倍压整流)的图。

39.图22是示出半导体集成电路装置的第五实施方式的图。

40.图23是示出过零检测单元的第一示例的图。

41.图24是示出过零检测过程的第一示例的时序图。

42.图25是示出过零检测过程的第二示例的时序图。

43.图26是示出过零检测过程的第三示例的时序图。

44.图27是示出过零检测单元的第二示例的图。

45.图28是示出过零检测过程的第四示例的时序图。

46.图29是示出过零检测过程的第五示例的时序图。

47.图30是示出过零检测过程的第六示例的时序图。

48.图31是示出电子设备的第五结构示例(正常整流、单侧继电器)的图。

49.图32是示出半导体集成电路装置的第六实施方式的图。

50.图33是示出输出脉冲停止过程的一个示例的时序图。

51.图34是示出封装布局的第三示例的图。

52.图35是示出第一芯片和第二芯片的内部结构的图。

53.图36是示出封装布局的第四示例的图。

54.图37是示出第一芯片和第二芯片的内部结构的图。

55.图38是示出ac监测单元和dc监测单元的一个结构示例的图。

56.图39是示出第一芯片的布局的图。

57.图40是示出高电压区域的一个结构示例的纵向截面图。

58.图41是示出高电压区域的一个结构示例的放大俯视图。

59.图42是示出第二芯片的布局的图。

60.图43是示出封装布局的第五示例的图。

61.图44是示出封装布局的第六示例的图。

62.图45是示出半导体集成电路装置的引脚分配(七个引脚)的平面图。

63.图46是示出半导体集成电路装置的引脚分配(十一个引脚)的平面图。

64.图47是示出生成比较信号(没有输入偏移、没有信号失真)的操作的图。

65.图48是示出生成比较信号(没有输入偏移、具有信号失真)的操作的示图。

66.图49是示出生成比较信号(具有输入偏移、具有信号失真)的操作的示图。

67.图50是示出半导体集成电路装置的第七实施方式的图。

68.图51是示出过零延迟时间的变化抑制过程的图。

69.图52是示出半导体集成电路装置的第八实施方式的图。

70.图53是示出任意设定目标过零延迟时间的示例的图。

71.图54是示出acout信号的第一输出波形的图。

72.图55是示出acout信号的第二输出波形的图。

73.图56是示出半导体集成电路装置的第九实施方式的图。

74.图57是示出过零检测电路的传统示例的图。

具体实施方式

75.《电子设备(第一结构示例和第二结构示例)》

76.图1和图2是分别示出当提供ac电压v0时运行的电子设备的第一结构示例(正常整流方法)和第二结构示例(倍压整流方法)的图。每个结构示例的电子设备10包括滤波器11、整流单元12、ac/dc转换器13、dc/dc转换器14、微计算机15、驱动器16、电动机17和过零检测电路18。

77.滤波器11从输入在带电(l)端子和中性(n)端子之间的ac电压v0(例如,ac 80v至264v)中去除噪声和浪涌,以便在l1端子和n1端子之间输出结果。注意,可以在滤波器11的

前一级设置熔丝等保护元件。

78.整流单元12是对由滤波器11进行滤波处理后的ac电压v0进行正常整流或倍压整流以生成整流电压v1(例如,dc 100v至450v),并且将整流电压v1提供给ac/dc转换器13、电动机17和过零检测电路18的电路块。整流单元12包括二极管12a至12d、电容器12e(正常整流方法)或电容器12f和12g(倍压整流方法)。

79.注意,正常整流方法(图1)是国外主流的商用ac电源一般为200v系统的整流方法。与之相比,倍压整流方法(图2)是日本主流的商用ac电源是100v系统的整流方法。

80.二极管12a的阴极和二极管12c的阳极都连接到l1端子。二极管12b的阴极和二极管12d的阳极都连接到n1端子。二极管12c和12d的阴极彼此连接,并且其连接节点对应于整流电压v1的输出端子。二极管12a和12b的阳极彼此连接,并且其连接节点连接到对微计算机15和过零检测电路18共用的接地端子gnd。这样,二极管12a至12d彼此连接以形成二极管桥,该二极管桥在滤波过程之后对ac电压v0进行全波整流以生成整流电压v1。

81.此外,如果整流单元12采用正常整流方法,则单个电容器12e连接在整流电压v1的输出端子和接地端子gnd之间,如图1所示。与之相比,如果整流单元12采用倍压整流方法,则电容器12f和12g串联连接在整流电压v1的输出端子和接地端子gnd之间,如图2所示。注意,电容器12f和12g的连接节点连接到l1端子。

82.ac/dc转换器13根据通过对ac电压v0进行整流而获得的整流电压v1来生成期望的第一dc电压v3(例如,dc 13.0v至18.0v),并且将第一dc电压v3输出到dc/dc转换器14、驱动器16和过零检测电路18。

83.dc/dc转换器14根据第一dc电压v3生成期望的第二dc电压v4(例如,dc 5.0v),并将第二dc电压v4输出到微计算机15等。

84.微计算机15在提供第二dc电压v4时工作,并根据过零检测电路18的检测结果(即acout信号s1和dcout信号s2)生成电动机控制信号s3,以控制电动机17的驱动。

85.驱动器16在提供第一dc电压v3时工作,并根据电动机控制信号s3生成电动机驱动信号s4。

86.电动机17在提供整流电压v1时工作,并且其是根据电动机驱动信号s4被驱动旋转的一种类型的负载。

87.过零检测电路18是检测ac电压v0的过零(即,ac电压v0与接地电位的交点)的电路块,其包括半导体集成电路装置100、以及外部附接到半导体集成电路装置100的二极管d1和电容器c1。

88.半导体集成电路装置100是集成了构成过零检测电路18(其细节将在后面描述)的至少一部分电路元件的ic或lsi,并且具有七个外部端子(引脚1至引脚7)作为用于建立与装置外部的连接的装置。

89.引脚1(acout引脚)是acout信号s1的输出端子,并且连接到微计算机15。引脚2(dcout引脚)是dcout信号s2的输出端子,并且连接到微计算机15。引脚3(gnd引脚)是接地端子,并且连接到与微计算机15共用的接地端子gnd。换句话说,半导体集成电路装置100(因此使用该半导体集成电路装置100的过零检测电路18)相对于与微计算机15共用的接地电压进行运作。引脚4(vcc引脚)是电源端子并且连接到ac/dc转换器13的输出端子(即,第一dc电压v3的输出端子)。注意,电容器c1连接在引脚4和引脚3之间。

90.引脚5(vhdc引脚)是dc输入端子,并且连接到整流单元12的输出端子(即,整流电压v1的输入端子)。引脚6(非连接(n.c.)引脚)是未使用的端子并且未连接到半导体集成电路装置100外部的任何地方。引脚7(vhac引脚)是ac输入端子,并且连接到二极管d1的阴极(对应于监测目标电压v2的输入端子)。注意,二极管d1的阳极连接到n1端子(或l1端子)。

91.以这种方式,与上述传统示例(图38)不同,该结构示例的过零检测电路18仅利用三个安装的部件(半导体集成电路装置100、二极管d1和电容器c1)来检测ac电压v0的过零。因此,可以获得诸如减少待机功耗(1w到几十mw)、减少印刷电路板面积(几百平方毫米到几十平方毫米)或提高负载驱动控制的精度的效果,因此可以提供适应市场趋势或客户需求的电子设备10。

92.但是,为了实现该结构示例的过零检测电路18,需要解决以下技术问题:(1)不能使用光电耦合器;(2)在l端子和n端子之间以外进行监测时过零发生变化;以及(3)在正常整流方法和倍压整流方法之间过零检测点不同。

93.特别地,参照附图对上述技术问题(2)和(3)进行了详细说明。图3是示出整流方法和各个部分处的电压之间的关系的图,其中从上至下依次示出ac电压v0、整流电压v1和监测目标电压v2的波形。

94.例如,如果ac电压v0具有在+1.41ac和-1.41ac之间变化的正弦波形,并且如果整流单元12采用正常整流方法(图1),则如该图的左侧所示,整流电压v1具有+1.41ac附近的纹波的dc波形,监测目标电压v2具有在+1.41ac和0v之间变化的半波整流波形。与之相比,如果整流单元12采用倍压整流方法(图2),则如该图右侧所示,整流电压v1具有纹波接近+1.41ac

×

2的直流波形,监测目标电压v2具有在+1.41ac

×

2和0v之间变化的正弦波形。

95.以这种方式,监测目标电压v2具有与ac电压v0的波形不同的波形,并且根据负载状态,波形中可能发生失真。换句话说,可以假设监测目标电压v2的过零从ac电压v0的过零发生变化。因此,在用于检测监测目标电压v2的过零的结构中,可能不能正确地检测ac电压v0的过零。

96.此外,当试图检测监测目标电压v2的过零时,检测点在正常整流方法中是0v的交点,在倍压整流方法中是+1.41ac的交点。因此,在用于检测监测目标电压v2的过零的结构中,需要根据整流方法改变检测点,并且难以支持两种整流方法。

97.在以下描述中,例示了半导体集成电路装置100的实施方式,并且描述了所有技术问题(1)至(3)都得到解决。

98.《半导体集成电路装置(第一实施方式)》

99.图4是示出半导体集成电路装置100的第一实施方式的图。本实施方式的半导体集成电路装置100包括集成的ac监测单元110、峰值检测单元120、过零检测单元130、第一输出单元140、dc监测单元150、第二输出单元160和欠压保护单元170。

100.ac监测单元110是高压电路单元(例如,具有650v的耐受电压),其根据输入到引脚7(vhac引脚)的监测目标电压v2(对应于从施加有ac电压v0的n1端子通过二极管d1输入的监测目标信号)生成适应于输入到峰值检测单元120的ac监测信号sa。

101.峰值检测单元120检测ac监测信号sa(因此为监控目标电压v2)的峰值,以生成峰值检测信号sb。

102.过零检测单元130是逻辑电路,其根据峰值检测信号sb估计ac电压v0的过零,以生

成过零检测信号sc。

103.第一输出单元140接收过零检测信号sc的输入以生成acout信号s1,并将acout信号s1输出到引脚1(acout引脚)。

104.dc监测单元150是高压电路块(例如,具有650v的耐受电压),其根据输入到引脚5(vhdc引脚)的整流电压v1生成dc监测信号sx。

105.第二输出单元160接收dc监测信号sx的输入以生成dcout信号s2,并将dcout信号s2输出到引脚2(dcout引脚)。

106.注意,在直接输出dc监测信号sx作为dcout信号s2的情况下,可以消除第二输出单元160。此外,如果dc监测功能本身不是必需的,则可以消除所有dc监测单元150、第二输出单元160、引脚2(dcout引脚)和引脚5(vhdc引脚)。

107.欠压保护单元170是保护功能单元(所谓的欠压锁定(uvlo)保护单元),其在输入到引脚4(vcc)的第一dc电压v3低于下限值时禁用半导体集成电路装置100的操作。

108.《ac监测单元》

109.图5是示出ac监测单元110的一个结构示例的图。该结构示例的ac监测单元110包括电阻器111至115、n沟道金属氧化物半导体场效应晶体管(nmosfet)116、p沟道mosfet(pmosfet)117和二极管118。

110.电阻器111至115按图示顺序串联在引脚7(vhac引脚)和引脚3(gnd引脚)之间。注意,电阻器113和电阻器114的连接节点对应于ac监测信号sa的输出端子。即,电阻器111~115作为对输入到引脚7的监测目标电压v2进行分压而生成ac监测信号sa的分压电路而发挥功能。例如,假设电阻器111至113的组合电阻是rx(例如10mω),并且电阻器114和115的组合电阻是ry(例如0.1mω)。则sa=(ry/(rx+ry))

×

v2(≈0.01

×

v2)成立。

111.此外,在该图的示例中,电阻器111至115中的电阻器112和115的每个电阻可以通过微调等来调整。因此,可以任意地设置上述分压比ry/(rx+ry)。

112.注意,优选使用耐受电压为100v或更高(例如,650v)的多晶硅电阻器作为电阻器111至115。特别地,当集成电阻器111至115时,不仅需要在通过电阻器111至115的路径中(在横向方向上)的高电压结构,而且需要在半导体基板与电阻器111至115之间(在垂直方向上)的高电压结构。因此,在集成有ac监测单元110的半导体基板中,优选形成在基板厚度方向(在垂直方向)上具有比其它区域高的耐受电压的高电压区域,并且在高电压区域上形成电阻器111至115。作为上述高电压区域,可以使用具有高耐受电压的丰富结果的横向双扩散mosfet(ldmosfet)区域。

113.nmosfet 116的漏极连接到引脚7。nmosfet 116的源极、栅极和背栅极都连接到引脚3。pmosfet 117的漏极连接到引脚3。pmosfet 117的源极、栅极和背栅极都连接到ac监测信号sa的输出端子。二极管118的阴极连接到pmosfet 117的背栅极。pmosfet 117的漏极和二极管118的阳极都连接到引脚3。以这种方式连接的nmosfet 116、pmosfet 117和二极管118中的每一个用作静电保护元件。

114.注意,ac监测单元110不限于使用分压器电路的该结构示例,而是可以具有例如其中以预定采样率对监测目标电压v2进行采样并且将采样值作为ac监测信号sa输出到峰值检测单元120的结构。

115.此外,dc监测单元150应当具有与ac监测单元110基本相同的结构。换句话说,在以

上描述中,“引脚7(vhac引脚)”可以由“引脚5(vhdc引脚)”代替,并且“ac监测信号sa”可以由“dc监测信号sx”代替,从而可以理解dc监测单元150的结构和操作。

116.《峰值检测单元》

117.图6是示出峰值检测单元120的一个结构示例的图。如该图所示,该结构示例的峰值检测单元120包括电阻器121和122、电容器123和124以及比较器125。

118.电阻器121的第一端子与ac监测信号sa的输入端子连接。电阻器121的第二端子连接到电阻器122的第一端子、电容器123的第一端子和比较器125的非反相输入端子(+)。电阻器122的第二端子连接到电容器124的第一端子和比较器125的反相输入端子(-)。电容器123和124的第二端子都连接到引脚3(gnd引脚)。比较器125的输出端子对应于峰值检测信号sb的输出端子。

119.注意,电阻器121(例如,2mω)和电容器123(例如,10pf)用作rc滤波器,其去除叠加在ac监测信号sa上的噪声分量,以便生成第一ac监测信号sa1。

120.与之相比,电阻器122(例如,4.7mω)和电容器124(例如,20pf)用作向第一ac监测信号sa1给出预定延迟的延迟单元,以便生成第二ac监测信号sa2。

121.比较器125将第一ac监测信号sa1(无延迟)与第二ac监测信号sa2(有延迟)进行比较,从而生成峰值检测信号sb。峰值检测信号sb在第一ac监测信号sa1高于第二ac监测信号sa2时为高电平,在第一ac监测信号sa1低于第二ac监测信号sa2时为低电平。以这种方式生成的峰值检测信号sb在监测目标电压v2中出现峰值之后稍微延迟地下降到低电平。稍后将通过具体示例详细描述这一点。

122.注意,该图的电路结构仅是示例,并且可以采用任何电路结构,只要可以适当地检测监测目标电压v2(或ac监测信号sa)的峰值即可。

123.《第一输出单元》

124.图7是示出第一输出单元140的一个结构示例的图。该结构示例的第一输出单元140包括反相器141和142、nmosfet 143和电阻器144。反相器141的输入端子连接到过零检测信号sc的输入端子。反相器141的输出端子连接到反相器142的输入端子。反相器142的输出端子连接到nmosfet 143的栅极。电阻器144的第一端子连接到电源端子(例如,dc 5v)。电阻器144的第二端子和nmosfet 143的漏极都连接到引脚1(acout引脚)。nmosfet 143的源极和背栅极都连接到引脚3(gnd引脚)。

125.在该结构示例的第一输出单元140中,当过零检测信号sc为高电平时,nmosfet 143导通,因此从引脚1输出的acout号s1变为低电平。与之相比,当过零检测信号sc为低电平时,nmosfet 143断开,因此acout号s1变为高电平。

126.以这种方式,在具有开路漏极的第一输出单元140中生成的acout号s1基本上是过零检测信号sc的逻辑反相信号。

127.《过零检测过程》

128.图8是示出过零检测单元130的过零检测过程的一个示例的时序图,其中ac电压v0、整流电压v1、监测目标电压v2(或ac监测信号sa)、第一ac监测信号sa1、第二ac监测信号sa2、峰值检测信号sb和过零检测信号sc按从上到下的顺序依次示出。在下面的描述中,对在整流单元12采用正常整流方法(图1)的情况下的行为进行了例示和详细描述。

129.ac电压v0的波形是以预定周期切换正极性和负极性的正弦波形。注意,在该图的

示例中,在ac电压v0中的时间点t1、t5和t9处出现从负极性到正极性的过零,而在时间点t3、t7和t11处出现从正极性到负极性的过零。此外,在该图的示例中,ac电压v0在时间点t2、t6和t10处具有正峰值,而在时间点t4、t8和t12处具有负峰值。

130.整流电压v1的波形是在ac电压v0的全波整流波形(参照细虚线)的峰值附近具有纹波的dc波形。

131.如果整流单元12采用正常整流方法(图1),则监测目标电压v2(或ac监测信号sa)的波形基本上是ac电压v0的半波整流波形。换句话说,如果ac电压v0具有正值,则监测目标电压v2也具有正值,而即使ac电压v0具有负值,监测目标电压v2也不低于0v。

132.注意,如重叠的细虚线(理想)和粗实线(现实)所示,监测目标电压v2的波形可能具有取决于负载状态等的失真。因此,即使检测到监测目标电压v2的过零,也难以正确地检测ac电压v0的过零。

133.与之相比,经过认真研究,发明人发现监测目标电压v2的峰值定时基本上与ac电压v0的峰值定时相同,而不依赖于负载状态等,换句话说,ac电压v0和监测目标电压v2仅在每个峰值定时具有相同的相位。基于该认识,发明人创建了一种新颖的算术算法,该算术算法能够根据监测目标电压v2的峰值定时来估计ac电压v0的过零。在下面的描述中,在继续图8的描述的同时,对上述算术算法进行了详细的描述。

134.第一ac监测信号sa1(粗实线)及其延迟信号,即第二ac监测信号sa2(粗虚线)在从监测目标电压v2的峰值定时(例如时间点t2)起经过预定延迟时间δ的时间点(例如时间点tx)处彼此交叉。下面参考该图给出具体的描述。在时间点tx之前和之后,第一ac监测信号sa1和第二ac监测信号sa2之间的高/低关系从sa1》sa2切换到sa1《sa2。结果,峰值检测信号sb在时间点tx从高电平下降到低电平。

135.换句话说,可以说峰值检测信号sb的下降沿指示监测目标电压v2的峰值定时(因此指示ac电压v0的正峰值定时)。因此,过零检测单元130顺序地检测峰值检测信号sb的下降沿,以便对峰值检测信号sb的周期t(例如,在该图中从时间点tx到时间点ty)进行计数,并且使用计数值来估计ac电压v0的过零。

136.更具体地,在ac电压v0具有恒定周期和恒定相位的前提下,过零检测单元130参考峰值检测信号sb的周期t,以确定过零检测信号sc的上升定时和下降定时。

137.例如,过零检测单元130从峰值检测信号sb下降到低电平的时间点(例如时间点ty)开始对与预先获得的周期t相对应的待机时间t1(例如t1=(1/4)

×

t-δ)进行计数,并且在待机时间t1过去的时间点将过零检测信号sc从低电平升高到高电平。过零检测信号sc的上升定时与ac电压v0从正切换到负(即,过零从正切换到负)时的定时基本相同。

138.此外,过零检测单元130在从峰值检测信号sb下降到低电平的时间点(例如,时间点ty)起经过了比待机时间t1长的待机时间t2(例如,t2=(3/4)

×

t-δ)的时间点处,将过零检测信号sc从高电平减小到低电平。过零检测信号sc的下降定时基本上与ac电压v0从负切换到正(即,过零从负切换到正)时的定时相同。

139.注意,作为用于确定待机时间t1和待机时间t2的时段周期的计数值,可以使用一个周期之前的计数值,或者可以使用几个周期的平均计数值。此外,根据延迟单元(电阻器122和电容器124)的电路特性已知用于确定待机时间t1和待机时间t2的延迟时间δ(即,峰值检测信号sb的真实峰值定时和脉冲边缘定时之间的偏移)。然而,可以忽略延迟时间δ并

且在不对其进行校正的情况下确定过零检测信号sc的上升定时和下降定时。

140.此外,在该图中,如上所述对正常整流方法(图1)中的过零检测过程进行了例示,但是在倍压整流方法(图2)中的过零检测过程中也是如此,除了监测目标电压v2(或ac监测信号sa)的波形不同之外,可以执行与上述相同的过零检测过程。换句话说,上述新颖的算术算法可以支持正常整流方法(图1)和倍压整流方法(图2)双方。

141.然而,该图的过零检测过程仅仅是一个示例,并且可以采用任何算术算法,只要可以根据峰值检测信号sb适当地生成过零检测信号sc的脉冲边缘即可。

142.《噪声去除过程》

143.接下来,在实际应用中,参考附图详细描述去除假定叠加在峰值检测信号sb上的噪声的方法。图9是示出过零检测单元130的噪声去除过程的一个示例的时序图,其中ac监测信号sa、峰值检测信号sb和过零检测信号sc按从上到下的顺序依次示出。注意,在下面的描述中,为了便于描述,忽略了延迟时间δ。

144.在该图的示例中,ac监测信号sa在时间点t22和t25处具有峰值,并且随之,峰值检测信号sb从高电平下降到低电平。因此,对于峰值检测信号sb的下降沿,确定过零检测信号sc的上升定时和下降定时,因此可以正确地估计ac电压v0的过零。这在上面已经进行了描述。

145.然而,在电子设备10中,由于电动机17的反电动势等,不期望的噪声(在该图中,噪声n1至n3)叠加在ac监测信号sa上。注意,噪声n1叠加在ac监测信号sa从零增大到峰值(即,从时间点t21到时间点t22)的时段中。与之相比,噪声n2叠加在ac监测信号sa保持为零的时段中(即,从时间点t23到时间点t24)。此外,噪声n3叠加在ac监测信号sa从峰值下降到零的时段中(即,从时间点t25到时间点t26)。

146.当叠加这些噪声n1至n3时,峰值检测信号sb可能被切换到不期望的逻辑电平,因此不能正确地检测ac监测信号sa的峰值。因此,在切换峰值检测信号sb的逻辑电平之后,如果切换之后的逻辑电平没有保持预定屏蔽时段(例如,1600μs),则过零检测单元130忽略逻辑电平的切换。

147.例如,从时间点t21到时间点t22,峰值检测信号sb由于噪声n1而下降到低电平,但是很快上升到高电平,因此该下降沿被忽略。换句话说,过零检测单元130认为峰值检测信号sb从时间点t21到时间点t22保持在高电平。

148.类似地,从时间点t23到时间点t24,峰值检测信号sb由于噪声n2而下降到低电平,但是很快上升到高电平,因此该下降沿也被忽略。换句话说,过零检测单元130认为峰值检测信号sb从时间点t23到时间点t24保持在高电平。

149.与之相比,从时间点t25到时间点t26,峰值检测信号sb由于噪声n3而上升到高电平,但是很快下降到低电平,因此该上升沿被忽略。换句话说,过零检测单元130认为峰值检测信号sb从时间点t25到时间点t26保持在低电平。

150.注意,执行上述噪声去除过程的单元不一定限于过零检测单元130。在接收到峰值检测信号sb的输入之后执行特定信号处理之前完成噪声去除过程是有用的。

151.此外,可以在峰值检测单元120和过零检测单元130之间设置模拟噪声滤波器或数字噪声滤波器(例如,有限脉冲响应(fir)滤波器)。

152.《半导体集成电路装置(第二实施方式)》

153.图10是示出半导体集成电路装置100的第二实施方式的图。本实施方式的半导体集成电路装置100基于第一实施方式(图1),并且还包括比较单元180和ac波形确定单元190(在该图中,未示出ac监测单元110、第一输出单元140、dc监测单元150、第二输出单元160和欠压保护单元170)。因此,具有与第一实施方式中相同结构的元件由与图4中相同的数字或符号表示,以便省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

154.比较单元180包括四个比较器181至184,并且将ac监测信号sa与多个阈值vth1至vth4(vth1《vth2《vth3《vth4)中的每一个进行比较,以生成多个比较信号sd1至sd4。

155.更具体地,比较器181将输入到非反相输入端子(+)的ac监测信号sa与输入到反相输入端子(-)的阈值vth1进行比较,以生成比较信号sd1。因此,当ac监测信号sa高于阈值vth1时,比较信号sd1为高电平,而当ac监测信号sa低于阈值vth1时,比较信号sd1为低电平。

156.比较器182将输入到非反相输入端子(+)的ac监测信号sa与输入到反相输入端子(-)的阈值vth2进行比较,以生成比较信号sd2。因此,当ac监测信号sa高于阈值vth2时,比较信号sd2为高电平,而当ac监测信号sa低于阈值vth2时,比较信号sd2为低电平。

157.比较器183将输入到非反相输入端子(+)的ac监测信号sa与输入到反相输入端子(-)的阈值vth3进行比较,以生成比较信号sd3。因此,当ac监测信号sa高于阈值vth3时,比较信号sd3为高电平,而当ac监测信号sa低于阈值vth3时,比较信号sd3为低电平。

158.比较器184将输入到非反相输入端子(+)的ac监测信号sa与输入到反相输入端子(-)的阈值vth4进行比较,以生成比较信号sd4。因此,当ac监测信号sa高于阈值vth4时,比较信号sd4为高电平,而当ac监测信号sa低于阈值vth4时,比较信号sd4为低电平。

159.注意,比较单元180不限于四个通道。通道的数目可以是任意的(两个或更多个通道)。

160.ac波形确定单元190存储比较信号sd1至sd4中的每一个中是否已经出现上升沿和下降沿中的每一个,并且在过零检测信号sc的一个周期期间检测比较信号sd1至sd4中的至少一个中是否已经出现上升沿和下降沿两者,从而生成波形确定信号se。当ac监测信号sa具有正常波形时,波形确定信号se是正常确定逻辑电平(例如低电平),而当ac监测信号sa具有异常波形时,波形确定信号se是异常确定逻辑电平(例如高电平)。

161.注意,当比较信号sd1至sd4的每个逻辑电平保持预定时段(例如,40μs)时,ac波形确定单元190第一次识别出逻辑电平有效。利用该结构,可以忽略比较信号sd1至sd4中的噪音或抖动,因此可以正确地执行ac波形确定过程。

162.当波形确定信号se是异常确定逻辑电平(例如高电平)时,过零检测单元130停止过零检测信号sc的生成或输出。例如,当ac电源发生瞬时电力故障时,如果ac监测信号sa的波形变得异常,则停止过零检测信号sc的生成或输出。因此,微计算机15迅速地识别ac电压v0中的异常的发生,从而无延迟地停止电动机17的驱动,并且因此可以增强电子设备10的安全性和可靠性。

163.《ac波形确定过程》

164.图11是示出由ac波形确定单元190进行的ac波形确定过程的一个示例的时序图,其中ac监测信号sa、峰值检测信号sb、过零检测信号sc、比较信号sd1至sd4和波形确定信号se按从上到下的顺序依次示出。

165.ac监测信号sa在从时间点t31到时间点t32的时段中正常输入,并且在预定检测时段tdet(对应于过零检测信号sc的一个周期)中,ac监测信号sa从零(《vth1)上升到峰值(》vth4),然后再次下降到零。结果,上升沿和下降沿都出现在比较信号sd1至sd4中的每一个中。因此,确定ac监测信号sa具有正常波形,并且波形确定信号se为低电平(即,正常确定中的逻辑电平)。

166.与之相比,在从时间点t32到时间点t33的时段中,ac监测信号sa从零上升到峰值并且再次下降。紧接着,在ac电源中发生瞬时电力故障,结果,ac监测信号sa保持在高于阈值vth4的电压值。注意,在使用具有较大功耗的光耦合器的传统结构(图20)中,如果在ac电源中发生瞬时电力故障,则也没有延迟地停止对负载的供电,因此没有特别的问题。然而,在不使用光电耦合器的该结构中,监测目标电压v2不被放电,因此可以出现如图中所示的状态。

167.在这种情况下,如果监测目标电压v2(因此ac监测信号sa)由于特定因素而周期性地变化,则尽管来自ac电源的供电被停止,ac监测信号sa的峰值仍被误检测,因此仍然输出过零检测信号sc。结果,微计算机15错误确定从ac电源连续地供应电力,并且可能存在通过剩余电力使电动机17连续地旋转的故障。

168.与之相比,在包括比较单元180和ac波形确定单元190的结构中,如果ac监测信号sa保持在高于阈值vth4的电压值,则所有比较信号sd1至sd4都固定为高电平,因此确定ac监测信号sa的波形异常。因此,波形确定信号se被升高到高电平(即,异常确定逻辑电平)。结果,在时间点t33之后,停止过零检测信号sc的生成和输出,因此微计算机15能够迅速地识别ac电源中的瞬时电力故障,并且能够无延迟地停止电动机17的驱动。

169.注意,由于监测目标电压v2的缓慢放电,在比上述检测时段tdet长的时段,ac监测信号sa中可能出现上升沿和下降沿。然而,通过将检测时段tdet设置为过零检测信号sc的一个周期,可以防止基于该脉冲边缘错误地确定ac监测信号sa具有正常波形。

170.图12是示出ac监测信号sa的正常确定示例的图,其中ac监测信号sa和比较信号sd1至sd4按从上到下的顺序依次示出。

171.在该图的左侧,类似于图11中的时间点t31至t32,示出了ac监测信号sa以跨越所有的阈值vth1~vth4的方式变化的情况。在这种情况下,在所有比较信号sd1至sd4中出现周期性脉冲边沿,并且确定ac监测信号sa正常。

172.与之相比,在该图的中间,示出了ac监测信号sa以仅跨越阈值vth1和vth2的方式变化的情况(这里,示出了半波整流波形的峰值低于阈值vth3的方式)。在这种情况下,虽然比较信号sd3和sd4被固定为低电平,但是在比较信号sd1和sd2中都出现周期性脉冲边缘,因此确定ac监测信号sa正常。

173.此外,在该图的右侧,示出了ac监测信号sa以越过阈值vth2至vth4的方式变化的情况(这里,ac波形的较低峰值高于阈值vth1的方式)。在这种情况下,虽然比较信号sd1被固定为高电平,但是在比较信号sd2至sd4中的每一个中出现周期性脉冲边缘,因此确定ac监测信号sa正常。

174.以这种方式,利用具有多个通道的比较单元180,可以对具有各种正常波形的ac监测信号sa适当地执行ac波形确定过程。

175.此外,不一定需要结合峰值检测过程或过零检测过程来执行上述ac波形确定过

程,而是可以单独执行上述ac波形确定过程。

176.《半导体集成电路装置(第三实施方式)》

177.图13是示出半导体集成电路装置100的第三实施方式的图。本实施方式的半导体集成电路装置100基于第一实施方式(图4)并且进一步包括集成ac/dc转换器13作为特征。因此,具有与第一实施方式中相同结构的元件由与图4中相同的数字或符号表示,以便省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

178.在构成ac/dc转换器13的电路元件当中,半导体集成电路装置100包括集成的电阻器13a和13b、误差放大器13c、比较器13d、rs触发器13e、电平移位器13f和nmosfet 13g。

179.此外,将外部端子(引脚x)与ac/dc转换器13的集成一起添加到半导体集成电路装置100。注意,构成ac/dc转换器13的电路元件中的线圈13h和二极管13i外部连接到引脚x。具体地,线圈13h的第一端子和二极管13i的阴极连接到引脚x。线圈13h的第二端子连接到第一dc电压v3的输出端子。二极管13i的阳极连接到引脚3(gnd引脚)。

180.在半导体集成电路装置100内部,电阻器13a和13b串联连接在引脚4(vcc引脚)和引脚3(gnd引脚)之间,并且用作从电阻器13a和13b的连接节点输出反馈信号fb(即,第一dc电压v3的分压)的分压器电路。

181.误差放大器13c根据输入到非反相输入端(+)的反馈信号fb和输入到反相输入端(-)的预定参考信号ref之间的差来生成误差信号err。反馈信号fb和参考信号ref之间的差越大,误差信号err越高,而反馈信号fb和参考信号ref之间的差越小,误差信号err越低。

182.比较器13d将具有输入到非反相输入端子(+)的锯齿波形(或三角波形)的斜坡信号slp与输入到反相输入端子(-)的误差信号err进行比较,以生成复位信号rst。当斜坡信号slp高于误差信号err时,复位信号rst为高电平,而当斜坡信号slp低于误差信号err时,复位信号rst为低电平。

183.rs触发器13e基于输入到置位端子(s)的置位信号set(即,具有以预定开关频率振荡的矩形波形的时钟信号)和输入到复位端子(r)的复位信号rst两者来确定脉宽调制信号pwm的逻辑电平,并且从输出端子(q)输出脉宽调制信号pwm。例如,当置位信号set上升为高电平时,脉宽调制信号pwm被置位为高电平,而当复位信号rst上升为高电平时,脉宽调制信号pwm被复位为低电平。

184.电平移位器13f对脉宽调制信号pwm(h=v3且l=gnd)进行电平移位,以生成驱动信号drv(h=vs+α且l=vs,其中vs表示引脚x处的nmosfet13g的源极电压)。

185.nmosfet 13g连接在引脚5(vhdc引脚)和引脚x之间,并且是通过驱动信号drv导通和断开的输出开关元件。

186.以这种方式,ac/dc转换器13被封装到半导体集成电路装置100的单个封装中,因此可以减少部件的数量。

187.注意,在该实施方式中描述了基于第一实施方式(图4)的示例,但是该示例也可以基于第二实施方式(图10)。

188.《半导体集成电路装置(第四实施方式)》

189.图14是示出半导体集成电路装置100的第四实施方式的图。本实施方式的半导体集成电路装置100基于第三实施方式(图13)并且进一步包括集成dc/ac转换器14作为特征。注意,用于输出第二dc电压v4的外部端子(引脚y)与dc/dc转换器14的集成一起被添加到本

实施方式的半导体集成电路装置100。这样,不仅ac/dc转换器13而且dc/dc转换器14都被封装在单个封装中,因此可以进一步减少部件的数量。

190.《封装》

191.图15是示出半导体集成电路装置100的封装的外部视图。该图示出了外部端子从封装的长边在两个方向上延伸的小外形封装(sop)的示例。

192.引脚1(acout引脚)、引脚2(dcout引脚)、引脚3(gnd引脚)和引脚4(vcc引脚)是未施加整流电压v1或监测目标电压v2的低耐受电压端子(引脚1和引脚2具有5v的耐受电压,引脚3和引脚4具有30v的耐受电压),并且布置在封装的第一侧。

193.与之相比,引脚5(vhdc引脚)和引脚7(vhac引脚)是被施加整流电压v1和监测目标电压v2的高耐受电压端子(具有700v的耐受电压),并且布置在封装的第二侧。通过这种引脚分配,可以确保引脚1至引脚4与引脚5或引脚7之间的绝缘爬电距离,因此可以容易地确保引脚之间的绝缘。

194.注意:取消了原来设置在引脚7(vhac引脚)和引脚6(n.c.引脚)之间的外部端子。因此,引脚7与相邻引脚6之间的端子间距离大于引脚1至引脚4的相邻引脚之间的端子间距离。此外,忽略未使用的引脚6,引脚5与引脚7之间的端子间距离自然大于引脚1至引脚4的相邻引脚之间的端子间距离。通过这种引脚分配,也可以充分地确保第二侧上的引脚之间的绝缘。

195.《封装布局(第一示例)》

196.图16是示出封装布局的第一示例的图(xz平面图)。在该图的半导体集成电路装置100中,第一芯片100a和第二芯片100b安装在岛100c上。

197.首先,参照附图详细描述第一芯片100a和第二芯片100b的内部结构。图17是示出第一芯片100a和第二芯片100b的内部结构的图,其中示出基于第一实施方式(图4)的一个示例。

198.第一芯片100a包括集成的ac监测单元110和dc监测单元150。此外,第一芯片100a具有焊盘p1至焊盘p5作为用于建立与芯片外部的电连接的装置。在第一芯片100a内部,焊盘p1连接到dc监测单元150的输入端子。焊盘p2连接到ac监测单元110的输入端子。焊盘p3连接到dc监测单元150的输出端子。焊盘p4连接到ac监测单元110的输出端子。焊盘p5连接到地线。

199.与之相比,第二芯片100b包括集成的峰值检测单元120、过零检测单元130、第一输出单元140、第二输出单元160和欠压保护单元170。此外,第二芯片100b具有焊盘p6至焊盘p12作为用于建立与芯片外部的电连接的装置。在第二芯片100b内部,焊盘p6连接到第二输出单元160的输入端子。焊盘p7连接到峰值检测单元120的输入端子。焊盘p8连接到地线。焊盘p9连接到欠压保护单元170的输入端子(即,电源线)。焊盘p10连接到地线。焊盘p11连接到第二输出单元160的输出端子。焊盘p12连接到第一输出单元140的输出端子。

200.注意,当第二实施方式(图10)作为基础时,比较单元180和ac波形确定单元190也应当集成在第二芯片100b中。

201.再次参照图16,继续描述封装布局。焊盘p1经由导线w1连接到引脚5(vhdc引脚)。焊盘p2经由导线w2连接到引脚7(vhac引脚)。焊盘p3经由导线w3连接到焊盘p6。焊盘p4经由导线w4连接到焊盘p7。焊盘p5经由导线w5连接到焊盘p8。焊盘p9经由导线w6连接到引脚4

(vcc引脚)。焊盘p10经由导线w7连接到引脚3(gnd引脚)。焊盘p11经由导线w8连接到引脚2(dcout引脚)。焊盘p12经由导线w9连接到引脚1(acout引脚)。

202.注意,关于封装内部的框架区域,引脚1(acout引脚)、引脚4(vcc引脚)、引脚5(vhdc引脚)和引脚7(vhac引脚)中的每一个均大于引脚2(dcout引脚)、引脚3(gnd引脚)和引脚6(n.c.引脚)中的每一个。

203.换句话说,关于x方向(即纸张上的左右方向),引脚1(acout引脚)和引脚4(vcc引脚)具有比引脚2(dcout引脚)和引脚3(gnd引脚)突出的部分。类似地,引脚5(vhdc引脚)和引脚7(vhac引脚)具有比引脚6(n.c.引脚)突出的部分。

204.此外,关于z方向(即纸上的上下方向),引脚1(acout引脚)和引脚4(vcc引脚)与岛100c部分重叠。类似地,引脚5(vhdc引脚)和引脚7(vhac引脚)与岛100c部分重叠。

205.此外,用于支撑岛100c的支撑框架100e和100f分别形成在引脚1(acout引脚)和引脚7(vhac引脚)之间以及引脚4(vcc引脚)和引脚5(vhdc引脚)之间。

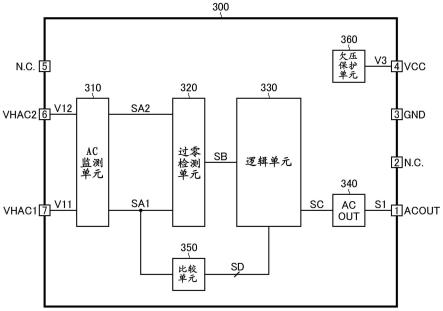

206.注意,在该图的封装布局中,第一芯片100a靠近岛100c上的第二侧(即,靠近引脚5至引脚7)设置,而第二芯片100b靠近第一侧(即,靠近引脚1至引脚4)设置。通过采用这种封装布局,导线w1至w9可以尽可能短。

207.接下来,描述半导体集成电路装置100不是由单芯片结构构成而是由双芯片结构构成的原因。如果处理高电压的ac监测单元110和dc监测单元150双方以及处理低电压的其它电路单元(120至140、160和170)都被集成在单个芯片中,则需要在高耐压处理区域和低耐压处理区域之间设置缓冲区域。因此,芯片尺寸变得非常大,从而导致显著的成本增加。

208.与之相比,如果半导体集成电路装置100由双芯片结构构成,则不需要在第一芯片100a和第二芯片100b中的每一个中设置缓冲区域。因此,可以减小芯片尺寸,结果,可以实现成本降低。此外,第一芯片100a和第二芯片100b是分离的,这对于耐受电压也是非常有利的。

209.接下来,描述第一芯片100a的接地路径。引脚3(gnd引脚)设置在引脚2(dcout引脚)和引脚4(vcc引脚)之间,作为用于阻挡噪声从引脚4(vcc引脚)传播到引脚2(dcout引脚)或引脚1(acout引脚)的屏蔽构件。因此,如果试图直接从第一芯片100a的焊盘p5(即,接地焊盘)引线键合到引脚3(gnd引脚),则不可避免地干扰从第二芯片100b的焊盘p11到引脚2(dcout引脚)的布线w8或从焊盘p12到引脚1(acout引脚)的布线w9。

210.因此,第一芯片100a的焊盘p5(即,接地焊盘)不直接引线键合到引脚3(gnd引脚),而是经由导线w5引线键合到第二芯片100b的焊盘p8。如上述图17中所示,焊盘p8经由形成在第二芯片100b内部的gnd线连接到第二芯片100b的焊盘p10(即,接地焊盘),并且进一步经由导线w7连接到引脚3(gnd引脚)。因此,第一芯片100a的地线经由焊盘p5、导线w5、焊盘p8、形成在第二芯片100b内部的地线、焊盘p10和导线w7连接到引脚3(gnd)。该接地路径可以避免与导线w8或w9的干扰。

211.图18是示意性地示出图16的α-α'横截面的图。如果沿着α-α'线切割半导体集成电路装置100,则从该图可以理解,经由导线w2、第一芯片100a的焊盘p2和焊盘p4、导线w4、第二芯片100b的焊盘p7和焊盘p12以及导线w9形成从引脚7(vhac引脚)到引脚1(acout引脚)的信号路径。

212.此外,从该图中还可以清楚地理解,第一芯片100a和第二芯片100b设置在公共岛

100c上,并用模制树脂100d密封。

213.此外,从该图中还清楚的是,半导体集成电路装置100的外部端子利用焊料220焊接到印刷线路板200的铜线210。

214.《封装布局(第二示例)》

215.图19是示出封装布局的第二示例的图。如该图所示,第一芯片100a和第二芯片100b之间沿z轴方向的位置关系可以与上述第一示例(图16)中的位置关系相反。

216.更具体地,在第一示例(图16)中,在岛100c上,第一芯片100a靠近纸张的上侧设置,而第二芯片100b靠近纸张的下侧设置。相反,在第二示例(图19)中,在同一岛100c上,第一芯片100a靠近纸张的下侧设置,而第二芯片100b靠近纸张的上侧设置。

217.注意,当改变上述芯片布局时,优选如图中所示适当地改变引脚功能和焊盘布置,使得在引脚和焊盘之间的引线键合中不发生阻碍。

218.此外,关于封装内部的框架区域,引脚1(vcc引脚)、引脚4(acout引脚)、引脚5(vhac引脚)和引脚7(vhdc引脚)中的每一个均大于引脚2(gnd引脚)、引脚3(dcout引脚)或引脚6(n.c.引脚)。

219.换句话说,关于x方向(即纸张上的左右方向),引脚1(vcc引脚)和引脚4(acout引脚)具有比引脚2(gnd引脚)和引脚3(dcout引脚)突出的部分。类似地,引脚5(vhac引脚)和引脚7(vhdc引脚)具有比引脚6(n.c.引脚)突出的部分。

220.此外,关于z方向(即纸上的上下方向),引脚1(vcc引脚)和引脚4(cout引脚)与岛100c部分重叠。类似地,引脚5(vhac引脚)和引脚7(vhdc引脚)与岛100c部分重叠。

221.此外,用于支撑岛100c的支撑框架100e和100f分别形成在引脚1(vcc引脚)和引脚7(vhdc引脚)之间以及引脚4(acout引脚)和引脚5(vhac引脚)之间。

222.《电子设备(第三结构示例和第四结构示例)》

223.图20和图21是分别示出电子设备10的第三结构示例(正常整流方法)和第四结构示例(倍压整流方法)的图。这些结构示例的电子设备10分别基于上述的第一结构示例(图1)以及第二结构示例(图2),并且与上述第一结构示例和第二结构示例的不同之处在于,对过零检测电路18的结构进行了修改并且添加了输入电抗器19。

224.因此,具有与第一结构示例和第二结构示例中相同结构的元件由与图1和图2中相同的数字或符号表示,从而省略重复的描述。在下面的描述中,主要描述第三结构示例和第四结构示例的特征部分。

225.如上所述,过零检测电路18是检测ac电压v0的过零的电路块,并且包括半导体集成电路装置300、外部连接到半导体集成电路装置300的二极管d11和d12、以及电容器c11。

226.半导体集成电路装置300是集成有形成过零检测电路18(细节将在后面描述)的电路元件的至少一部分的ic或lsi,并且其具有七个外部端子(引脚1至引脚7)作为用于建立与装置外部的电连接的装置。

227.引脚1(acout引脚)是acout信号s1的输出端子,并且连接到微计算机15。引脚2(n.c.引脚)是未使用的端子并且未连接到半导体集成电路装置300外部的任何地方。引脚3(gnd引脚)是接地端子,并且连接到与微计算机15共用的接地端子gnd。换句话说,半导体集成电路装置300(因此使用该半导体集成电路装置300的过零检测电路18)相对于与微计算机15共用的接地电压进行运作。引脚4(vcc引脚)是电源端子并且连接到ac/dc转换器13的

输出端子(即,第一dc电压v3的输出端子)。注意,电容器c11连接在引脚4和引脚3之间。

228.引脚5(n.c.引脚)是未使用的端子并且未连接到半导体集成电路装置300外部的任何地方。引脚6(vhac2引脚)是第二ac输入端子,并且连接到二极管d12的阴极(对应于监测目标电压v12的输入端子)。二极管d12的阳极连接到l1端子(对应于第二节点)。引脚7(vhac1引脚)是第一ac输入端子,并且连接到二极管d11的阴极(对应于监测目标电压v11的输入端子)。二极管d11的阳极连接到n1端子(对应于第一节点)。

229.注意,如果整流单元12采用正常整流方法(图20)时,l1端子的端子电压和n1端子的端子电压彼此相等。因此,如果二极管d11和d12的阳极连接目的地彼此互换的话没有问题。

230.此外,二极管d11和d12的阳极连接目的地不一定限于l1端子和n1端子。监测目标电压v11和v12可以从其间施加ac电压v0的任意节点取出,而与输入电抗器19的前一级或后一级无关。

231.以提高输入功率因数、降低谐波、降低电动机噪声等为目的而设置输入电抗器19。注意,该图示出了输入电抗器19设置在滤波器11的前一级(l端子侧)上的示例,但是其位置不限于此。输入电抗器19可以设置在滤波器11的n端子侧或后一级上。

232.《半导体集成电路装置(第五实施方式)》

233.图22是示出半导体集成电路装置300的第五实施方式的图。如该图所示,本实施方式的半导体集成电路装置300包括集成的ac监测单元310、过零检测单元320、逻辑单元330、第一输出单元340、比较单元350和欠压保护单元360。

234.ac监测单元310是高压电路单元(例如,具有650v的耐受电压),其根据分别输入到引脚7(vhac1引脚)的监测目标电压v11和输入到引脚6(vhac2引脚)的监测目标电压v12,生成适应于输入到过零检测单元320的ac监测信号sa1和sa2。注意,监测目标电压v11和v12分别对应于经由二极管d11和d12从其间施加ac电压v0的n1端子和l1端子输入的第一监测目标信号和第二监测目标信号。

235.过零检测单元320将ac监测信号sa1与ac监测信号sa2进行比较,以生成比较信号sb。

236.逻辑单元330根据比较信号sb估计ac电压v0的过零,从而生成过零检测信号sc。此外,逻辑单元330还具有根据比较信号sd的检测结果来停止过零检测信号sc的生成或输出的功能(即,ac波形确定功能)。该ac波形确定功能基本上与上述ac波形确定单元190的功能相同,并且省略重复的描述。

237.第一输出单元340接收过零检测信号sc的输入以生成acout信号s1,并将acout信号s1输出到引脚1(acout引脚)。注意,第一输出单元340应当具有与图7的第一输出单元140基本相同的结构。换句话说,图7中的“过零检测信号sc”可以由“过零检测信号sc”代替,从而可以理解第一输出单元340的结构和操作。

238.比较单元350将ac监测信号sa1与多个阈值中的每一个进行比较,以生成多个比较信号sd。注意,比较单元350应当具有与图10的比较单元180基本相同的结构。换句话说,图10的“ac监测信号sa”可以用“ac监测信号sa1”代替,并且可以用“比较信号sd”来代替“比较信号sd1至sd4”,从而可以理解比较单元350的结构和操作。关于要与ac监测信号sa1进行比较的多个阈值,例如,不仅可以设置用于检测瞬时电力故障的阈值,而且可以设置用于检测

uvlo的阈值。

239.欠压保护单元360是保护功能单元(所谓的uvlo保护单元),其在输入到引脚4(vcc)的第一dc电压v3低于下限值时禁用半导体集成电路装置300的操作。

240.《过零检测单元(第一示例)》

241.图23是示出过零检测单元320的第一示例的图。该示例的过零检测单元320包括比较器321,比较器321将输入到非反相输入端子(+)的ac监测信号sa1与输入到反相输入端子(-)的ac监测信号sa2进行比较,以生成比较信号sb。当sa1》sa2成立时,比较信号sb为高电平,而当sa1《sa2成立时,比较信号sb为低电平。

242.设置在过零检测单元320的前一级的ac监测单元310包括电阻器311至314。电阻器311和312串联连接在引脚7(vhac1)和引脚3(gnd)之间,以便从电阻器311和312的连接节点输出ac监测信号sa1(对应于监测目标电压v11的分压)。电阻器313和134串联连接在引脚6(vhac2)和引脚3(gnd)之间,以便从电阻器313和134的连接节点输出ac监测信号sa2(对应于监测目标电压v12的分压)。

243.注意,在该图中,为了简单描述,仅示出电阻器311至314作为ac监测单元310的结构元件,但是实际上,类似于图5的ac监测单元110,优选包括各种静电保护元件。

244.《过零检测过程(第一示例至第三示例)》

245.接下来,描述半导体集成电路装置300的过零检测过程。图24是示出过零检测过程的第一示例的时序图,其中ac电压v0、监测目标电压v11和v12以及acout信号s1按从上到下的顺序依次示出。特别地,该图示出了监测目标电压v11和v12在ac电压v0的过零处彼此交叉的理想状态。

246.半导体集成电路装置300以伪方式分别监测ac电压v0两端的电压(即n1端子处的端子电压和l1端子处的端子电压)作为监测目标电压v11和v12,并且根据其比较结果切换acout信号s1的逻辑电平。参考该图,当v11》v12成立时,acout信号s1为高电平,而当v11《v12成立时,acout信号s1为低电平。

247.在这种情况下,acout信号s1的上升定时基本上与ac电压v0从负切换到正(即,在从负到正的过零处)时的定时相同(见时间点t41、t43和t45)。相反,acout信号s1的下降定时与ac电压v0从正切换到负(即,在从正到负的过零处)时的定时基本相同(见时间点t42、t44和t46)。

248.图25是示出过零检测过程的第二示例的时序图,其中ac电压v0、ac监测信号sa1(实线)和sa2(虚线)以及比较信号sb按从上到下的顺序依次示出。注意,该图示出了在整流单元12采用倍压整流方法(图21)的情况下的行为。

249.如该图所示,在实际的电子设备10中,由于输入电抗器19的影响,ac监测信号sa1、sa2的波形大幅失真。特别地,ac监测信号sa1的上升速度易于根据负载z而变化,因此比较信号sb的上升定时可能极大地变化。相反,ac监测信号sa1的下降速度不易于根据负载z而变化,因此比较信号sb的下降定时具有相对小的变化。

250.从以上考虑,优选地,逻辑单元330应当检测比较信号sb的下降定时(即,当sa1》sa2切换到sa1《sa2以及ac监测信号sa1减小时的定时),以便基于检测到的下降定时来估计ac电压v0的过零。

251.图26是示出过零检测过程的第三示例的时序图,其中ac电压v0、ac监测信号sa1

(实线)和sa2(虚线)、比较信号sb、边缘检测信号edge(即,逻辑单元330的内部信号)和过零检测信号sc按从上到下的顺序依次示出。注意,该图示出了在整流单元12采用倍压整流方法(图21)的情况下的行为。

252.如时间点t51至t55所示,在逻辑单元330内部,在比较信号sb的每个下降定时,在边缘检测信号edge上产生脉冲。然后,逻辑单元330对边缘检测信号edge的脉冲间隔(即,比较信号sb的周期t)进行计数,以便使用计数值来估计ac电压v0的过零。

253.更具体地,在ac电压v0具有恒定周期和恒定相位的前提下,逻辑单元330参考比较信号sb的周期t,以确定过零检测信号sc的上升定时和下降定时。

254.例如,逻辑单元330在比较信号sb下降到低电平的时间点(例如,时间点t53)将过零检测信号sc从高电平降低到低电平。过零检测信号sc的该下降定时基本上与ac电压v0从负切换到正(即,过零从负切换到正)时的定时相同。

255.此外,逻辑单元330从比较信号sb下降到低电平的时间点开始对与预先获得的周期t相对应的待机时间t3(例如t3=t/2)进行计数,并且在待机时间t3过去的时间点将过零检测信号sc从低电平增大到高电平。过零检测信号sc的上升定时与ac电压v0从正切换到负(即,过零从正切换到负)时的定时基本相同。

256.《过零检测单元(第二示例)》

257.图27是示出过零检测单元320的第二示例的图。该示例的过零检测单元320基于第一示例(图23),并且还包括比较器322。比较器322将输入到非反相输入端子(+)的ac监测信号sa1与输入到反相输入端子(-)的预定阈值vth(例如,vth=20mv)进行比较,从而生成比较信号sb2。当sa1》vth成立时,比较信号sb2为高电平,而当sa1《vth成立时,比较信号sb2为低电平。

258.在下面的描述中,参照半导体集成电路装置300的过零检测过程来描述引入比较器322的意义。

259.《过零检测过程(第四示例至第六示例)》

260.图28是示出过零检测过程的第四示例的时序图,其中ac电压v0、ac监测信号sa1(实线)和sa2(虚线)、比较信号sb和sb2、边缘检测信号edge和过零检测信号sc按从上到下的顺序依次示出。注意,该图示出了在整流单元12采用倍压整流方法(图21)的情况下的行为。

261.如该图所示,当ac监测信号sa1和sa2都下降至接近0v时,比较信号sb的逻辑电平可能变得不稳定,从而可能引起抖动。

262.因此,当ac监测信号sa1低于预定阈值vth时,逻辑单元330对比较信号sb2而不是比较信号sb的周期t进行计数,并且使用该计数值来估计ac电压v0的过零。

263.具体地,如时间点t61至t65中的每一个所示,在逻辑单元330内部,在比较信号sb2的每个下降定时在边缘检测信号edge中生成脉冲。然后,逻辑单元330对边缘检测信号edge的脉冲间隔(即,比较信号sb2的周期t)进行计数,以便使用计数值来估计ac电压v0的过零。

264.例如,逻辑单元330在比较信号sb2下降到低电平的时间点(例如,在时间点t63)将过零检测信号sc从高电平降低到低电平。过零检测信号sc的该下降定时基本上与ac电压v0从负切换到正(即,过零从负切换到正)时的定时相同。

265.此外,逻辑单元330从比较信号sb2下降到低电平的时间点开始对与预先获得的周

期t相对应的待机时间t3(例如t3=t/2)进行计数,并且在待机时间t3过去的时间点将过零检测信号sc从低电平增大到高电平。过零检测信号sc的上升定时与ac电压v0从正切换到负(即,过零从正切换到负)时的定时基本相同。

266.图29和图30是分别示出过零检测过程的第五示例和第六示例的时序图,其中ac电压v0、ac监测信号sa1(实线)和sa2(虚线)、比较信号sb和sb2、边缘检测信号edge和过零检测信号sc按从上到下的顺序依次示出。注意,时序图示出了在整流单元12采用倍压整流方法(图21)的情况下的行为。

267.如图中所示,逻辑单元330具有屏蔽功能,作为针对比较信号sb2中的抖动的措施。具体地,如果在比较信号sb2从高电平下降到低电平之后的预定屏蔽时段tm期间比较信号sb没有保持在低电平,则逻辑单元330忽略比较信号sb2的下降沿。

268.利用该屏蔽功能,即使在比较信号sb2中发生抖动,也不会生成边缘检测信号edge所不需要的脉冲,因此在ac电压v0的过零检测过程中不会发生障碍。

269.注意,应当在逻辑单元330内适当地调整屏蔽时段tm的长度。此外,待机时间t3的计数开始定时可以是边缘检测信号edge的脉冲生成定时,而不是比较信号sb2的下降定时。在这种情况下,通过将待机时间t3设置为t/2-tm,可以将过零检测信号sc的上升定时调整为ac电压v0的过零。

270.《电子设备(第五个结构示例)》

271.图31是示出电子设备10的第五结构示例(正常整流方法,单侧继电器)的图。该结构示例的电子设备10基于上述第三结构示例(图20),并且与上述第三结构示例的不同之处在于继电器开关20设置在n端子侧。因此,具有与第三结构示例中相同结构的元件由与图20中相同的数字或符号表示,从而省略了重复的描述。在下面的描述中,主要描述第五结构示例的特征部分。

272.如该图所示,在该结构示例的电子设备10中,当电源关断时,继电器开关20断开,并且n端子开路。在这种情况下,如果l1端子和n1端子彼此完全绝缘,则即使ac电压v0连续地施加到l1端子,n1端子也保持在高阻抗状态,因此监测目标电压v11和v12不变为相同的电势。

273.然而,实际上,在l1端子和n1端子之间存在泄漏路径(即,电阻部件r)。因此,在继电器开关20断开之后,监测目标电压v11和v12变为相同电势(相同相位)。因此,在比较信号sb中可能发生抖动,使得在acout信号s1中可能发生不期望的脉冲输出。

274.注意,该图例示了整流单元12采用正常整流方法的情况,但是在整流单元12采用倍压整流方法的情况下可能发生与上述相同的故障。

275.《半导体集成电路装置(第六实施方式)》

276.图32是示出半导体集成电路装置300的第六实施方式的图。本实施方式的半导体集成电路装置300基于上述第五实施方式(图22)并且还包括输入停止检测单元370。因此,具有与第五实施方式中相同结构的元件由与图22中相同的数字或符号表示,以便省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

277.输入停止检测单元370包括偏置电源371和比较器372。

278.偏置电源371将ac监测信号sa1上拉预定的偏置电压vofs(例如,vofs=20v至40v),以便将结果输出到比较器372。

279.比较器372将输入到非反相输入端子(+)的偏移(sa1+vofs)后的ac监测信号与输入到反相输入端子(-)的ac监测信号sa2进行比较,从而生成输入停止检测信号se。因此,当sa1+vofs》sa2成立时,输入停止检测信号se为高电平,而当sa1+vofs《sa2成立时,输入停止检测信号se为低电平。

280.换句话说,在继电器开关20断开之后,当ac监测信号sa1和sa2变为相同相位(或相同电势)时,sa1+vofs》sa2总是成立,因此输入停止检测信号se不下降到低电平。

281.逻辑单元330检测到输入停止检测信号se保持在高电平,并将过零检测信号sc固定在高电平。结果,即使在比较信号sb中发生不期望的抖动,acout信号s1也可以固定在低电平。因此,在继电器开关20断开之后,可以可靠地停止acout信号s1中的脉冲输出。

282.注意,设置为,如果在输入停止检测信号se上升到高电平之后,输入停止检测信号se在预定屏蔽时段tmask(》t)内没有保持在高电平,则逻辑单元330忽略该上升。

283.通过这种布置,只要ac监测信号sa1和sa2之间的高低关系被周期性地反转,过零检测信号sc就不会被固定为高电平,因此在acout信号s1的正常输出操作中不会出现障碍。

284.《输出脉冲停止过程》

285.图33是示出电源关断时的输出脉冲停止过程的一个示例的时序图,其中ac监测信号sa1(实线)和sa2(虚线)、过零检测信号sc和输入停止检测信号se按从上到下的顺序依次示出。

286.在时间点t91之前,继电器开关20接通。因此,ac监测信号sa1和sa2之间的高低关系被周期性地反转,并且分别在过零检测信号sc和输入停止检测信号se中生成周期性脉冲。注意,如上所述,除非输入停止检测信号se在屏蔽时段tmask(》t)内保持为高电平,否则过零检测信号sc不固定为高电平。

287.当继电器开关20在时间点t91断开时,ac监测信号sa1和sa2变为相同相位,因此输入停止检测信号se不下降到低电平。然而,在该时间点没有经过屏蔽时段tmask,因此过零检测信号sc没有固定为高电平。

288.此后,当在输入停止检测信号se保持在高电平的同时在时间点t92经过屏蔽时段tmask时,在确定ac监测信号sa1和sa2具有相同相位的情况下,过零检测信号sc被固定在高电平。因此,可以可靠地停止acout信号s1中的脉冲输出。

289.注意,本实施方式的半导体集成电路装置300基于第五实施方式(图22),但是过零检测方法并不关心何时引入输入停止检测单元370。例如,图32的过零检测单元320和逻辑单元330可以由图4的峰值检测单元120和过零检测单元130替换。注意,当执行该替换时,ac监测信号sa1和sa2中的仅一个(例如,ac监测信号sa1)应当被输入到峰值检测单元120。

290.《封装布局(第三示例)》

291.图34是示出半导体集成电路装置300的封装布局的第三示例的图(xz平面图)。在该图的半导体集成电路装置300中,第一芯片300a和第二芯片300b安装在岛300c上。

292.首先,参照附图详细描述第一芯片300a和第二芯片300b的内部结构。图35是示出第一芯片300a和第二芯片300b的内部结构的图,并且示出了基于第五实施方式(图22)的一个示例。

293.第一芯片300a包括集成的ac监测单元310。此外,第一芯片300a具有焊盘p21至焊盘p25作为用于建立与芯片外部的电连接的装置。在第一芯片300a内部,焊盘p21连接到ac

监测单元310的第一输入端子(对应于监测目标电压v11的输入端子)。焊盘p22连接到ac监测单元310的第二输入端子(对应于监测目标电压v12的输入端子)。焊盘p23连接到ac监测单元310的第一输出端子(对应于ac监测信号sa1的输出端子)。焊盘p24连接到ac监测单元310的第二输出端子(对应于ac监测信号sa2的输出端子)。焊盘p25连接到地线。

294.与之相比,第二芯片300b包括集成的过零检测单元320、逻辑单元330、第一输出单元340、比较单元350和欠压保护单元360。此外,第二芯片300b具有焊盘p26至焊盘p31作为用于建立与芯片外部的电连接的装置。在第二芯片300b内部,焊盘p26连接到过零检测单元320的第一输入端子(对应于ac监测信号sa1的输入端子)。焊盘p27连接到过零检测单元320的第二输入端子(对应于ac监测信号sa2的输入端子)。焊盘p28连接到地线。焊盘p29连接到欠压保护单元360的输入端子(即,电源线)。焊盘p30连接到地线。焊盘p31连接到第一输出单元340的输出端子。

295.注意,当第六实施方式(图32)作为基础时,输入停止检测单元370也应当集成在第二芯片300b中。

296.再次参照图34,继续描述封装布局。焊盘p21经由导线w21连接到引脚7(vhac1引脚)。焊盘p22经由导线w22连接到引脚6(vhac2引脚)。焊盘p23经由导线w23连接到焊盘p26。焊盘p24经由导线w24连接到焊盘p27。焊盘p25经由导线w25连接到焊盘p28。焊盘p29经由导线w26连接到引脚4(vcc引脚)。焊盘p30经由导线w27连接到引脚3(gnd引脚)。焊盘p31经由导线w28连接到引脚1(acout引脚)。

297.注意,关于封装内部的框架区域,引脚1(acout引脚)、引脚4(vcc引脚)、引脚5(n.c.引脚)和引脚7(vhac1引脚)中的每一个均大于引脚2(n.c.引脚)、引脚3(gnd引脚)或引脚6(vhac2引脚)。

298.换句话说,关于x方向(即纸张上的左右方向),引脚1(acout引脚)和引脚4(vcc引脚)具有比引脚2(n.c.脚)和引脚3(gnd引脚)突出的部分。类似地,引脚5(n.c.引脚)和引脚7(vhac1引脚)具有比引脚6(vhac2引脚)突出的部分。

299.此外,关于z方向(即纸上的上下方向),引脚1(acout引脚)和引脚4(vcc引脚)与岛300c部分重叠。类似地,引脚5(n.c.引脚)和引脚7(vhac1引脚)与岛300c部分重叠。

300.此外,支撑岛300c的支撑框架300e和300f分别形成在引脚1(acout引脚)和引脚7(vhac1引脚)之间以及引脚4(vcc引脚)和引脚5(n.c.引脚)之间。

301.注意,芯片的相对位置、双芯片结构的优点以及第一芯片300a的接地路径与上述第一示例(图16)和第二示例(图19)中描述的相同,并且省略重复描述。

302.《封装布局(第四示例)》

303.图36是示出半导体集成电路装置300的封装布局的第四示例的图(xz平面图)。在该图的半导体集成电路装置300中,类似于上述第三示例(图34),第一芯片300a和第二芯片300b安装在岛300c上。此外,在该图的半导体集成电路装置300中,随着dc监测单元的并入(细节将在后面描述),封装引脚的数量从“7”增加到“11”304.首先,参照附图详细描述第一芯片300a和第二芯片300b的内部结构。图37是示出第一芯片300a和第二芯片300b的内部结构的图,并且示出了其中添加了dc监测单元380和第二输出单元390的基于第五实施方式(图22)的结构。

305.注意,第一芯片300a和第二芯片300b的内部结构与上述图35中基本相同。因此,在

下面的描述中,主要描述了从图35中修改而来的部分。

306.第一芯片300a还包括集成的dc监测单元380。dc监测单元380是高压电路块(例如,具有650v的耐受电压),其根据输入到引脚9(vhdc引脚)的整流电压v1生成dc监测信号sx,并且对应于第一至第四实施方式中的dc监测单元150。

307.此外,将焊盘p32和焊盘p33与dc监测单元380的集成一起添加到第一芯片300a。在第一芯片300a内部,焊盘p32连接到dc监测单元380的输入端子。焊盘p33连接到dc监测单元380的输出端子。

308.与之相比,第二输出单元390附加地集成到第二芯片300b。第二输出单元390是接收dc监测信号sx的输入以生成dcout信号s2并将dcout信号s2输出到引脚4(dcout引脚)的电路块,并且其对应于第一至第四实施方式中的第二输出单元160。

309.此外,将焊盘p34和p35与第二输出单元390的集成一起添加到第二芯片300b。在第二芯片300b内部,焊盘p34连接到第二输出单元390的输入端子。焊盘p35连接到第二输出单元390的输出端子。

310.再次参照图36,继续描述封装布局。焊盘p21经由导线w21连接到引脚11(vhac1引脚)。焊盘p22经由导线w22连接到引脚10(vhac2引脚)。焊盘p23经由导线w23连接到焊盘p26。焊盘p24经由导线w24连接到焊盘p27。焊盘p25经由导线w25连接到焊盘p28。焊盘p29经由导线w26连接到引脚7(vcc引脚)。焊盘p30经由导线w27连接到引脚5(gnd引脚)。焊盘p31经由导线w28连接到引脚3(acout引脚)。焊盘p32经由导线w29连接到引脚9(vhdc引脚)。焊盘p33经由导线w30连接到焊盘p34。焊盘p35经由导线w31连接到引脚4(dcout引脚)。

311.注意,对于封装内部的框架区域,引脚2(n.c.引脚)和引脚6(n.c.引脚)中的每一个均大于引脚3(acout引脚)、引脚4(dcout引脚)或引脚5(gnd引脚)。

312.换句话说,关于x方向(即纸张上的左右方向),引脚2(n.c.引脚)和引脚6(n.c.引脚)具有比引脚3(acout引脚)、引脚4(dcout引脚)和引脚5(gnd引脚)突出的部分。

313.此外,关于z方向(即纸张上的上下方向),引脚2(n.c.引脚)和引脚6(n.c.引脚)没有与岛100c重叠的部分。与此类似,引脚1(n.c.引脚)、引脚7(vcc引脚)、引脚8(n.c.引脚)和引脚11(vhac1引脚)也没有与岛100c重叠的部分。

314.此外,支撑岛300c的支撑框架300e和300f分别形成在引脚1(n.c.引脚)和引脚11(vhac1引脚)之间以及引脚7(vcc引脚)和引脚8(n.c.引脚)之间。

315.《ac监测单元和dc监测单元》

316.图38是示出上述图37中的ac监测单元310和dc监测单元380的一个结构示例的图。该结构示例的ac监测单元310包括电阻器311a至315a和311b至315b、nmosfet 316a和316b、pmosfet 317a和317b以及熔丝318a和318b。

317.电阻器311a至315a按所示顺序串联连接在焊盘p21(vhac1焊盘)和焊盘p25(gnd焊盘)之间。注意,电阻器313a和电阻器314a的连接节点连接到焊盘p23(acin1焊盘)。换句话说,电阻器311a至315a用作分压器电路,其对输入到焊盘p21的监测目标电压v11(即,第一监测目标信号)进行分压,以生成ac监测信号sa1。

318.与之相比,电阻器311b至315b以所示顺序串联连接在焊盘p22(vhac2焊盘)和焊盘p25(gnd焊盘)之间。电阻器313b和电阻器314b的连接节点连接到焊盘p24(acin2焊盘)。换句话说,电阻器311b至315b用作分压器电路,其对输入到焊盘p22的监测目标电压v12(即,

第二监测目标信号)进行分压,以生成ac监测信号sa2。

319.注意,在电阻器311a至315a和电阻器311b至315b中,电阻器311a和电阻器311b对应于第一反馈电阻器。此外,电阻器312a至315a和电阻器312b至315b对应于第二反馈电阻器。具体地,在第二反馈电阻器中,电阻器312a和315a以及电阻器312b和315b的每个电阻值可以通过使用熔丝318a和318b进行微调来任意调整。

320.nmosfet 316a的漏极连接到焊盘p21。nmosfet 316a的源极、栅极和背栅极连接到焊盘p25。pmosfet 317a的漏极连接到焊盘p25。pmosfet 317a的源极、栅极和背栅极连接到焊盘p23。

321.nmosfet 316b的漏极连接到焊盘p22。nmosfet 316b的源极、栅极和背栅极连接到焊盘p25。pmosfet 317b的漏极连接到焊盘p25。pmosfet 317b的源极、栅极和背栅极连接到焊盘p22。

322.以这种方式连接的nmosfet 316a和316b以及pmosfet 317a和317b中的每一个都用作静电保护元件。

323.与之相比,该结构示例的dc监测单元380包括电阻器381至385、nmosfet 386、pmosfet 387和熔丝388。

324.电阻器381至385按所示顺序串联连接在焊盘p32(vhdc焊盘)和焊盘p25(gnd焊盘)之间。注意,电阻器383和电阻器384的连接节点连接到焊盘p33(dcin焊盘)。换句话说,电阻器381至385用作分压器电路,其对输入到焊盘p32的整流电压v1(即,第三监测目标信号)进行分压,以生成dc监测信号sx。

325.注意,在电阻器381至385中,电阻器381对应于第一反馈电阻器,电阻器382至385对应于第二反馈电阻器。具体地,在第二反馈电阻器中,可以通过使用熔丝388进行微调来任意地调整电阻器382和385的每个电阻值。

326.nmosfet 386的漏极连接到焊盘p32。nmosfet 386的源极、栅极和背栅极连接到焊盘p25。pmosfet 387的漏极连接到焊盘p25。pmosfet 387的源极、栅极和背栅极连接到焊盘p33。

327.以这种方式连接的nmosfet 386和pmosfet 387(以及伴随其的体二极管)用作静电保护元件。

328.《芯片布局(第一个芯片)》

329.图39是示出第一芯片300a的布局的图。注意,为了避免复杂性,未示出形成在第一芯片300a中的布线。此外,在下面的描述中,为了便于描述,纸张上的上、下、左和右方向被定义为第一芯片300a的平面图中的上、下、左和右方向,以便描述焊盘或元件的位置关系。

330.在平面图中,第一芯片300a被切割成矩形形状,该矩形形状在短边(右侧或左侧)和长边(上侧或下侧)之间具有基本上相等的比率(精确地说,略微横向的矩形形状)。

331.在第一芯片300a的平面图中,区域a1(即,第一芯片300a的大致左半区域)包括在第一芯片300a的上下方向上形成和布置的三个高压区域400x至400z(稍后描述细节)。一对电阻器311a和焊盘p21(vhac1)、一对电阻器311b和焊盘p22(vhac2)以及一对电阻器381和焊盘p32(vhdc)分别形成在高压区域400x至400z中。

332.与之相比,在第一芯片300a、焊盘p23至焊盘p25和焊盘p33的平面图中,电阻器312a至315a、312b至315b和382至385、nmosfet 316a、316b和386、pmosfet 317a、317b和387

以及熔丝318a、318b和388形成在区域a2(即,第一芯片300a的大致右半侧区域)中。

333.在第一芯片300a的平面图中,焊盘p23至焊盘p25和焊盘p33形成并布置在第一芯片300a的左右方向上,从第一芯片300a的上下方向上的中间略向上侧(即,在从高压区域400y和400z之间的边界向右延伸的线上)。注意,焊盘应当以例如焊盘p33(dcin)、焊盘p24(acin2)、焊盘p23(acin1)和焊盘p25(gnd)从纸张左侧依次布置的方式布置。此外,焊盘p23和焊盘p25之间的焊盘间距离应当大于焊盘p23和焊盘p24之间的焊盘间距离或者焊盘p24和焊盘p33之间的焊盘间距离。

334.在第一芯片300a的平面图中,电阻器312a至315a形成在比焊盘p23至焊盘p25和焊盘p33更靠近第一芯片300a的下侧的位置处,并且形成在与高压区域400x的右侧相邻的位置处(更具体地,形成在高压区域400x的上下方向上从中间稍微向上侧的位置处)。此外,在纸张上的左右方向上,在第一芯片300a的平面图中,电阻器312a至315a从与焊盘p33(dcin)的左侧基本上相同的线上的位置形成到与焊盘p23(acin1)的左侧基本上相同的线上的位置。

335.在第一芯片300a的平面图中,电阻器312b至315b形成在比焊盘p23至焊盘p25和焊盘p33更靠近第一芯片300a的下侧的位置处(更具体地,形成在电阻器312a至315a与焊盘p23至焊盘p25和焊盘p33之间的位置处),并且形成在与高电压区域400y的右侧相邻的位置处(更具体地,在接近高压区域400y的下侧的位置处)。此外,在纸张上的左右方向上,与电阻器312a至315a类似,在第一芯片300a的平面图中,电阻器312b至315b从与焊盘p33(dcin)的左侧基本上相同的线上的位置形成到与焊盘p23(acin1)的左侧基本上相同的线上的位置。

336.在第一芯片300a的平面图中,电阻器382至385形成在比焊盘p23至焊盘p25和焊盘p33更靠近第一芯片300a的上侧的位置处,并且形成在与高压区域400z的右侧相邻的位置处(更具体地,形成在靠近高压区域400z的上侧的位置处)。此外,在纸张上的左右方向上,与电阻器312a至315a和312b至315b类似,在第一芯片300a的平面图中,从与焊盘p33(dcin)的左侧基本上相同的线上的位置到与焊盘p23(acin1)的左侧基本上相同的线上的位置形成电阻器382至385。

337.注意,电阻器312a和315a、电阻器312b和315b以及电阻器382和385各自具有多个单位电阻器,并且可以使用熔丝318a、318b和388任意改变其连接状态(串联连接的数目和并联连接的数目)。

338.在第一芯片300a的平面图中,在第一芯片300a的上下方向上形成和布置nmosfet 316a、316b和386。参照该图,nmosfet 316a形成在焊盘p25下方,并且nmosfet 316b形成在焊盘p25上方。此外,nmosfet 386进一步形成在nmosfet 316b上方(即,在第一芯片300a的右上角上)。

339.在第一芯片300a的平面图中,pmosfet 317a形成在焊盘p23与第一芯片300a的下侧之间的大致中间位置处。与之相比,在第一芯片300a的平面图中,pmosfet 317b形成在焊盘p33和高压区域400y之间的位置处。此外,在第一芯片300a的平面图中,pmosfet 387形成在焊盘p33和高压区域400z之间的位置处。注意,pmosfet 317b和387形成并布置在第一芯片300a的上下方向上。

340.在第一芯片300a的平面图中,在第一芯片300a的上下方向上形成并布置熔丝

318a、318b和388。参照该图,熔丝318a形成在pmosfet 317a和第一芯片300a的下侧之间,熔丝318b形成在焊盘p23和pmosfet 317a之间。此外,熔丝388形成在焊盘p23和第一芯片300a的上侧之间。注意,熔丝318a、318b和388中的每一个可以理解为包括多个熔丝元件的熔丝元件组。

341.注意,优选使用具有100v或更高(例如,650v)的耐受电压的多晶硅电阻器作为被施加高电压的电阻器311a、311b和381。特别地,当集成上述电阻器时,不仅需要(在横向方向上)通过电阻器的路径的高耐受电压,而且需要(在垂直方向上)每个电阻器与半导体基板之间的高耐受电压。

342.因此,在集成有ac监测单元310和dc监测单元380的第一芯片300a中,优选地在基板厚度方向(在垂直方向)上形成具有比其它区域高的耐受电压的三个高压区域400x至400z,并且分别在高压区域400x至400z上形成电阻器311a和311b以及电阻器381。

343.注意,作为上述三个高电压区域400x至400z,可以使用具有高耐受电压的丰富结果的横向双扩散mosfet(ldmosfet)区域。在下面的描述中,具体描述ldmosfet区域的结构。

344.《高压区域(ldmosfet区域)》

345.图40和图41分别是示出第一芯片300a的一个结构示例(具体地,分别位于高压区域400x至400z的中间的反馈电阻器形成的区域及其附近)的纵向截面视图和俯视图。注意,图40的纵向截面视图示例性地示出了图41的α1-α2横截面。

346.该图的第一芯片300a包括p型半导体基板410,并且用作高压区域400(对应于上述高压区域400x至400z)的ldmosfet区域形成在p型半导体基板410上。更具体地,在p型半导体基板410上,低浓度n型半导体区域411和围绕该低浓度n型半导体区域411的高浓度p型半导体区域412形成在高压区域400的中间部分中。注意,通过降低低浓度n型半导体区域411中的杂质浓度或通过增加低浓度n型半导体区域411的厚度来增加高电压区域400中的基板的厚度方向上的耐受电压。

347.高浓度n型半导体区域413形成在低浓度n型半导体区域411中,高浓度n型半导体区域414形成在高浓度p型半导体区域412中。这些高浓度n型半导体区域413和414分别对应于ldmosfet的漏极区域(d)和源极区域(s)。注意,如图41所示,在平面图中,多个同心环状漏极区域(d)和源极区域(s)交替形成在高压区400中。

348.另外,在低浓度n型半导体区域411的外表面层上,以包围高浓度n型半导体区域413的方式形成场氧化膜415。此外,在p型半导体基板410的表面层上,形成栅极氧化膜416以桥接在高浓度n型半导体区域414和场氧化膜415之间。注意,在栅极氧化膜416上形成由多晶硅制成的栅极区域417。

349.此外,在场氧化膜415上,形成由多晶硅制成的场板418,作为均衡电场分布(即等电位线之间的间隔)的手段,以防止介质击穿。

350.另外,在场氧化膜415的正下方形成低浓度p型半导体区域419,作为在场氧化膜415与低浓度n型半导体区域411之间形成寄生电容的装置。根据该结构,能够与寄生电容所保持的电压相对应地提高基板的厚度方向上的耐受电压。

351.此外,在被高浓度n型半导体区域413(对应于最内漏极区域(d))围绕的低浓度n型半导体区域411的中间部分的表面层上,形成场氧化物膜402,并且在该场氧化物膜402上形成反馈电阻器401(即电阻器311a、311b或381)。注意,反馈电阻器401应当使用与栅极区域

417和场板418相同的多晶硅层形成。

352.此外,在该示出的示例中,反馈电阻器401的两端分别通过通孔连接到第一金属层1m,并且进一步地,第一金属层1m通过通孔连接到第二金属层2m。例如,焊盘403(即,焊盘p21、p22或p32)应当形成在第二金属层2m上。然而,金属层的数目不限于此。可以仅有一层,或者可以有三层或更多层。

353.进一步地,如图41所示,优选通过组合多个单位电阻器401(1)至401(m)(m≥2)来形成反馈电阻器401。例如,如果一个单位电阻器的电阻值是1mω,则应当串联连接十个单位电阻器,以便使反馈电阻器401具有10mω的组合电阻。

354.以这种方式,通过使用ldmosfet区域(例如,具有600v的耐受电压)作为高压区域400,可以实现反馈电阻器401和p型半导体基板410之间的高耐受电压。

355.《芯片布局(第二芯片)》

356.图42是示出第二芯片300b的布局的图。在下面的描述中,为了便于描述,纸张上的上、下、左和右方向被定义为第二芯片300b的平面图中的上、下、左和右方向,以便描述焊盘或电路块的位置关系。

357.注意,在该图中,除了上面已经参考图37描述的焊盘p26至焊盘p31和焊盘p34至焊盘p35之外,还新示出了用于芯片测试的焊盘p41至焊盘p49。对焊盘p41至焊盘p49进行简要描述。焊盘p41(scanin)、焊盘p42(scanmode)、焊盘p43(scanclk)、焊盘p44(scanrst)、焊盘p45(scanen)和焊盘p49(scanout)是用于扫描通过测试的焊盘组(测试信号输入焊盘、模式切换信号输入焊盘、时钟信号输入焊盘、复位信号输入焊盘、使能信号输入焊盘和测试信号输出焊盘)。焊盘p46(tsd)是温度保护信号输出焊盘。焊盘p47(vcla)是模拟电路的测试电压施加焊盘。焊盘p48(vcld)是数字电路的测试电压施加焊盘。

358.在平面图中,第二芯片300b被切割成纵向矩形形状,其中右侧和左侧比上侧和下侧长。

359.在第二芯片300b的平面图中,在第二芯片300b的左侧附近,在纸张上在上下方向上按照从上到下的顺序依次形成和布置有焊盘p34(dcin)、焊盘p27(acin2)、焊盘p26(acin1)、焊盘p28(gnd)、焊盘p31(acout)和焊盘p49(scanout)。

360.相比较,在第二芯片300b的平面图中,在第二芯片300b的右侧附近,在纸张上在上下方向上按照从上到下的顺序依次形成和布置有焊盘p41(scanin)、焊盘p42(scanmode)、焊盘p43(scanclk)、焊盘p44(scanrst)、焊盘p45(scanrst)、焊盘p46(tsd)、焊盘p47(vcla)和焊盘p48(vcld)。

361.此外,在第二芯片300b的平面图中,在第二芯片300b的下侧附近,在纸张上在左右方向上按照从左到右的顺序依次形成和布置有焊盘p35(dcout)、焊盘p30(gnd)和焊盘p29(vcc)。

362.焊盘p26和焊盘p27优选相互靠近放置。优选地,焊盘p27和焊盘p34之间的焊盘间距离大于焊盘p26和焊盘p27之间的焊盘间距离。优选地,将焊盘p28(gnd)设置在焊盘p26(acin1)和焊盘p31(acout)之间。优选地,将焊盘p30(gnd)设置在焊盘p29(vcc)和焊盘p35(dcout)之间。静电保护元件(28vpd或ebz)形成在焊盘p26至焊盘p28、焊盘p31和焊盘p34至焊盘p35的正下方。test块(测试电路)分别形成在焊盘p41和焊盘p42之间以及焊盘p43和焊盘p44之间。

363.在第二芯片300b的平面图中,在靠近焊盘p26至焊盘p28、焊盘p31和焊盘p34的区域(即,占据第二芯片300b的左侧的大约1/4和上侧的大约3/4的区域,除了焊盘形成区域之外)中,形成acdet块(对应于比较单元350)、acmon块(即,设置在zerodet块的前一级上的rc滤波器,图37中未示出)、zerodet块(对应于过零检测单元320)、zerodet02v块(对应于输入停止检测单元370)和acoui块(对应于第一输出单元340)。

364.acmon块、zerodet块和zerodet02v块中的每一个形成在从邻近焊盘p26的位置到邻近焊盘p31的位置的纵向区域中。此外,在第二芯片300b的左右方向上形成并布置有acmon块、zerodet块和zerodet02v块。

365.在第二芯片300b的上侧与acmon块的上侧、zerodet块的上侧和zerodet02v块的上侧之间的区域中形成acdet块。注意,acdet块具有比acmon块、zerodet块和zerodet02v块中的每一个更大的面积。

366.acout块形成在从acmon块的下侧、zerodet块的下侧和zerodet02v块的下侧到第二芯片300b的左侧的具有弯曲形状的区域中。换句话说,acout块的一部分形成在焊盘p31和焊盘p49之间的区域中。

367.在靠近焊盘p35(dcout)的区域(即,在被焊盘p35、焊盘p30和焊盘p49包围的横向区域)形成dcout块。dcout块具有比acout块更大的面积。

368.在第二芯片300b的右上区域(即,除了焊盘形成区域之外,占据第二芯片300b的右侧的大约3/4和上侧的大约4/7的区域)中形成logic块(对应于上述逻辑单元330)。logic块具有比任何其它块更大的面积。

369.在第二芯片300b的平面图中,在未形成上述块(acdet、acmon、zerodet、zerodet02v、acout、dcout和logic)的区域(即,占据第二芯片300b的右侧的大约3/4和下侧的大约3/7的区域)中,形成生成带隙基准电压的bgr块、根据带隙基准电压生成内部参考电压的vrefamp块、监测内部参考电压的vrefdet块(对应于欠压保护单元360)、生成内部参考电流的iref块、向logic块提供时钟信号的osc块、以及设置logic块的操作的fuse块。

370.《封装布局(第五示例)》

371.图43是示出半导体集成电路装置300的封装布局的第五示例的图(xz平面图)。该图的半导体集成电路装置300基于图34的封装布局(第三示例),其中图39的第一芯片300和图42的第二芯片300b安装在岛300c上。

372.具体地,在该图中,图39的第一芯片300a沿顺时针方向(或沿逆时针方向)旋转180

°

,并且安装在岛300c的右上方区域中。此外,在该图中,图42的第二芯片300b沿顺时针方向旋转90

°

并安装在岛300c的左下方区域中。

373.焊盘p21(vhac1)经由导线w21连接到引脚7(vhac1)的远端侧。焊盘p22(vhac2)经由导线w22连接到引脚6(vhac2)。焊盘p23(acin1)经由导线w23连接到焊盘p26(acin1)。焊盘p24(acin2)经由导线w24连接到焊盘p27(acin2)。焊盘p25(gnd)经由导线w25连接到焊盘p28(gnd)。焊盘p33(dcin)经由导线w30连接到焊盘p34(dcin)。焊盘p29(vcc)经由导线w26连接到引脚4(vcc)的远端侧。焊盘p30(gnd)经由导线w27连接到引脚3(gnd)。焊盘p31(acout)经由导线w28连接到引脚1(acout)的远端侧。

374.注意,在该图的半导体集成电路装置300中,不使用dc电压监测功能,因此焊盘p32(vhdc)和焊盘p35(dcout)不连接到任何引脚。相比较,焊盘p33(dcin)和焊盘p34(dcin)经

由导线w30彼此连接。因此,例如类似于上述图37,dc电压监测功能可以仅通过经由导线w29连接焊盘p32(vhdc)而不使用引脚5以及通过经由导线w30连接焊盘p35(dcout)而不使用引脚2来使用。

375.此外,第一芯片300a的焊盘p23至焊盘p25和焊盘p33,以及第二芯片300b的焊盘p26至焊盘p28和焊盘p34以每个对应的顺序在纸张上沿左右方向(x轴方向)布置。因此,焊盘之间的导线w23至w25和w30可以以最小距离形成而不交叉。

376.此外,第一芯片300a的焊盘p21至焊盘p22和焊盘p32分别以与引脚7(vhac1引脚)、引脚6(vhac2引脚)和引脚5(即当使用dc电压监测功能时的vhdc引脚)相对应的顺序在纸张上沿上下方向(z轴方向)布置。因此,引脚和焊盘之间的导线w21和w22(以及当使用dc电压监测功能时的导线w29)可以以最小距离形成而不交叉。

377.类似地,第二芯片300b的焊盘p29至焊盘p30和焊盘p35以分别以与引脚4(vcc引脚)、引脚3(gnd引脚)和引脚2(当使用dc电压监测功能时为dcout引脚)的顺序在纸张上沿上下方向(z轴方向)布置。因此,引脚和焊盘之间的导线w26和w27(以及当使用dc电压监测功能时的导线w29)可以以最小距离形成而不交叉。

378.注意,在封装到半导体集成电路装置300中之后,不使用用于芯片测试的焊盘p41至焊盘p49,因此焊盘p41至焊盘p49不连接到任何引脚。

379.此外,关于封装内部的框架区域,引脚1(acout引脚)、引脚4(vcc引脚)、引脚5(n.c.引脚)和引脚7(vhac1引脚)中的每一个均大于引脚2(n.c.引脚)、引脚3(gnd引脚)或引脚6(vhac2引脚)。

380.换句话说,关于x方向(即纸张上的左右方向),引脚1(acout引脚)和引脚4(vcc引脚)具有比引脚2(n.c.脚)和引脚3(gnd引脚)突出的部分。类似地,引脚5(n.c.引脚)和引脚7(vhac1引脚)具有比引脚6(vhac2引脚)突出的部分。

381.此外,关于z方向(即纸上的上下方向),引脚1(acout引脚)和引脚4(vcc引脚)与岛300c部分重叠。类似地,引脚5(n.c.引脚)和引脚7(vhac1引脚)与岛300c部分重叠。

382.此外,支撑岛300c的支撑框架300e和300f分别形成在引脚1(acout引脚)和引脚7(vhac1引脚)之间以及引脚4(vcc引脚)和引脚5(n.c.引脚)之间。

383.《封装布局(第六示例)》

384.图44是示出半导体集成电路装置300的封装布局的第六示例的图(xz平面图)。与上述第五示例(图43)类似,该图的半导体集成电路装置300基于图36的封装布局(第四示例),其中图39的第一芯片300和图42的第二芯片300b安装在岛300c上。

385.具体地,在该图中,图39的第一芯片300a沿顺时针方向(或沿逆时针方向)旋转180

°

,并且安装在岛300c的左右中上侧区域中(即,从图43中的位置移动到岛300c的左中和右中的位置)。此外,在该图中,图42的第二芯片300b沿顺时针方向旋转90

°

并且安装在岛300c的左下区域中(即,从图43中的位置移动到岛300c的上下中部的位置)。

386.焊盘p21(vhac1)经由导线w21连接到引脚11(vhac1)。焊盘p22(vhac2)经由导线w22连接到引脚10(vhac2)。焊盘p32(vhdc)经由导线w29连接到引脚9(vhdc引脚)。焊盘p23(acin1)经由导线w23连接到焊盘p26(acin1)。焊盘p24(acin2)经由导线w24连接到焊盘p27(acin2)。焊盘p25(gnd)经由导线w25连接到焊盘p28(gnd)。焊盘p33(dcin)经由导线w30连接到焊盘p34(dcin)。焊盘p29(vcc)经由导线w26连接到引脚7(vcc)的远端侧。焊盘p30

(gnd)经由导线w27连接到引脚5(gnd)。焊盘p35(dcout)经由导线w31连接到引脚4(dcout引脚)。焊盘p31(acout)经由导线w28连接到引脚3(acout)的远端侧。

387.注意,第一芯片300a的焊盘p23至焊盘p25和焊盘p33,以及第二芯片300b的焊盘p26至焊盘p28和焊盘p34分别以每个对应的顺序在纸张上沿左右方向(x轴方向)布置。因此,焊盘之间的导线w23至w25和w30可以以最小距离形成而不交叉。这与上面参照图43所描述的相同。

388.此外,第一芯片300a的焊盘p21至焊盘p22和焊盘p32以分别对应于引脚11(vhac1引脚)、引脚10(vhac2引脚)和引脚9(vhdc引脚)的顺序在纸张上沿上下方向(z轴方向)布置。因此,引脚和焊盘之间的导线w21、w22和w29可以以最小距离形成而不交叉。

389.类似地,第二芯片300b的焊盘p29至焊盘p30和焊盘p35以分别对应于引脚7(vcc引脚)、引脚5(gnd引脚)和引脚4(dcout引脚)的顺序在纸张上沿上下方向(z轴方向)布置。因此,引脚和焊盘之间的导线w26、w27和w31可以以最小距离形成而不交叉。

390.注意,在封装到半导体集成电路装置300中之后,不使用用于芯片测试的焊盘p41至焊盘p49,因此焊盘p41至焊盘p49不连接到任何引脚。这也与上面参照图43所描述的相同。

391.此外,对于封装内部的框架区域,引脚2(n.c.引脚)和引脚6(n.c.引脚)中的每一个均大于引脚3(acout引脚)、引脚4(dcout引脚)或引脚5(gnd引脚)。

392.换句话说,关于x方向(即纸张上的左右方向),引脚2(n.c.引脚)和引脚6(n.c.引脚)具有比引脚3(acout引脚)、引脚4(dcout引脚)和引脚5(gnd引脚)突出的部分。

393.此外,关于z方向(即纸张上的上下方向),引脚2(n.c.引脚)和引脚6(n.c.引脚)没有与岛100c重叠的部分。类似地,引脚1(n.c.引脚)、引脚7(vcc引脚)、引脚8(n.c.引脚)和引脚11(vhac1引脚)也没有与岛100c重叠的部分。

394.此外,支撑岛300c的支撑框架300e和300f分别形成在引脚1(n.c.引脚)和引脚11(vhac1引脚)之间以及引脚7(vcc引脚)和引脚8(n.c.引脚)之间。

395.《引脚分配》

396.图45是示出采用七引脚封装(图43)的半导体集成电路装置300的引脚分配的平面图。在封装的左侧,引脚1(acout)、引脚2(n.c.)、引脚3(gnd)和引脚4(vcc)在纸张上按从上到下的顺序依次引出。相比较,在封装的右侧,引脚5(n.c.)、引脚6(vhac2)和引脚7(vhac1)在纸张上按从下到上的顺序依次引出。

397.注意,优选地,将每个施加有高电压的引脚7(vhac1)与引脚6(vhac2)之间的端子间距离w11设置为大于引脚1至引脚4的相邻引脚之间的端子间距离w12以及引脚5与引脚6之间的端子间距离w13。例如,在该示出的示例中,去除最初设置在引脚6和引脚7之间的外部端子(即,与引脚2相对的引脚),因此增大了引脚6和引脚7之间的端子间距离w11。

398.此外,从封装左侧引出的引脚1至引脚4的长度不一定与从封装右侧引出的引脚5至引脚7的长度相同。例如,如该图所示,引脚5至引脚7可以被引出为比引脚1至引脚4长。

399.图46是示出采用十一引脚封装(图44)的半导体集成电路装置300的引脚分配的平面图。在该图的示例中,在封装的左侧,引脚1(n.c.)、引脚2(n.c.)、引脚3(acout)、引脚4(dcout)、引脚5(gnd)、引脚6(n.c.)和引脚7(vcc)在纸张上按从上到下的顺序依次引出。相比较,在封装的右侧,引脚8(n.c.引脚)、引脚9(vhdc)、引脚10(vhac2)和引脚11(vhac1)在

纸张上按从下到上的顺序依次引出。

400.注意,优选地,将每个施加有高电压的引脚11(vhac1)与引脚10(vhac2)之间的端子间距离w21、引脚10(vhac2)与引脚9(vhdc)之间的端子间距离w22以及引脚9(vhdc)与引脚8(n.c.)之间的端子间距离w23设置为大于引脚1至引脚7的相邻引脚之间的端子间距离w24。例如,在该示出的示例中,去除最初设置在引脚8与引脚9之间、引脚9与引脚10之间以及引脚10与引脚11之间的外部端子(即,分别与引脚2、引脚4和引脚6相对的引脚),因此增大了引脚8与引脚9之间的端子间距离w23、引脚9与引脚10之间的端子间距离w22以及引脚10与引脚11之间的端子间距离w21。

401.此外,从封装左侧引出的引脚1至引脚7的长度不一定与从封装右侧引出的引脚8至引脚11的长度相同。例如,如该图所示,引脚8至引脚11可以被引出为比引脚1至引脚7短。

402.此外,优选地,引脚1至引脚11中的每一个在近端处形成为较薄。

403.《输入偏移和信号延迟》

404.接下来,参考图47至图49讨论过零检测单元320中的输入偏移和信号延迟。图47至图49是示出在过零检测单元320中生成比较信号sb的操作的示图,其中ac监测信号sa1(实线)和sa2(虚线)以及比较信号sb在纸张上从上到下依次示出。

405.注意,图47至图49分别示出了在第一条件(无输入偏移和无信号失真)、第二条件(无输入偏移和有信号失真)和第三条件(有输入偏移和有信号失真)下的行为。

406.如图47中所示,在ac监测信号sa1和sa2中几乎不发生失真的应用中(例如电动机由小电流驱动的烘干机),即使过零检测单元320没有输入偏移,在比较信号sb中也几乎不发生抖动。因此,过零检测单元320没有信号延迟,并且每当ac监测信号sa1和sa2彼此交叉时,比较信号sb的逻辑电平无延迟地切换。

407.相比较,如图48中所示,在ac监测信号sa1和sa2中容易发生失真的应用中(例如电动机由大电流驱动的洗衣机),如果过零检测单元320没有输入偏移,则在接近过零定时的比较信号sb中可能发生抖动。

408.注意,如图49中所示,如果过零检测单元320具有输入偏移(例如,将ac监测信号sa1向正侧移位的输入偏移sa1_ofs),则即使在ac监测信号sa1和sa2中发生失真,也可以避免比较信号sb中的抖动。然而,如果过零检测单元320具有输入偏移,则比较信号sb的逻辑切换定时(因此过零定时的检测结果)被延迟延迟时间td。

409.特别地,已知延迟时间td依赖于施加到vhac1引脚的监测目标电压v11(因此ac电压v0),并且可能干扰应用的操作。在下面的描述中,提出了解决这种故障的新颖实施方式。

410.《半导体集成电路装置(第七实施方式)》

411.图50是示出半导体集成电路装置300的第七实施方式的图。该实施方式的半导体集成电路装置300基于图上述图37(即,第五实施方式(图22)加上dc监测功能加上十一引脚封装),并且还包括延迟调整单元510和控制单元520。因此,上述结构元件由与图37中相同的数字或符号表示,因此省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

412.延迟调整单元510设置在逻辑单元330的后一级,根据从控制单元520指示的延迟调整量td_adj,调整过零检测信号sc的延迟时间td(在下面的描述中称为过零延迟时间td)。

413.控制单元520基于从比较单元350输出的多个比较信号sd(即,监测目标电压v11的峰值,因此是反映ac电压v0的峰值的逻辑信号)来设置延迟调整量td_adj。此外,控制单元520还具有基于多个比较信号sd切换过零检测单元320的输入偏移sa1_ofs的功能。

414.图51是示出由延迟调整单元510和控制单元520进行的过零延迟时间td的变化抑制过程的图,其中,在纸张上从上到下依次示出过零延迟时间td、延迟调整量td_adj和输入偏移sa1_ofs。

415.注意,该图中的横轴表示端子电压vhac1的峰值(即,施加到vhac1引脚的监测目标电压v11的峰值,因此对应于ac电压v0的峰值),并且关于要与之比较的阈值电压vthh、vthm和vthl,vthh》vthm》vthl成立。

416.此外,关于过零延迟时间td,实线l1示出在执行延迟调整量td_adj和输入偏移sa1_ofs的切换控制的情况下的行为。相比较,虚线l2示出在不执行延迟调整量td_adj和输入偏移sa1_ofs的切换控制的情况下(在td_adj=0并且sa1_ofs=+ofs始终成立的情况下)的行为。此外,点虚线l3示出了在没有给出输入偏移sa1_ofs的情况下(在td_adj=0并且sa1_ofs=0始终成立的情况下)的行为。

417.在不执行延迟调整量td_adj和输入偏移sa1_ofs的切换控制的情况下,如虚线l2所示,随着端子电压vhac1减小,过零延迟时间td增大并与预定目标过零延迟时间td_target分离。

418.相比较,在执行延迟调整量td_adj和输入偏移sa1_ofs的切换控制的情况下,如实线l1所示,过零延迟时间td被维持在预定目标过零延迟时间td_target(或接近该预定目标过零延迟时间td_target的值)。

419.具体地参照该图,例如,在vthh《vhac1成立的电压范围(i)内,设置td_adj=0(无延迟调整),并且sa1_ofs=+ofs(有输入偏移)。在该电压范围(i)中,不调整过零延迟时间td,因此实线l1表现出与虚线l2相同的行为。换句话说,随着端子电压vhac1的降低,过零延迟时间td增加并与目标过零延迟时间td_target分离。然而,在电压范围(i)中,与目标过零延迟时间td_target的间隔不是很大,因此没有特殊的故障。

420.相比较,在vthm《vhac1《vthh成立的电压范围(ii)中,设置td_adj=-adj1(小延迟调整)和sa1_ofs=+ofs(具有输入偏移)。换句话说,延迟调整后的过零延迟时间td(实线l1)被示为td=td0-adj1(其中,td0表示未调整延迟时的过零延迟时间(虚线l2))。

421.此外,在vthl《vhac1《vthm成立的电压范围(iii)内,设置td_adj=-adj2(较大延迟调整)且sa1_ofs=+ofs(具有输入偏移)。换句话说,延迟调整之后的过零延迟时间td(实线l1)被示为td=td0-adj2(其中,adj2》adj1成立)。

422.当然,延迟调整后的过零延迟时间td(实线l1)还根据端子电压vhac1而变化,类似于未调整延迟时的过零延迟时间td0(虚线l2),但是因为仅延迟调整量td_adj向负侧移位,所以可以将与目标过零延迟时间td_target的间隔控制得较小。

423.此外,在vhac1《vthl成立的电压范围(iv)内,设定td_adj=0(无延迟调整),并且sa1_ofs=0(无输入偏移)。这样,在即使执行延迟调整也不能将与目标过零延迟时间td_target的间隔控制在期望范围内的电压范围(iv)中,停止给出输入偏移sa1_ofs。结果,在过零检测单元320中不发生信号延迟,因此过零延迟时间td不与目标过零延迟时间td_target分离。

424.注意,在ac监测信号sa1和sa2中几乎不发生失真的应用中,不依赖于端子电压vhac1的峰值,延迟调整量td_adj和输入偏移sa1_ofs都应当固定为零,并且过零延迟时间td应当保持在目标过零延迟时间td_target,如点虚线l3所示。

425.《半导体集成电路装置(第八实施方式)》

426.图52是示出半导体集成电路装置300的第八实施方式的图。本实施方式的半导体集成电路装置300基于第七实施方式(图50),其中引脚6被用作延迟设置端子dset。因此,上述结构元件由与图50中相同的数字或符号表示,因此省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

427.在半导体集成电路装置300的内部,在内部基准电压vref的输入端子与延迟设置端子dset之间连接有内部电阻器531(具有电阻值r1)。此外,在半导体集成电路装置300的外部,外部电阻器532(具有电阻值r2)连接在延迟设置端子dset和接地端子之间。因此,通过使用预定分压比α(=r2/(r1+r2))对内部参考电压vref进行分压而获得的端子电压vdset(=α

×

vref)出现在延迟设置端子dset处。

428.控制单元520具有根据端子电压vdset(对应于延迟设置信号)将目标过零延迟时间td_target设置为任意值的功能。

429.图53是示出任意设置目标过零延迟时间td_target的示例的图。注意,该图中的横轴表示端子电压vdset,对于要与之比较的阈值电压vh、vm和vl,vref》vh》vm》vl成立(例如vref=3.0v、vh=2.5v、vm=1.0v且vl=0.3v)。

430.具体参照该图,在vh《vdset成立的电压范围(i)内,设定td_target=0。注意,为了将端子电压vdset控制在电压范围(i)内,例如,延迟设置端子dset应当处于开路(vdset≈3.0v)。

431.此外,在vm《vdset《vh成立的电压范围(ii)中,设定td_target=-2x(例如x=200(μs))。注意,为了将端子电压vdset控制在电压范围(ii)内,例如,330kω的外部电阻器532应当与280kω的内部电阻器531连接(vdset≈1.6v)。

432.此外,在vl《vdset《vm成立的电压范围(iii)内,设定td_target=-1x。注意,为了将端子电压vdset控制在电压范围(iii)内,例如,68kω的外部电阻器532应当与280kω的内部电阻器531连接(vdset≈0.6v)。

433.此外,在vdset《vl成立的电压范围(iv)内,设定td_target=+1x。注意,为了将端子电压vdset控制在电压范围(iv)内,例如,延迟端子dset应当短路为gnd(vdset≈0v)。

434.这里,在逻辑单元330中,如上所述,检测前一周期中的ac监测信号sa1和sa2之间的交叉定时,并且执行下一周期中的过零检测信号sc的定时控制(参见图26等)。因此,如上所述,也可以将目标过零延迟时间td_target设置为负值(《0)。

435.注意,任意设置目标过零延迟时间td_target的功能(第八实施方式)不必与过零延迟时间td的变化抑制功能(第七实施方式)组合,而是可以独立地引入其中的每一个。

436.此外,本实施方式示出了目标过零延迟时间td_target根据端子电压vdset以四个步长进行切换的示例,但是切换步长的数目是任意的。

437.《acout输出波形》

438.接下来,检查acout信号s1的输出波形。acout信号s1的输出形式可以是矩形类型,其中在ac电压v0的每个过零定时交替地切换逻辑电平(图54),或者可以是其中每ac电压v0

的过零定时就生成具有预定脉冲宽度tw的触发脉冲的边缘型(图55)。

439.《半导体集成电路装置(第九实施方式)》

440.图56是示出半导体集成电路装置300的第九实施方式的图。本实施方式的半导体集成电路装置300基于上述的图37(即,第五实施方式(图22)加上dc监测功能加上十一引脚封装),其中引脚2用作输出模式设置端子mode。因此,上述结构元件由与图37中相同的数字或符号表示,因此省略重复的描述。在下面的描述中,主要描述本实施方式的特征部分。

441.逻辑单元330具有根据到输出模式设置端子mode的输入信号将acout信号s1的输出形式切换成矩形类型(图54)和边缘类型(图55)之一的功能。注意,到输出模式设置端子mode的输入信号可以是模拟信号,也可以是数字信号。

442.进一步地,第七实施方式(图50)、第八实施方式(图52)以及第九实施方式(图56)示出了基于图37的示例,但是其也可以基于其它实施方式。例如,当采用第七至第九实施方式时,是否提供dc监测功能、封装引脚的数量等都不重要。

443.《发明内容》

444.在下面的描述中,以块的形式描述了本说明书中公开的各种实施方式。

445.例如,本说明书中公开的过零检测电路包括:峰值检测单元,该峰值检测单元用于检测通过二极管从ac信号输入端子输入的监测目标信号的峰值,从而生成峰值检测信号;以及过零检测单元,该过零检测单元用于根据所述峰值检测信号估计所述ac信号的过零,从而生成过零检测信号。

446.注意,具有上述结构的所述过零检测电路优选地还包括监测单元,该监测单元用于将所述监测目标信号调整为适应于输入到所述峰值检测单元。

447.此外,在具有上述结构的所述过零检测电路中,所述过零检测单元优选地对所述峰值检测信号的周期进行计数,并且使用其计数值来估计所述ac信号的过零。

448.此外,具有上述结构的所述过零检测电路优选地还包括:比较单元,该比较单元用于将所述监测目标信号与多个阈值进行比较,以生成多个比较信号;以及波形确定单元,该波形确定单元用于在所述过零检测信号的一个周期期间检测在所述比较信号中的至少一个中是否已经出现上升沿和下降沿两者,从而生成波形确定信号。

449.此外,在具有上述结构的所述过零检测电路中,当所述波形确定信号是异常确定逻辑电平时,所述过零检测单元优选地停止所述过零检测信号的生成或输出。

450.此外,在具有上述结构的所述过零检测电路中,如果所述峰值检测信号的逻辑电平被切换,并且切换之后的所述逻辑电平接着没有保持预定时段,则所述过零检测单元优选地忽略所述逻辑电平的切换。

451.此外,例如,本说明书中公开的所述过零检测电路包括:过零检测单元,该过零检测单元用于比较分别通过二极管从其间施加ac信号的第一节点和第二节点输入的第一监测目标信号和第二监测目标信号,从而生成第一比较信号;以及逻辑单元,该逻辑单元用于根据所述第一比较信号估计所述ac信号的过零,从而生成所述过零检测信号。

452.注意,具有上述结构的所述过零检测电路优选地还包括监测单元,该监测单元用于将所述第一监测目标信号和所述第二监测目标信号调整为适应于输入到所述过零检测单元。

453.此外,在具有上述结构的所述过零检测电路中,所述逻辑单元优选地对所述第一

比较信号的周期进行计数,并使用其计数值来估计所述ac信号的过零。

454.此外,在具有上述结构的所述过零检测电路中,所述过零检测单元优选地将所述第一监测目标信号与预定阈值进行比较以生成第二比较信号,并且所述逻辑单元优选地在所述第一监测目标信号低于所述阈值时对所述第二比较信号而不是所述第一比较信号的周期进行计数,并且使用其计数值来估计所述ac信号的过零。

455.此外,在具有上述结构的所述过零检测电路中,如果所述第二比较信号的逻辑电平被切换,并且切换之后的所述逻辑电平接着没有保持预定时段,则所述逻辑单元优选地忽略所述逻辑电平的所述切换。

456.此外,具有上述结构的所述过零检测电路优选地还包括:控制单元,该控制单元用于基于所述ac信号的峰值来设置延迟调整量;以及延迟调整单元,该延迟调整单元用于根据所述延迟调整量来调整所述过零检测信号的延迟时间。

457.此外,在具有上述结构的所述过零检测电路中,优选地,所述ac信号的所述峰值越低,所述控制单元越增大所述延迟调整量。

458.此外,在具有上述结构的所述过零检测电路中,所述控制单元优选地基于所述ac信号的所述峰值切换所述过零检测单元的输入偏移。

459.此外,在具有上述结构的所述过零检测电路中,当所述ac信号的所述峰值低于预定阈值时,所述控制单元优选地将所述延迟调整量和所述输入偏移都设置为零。

460.此外,具有上述结构的所述过零检测电路优选地还包括比较单元,该比较单元用于将所述第一监测目标信号或其分压信号与多个阈值进行比较,以生成多个比较信号,并且所述控制单元优选地接收所述多个比较信号的输入,所述多个比较信号的输入具有反映所述ac信号的所述峰值的逻辑值。

461.此外,在具有上述结构的所述过零检测电路中,所述控制单元优选地具有在不依赖于所述ac信号的所述峰值的情况下将所述延迟调整量和所述输入偏移都设置为零的功能。

462.此外,具有上述结构的所述过零检测电路优选地还包括控制单元,该控制单元用于根据所述延迟设置信号来设置所述过零检测信号的所述延迟时间。

463.此外,在具有上述结构的所述过零检测电路中,所述延迟设置信号是具有与外部电阻器的电阻值相对应的电压值的模拟信号,并且所述控制单元优选地根据所述模拟信号与阈值之间的比较结果逐步切换所述延迟时间。

464.此外,在具有上述结构的所述过零检测电路中,所述过零检测信号优选地是其中在所述ac信号的每个过零定时交替切换逻辑电平的矩形类型,或者是其中在所述ac信号的每个过零定时生成具有预定脉冲宽度的触发脉冲的边缘类型。

465.此外,在具有上述结构的所述过零检测电路中,所述逻辑单元优选地根据输出模式设置信号将所述过零检测信号的输出形式切换为所述矩形类型和所述边缘类型之一。

466.此外,例如,本说明书中公开的所述过零检测电路包括:逻辑单元,该逻辑单元用于根据分别通过二极管从其间施加ac信号的第一节点和第二节点输入的第一监测目标信号和第二监测目标信号中的至少一个来估计所述ac信号的过零,从而生成过零检测信号;以及输入停止检测单元,该输入停止检测单元用于在向所述第一监测目标信号和所述第二监测目标信号中的一个给出偏移之后将其进行比较以生成输入停止检测信号,其中,所述

逻辑单元根据所述输入停止检测信号固定所述过零检测信号的逻辑电平。

467.注意,在具有上述结构的所述过零检测电路中,如果所述输入停止检测信号的逻辑电平被切换,并且切换之后的所述逻辑电平接着没有保持预定时段,则所述逻辑单元优选地忽略所述逻辑电平的所述切换。

468.此外,具有上述结构的所述过零检测电路优选地还包括过零检测单元,该过零检测单元用于将所述第一监测目标信号与所述第二监测目标信号进行比较以生成比较信号,并且所述逻辑单元优选地根据所述比较信号估计所述ac信号的过零。

469.此外,具有上述结构的所述过零检测电路优选地还包括监测单元,该监测单元用于将所述第一监测目标信号和所述第二监测目标信号调整为适应于输入到所述过零检测单元。

470.此外,在具有上述结构的所述过零检测电路中,所述逻辑单元优选地对所述比较信号的周期进行计数,并使用其计数值来估计所述ac信号的过零。

471.此外,例如,本说明书中公开的所述半导体集成电路装置包括构成具有上述结构的所述过零检测电路的电路元件的至少一部分的集成。

472.注意,在具有上述结构的所述半导体集成电路装置中,优选地,接收所述监测目标信号的输入的第一外部端子和与所述第一外部端子相邻的第二外部端子之间的端子间距离应当大于其他外部端子之间的端子间距离。

473.此外,具有上述结构的所述半导体集成电路装置优选地还包括集成的ac/dc转换器,该集成的ac/dc转换器用于根据作为所述ac信号输入的ac电压生成第一dc电压。

474.此外,具有上述结构的所述半导体集成电路装置优选地还包括集成dc/dc转换器,该集成的dc/dc转换器用于根据所述第一dc电压生成第二dc电压。

475.此外,具有上述结构的所述半导体集成电路装置优选地由第一芯片和第二芯片构成,在所述第一芯片中集成有用于调整所述监测目标信号以适合于输入到所述峰值检测单元的监测单元,在所述第二芯片中集成有所述峰值检测单元和所述过零检测单元,所述第一芯片和所述第二芯片优选地用模制树脂密封。

476.此外,本说明书中公开的所述电子设备包括:整流单元,该整流单元用于执行ac电压的正常整流或倍压整流以生成整流电压;过零检测电路,该过零检测电路用于检测所述ac电压的过零;以及微计算机,该微计算机用于根据所述过零检测电路的检测结果来进行控制以驱动负载,其中,所述过零检测电路是具有上述结构的所述过零检测电路,或者是使用具有上述结构的所述半导体集成电路装置构成的所述过零检测电路。

477.注意,在具有上述结构的所述电子设备中,所述整流单元优选地包括串联连接在整流电压的输出端子和接地端子之间的第一电容器和第二电容器,并且第一电容器和第二电容器的连接节点优选地连接到从其引出所述第二监测目标信号的所述第二节点。

478.注意,在具有上述结构的所述电子设备中,所述过零检测电路优选地相对于所述微计算机公共的接地电压进行操作。

479.此外,在具有上述结构的所述电子设备中,所述负载优选为电动机或三端双向可控硅开关元件。

480.《注释a》

481.如下添加关于上述图39至图42的注释。在平面图中,其中集成有用于将所述第一

监测目标信号和所述第二监测目标信号调整为适应于输入到所述过零检测单元的所述监测单元的所述第一芯片优选地被切割成在短边和长边之间具有基本上相等的比率的矩形形状。

482.注意,在所述第一芯片中,优选在基板厚度方向(在垂直方向)上形成具有比其它区域高的耐受电压的高压区域,并且在所述高压区域上方形成第一焊盘和与该第一焊盘连接的第一反馈电阻器,所述第一监测目标信号和所述第二监测目标信号被输入到所述第一焊盘。

483.此外,优选地,在所述第一芯片的平面图中沿着所述第一芯片的第一侧形成多个高压区域。此外,优选地,在所述第一芯片的平面图中,形成集中在所述第一芯片的第一区域(例如,所述第一芯片的一半区域)中的多个高压区域(例如,第一高压区域、第二高压区域和第三高压区域)。

484.相比较,在所述第一芯片的平面图中,优选地在所述第一芯片的第二区域(例如,所述第一芯片的剩余半区域)中形成将信号从所述监测单元输出到所述过零检测单元的第二焊盘、连接到所述第二焊盘的第二反馈电阻器、连接到所述接地端子的第三焊盘、保护所述焊盘的静电保护元件、以及调整所述第二反馈电阻器的电阻值的熔丝。

485.注意,在所述第一芯片的平面图中,优选地沿着与所述第一芯片的所述第一侧垂直的第二侧形成多个第二焊盘和第三焊盘。特别地,在所述第一芯片的平面图中,优选地沿着所述第二侧形成并布置所述第二焊盘和所述第三焊盘,并且所述第二焊盘和所述第三焊盘比所述第一侧的中间更靠近所述第二侧。此外,优选地,将所述第二焊盘和所述第三焊盘之间的焊盘间距离设置为大于所述多个第二焊盘的焊盘间距离。

486.此外,在所述第一芯片的平面图中,所述第二反馈电阻器优选地形成在与所述高压区域相邻的位置处。

487.此外,优选使用具有100v或更高(例如650v)的耐受电压的多晶硅电阻器作为被施加高电压的所述第一反馈电阻器。

488.此外,优选地,所述高压区域是ldmosfet区域。

489.此外,在所述第一芯片的平面图中的所述ldmosfet区域中,优选地,多个同心环状漏极区域和源极区域交替形成,并且所述第一反馈电阻器形成在由最内漏极区域围绕的场氧化物膜上。

490.此外,所述第一反馈电阻器和所述第二反馈电阻器中的每一个形成为多个单位电阻器的组合。

491.相比较,其中集成有所述过零检测单元的所述第二芯片优选地在平面图中被切割成长矩形形状。

492.注意,在所述第二芯片的平面图中,连接到所述第一芯片的多个焊盘优选地形成并布置为靠近所述第二芯片的第一侧。

493.相比较,在所述第二芯片的平面图中,未连接到所述第一芯片的多个焊盘优选地形成并布置为靠近与所述第二芯片的所述第一侧相对的第二侧。

494.此外,优选地,输入所述第一监测目标信号的分压信号的第一焊盘和输入所述第二监测目标信号的分压信号的第二焊盘彼此相邻地布置。

495.此外,优选地,输入所述第三监测目标信号的分压信号的所述第三焊盘与所述第

二焊盘之间的焊盘间距离大于所述第一焊盘与所述第二焊盘之间的焊盘间距离。

496.此外,优选地,在所述第一焊盘和输出所述acout信号的第四焊盘之间设置连接到所述接地电位的第五焊盘。

497.此外,优选地,在输出所述dcout信号的第六焊盘和连接到所述电源电位的第七焊盘之间设置连接到所述接地电位的第八焊盘。

498.此外,优选在第一焊盘至第六焊盘中的每一个的正下方形成静电保护元件。

499.此外,优选在第一测试焊盘和第二测试焊盘之间形成测试电路。

500.此外,在所述第二芯片的平面图中,优选在接近第一焊盘至第五焊盘的区域中形成所述比较单元、所述rc滤波器、所述过零检测单元、所述输入停止检测单元和所述第一输出单元。

501.此外,在所述第二芯片的平面图中,优选在靠近第六焊盘的区域中形成所述第二输出单元。

502.《注释b》

503.接下来,如下添加关于上述图43和图44的注释。第一芯片和第二芯片中的每个焊盘优选地经由导线连接到对应的引脚。

504.注意,第一芯片的dcin引脚和第二芯片的dcin引脚优选地彼此连接,而不管是否使用dc电压监测功能。

505.此外,优选地,分别彼此连接的所述第一芯片的多个输出焊盘和接地焊盘以及所述第二芯片的多个输入焊盘和接地焊盘应当以对应的顺序布置。

506.《注释c》

507.接下来,如下添加关于上述图45和图46的注释。作为所述半导体集成电路装置的封装,优选使用例如七引脚封装或十一引脚封装。

508.注意,优选从封装的第一侧引出未被施加高电压的引脚,并且从封装的第二侧引出被施加高电压的引脚。

509.此外,优选地,施加高电压的引脚之间的端子间距离应当大于未施加高电压的引脚之间的端子间距离。

510.此外,从封装的第一侧引出的引脚的长度不一定与从封装的第二侧引出的引脚的长度相同。例如,从第二侧引出的引脚可以比从第一侧引出的引脚长。此外,相反,来自第二侧的引脚可以比来自第一侧的引脚短。

511.此外,每个引脚可在近端形成为较薄。

512.《其它变型例》

513.注意,上述实施方式示出了根据过零检测电路的检测结果来控制电动机的驱动的示例,但是过零检测电路的应用不限于此。也可以适当地应用于检测ac电压的过零从而控制三端双向可控硅开关元件的驱动的电源装置等。

514.以这种方式,除了上述实施方式之外,在本说明书中公开的各种技术特征可以在不脱离其精神的情况下在技术发明的范围内进行各种修改。

515.例如,双极型晶体管和mos场效应晶体管可以互换,各种信号的逻辑电平可以任意反转。换句话说,上述实施方式仅是每个方面的示例,不应被理解为限制。本发明的技术范围不限于实施方式,并且应当理解为包括在等同于权利要求的含义和范围内的所有变型。

516.工业实用性

517.本说明书中公开的过零检测电路可以用于控制例如电动机或三端双向可控硅开关元件的驱动。

518.符号的说明

519.10 电子设备

520.11 滤波器

521.12 整流单元

522.12a至12d 二极管

523.12e至12g 电容器

524.13 ac/dc转换器

525.13a、13b 电阻器

526.13c 误差放大器

527.13d 比较器

528.13e rs触发器

529.13f 电平移位器

530.13g nmosfet

531.13h 线圈

532.13i 二极管

533.14 dc/dc转换器

534.15 微计算机

535.16 驱动器

536.17 电动机

537.18 过零检测电路

538.19 输入电抗器

539.20 继电器开关

540.100 半导体集成电路装置(过零ic)

541.100a 第一芯片

542.100b 第二芯片

543.100c 岛

544.100d 模塑树脂

545.100e、100f 支撑框架

546.110 ac监测单元

547.111至115 电阻器

548.116 nmosfet

549.117 pmosfet

550.118 二极管

551.120 峰值检测单元

552.121、122 电阻器

553.123、124 电容器

554.125 比较器

555.130 过零检测单元

556.140 第一输出单元

557.141、142 逆变器

558.143nmosfet

559.144 电阻器

560.150 dc监测单元

561.160 第二输出单元

562.170 欠压保护单元

563.180 比较单元

564.181至184比较器

565.190 ac波形确定单元

566.200 印刷线路板

567.210 铜线

568.220 焊料

569.300 半导体集成电路装置(过零ic)

570.300a 第一芯片

571.300b 第二芯片

572.300c 岛

573.310 ac监测单元

574.311至314 电阻器

575.311a至315a、311b至315b 电阻器

576.316a、316b nmosfet

577.317a、317b pmosfet

578.318a、318b 熔丝

579.320 过零检测单元

580.321、322 比较器

581.330 逻辑单元

582.340 第一输出单元

583.350 比较单元

584.360 欠压保护单元

585.370 输入停止检测单元

586.371 偏置电源

587.372 比较器

588.380 dc监测单元

589.381至385 电阻器

590.386 nmosfet

591.387 pmosfet

592.388 熔丝

593.390 第二输出单元

594.400、400x至400z 高压区域(ldmosfet区域)

595.401 反馈电阻(多晶硅电阻)

596.401 (1)至401(m)单位电阻器

597.402 场氧化膜

598.410 p型半导体基板

599.411 低浓度n型半导体区域

600.412 高浓度p型半导体区域

601.413、414 高浓度n型半导体区域

602.415 场氧化膜

603.416 栅极氧化膜

604.417 栅极区域

605.418 场板

606.419 低浓度p型半导体区域

607.510 延时调整单元

608.520 控制单元

609.531 内部电阻器

610.532 外部电阻器

611.a1、a2 区域

612.c1、c11 电容器

613.d1、d11、d12 二极管

614.p1至p12、p21至p35、p41至p49 焊盘

615.r 电阻部件

616.w1至w9、w21至w31 导线

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1