一种高密度连接器检测治具、检测方法与流程

1.本发明涉及pcb板连接器检测技术领域,具体涉及一种高密度连接器检测治具、检测方法。

背景技术:

2.连接器在服务器产业的应用上是相当广范,不同pcb板就经常透过线缆做讯号或电源的连接,而对于高速讯号如:pcie、sata、usb

…

等的要求除了考虑阻抗问题也需考虑到连接器单体到打件到pcb板上的制程良率是否符合量产后的生产效率。

3.而对于当前高速讯号所使用的高密度端口连接器,例如符合当前pcie gen5规格的mcio(mini cooledge io connector)连接器,因pcba板上的mcio连接器考虑高速讯号衰减而将所有引脚都会尽量缩短并且内缩至连接器下面,因为无法看到连接器引脚,是无法由目测法从外观上判断连接器是否会因为pcb打件时造成物理上的引脚短路而造成的功能异常。

4.透过外部仪器来做讯号电气的量测主要进行:a.连接器单体出厂验证,此方法是透过各家连接器厂商提供自己量测仪具来确保自己生产的连接器是否符合规格书上的记载参数,但此方法是无法对打件在pcb上面的连接器来做验证。b.pcba上的mcio连接器验证,可以透过如tdr(time domain reflectometry时域反射技术)等相关仪器来确定pcba上的mcio连接器针对阻抗来验证,其秏费人力与物力的成本。

技术实现要素:

5.针对连接器引脚内缩至连接器下面,无法由目测法从外观上判断连接器是否会因为pcb打件时造成物理上的引脚短路而造成的功能异常以及通过tdr仪器来确定pcba上的连接器针对阻抗来验证,秏费人力与物力的成本的问题,本发明提供一种高密度连接器检测治具、检测方法。

6.本发明的技术方案是:

7.第一方面,本发明技术方案提供一种高密度连接器检测治具,待测件为高密度连接器,包括治具板,所述治具板上设置有控制处理模块、结果显示模块和治具板连接器;

8.将治具板连接器的差分信号对引脚按照引脚编号顺序划分为若干个组,前一个组的最后一个引脚与后一个组的第一个引脚为同一个引脚;

9.每个组中的引脚连接有一路检测线路;

10.每个组中第一个引脚与本组连接的检测线路连接,本组中剩余的其他引脚中相邻的两个引脚连接一个通道选择芯片的输入端,通道选择芯片的输出端与本组连接的检测线路连接;

11.每个通道选择芯片的选择控制端与控制处理模块连接;

12.检测线路的输出端通过控制处理模块与结果显示模块连接,用于将检测结果输出显示;结果显示模块包括led灯,每个引脚按照引脚编号对应一个编号的led灯。

13.检测时,待测件通过平行线缆与治具板连接器连接。每组差分讯号的检测先将第一通道选择芯片和第二通道选择芯片的选择控制端切到初始位置;

14.控制处理模块根据检测线路输出端的电平准位,来判别当前引脚状态是否正常,如发现当前引脚异常时,会进一步的透过第一通道选择芯片和第二通道选择芯片的切换输入引脚来定位异常引脚;将已定位出异常的引脚通过结果显示模块在其位置上的led点亮;

15.每次检测中没检测一个差分信号对控制处理模块内的计数器加1,来确保每个差分信号都有被检测到;所有差分信号被检测完成后,即会显示完成led灯编号告知使用者。

16.进一步的,每一路检测线路包括光电耦合器;

17.光电耦合器的第一输入端通过第一电阻连接有电源,光电耦合器的控制输入端连接到本组通道选择芯片的输出端,光电耦合器的输出端连接到控制处理模块。

18.进一步的,将治具板连接器的差分信号对引脚按照引脚编号顺序划分为若干个组,每组包括四个引脚;将a1-a4引脚划分为一组,a4-a7引脚划分为一组,依次类推直至最后一组。

19.进一步的,每组中的引脚连接两个通道选择芯片,每个通道选择芯片包括i0通道端和i1通道端,两个通道选择芯片分别为第一通道选择芯片和第二通道选择芯片;

20.每组中的第二个引脚和第三个引脚与第一通道选择芯片连接,第三个引脚和第四个引脚与第二通道选择芯片连接;第一通道选择芯片和第二通道选择芯片均与本组的光电耦合器连接。

21.进一步的,每组内的第一个引脚接地,第一个引脚还通过串联连接的第四电阻和第三电阻连接到本组的光电耦合器的控制输入端;

22.第二个引脚与第一通道选择芯片的i0通道端连接,第三个引脚与第一通道选择芯片的i1通道端连接;第四个引脚与第二通道选择芯片的i0通道端连接,第三个引脚与第二通道选择芯片的i1通道端连接;第一通道选择芯片和第二通道选择芯片的选择控制端分别与控制处理模块连接;

23.第一通道选择芯片的输出端连接到本组的光电耦合器的控制输入端,第二通道选择芯片的输出端接地,第二通道选择芯片的输出端还通过第二电阻连接到本组的光电耦合器的控制输入端;本组的光电耦合器的输出端通过串联连接的第五电阻和第四电阻接地。

24.进一步的,控制处理模块包括cpld;

25.cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i0通道端接通时,第二个引脚与光电耦合器控制输入端连接,第四个引脚接地,第四个引脚还通过第二电阻与光电耦合器控制输入端连接;

26.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断只有第二个引脚和第一个引脚短路时,满足导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态;cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路。

27.进一步的,cpld控制第一通道选择芯片的i1通道端接通、第二通道选择芯片的i0通道端接通时,第三个引脚与光电耦合器控制输入端连接,第四个引脚接地,第四个引脚还通过第二电阻与光电耦合器控制输入端连接;

28.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的

导通电流,判断只有第三个引脚和第四个引脚短路时,满足导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第三个引脚和第四个引脚正常。

29.进一步的,cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i1通道端接通时,第二个引脚与光电耦合器控制输入端连接,第三个引脚接地,第三个引脚还通过第二电阻与光电耦合器控制输入端连接;

30.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断第二个引脚和第一个引脚短路同时第二个引脚和第三个引脚短路,或第二个引脚和第三个引脚短路,满足导通条件,并且此时当第二个引脚和第一个引脚正常时,第二个引脚与第三个引脚短路;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第一个引脚、第二个引脚、第三个引脚正常。

31.第二方面,本发明技术方案还提供一种高密度连接器检测方法,包括如下步骤:

32.平行线缆将待测件与测试治具安装完成;

33.cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i0通道端接通;

34.cpld判断光电耦合器的输出为0时,判断本组中第二个引脚和第一个引脚短路;cpld判断光电耦合器的输出为1时,第二个引脚和第一个引脚正常;

35.cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路;

36.每对引脚检测完成cpld内的计数器加1,直至检测完成,计数器清零。

37.进一步的,cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路的步骤包括:

38.cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i1通道端接通;

39.cpld判断光电耦合器的输出为0时,判断第二个引脚和第一个引脚短路同时第二个引脚与第三个引脚短路,或者第二个引脚与第三个引脚短路;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第一个引脚、第二个引脚和第三个引脚正常;

40.cpld控制第一通道选择芯片的i1通道端接通、第二通道选择芯片的i0通道端接通;

41.cpld判断光电耦合器的输出为0时,第三个引脚和第四个引脚短路,cpld判断光电耦合器的输出为1时,本组内的引脚正常。

42.从以上技术方案可以看出,本发明具有以下优点:连接器检测治具可针对目前符合pcie gen5规格之mcio高密度连接器做检测,通过通道选择器进行引脚的选择,通过侦测线路,再通过cpld的判读后以最方便且直观的方式透过led显示检验结果,此治具可以检测出连接器在pcb打件上的制程瑕疵。解决已经将连接器打件于pcb板上的不易检测的问题,确保连接器的可靠性。而无需另外花费大量人力时间与仪器成本来做验证。

43.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

44.由此可见,本发明与现有技术相比,具有突出的实质性特点和显著地进步,其实施的有益效果也是显而易见的。

附图说明

45.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

46.图1是本发明一个实施例的治具的示意性框图。

47.图2是本发明一个实施例的治具的一组引脚连接示意图。

48.图3是本发明一个实施例的治具的判断a1与a2引脚状态的连接示意图。

49.图4是本发明一个实施例的治具的判断a3与a4引脚状态的连接示意图。

50.图5是本发明一个实施例的治具的判断a2与a3引脚状态的连接示意图。

具体实施方式

51.对于当前高速讯号所使用的高密度端口连接器,例如符合当前pcie gen5规格的mcio(mini cooledge io connector)连接器,因pcba板上的mcio连接器考虑高速讯号衰减而将所有引脚都会尽量缩短并且内缩至连接器下面,因为无法看到连接器引脚,是无法由目测法从外观上判断连接器是否会因为pcb打件时造成物理上的引脚短路而造成的功能异常。

52.透过外部仪器来做讯号电气的量测主要进行:a.连接器单体出厂验证,此方法是透过各家连接器厂商提供自己量测仪具来确保自己生产的连接器是否符合规格书上的记载参数,但此方法是无法对打件在pcb上面的连接器来做验证。b.pcba上的mcio连接器验证,可以透过如tdr(time domain reflectometry时域反射技术)等相关仪器来确定pcba上的mcio连接器针对阻抗来验证,其秏费人力与物力的成本。本技术设计一种检测治具,待测mcio连接器仅需透过线缆(cable)与检测治具做连接后,即可以轻易的开始连接器的检测,当检测完成后会将由检测线路将检测结果传输给控制处理模块做检测结果的判读与记录,并将此检验结果:通过/异常直接透过led的亮(异常)或灭(正常)来呈现,让此检验结果更让使用者可以容易判读。为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

53.如图1所示,本发明实施例提供一种高密度连接器检测治具,待测件为高密度连接器,包括治具板,所述治具板上设置有控制处理模块、结果显示模块和治具板连接器;

54.将治具板连接器的差分信号对引脚按照引脚编号顺序划分为若干个组,前一个组的最后一个引脚与后一个组的第一个引脚为同一个引脚;

55.每个组中的引脚连接有一路检测线路;

56.每个组中第一个引脚与本组连接的检测线路连接,本组中剩余的其他引脚中相邻的两个引脚连接一个通道选择芯片的输入端,通道选择芯片的输出端与本组连接的检测线路连接;

57.每个通道选择芯片的选择控制端与控制处理模块连接;

58.检测线路的输出端通过控制处理模块与结果显示模块连接,用于将检测结果输出

显示;结果显示模块包括led灯,每个引脚按照引脚编号对应一个编号的led灯。

59.检测时,待测件通过平行线缆与治具板连接器连接。每组差分讯号的检测先将第一通道选择芯片和第二通道选择芯片的选择控制端切到初始位置;

60.控制处理模块根据检测线路输出端的电平准位,来判别当前引脚状态是否正常,如发现当前引脚异常时,会进一步的透过第一通道选择芯片和第二通道选择芯片的切换输入引脚来定位异常引脚;将已定位出异常的引脚通过结果显示模块在其位置上的led点亮;

61.每次检测中没检测一个差分信号对控制处理模块内的计数器加1,来确保每个差分信号都有被检测到;所有差分信号被检测完成后,即会显示完成led灯编号告知使用者。

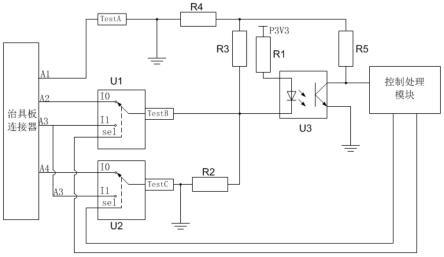

62.如图2所示,在有些实施例中,每一路检测线路包括光电耦合器u3;

63.光电耦合器u3的第一输入端通过第一电阻r1连接有电源p3v3,光电耦合器u3的控制输入端连接到本组的通道选择芯片的输出端,光电耦合器u3的输出端连接到控制处理模块。

64.在有些实施例中,将治具板连接器的差分信号对引脚按照引脚编号顺序划分为若干个组,每组包括四个引脚;将a1-a4引脚划分为一组,a4-a7引脚划分为一组,依次类推直至最后一组。

65.每组中的引脚连接两个通道选择芯片,每个通道选择芯片包括i0通道端和i1通道端,两个通道选择芯片分别为第一通道选择芯片u1和第二通道选择芯片u2;

66.每组中的第二个引脚和第三个引脚与第一通道选择芯片连接,第三个引脚和第四个引脚与第二通道选择芯片连接;第一通道选择芯片和第二通道选择芯片均与本组的光电耦合器连接。

67.每组内的第一个引脚接地,第一个引脚还通过串联连接的第四电阻和第三电阻连接到本组的光电耦合器的控制输入端;

68.第二个引脚与第一通道选择芯片的i0通道端连接,第三个引脚与第一通道选择芯片的i1通道端连接;第四个引脚与第二通道选择芯片的i0通道端连接,第三个引脚与第二通道选择芯片的i1通道端连接;第一通道选择芯片和第二通道选择芯片的选择控制端分别与控制处理模块连接;

69.第一通道选择芯片的输出端连接到本组的光电耦合器的控制输入端,第二通道选择芯片的输出端接地,第二通道选择芯片的输出端还通过第二电阻连接到本组的光电耦合器的控制输入端;本组的光电耦合器的输出端通过串联连接的第五电阻和第四电阻接地。在待测物上的mcio连接器,只要透过一般平行线缆(pin a1

–

a1/b1-b1),一头安装在待测物上,另一头直接插在之举的治具板连接器上。

70.控制处理模块包括cpld;cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i0通道端接通时,第二个引脚与光电耦合器控制输入端连接,第四个引脚接地,第四个引脚还通过第二电阻与光电耦合器控制输入端连接。

71.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断只有第二个引脚和第一个引脚短路时,满足导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态;cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路。

72.cpld控制第一通道选择芯片的i1通道端接通、第二通道选择芯片的i0通道端接通

时,第三个引脚与光电耦合器控制输入端连接,第四个引脚接地,第四个引脚还通过第二电阻与光电耦合器控制输入端连接;

73.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断只有第三个引脚和第四个引脚短路时,满足导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第三个引脚和第四个引脚正常。

74.cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i1通道端接通时,第二个引脚与光电耦合器控制输入端连接,第三个引脚接地,第三个引脚还通过第二电阻与光电耦合器控制输入端连接;

75.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断第二个引脚和第一个引脚短路同时第二个引脚和第三个引脚短路,或第二个引脚和第三个引脚短路,满足导通条件,并且此时当第二个引脚和第一个引脚正常时,第二个引脚与第三个引脚短路;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第一个引脚、第二个引脚、第三个引脚正常。

76.如图2所示的其中一组a1-a4引脚连接示意图,a2引脚和a3引脚与第一通道选择芯片u1连接,a3引脚和a4引脚与第二通道选择芯片u2连接;第一通道选择芯片u1和第二通道选择芯片u2均与光电耦合器u3连接。

77.a1引脚接地,a1引脚还通过串联连接的第四电阻r4和第三电阻r3连接到光电耦合器u3的控制输入端;

78.a2引脚与第一通道选择芯片u1的i0通道端连接,a3引脚与第一通道选择芯片u1的i1通道端连接;a4引脚与第二通道选择芯片u2的i0通道端连接,a3引脚与第二通道选择芯片u2的i1通道端连接;第一通道选择芯片u1和第二通道选择芯片u2的选择控制端sel分别与cpld连接;

79.第一通道选择芯片u1的输出端连接到光电耦合器u3的控制输入端,第二通道选择芯片u2的输出端接地,第二通道选择芯片u2的输出端还通过第二电阻r2连接到光电耦合器u3的控制输入端;光电耦合器u3的输出端通过串联连接的第五电阻r5和第四电阻r4接地。

80.a1引脚为测试点testa,第一通道选择芯片的输出端为测试点testb,第二通道选择芯片的输出端为测试点testc;

81.如图3所示,cpld控制第一通道选择芯片u1的i0通道端接通、第二通道选择芯片u2的i0通道端接通时,a2引脚为测试点testb,a4引脚为测试点testc,第二个引脚与光电耦合器控制输入端连接,第四个引脚接地,第四个引脚还通过第二电阻与光电耦合器控制输入端连接;本发明实施例中选择光电耦合器的型号为pc817,导通电流为20ma左右,设计的检测线路中第一电阻r1的阻值为100ω,第二电阻r2的阻值为10kω,第三电阻r3的阻值为100kω,第四电阻r4的阻值为10kω,第五电阻r5的阻值为1kω,本发明实施例中基于给定的电路中各参数值进行计算判断。

82.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,选择光电耦合器的导通电流为20ma左右,根据光电耦合器的导通电流,判断只有a2引脚和a1引脚短路时,id=(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件;cpld判断光电耦合器的输出为1时,id=(3.3-1.2)v/(100+100k+10k)ω=19ua,光电耦合器处于截止状态;此时,a1引脚和a2引脚是正常的,a2引脚和a3引脚,以及a3引脚与a4引脚需要进一步检测判断。

83.如图4所示,cpld控制第一通道选择芯片的i1通道端接通、第二通道选择芯片的i0通道端接通时,a3引脚为测试点testb,a4引脚为测试点testc。

84.cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断只有a3引脚和a4引脚短路时,id为(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,a3引脚和a4引脚正常。接下来需要进一步判断a2引脚和a3引脚是否正常;

85.如图5所示,cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i1通道端接通时,a2引脚为测试点testb,a3引脚为测试点testc。cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断a2引脚和a1引脚短路同时a2引脚和a3引脚短路,或a2引脚和a3引脚短路,id为(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件,也就是说此时通过cpld判断光电耦合器的输出为0来判断若前一步判断a1引脚和a2引脚正常,那么a2引脚和a3引脚短路;若前一步判断a1引脚和a2引脚短路,那么此时,a2引脚和a3引脚可能短路,cpld判断光电耦合器的输出为1时,id=(3.3-1.2)v/(100k+10k)ω=19ua,或者id=(3.3-1.2)v/(100+10k)ω=0.21ma,不能驱动光电耦合器导通,光电耦合器处于截止状态,a1引脚、a2引脚和a3引脚正常。

86.本发明实施例还提供一种高密度连接器检测方法,包括如下步骤:

87.步骤1:平行线缆将待测件与测试治具安装完成;

88.步骤2:cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i0通道端接通;

89.步骤3:cpld判断光电耦合器的输出为0时,判断本组中第二个引脚和第一个引脚短路;cpld判断光电耦合器的输出为1时,第二个引脚和第一个引脚正常;

90.步骤4:cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路;

91.步骤5:每对引脚检测完成cpld内的计数器加1,直至检测完成,计数器清零。

92.在有些实施例中,步骤4中,cpld控制通道选择芯片通道切换判断第三个引脚和第四个引脚是否短路以及第二个引脚和第三个引脚是否短路的步骤包括:

93.步骤41:cpld控制第一通道选择芯片的i0通道端接通、第二通道选择芯片的i1通道端接通;

94.步骤42:cpld判断光电耦合器的输出为0时,判断第二个引脚和第一个引脚短路同时第二个引脚与第三个引脚短路,或者第二个引脚与第三个引脚短路;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,第一个引脚、第二个引脚和第三个引脚正常;

95.步骤43:cpld控制第一通道选择芯片的i1通道端接通、第二通道选择芯片的i0通道端接通;

96.步骤44:cpld判断光电耦合器的输出为0时,第三个引脚和第四个引脚短路,cpld判断光电耦合器的输出为1时,本组内的引脚正常。

97.一组差分线路的组成是引脚a1/a2/a3/a4,a4/a5/a6/a7

…

以此四個排序往下递增,我们由一组检测线路来做检验,a1/a4在连接器使用上为接地线(gnd)做高速讯号的屏蔽作用,此部份无需另外做短路检验,我们主要关注a2/a3的差分信号线是否会与a1/a4短路,或是a2与a3间的短路,u1/u2由cpld控制,此有三种状况testb=引脚a2、testc=引脚

a3;或是testb=引脚a3、testc=引脚a4;或是testb=引脚a2、testc=引脚a4,第四状况因为无验证需求故在此列为don’t care。透过cpld来切换第一通道选择芯片和第二通道选择芯片均为mux芯片;cpld来切换mux芯片符合表1,表1为引脚判断逻辑表,来侦测。

98.检测部份是透过pc817光电耦合器来做为输出结果的判断线路,主是是透过限制led电流(id)方式让pc817光电耦合器里的led被刀捅而发亮或关闭,来让光电耦合器导通与截止,而能在输出部份输出一个低电平准位或高电平准位给cpld来确定结果。

99.表1

[0100][0101][0102]

如图2所示,a2引脚和a3引脚与第一通道选择芯片u1连接,a3引脚和a4引脚与第二通道选择芯片u2连接;第一通道选择芯片u1和第二通道选择芯片u2均与光电耦合器u3连接。

[0103]

a1引脚接地,a1引脚还通过串联连接的第四电阻r4和第三电阻r3连接到光电耦合器u3的控制输入端;

[0104]

a2引脚与第一通道选择芯片u1的i0通道端连接,a3引脚与第一通道选择芯片u1的i1通道端连接;a4引脚与第二通道选择芯片u2的i0通道端连接,a3引脚与第二通道选择芯片u2的i1通道端连接;第一通道选择芯片u1和第二通道选择芯片u2的选择控制端sel分别与cpld连接;

[0105]

第一通道选择芯片u1的输出端连接到光电耦合器u3的控制输入端,第二通道选择芯片u2的输出端接地,第二通道选择芯片u2的输出端还通过第二电阻r2连接到光电耦合器u3的控制输入端;光电耦合器u3的输出端通过串联连接的第五电阻r5和第四电阻r4接地。

[0106]

a1引脚为测试点testa,第一通道选择芯片的输出端为测试点testb,第二通道选择芯片的输出端为测试点testc;

[0107]

如图3所示,cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,选择光电耦合器的导通电流为20ma左右,根据光电耦合器的导通电流,判断只有a2引脚和a1引脚短路时,id=(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件;cpld判断光电耦合器的输出为1时,id=(3.3-1.2)v/(100+100k+10k)ω=19ua,光电耦合器处于截止状态;此时,a1引脚和a2引脚是正常的,a2引脚和a3引脚,以及a3引脚与a4引脚需要进一步检测判

断。

[0108]

如图4所示,cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断只有a3引脚和a4引脚短路时,id为(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件;cpld判断光电耦合器的输出为1时,光电耦合器处于截止状态,a3引脚和a4引脚正常。接下来需要进一步判断a2引脚和a3引脚是否正常;

[0109]

如图5所示,cpld判断光电耦合器的输出为0时,光电耦合器处于导通状态,根据光电耦合器的导通电流,判断a2引脚和a1引脚短路同时a2引脚和a3引脚短路,或a2引脚和a3引脚短路,id为(3.3-1.2)v/100ω=21ma,满足光电耦合器的导通条件,也就是说此时通过cpld判断光电耦合器的输出为0来判断若前一步判断a1引脚和a2引脚正常,那么a2引脚和a3引脚短路;若前一步判断a1引脚和a2引脚短路,那么此时,a2引脚和a3引脚可能短路,cpld判断光电耦合器的输出为1时,id=(3.3-1.2)v/(100k+10k)ω=19ua,或者id=(3.3-1.2)v/(100+10k)ω=0.21ma,不能驱动光电耦合器导通,光电耦合器处于截止状态,a1引脚、a2引脚和a3引脚正常。

[0110]

尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1