用于数据的缓冲传输的电路的制作方法

[0001]

本发明涉及一种用于从多个发送器向一个接收器缓冲传输数据的电路。本发明尤其涉及一种电路,其具有四个数据缓冲器(随后称为缓冲器)和控制发送器/或接收器对缓冲器的写入访问和读取访问的控制逻辑电路。

背景技术:

[0002]

由现有技术已知用于数据的缓冲传输的电路,所述电路对于每个通道具有三个缓冲器。所谓的电路提供一个用于写入数据的缓冲器和一个用于读出数据的缓冲器,而另一个缓冲器能实现将写入数据的缓冲器与从其中读出数据的缓冲器交换。因此,在两个通道的情况下需要六个缓冲器。

技术实现要素:

[0003]

对此,本发明丰富了现有技术,因为按照本发明的电路能实现利用四个缓冲器从两个发送器传输数据到一个接收器,而不限制发送器对电路的写入访问。

[0004]

按照本发明的电路包括第一缓冲器、第二缓冲器、第三缓冲器、第四缓冲器、用于第一数据的第一数据输入端、用于第二数据的第二数据输入端、数据输出端和控制逻辑电路。控制逻辑电路设计成,将第一数据输入端与其中一个缓冲器连接,将第二数据输入端与其中一个缓冲器连接并且将数据输出端与其中一个缓冲器连接。

[0005]

控制逻辑电路还设计成,如果第一数据通过第一数据输入端有效地写入当前与第一数据输入端连接的缓冲器中,则将当前与第一数据输入端连接的缓冲器与未连接的缓冲器交换,如果第二数据通过数据输入端有效地写入当前与第二数据输入端连接的缓冲器中,则将当前与第二数据输入端连接的缓冲器与未连接的缓冲器交换,并且为了读出数据,当未连接的缓冲器具有更新的有效写入的数据时,将当前与数据输出端连接的缓冲器与未连接的缓冲器交换。

[0006]

在此,在说明书和权利要求书中使用的“数据输入端”的概念尤其理解为可以将数据传输到电路上的通信连接部。此外,在说明书和权利要求书中使用的“数据输出端”的概念尤其理解为可以由所述电路输出数据的通信连接部。所述通信连接部例如可以是导电连接,借助所述导电连接可以将代表数据的电流电瓶和/或电压电平(例如逻辑电平)传递到电路上或者从电路输出。

[0007]

此外,在说明书和权利要求书中使用的“缓冲器”的概念尤其理解为存储元件(构件)或者存储元件(构件)中的可寻址的区域。亦即,在缓冲器之间的区别不仅可以涉及逻辑上的区别(例如在存储元件的可寻址的区域方面),而且也可以涉及在相关的存储元件(构件)方面的区别。此外,在说明书和权利要求书中使用的“控制逻辑电路”的概念尤其理解为一种电路,其设计成,基于对电路的状态的分析或者对电路提出的读取和/或写入需求(“read/write requests”)控制所述电路并且尤其选择从哪个缓冲器提供数据包并且将数据包写入哪个缓冲器。

[0008]

此外,在说明书和权利要求书中使用的“有效”和“无效”的概念尤其涉及数据的正确性。无效的数据包例如是在写入缓冲器时出现写入错误(并且因此在形式和/或内容方面以错误的方式不同于已告知的数据包)的数据包,或者是虽然正确写入缓冲器但是(由于之前的错误)包含错误的信息的数据包。

[0009]

因此,按照本发明的设备能实现从发送器(或者一个或多个数据生成者)至接收器(或者一个或多个数据使用者)的连续的数据流,其方式为,将数据包写入与数据输入端连接的缓冲器并且在读出时从缓冲器提供。此外,按照本发明的电路能实现接收通过冗余的数据通道传输的数据。在此,冗余的数据通道尤其是传输相同的有效数据的数据通道,其中,有效数据例如沿着不同的(物理的)传输路径或者时间上错开地通过相同的(物理的)传输路径传递。

[0010]

所述电路例如可以用作自动化技术中的4-缓冲器fifo(先入先出)并且在那里在收发器中实现。收发器例如可以用于将过程数据从本地总线继续传送至现场总线(例如在总线耦合器或者总线控制器中)。例如,本地总线可以具有逻辑环形拓扑,其中,将数据沿两个环形方向(冗余地)在总线用户设备之间交换。

[0011]

可以将过程数据以数据包/数据块(固定长度)的形式写入缓冲器中。在此,控制逻辑电路可以监视所述数据是否超过先前配置的数据块长度。在将数据写入缓冲器之后,可以将来自相应的发送器的数据标记为“有效的”或者“无效的”。在错误情况下,可以从另外的缓冲器向接收器供应数据。

[0012]

控制逻辑电路优选设计成,为了读出数据,代替将当前与数据输出端连接的缓冲器与未连接的缓冲器交换,如果信令读出请求并且同时信令已经将第一数据写入与第一数据输入端连接的缓冲器,则将当前与第一数据输入端连接的缓冲器与数据输出端连接,并且如果信令读出请求并且同时信令已经将第二数据写入与第二数据输入端连接的缓冲器,则将当前与第二数据输入端连接的缓冲器与数据输出端连接。

[0013]

在此,在说明书和权利要求书中使用的“同时信令”的表述尤其理解为,在两个信号之间的时间延迟这样小,使得在电路产生基于在先的信号的控制指令之前,控制逻辑电路就接收在后的信号,或者说时间上的间隔处于在产生控制指令之前控制逻辑电路所等待的间隔之内。

[0014]

可以确定第一输入端或者第二数据输入端的优先级,并且控制逻辑电路还设计成,如果信令读出请求并且同时信令已经将数据写入与第一数据输入端连接的缓冲器并且已经将数据写入与第二数据输入端连接的缓冲器,则为了读出数据,将当前与优先的数据输入端连接的缓冲器与数据输出端连接。

[0015]

因此,如果通过两个数据输入端同时接收数据,则(首先或者仅)继续传送通过优先的数据输入端接收的数据。

[0016]

缓冲器与第一数据输入端、第二数据输入端或者数据输出端的连接可以包括定址位移(“address offset”)的改变。

[0017]

缓冲器与第一数据输入端、第二数据输入端或者数据输出端的连接可以包括在信号路径之间的转换。

[0018]

电路优选集成到总线用户设备、尤其是总线收发器中。

[0019]

控制逻辑电路优选设计成,如果将数据有效地写入缓冲器中并且交换该缓冲器,

则设置旗标并且周期地重置该旗标,其中,在设置了旗标的情况下抑制当前与第一和第二数据输入端连接的缓冲器与另一个缓冲器的交换。

[0020]

所述电路优选设置在具有第一发送器、第二发送器和接收器的系统中,其中,第一发送器与第一数据输入端连接,第二发送器与第二数据输入端连接并且接收器与数据输出端连接,并且发送器设计成,将数据包通过数据输入端传输到电路上并且向所述电路信令写入过程的结束。

[0021]

在此,在说明书和权利要求书中使用的“数据包”的概念尤其理解为成块发送/接收的二进制编码的信息,其中,所述信息通常处于一定语境中。此外,数据包经常具有确定的结构,所述结构能实现给二进制编码的信息指定数据包的相应的部段。

[0022]

接收器优选设计成,向电路信令读出请求并且通过电路的数据输出端读出数据包。

[0023]

电路优选具有s+2个缓冲器,其中,s表明发送器的数量。

附图说明

[0024]

随后借助实施例的详细的说明中阐述本发明,其中,参照附图,图中:

[0025]

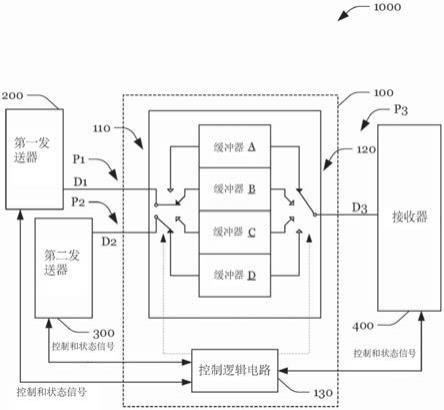

图1示出按照一实施例的按照本发明的电路;

[0026]

图2示出在写入访问和读取访问时在图1的电路中的流程;

[0027]

图3示出运行图1中示出的电路的流程图;

[0028]

图4a示出图1中示出的电路的状态图;

[0029]

图4b示出关于图4a中示出的状态图的伪码;以及

[0030]

图5示出图1中示出的电路关于数据的冗余传输的可能的应用。

[0031]

在此,在图中通过相同的附图标记表示相同的和功能类似的元件。

具体实施方式

[0032]

图1示出示例性的电路100,其具有第一缓冲器a、第二缓冲器b、第三缓冲器c和第四缓冲器d。缓冲器a-d可以构造为存储元件(例如“dpram页面”)中的多个可寻址的区域或者构造为多个独立的存储元件(例如多个dpram)。电路100包括用于第一数据d1的第一数据输入端p1、用于第二数据d2的第二数据输入端p2和用于输出数据d3的数据输出端p3。第一数据输入端p1与第一发送器200连接,第二数据输入端p2与第二发送器300连接并且数据输出端p3与接收器400连接。

[0033]

电路100还包括控制逻辑电路130。所述控制逻辑电路130设计成,将第一数据输入端p1与其中一个缓冲器a-d连接,将第二数据输入端p2与其中一个缓冲器a-d连接并且将数据输出端p3与其中一个缓冲器a-d连接。如图1中所示,在数据输入端p1、p2和缓冲器a-d之间尤其可以设有第一开关110,该第一开关能实现在第一发送器200和其中一个缓冲器a-d之间建立第一数据连接并且同时在第二发送器200和其中一个缓冲器a-d之间建立第二数据连接。通过可切换的连接,发送器200、300可以交替地将数据写入每个所述缓冲器a-d中。如图1中所示,第一开关110(或者开关位置)可以通过控制线路由控制逻辑电路130控制。

[0034]

此外,如图1中所示,在数据输出端p3和缓冲器a-d之间设有第二开关120,所述第二开关能实现在接收器400和其中一个缓冲器a-d之间建立第三数据连接。通过可切换的连

接,可以从每个所述缓冲器a-d向接收器400提供数据。如第一开关110那样,第二开关120也可以借助控制线路由控制逻辑电路130控制,其方式例如为,控制逻辑电路130通过控制线路将控制信号传输至开关110、120,所述控制信号向所述开关110、120信令,哪个缓冲器a-d与发送器200、300和接收器400连接并且哪个缓冲器a-d没有连接。

[0035]

在此,要理解的是,图1中示出的开关110、120主要用于阐释在不同的连接之间的转换。然而,本发明不局限于特定的开关110、120的应用。更确切地说,图1中示出的开关110、120可以以任意如下机构的形式实现,所述机构能实现在缓冲器之间的转换,亦即能实现断开现有的连接并且建立新的连接。

[0036]

如图2中所示,第一发送器200和第二发送器300可以将数据写入与其连接的缓冲器a-d并且从与其连接的缓冲器a-d向接收器400提供数据。在将数据写入到与发送器200、300连接的缓冲器a-d之后,相应的发送器200、300可以触发缓冲器交换。为此,相应的发送器200、300可以向逻辑电路130信令,已经顺利结束写入过程并且写入到缓冲器a-d中的数据是有效的。接着,可以在写入的缓冲器a-d和未连接的缓冲器a-d之间执行缓冲器交换。

[0037]

因此,如果第一数据d1通过第一数据输入端p1有效地写入当前与第一数据输入端p1连接的缓冲器a-d中,则将当前与第一数据输入端p1连接的缓冲器a-d与未连接的缓冲器a-d交换,并且如果第二数据d2通过第二数据输入端p2有效地写入当前与第二数据输入端p2连接的缓冲器a-d中,则将当前与第二数据输入端p2连接的缓冲器a-d与未连接的缓冲器a-d交换。接着,为了读出数据d3,可以将当前与数据输出端p3连接的缓冲器a-d与未连接的缓冲器a-d交换,(其中,这可以取决于未连接的缓冲器a-d同当前与数据输出端p3连接的缓冲器a-d相比是否具有更新的有效写入的数据。)

[0038]

如果控制逻辑电路130同时信令,第一数据d1通过第一数据输入端p1有效地写入当前与第一数据输入端p1连接的缓冲器a-d中并且第二数据d2通过第二数据输入端p2有效地写入当前与第二数据输入端p2连接的缓冲器a-d中,则控制逻辑电路130还可以设计成,根据通过电路100确定优先级为第一数据输入端p1还是第二数据输入端p2,促使当前与第一数据输入端p1或者第二数据输入端p2连接的缓冲器a-d直接与当前未连接的缓冲器a-d交换。要优先的数据输入端p1、p2可以是固定的(不变的)或者可以由控制逻辑电路130根据情况基于控制信号或者控制故障确定。

[0039]

如果控制逻辑信号130同时信令,向接收器400提供数据d3并且将第一数据d1通过第一数据输入端p1有效地写入当前与第一数据输入端p1连接的缓冲器a-d中或者将第二数据d2通过第二数据输入端p2有效地写入当前与第二数据输入端p2连接的缓冲器a-d,则控制逻辑电路130还可以设计成,促使当前与第一数据输入端p1或者当前与第二数据输入端p2连接的缓冲器a-d直接与当前与数据输出端p3连接的缓冲器a-d交换。

[0040]

此外,如果控制逻辑电路130同时信令,向接收器400提供数据d3并且第一数据d1通过第一数据输入端p1有效地写入当前与第一数据输入端p1连接的缓冲器a-d中并且第二数据d2通过第二数据输入端p2有效地写入当前与第二数据输入端p2连接的缓冲器a-d中,则控制逻辑电路130可以设计成,根据通过电路100确定优先级为第一数据输入端p1还是第二数据输入端p2,促使当前与第一数据输入端p1或者第二数据输入端p2连接的缓冲器a-d直接与当前与数据输出端p3连接的缓冲器a-d交换。

[0041]

根据电路100的使用情况,控制逻辑电路130可以应用一种、多种或所有前述规则,

这些规则在图3中借助流程图示例性地阐释。在此,发送器200、300可以随时将数据写入电路100中并且接收器100可以随时从电路100读出数据。

[0042]

如图4a和图4b中所示,电路100具有两个状态,即“empty”(空)和“filled”(满)。在重新启动或者复位之后,电路100处于状态“empty”中。如果在该状态下发送器200、300和接收器400同时请求缓冲器交换,则直接交换与相应的发送器200、300和接收器400连接的缓冲器a-d并且电路100留在状态“empty”中。然而,如果在该状态下仅一个发送器200、300请求缓冲器交换,则将与相应的发送器200、300连接的缓冲器a-d与空闲的缓冲器(“交换缓冲器”,swap-buffer)并且电路100更换至状态“filled”。

[0043]

如果在该状态下还是仅一个发送器200、300(但是接收器400没有同时)请求缓冲器交换,则将与相应的发送器200、300连接的缓冲器a-d与空闲的缓冲器a-d(“交换缓冲器”,swap-buffer)交换并且电路100留在状态“filled”中。然而,如果接收器400请求缓冲器交换,则将与接收器400连接的缓冲器a-d与空闲的缓冲器a-d(“交换缓冲器”,swap-buffer)交换,或者在由接收器400和发送器200、300同时请求缓冲器交换的情况下,直接与同相应的发送器200、300连接的缓冲器交换并且电路100过渡到状态“empty”中。

[0044]

除了图3、图4a和图4b中阐释的规则之外,控制逻辑电路130还可以设计成遵循(任意)其他规则。例如,控制逻辑电路130可以设计成,将电路100的运行划分成周期并且在写入和交换与数据输入端p1、p2连接的缓冲器a-d之后,抑制随后在相同周期内写入的缓冲器a-d的交换。例如,控制逻辑电路130可以设计成,在写入和交换与数据输入端p1、p2连接的缓冲器a-d之后设置旗标(即指示值)并且在设置旗标期间,抑制与数据输入端p1、p2连接的缓冲器a-d的交换,其中,在每个周期结束时重置旗标。在此,周期的结束通过时间间隔到期或者通过接受周期信号来定义。由此可以实现确定更快速的两个冗余数据通道的优先级。

[0045]

例如,第一发送器200和第二发送器300传输冗余的数据d1、d2,从而在无错误的运行中,第一数据d1和第二数据d2彼此一致并且(基本上)同时被接收。例如,如图5中所示,第一发送器200和第二发送器300可以与数据生产者500和电路100一起设置在环形拓扑中,其中,数据d1、d2的(沿两个环形方向的)传输冗余地进行。例如,数据生产者500可以设计成,在无错误的运行中在规则的间隔中将数据包通过发送器200、300(例如可以构造为收发器)和电路100传输至接收器400,其中,接收器400在规则的间隔中请求电路100的数据包,或者在规则的间隔中从电路100读出数据包。

[0046]

附图标记列表

[0047]

100 电路

[0048]

110 第一开关

[0049]

120 第二开关

[0050]

130 控制逻辑电路

[0051]

200 第一发送器

[0052]

300 第二发送器

[0053]

400 接收器

[0054]

500 数据生产者

[0055]

1000 系统

[0056]

a 缓冲器

[0057]

b 缓冲器

[0058]

c 缓冲器

[0059]

d 缓冲器

[0060]

p1 第一数据输入端

[0061]

p2 第二数据输入端

[0062]

p3 数据输出端。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1