存储器装置及其操作方法与流程

1.本发明是有关于一种存储器装置及其操作方法。

背景技术:

2.大数据(big data)、人工智能(ai)和机器学习为目前市场焦点。ai运算上需要大量乘积累加运算(mac,multiply accumulate)。近来,ai硬件需要高性能且低功率的mac解决方案。存储器内运算(in-memory computation)已为广泛提出,因为可直接在存储器阵列内执行mac,减少数据搬移,以节省功率与延迟。

3.故而,如何实施存储器内大量数据运算,对于大数据、ai、机器学习等领域亦为重要关键。

技术实现要素:

4.根据本案一实例,提出一种存储器装置,包括:一存储器阵列,包括多个存储器单元与多条位线;以及一电流转换电路,耦接至该存储器阵列。其中,于执行一运算操作时,该存储器阵列的这些存储器单元产生相关于一运算操作结果的一源极电流。该源极电流由该电流转换电路转换成一输出数值,用以提供一下一运算操作的一输入信号。

5.根据本案更一实例,提出一种存储器装置的操作方法,该存储器装置包括一存储器阵列,该存储器阵列包括多个存储器单元与多条位线,该操作方法包括:于执行一运算操作时,该存储器阵列的这些存储器单元产生相关于一运算操作结果的一源极电流;以及将该源极电流转换成一输出数值,用以提供一下一运算操作的一输入信号。

6.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

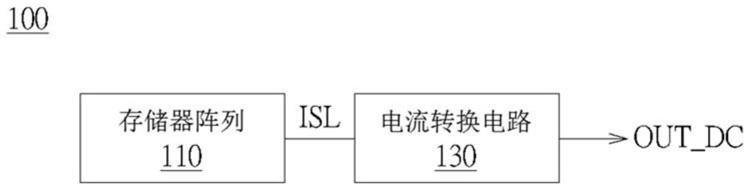

7.图1绘示依照本案一实施例的存储器装置的功能方块图。

8.图2绘示依照本发明一实施例的存储器阵列的源端感应示意图。

9.图3绘示依照本发明一实施例的电流转换电路示意图。

10.图4绘示依照本发明另一实施例的电流转换电路示意图。

11.图5绘示依照本发明又一实施例的电流转换电路示意图。

12.【符号说明】

13.100:存储器装置

14.110:存储器阵列

15.130:电流转换电路

16.isl、isl1、isl2:源极电流

17.out_dc:输出数值

18.wl0~wln:字线

19.bl1~bl2:位线

20.ssl1~ssl2:串选择线

21.sl1~sl2:源极线

22.t:存储器单元

23.bk1~bk2:区块

24.130a、130b、130c:电流转换电路

25.a1~a3:操作放大器

26.mp11~mp13、mn11~mn12、mp21~mp23、mn21~mn28_p、mp31、mn31~mn33:晶体管

27.iref1、iref2:参考电流源

28.vref:参考电压

29.n11~n12、n3:节点

30.out1~out2:输出端

31.vdd:操作电压

32.i11~i12、i21~i22、i3:电流

33.410:控制逻辑电路

34.out_dc:输出数值

35.en0~enp:使能信号

36.vb1:偏压电压

37.rl:电阻

38.510:模拟数字转换器

39.vb2:偏压电压

40.305、405、505:电压调整电路

具体实施方式

41.本说明书的技术用语是参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释是以本说明书的说明或定义为准。本揭露的各个实施例分别具有一或多个技术特征。在可能实施的前提下,本技术领域普通技术人员可选择性地实施任一实施例中部分或全部的技术特征,或者选择性地将这些实施例中部分或全部的技术特征加以组合。

42.图1绘示依照本案一实施例的存储器装置的功能方块图。如图1所示,依照本案一实施例的存储器装置100包括:存储器阵列110与电流转换电路130。

43.存储器阵列110耦接至电流转换电路130。当于人工智能运算中执行乘积累加运算(mac,multiply accumulate)时,存储器阵列110会产生相关于乘积累加运算结果的一源极电流isl。电流转换电路130会将源极电流isl转换成输出数值out_dc,该输出数值out_dc代表乘积累加运算结果。输出数值out_dc可以当成下一运算操作的输入信号。例如,以单个存储器装置100当成一级运算单元的话,则该存储器装置100执行乘积累加运算所得的输出数值out_dc可以输入至下一级运算单元(亦即另一个存储器装置100),以继续进行ai运算。

44.图2绘示依照本发明一实施例的存储器阵列的源极端感应示意图。图2以存储器阵列为三维(3d)存储器阵列为例做说明,但当知本案并不受限于此。

45.如图2所示,存储器阵列110包括:多个字线wl0~wln(n为正整数),多条位线(以bl1~bl2为例),多条串选择线(以ssl1~ssl2为例),多条源极线sl1~sl2,以及多个存储器单元t。这些存储器单元t形成于字线与位线的交叉处。存储器阵列110包括多个区块(bk1,bk2,...)。

46.底下说明以位线电压当成输入,而将与字线耦接的存储器单元t的电导(cell conductance,gcell)当成权重,来进行乘积累加运算的例子。其中,存储器单元t所产生的电流icell可为位线电压vbl与存储器单元的权重(例如但不受限于为电导gcell)的乘积(icell=vbl

×

gcell)。但当知本案并不受限于此。

47.当具有多个存储器单元t时,源极线sl1或sl2耦接至这些存储器单元t的源极,这些存储器单元t所产生的电流会经由这些条源极线sl1~sl2输出加总成为源极电流isl。

48.更进一步说明,以图2为例,区块bk1可包含:耦接至字线wl1的至少一组存储器单元串,以及串选择线ssl1。该存储器单元串具有多个相互耦接的存储器单元t。于进行乘积累加运算时,在区块bk1内的串选择线ssl1被开启。当字线wl1被选择时,与字线wl1耦接的这些存储器单元t将被导通,其中,字线wl1上的这些存储器单元t的权重可分别为w1与w2,而位线bl1具有位线电压vbl1,位线bl2具有位线电压vbl2,当进行乘积累加运算时,与字线wl1耦接的这些存储器单元t所产生的源极电流isl1便可如下表示:

49.isl1=vbl1

×

w1+vbl2

×

w2。如果输入与权重皆以逻辑电平表示,逻辑1为高电平,逻辑0为低电平,举例而言,当vbl1=1,vbl2=0,w1=1,w2=1,则isl1=1

×

1+0

×

1=1。

50.再更进一步说明,仍以图2为例,区块bk1具有多个阵列存储器单元串,这些存储器单元串相互耦接在一起,并且分别与对应的字线(wl1~wln)耦接。于进行乘积累加运算时,在区块bk1内的串选择线ssl1被选择开启。当有字线wl1~wln被选择时,这些存储器单元t将被导通,当进行乘积累加运算时,位线电压vbl1与vbl2与这些存储器单元t的各个权重相乘加总,因而产生对应于区块bk1的源极电流isl1。同样的,区块bk2也具有多个阵列存储器单元串,这些存储器单元串相互耦接在一起,并且也分别与对应的字线(wl1~wln)耦接。于进行乘积累加运算时,在区块bk2内的串选择线ssl2被开启时,同样可产生对应于区块bk2的源极电流isl2。此时存储器阵列110所输出的源极电流isl=isl1+isl2。

51.因此,这些存储器单元可经由前述方式被感应以产生源极电流isl。亦即,存储器阵列110所输出的源极电流isl为多个区块内的这些存储器单元所产生的源极电流的总和。

52.图3绘示依照本发明一实施例的电流转换电路示意图。电流转换电路130a包括:电压调整电路305、晶体管mp12~mp13、mn11~mn12,以及参考电流源iref1。其中,电压调整电路305可以是操作放大器a1与晶体管mp11所组成。

53.操作放大器a1的两输入端分别耦接至参考电压vref与晶体管mp11的源极。操作放大器a1的输出端则耦接至晶体管mp11的栅极。操作放大器a1与晶体管mp11用以提供稳定的电压。详言之,通过操作放大器a1的负回授机制,可使得晶体管mp11的源极电压接近参考电压vref。由于晶体管mp11为导通,故而,使得晶体管mp11的漏极电压也接近晶体管mp11的源极电压与参考电压vref,亦即,节点n11的电压可接近于参考电压vref,如此可使得源极电流isl能稳定。

54.晶体管mp11具有:一源极接收源极电流isl;一栅极,耦接至操作放大器a1的输出端;以及一漏极,耦接至节点n11。

55.晶体管mn11具有:一源极与一栅极,耦接至节点n11;以及一漏极,耦接至参考电压vss,该参考电压可以是一接地电压。

56.晶体管mn12具有:一源极,耦接至一输出端out1;一栅极,耦接至晶体管mn11的栅极;以及一漏极,耦接至参考电压vss。晶体管mn11与mn12形成一第一电流镜,以镜射源极电流isl以产生电流i11。

57.晶体管mp12具有:一源极,耦接至一操作电压vdd;一栅极,耦接至晶体管mp13的栅极(亦即,节点n12);以及一漏极,耦接至输出端out1。

58.晶体管mp13具有:一源极,耦接至一操作电压vdd;一栅极,耦接至晶体管mp12的栅极(亦即,节点n12)与参考电流源iref1;以及一漏极,耦接至参考电流源iref1。

59.晶体管mp12与mp13形成一第二电流镜,以镜射参考电流iref1以产生电流i12。

60.以下将说明电流转换电路130a的操作。

61.通过晶体管mp11与操作放大器a1,可使得节点n11的节点电压约等于参考电压vref。通过由晶体管mn11与mn12所形成的第一电流镜,可以在晶体管mn12的电流路径上形成电流i11,其中,i11=isl。

62.相似地,通过由晶体管mp12与mp13所形成的第二电流镜,可以在晶体管mp12的电流路径上形成电流i12,其中,i12=iref1。

63.因此,输出端out1的电位可由晶体管mp12的上拉强度(pull up strength)与晶体管mn12的下拉强度(pull down strength)来决定。故而,如果电流i11(=源极电流isl)大于电流i12(=参考电流iref1),则out1所输出的数值可为高电平,例如逻辑1;反之,如果电流i11(=源极电流isl)小于电流i12(=参考电流iref1),则out1所输出的数值可为低电平,例如逻辑0。在本案实施例中,参考电流iref1的值是可以视需要而进行调整。例如,在一例中,参考电流iref1的值可设定为数值m,而在另一例中,参考电流iref1的值可设定数值m的倍数,例如但不限于2

×

m。

64.亦即,通过图3的电流转换电路130a可以得到乘积累加运算结果(out1),在图3中,out1即为输出数值out_dc。

65.图4绘示依照本发明另一实施例的电流转换电路示意图。电流转换电路130b包括:电压调整电压405、晶体管mp22~mp23、mn21~mn28_p(p为正整数),参考电流源iref2,以及控制逻辑电路410。其中,电压调整电路405可以是操作放大器a2与晶体管mp21所组成。

66.操作放大器a2、晶体管mp21~mp23、mn21与mn22的操作相同或相似于图3的操作放大器a1、晶体管mp11~mp13、mn11与mn12,故其操作细节在此省略。

67.控制逻辑电路410,在本实施例中,举例而言,可以是逐次逼近型缓存器逻辑(sar,successive approximation register logic)电路,控制逻辑电路410可以输出使能信号(或称为控制信号)en0~enp给晶体管mn26_0~mn26_p。晶体管mn25与mn26_0~mn26_p当成开关晶体管(亦可称为开关晶体管群组),用以控制iref1的数值。其中,i22=iref1。另,晶体管mn25的栅极接收偏压电压vb1,而偏压电压vb1使得晶体管mn25正常下为导通。使能信号en0~enp则控制晶体管mn26_0~mn26_p为导通或关闭。控制逻辑电路410根据电流i22与i21(亦即源极电流isl,i21=isl)而逐回合地产生与控制这些使能信号en0~enp,这些使能信号en0~enp控制该开关晶体管群组。

68.参考电流源iref2会流经晶体管mn24。晶体管mn24、mn27与mn28_0~mn28_p形成多

个电流镜(亦可称为电流镜群组)。举例而言,若晶体管mn24尺寸的宽长比为1,晶体管mn27尺寸的宽长比可为0.5,而晶体管mn28_0~mn28_p尺寸的宽长比可分别为20、21、...、2p。也就是说,流经晶体管mn27的电流为0.5

×

iref2;如果晶体管mn26_0为导通,则流经晶体管mn28_0的电流为20

×

iref2;如果晶体管mn26_1为导通,则流经晶体管mn28_1的电流为21

×

iref2;其余可依此类推。

69.以下将说明电流转换电路130b的操作。

70.通过晶体管mp21、操作放大器a2、晶体管mn21与mn22,可以在晶体管mn22的电流路径上形成电流i21,其中,i21=isl。亦即,通过由晶体管mn21与mn22所形成的第三电流镜来镜射源极电流isl以产生电流i21。

71.相似地,通过由晶体管mp22与mp23所形成的电流镜,可以在晶体管mp22的电流路径上形成电流i22,其中,电流i22可为晶体管mn27与mn28_0~mn28_p的电流总和。亦即,通过由mp22与mp23所形成的第四电流镜来镜射参考电流iref1以产生电流i22。

72.如果电流i21(=源极电流isl)大于电流i22,则out2所输出的数值可为高电平,例如逻辑1;反之,如果电流i21(=源极电流isl)小于电流i22,则out2所输出的数值可为低电平,例如逻辑0。

73.通过逐回合地控制使能信号en0~enp,控制逻辑电路410可使得电流i22逐渐逼近源极电流isl。当电流i22最逼近源极电流isl时,控制逻辑电路410可以输出这些使能信号en0~enp。

74.亦即,通过图4的电流转换电路130b可以在晶体管mp23的电流路径上产生参考电流iref1。亦即,图4的晶体管mn24、参考电流源iref2、控制逻辑电路410、晶体管mn25、晶体管mn260~mn26_p、晶体管mn27、晶体管mn28_0~mn28_p可用以产生图3的参考电流iref1。

75.图5绘示依照本发明又一实施例的电流转换电路示意图。电流转换电路130c包括:电压调整电路505、晶体管mn31~mn33、电阻rl与模拟数字转换器(adc)510。其中,电压调整电路505可以是操作放大器a3与晶体管mp31所组成。图5的电流转换电路130c可以得到q位分辨率的乘积累加运算结果out_dc,其中,q为正整数,其代表模拟数字转换器(adc)510的分辨率。

76.操作放大器a3、晶体管mp31、mn31与mn32的操作相同或相似于图3的操作放大器a1、晶体管mp11、mn11与mn12,故其操作细节在此省略。

77.晶体管mn33具有:一源极,耦接电阻rl;一栅极,接收偏压电压vb2;以及一漏极,耦接至晶体管mn32的漏极。偏压电压vb2使得晶体管mn33在正常状态下为导通。

78.以下将说明电流转换电路130c的操作。

79.通过晶体管mp31、操作放大器a3、晶体管mn31与mn32,可以在晶体管mn32的电流路径上形成电流i3,其中,i3=isl。亦即,通过由晶体管mn31与mn32所形成的第五电流镜来镜射源极电流isl以产生电流i3。

80.由于电流i3亦流经电阻rl,故而,节点n3的节点电压为vdd-rl

×

i3,进一步将节点n3电压传送到adc510电路,节点n3的电压相关于源极电流isl的电流值,adc 510可将节点n3的电压,转换成乘积累加运算结果out_dc。

81.本案实施例应用源极端感应(source side sensing)来执行乘积累加运算。存储器单元电流代表输入(例如但不受限于,位线电压)与权重(例如但不受限于,存储器单元电

导)的乘积。多个存储器单元的各个源极耦接至共同节点,则这些存储器单元的各个存储器单元源极电流可被加总,以达成乘积累加运算的目的。所得到的乘积累加运算结果可以输入给其他级的乘积累加运算,或是输入到控制器(未示出)以当成特定信息或特定图样(pattern)辨识,进而可以应用于ai、大数据、机器学习等需要大量信息运算的领域。

82.在本案实施例中,存储器装置例如为3d nand闪存装置,但本案并不受限于此,本案亦可应用至其他类型的存储器,此皆在本案精神范围内。

83.在上例中,以位线电压当成输入而存储器单元电导当成权重,输入乘上权重得到存储器单元电流为例做说明,但当知本案并不受限于此。在本案其他可能实施例中,可以控制存储器单元电流的任意参阵列合也可以当成输入或权重,例加,输入可以是字线电压,而权重可以是存储器单元的阈值电压等,此皆在本案精神范围内。

84.综上所述,虽然本发明已以实施例揭露如上,然其并非用以限定本发明。本发明所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当以随附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1