数据处理装置的制作方法

1.本发明是关于数据处理装置,尤其是关于包含可协同运行的多个系统级芯片的数据处理装置。

背景技术:

2.系统级芯片(system on a chip,soc)设计是指将一个终端产品(或称系统)的主要功能整合进单一芯片,该单一芯片被称为soc。

3.低运算能力(low arithmetic capability)的系统级芯片通常用于较低阶的电子产品(例如:分辨率为1920

×

1080的电视),而高运算能力的系统级芯片通常用于较高阶的电子产品(例如:分辨率为3840

×

1920的电视)。考虑到不同运算能力的多种系统级芯片的总研发制造成本一定高于该多种系统级芯片的任一个的研发制造成本,以及考虑到高运算能力的系统级芯片用于低阶电子产品不符成本效益,本产业需要一种技术能够通过多个低运算能力的系统级芯片的组合来实现高运算能力,从而弹性地将单个低运算能力的系统级芯片用于低阶电子产品,以及将多个低运算能力的系统级芯片的组合用于高阶电子产品。

4.已知的多核(multi-core)与多集群(multi-cluster)技术包括通用中断控制器(generic interrupt controller,gic)、一致性网状网络(coherent mesh network,cmn)技术以及缓存一致互连加速器(cache coherent interconnect for accelerators,ccix)技术。上述技术并非着眼于不同系统级芯片的协同运行。

技术实现要素:

5.本公开的目的之一在于提供一种数据处理装置,包含可协同运行的多个系统级芯片,以实现更高的数据处理性能。

6.本公开的数据处理装置的一个实施例包含第一系统级芯片、外部电路与第二系统级芯片。该第一系统级芯片包含第一中央处理器(central processing unit,cpu)与第一收发电路。该第一中央处理器用来在加强处理模式下,将待处理数据分成多个输入部分,包含第一输入部分与第二输入部分;该第一中央处理器还用来在该加强处理模式下,取得并处理该第一输入部分以产生并输出第一输出数据。该第一收发电路耦接该第一中央处理器,用来在该加强处理模式下,取得该第二输入部分以传送该第二输入部分经由该外部电路至该第二系统级芯片;该第一收发电路还用来在该加强处理模式下,经由该外部电路接收第二输出数据,以发送该第二输出数据。该外部电路不包含于该第一系统级芯片与该第二系统级芯片的任一个中。该第二系统级芯片包含第二收发电路与第二中央处理器。该第二收发电路用来在该加强处理模式下,经由该外部电路接收该第二输入部分,以及输出该第二输出数据经由该外部电路至该第一系统级芯片。该第二中央处理器耦接该第二收发电路,用来在该加强处理模式下,接收该第二输入部分,并处理该第二输入部分以产生该第二输出数据;该第二中央处理器还用来在该加强处理模式下,输出该第二输出数据至该第二收发电路。

7.有关本发明的特征、实施与性能,在此配合附图作较佳实施例详细说明如下。

附图说明

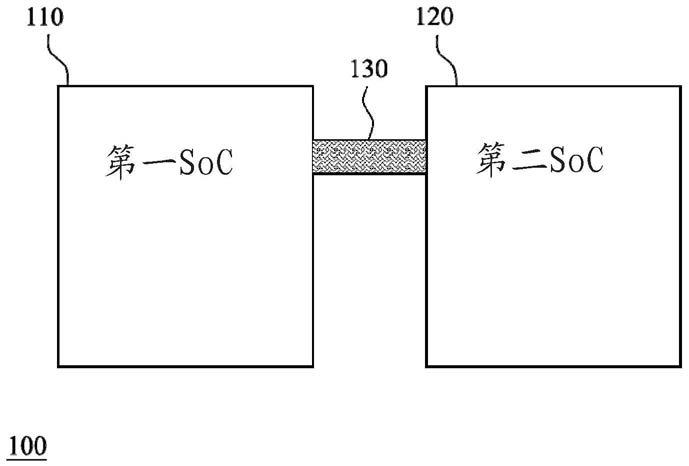

8.图1显示本公开的影像处理装置的一个实施例;

9.图2显示图1的第一soc与第二soc的一个实施例;

10.图3显示图1的第一soc与第二soc的另一个实施例;

11.图4显示影像处理管路可作为图3的第一/第二影像处理管路的一个实施例;

12.图5显示图1的第一soc与第二soc的又一实施例;

13.图6显示本公开的数据处理装置的一个实施例;

14.图7显示图6的第一soc与第二soc的一个实施例;

15.图8显示图6的第一soc与第二soc的协作示例;

16.图9显示图6的第一soc与第二soc的另一实施例;

17.图10显示本公开的图形处理装置的一个实施例;

18.图11显示图10的第一soc与第二soc的一个实施例;

19.图12显示图11的一个示例性实施的示意图;以及

20.图13显示图11的另一个示例性实施的示意图。

具体实施方式

21.本公开揭示一种影像处理装置、一种数据处理装置与一种图形处理装置,每种装置包含可协同运行的多个系统级芯片,以实现更高的处理性能。为帮助理解,以下说明包含多个实施例、示例与示例性实施,这些说明非用来限制本发明的实施范围。

22.图1显示本公开的影像处理装置的一个实施例。图1的影像处理装置100包含第一soc 110、第二soc 120以及外部电路130。第一soc 110作为主要soc,第二soc 120作为性能增强soc(performance-enhancing soc),它们具有相同或不同的电路配置(circuit configuration);然而,基于实施需求,第一soc 110和/或第二soc 120中的某些电路可能无实质作用。外部电路130不包含于第一soc 110与第二soc 120的任一个中。举例而言,若第一soc 110与第二soc 120均为已封装芯片(packaged chips)设于电路板(例如:印刷电路板)上,外部电路130会是/包含该电路板的信号传输线路。另举例而言,若第一soc 110与第二soc 120均为未封装裸片(non-packaged dies)包含于半导体封装,外部电路130会包含于该半导体封装,并视该半导体封装的型态(例如:打线封装、覆晶封装等等)而包括下列至少其中之一:至少一连接垫;至少一连接线;至少一金属球;以及至少一线路位于基板的表面或包含于该基板。

23.图2显示图1的第一soc 110与第二soc 120的一个实施例。如图2所示,第一soc 110包含数据分流电路112、第一影像处理电路114以及传送电路116,第二soc 120包含接收电路122以及第二影像处理电路124。第一soc 110与第二soc 120的每一个用来处理输入影像数据的一部分,以在不超出处理能力的前提下,通过协作达到更高的影像处理性能。第一soc 110与第二soc 120的各电路说明于下。

24.请参照图1-2。数据分流电路112用来将该输入影像数据分成n个输入部分,包含第一输入部分与第二输入部分,以供第一影像处理电路114与第二影像处理电路124分别进行

处理,其中该n为大于1的整数,其也表示影像处理装置100包含n个可协同运行的soc。在一个示例性实施中,数据分流电路112通过计算水平影像线的已接收的水平像素的数目来判断目前接收的水平像素的水平位置,从而将该输入影像数据分成左半边画面的数据与右半边画面的数据(当n=2),或将该输入影像数据分成更多个部分(当n》2),上述数据分流作法可通过已知技术来实现。在一个示例性实施中,该n为2,第一影像处理电路114与第二影像处理电路124的每一个的处理能力所表明的影像尺寸与帧率(frame rate)分别为7680像素

×

4320像素与60hz(简称8k4k60hz),或是该影像尺寸与帧率的等同(例如:后述的4k4k120hz),该输入影像数据的分流情形为下列其中之一:

25.(1)该输入影像数据的尺寸与帧率为8k4k60hz。该第一输入部分为该输入影像数据所对应的左半边画面的数据,其尺寸与帧率分别为3840像素

×

4320像素与60hz(简称4k4k60hz)。该第二输入部分为该输入影像数据所对应的右半边画面的数据,其尺寸与帧率也是4k4k60hz。

26.(2)该输入影像数据的尺寸与帧率为8k4k60hz。该第一输入部分为该输入影像数据所对应的左半边画面的数据以及一部分的右半边画面的数据,该第一输入部分的尺寸与帧率分别为(3840+n)像素

×

4320像素与60hz(简称(4k+n)4k60hz)。该第二输入部分为该输入影像数据所对应的右半边画面的数据以及一部分的左半边画面的数据,该第二输入部分的尺寸与帧率也是(4k+n)4k60hz。此情形下,该第一输入部分的右半边画面的数据与该第二输入部分的左半边画面的数据通常是毗邻该左右两半画面的衔接处的数据,用来给第一影像处理电路114与第二影像处理电路124参考,以帮助处理后的左右两半画面无缝地衔接。

27.(3)该输入影像数据的尺寸与帧率分别为3840像素

×

2160像素与120hz(简称4k2k120hz)。该第一输入部分为该输入影像数据所对应的左半边画面的数据,其尺寸与帧率分别为1920像素

×

2160像素与120hz(简称2k2k120hz)。该第二输入部分为该输入影像数据所对应的右半边画面的数据,其尺寸与帧率也是2k2k120hz。

28.(4)该输入影像数据的尺寸与帧率为4k2k120hz。该第一输入部分为该输入影像数据所对应的左半边画面的数据以及一部分的右半边画面的数据,该第一输入部分的尺寸与帧率分别为(1920+n)像素

×

2160像素与120hz(简称(2k+n)2k120hz)。该第二输入部分为该输入影像数据所对应的右半边画面的数据以及一部分的左半边画面的数据,该第二输入部分的尺寸与帧率也是(2k+n)2k120hz。此情形下,该第一输入部分的右半边画面的数据与该第二输入部分的左半边画面的数据通常是毗邻该左右两半画面的衔接处的数据,用来给第一影像处理电路114与第二影像处理电路124参考,以帮助处理后的左右两半画面无缝地衔接。

29.请参照图1-2。传送电路116耦接数据分流电路112,用来接收该第二输入部分,以输出该第二输入部分经由外部电路130至第二系统soc 120。接收电路122耦接外部电路130,用来接收该第二输入部分,以转送该第二输入部分给第二影像处理电路124。在一个示例性实施中,传送电路116与接收电路122之间的传输是基于已知或自行开发的信号传输标准(signaling standard)(例如:v-by-one hs标准或hdmi标准),而第一soc 110内的传输与第二soc 120内的传输都不用也不是基于该信号传输标准,该信号传输标准所支持的最大数据传输率通常不小于第二soc 120的影像数据处理能力。在一个示例性实施中,第一

soc 110包含第一加密电路(未显示),用来在输出该第二输入部分经由外部电路130至接收电路122前,加密该第二输入部分;第二soc 120包含第二解密电路(未显示),用来在收到该第二输入部分后,解密该第二输入部分。在一个示例性实施中,若第一soc 110有需要从第二soc 120接收数据,第一soc 110包含第一收发电路(例如:图3的第一收发电路310)包括传送电路116;若从第二soc 120接收的数据是加密过的,第一soc 110包含第一解密电路(未显示)以解密第二soc 120的数据;在本示例性实施中,若第二soc 120能够输出数据给第一soc 110,第二soc 120包含第二收发电路(例如:图3的第二收发电路320)包括接收电路122,第二soc 120可视实施需求包含第二加密电路(未显示),该第二加密电路在该第二收发电路输出数据给该第一收发电路前,加密该数据。上述加密电路与解密电路可通过已知或自行开发的技术(例如:高清数字内容保护(high-bandwidth digital content protection,hdcp))来实现。

30.请参照图1-2。第一影像处理电路114耦接数据分流电路112,用来接收并处理该第一输入部分,以产生输出影像数据的多个输出部分的第一输出部分给后端电路(例如:面板控制电路)。第二影像处理电路124耦接接收电路122,用来接收并处理该第二输入部分,以产生该输出影像数据的该多个输出部分的第二输出部分给该后端电路。举例而言,在前述情形(1)或(2)的情形下,当该第一/第二输出部分的尺寸与帧率分别为3840像素

×

4320像素与120hz(简称4k4k120hz)时,第一影像处理电路114/第二影像处理电路124包含已知或自行开发的帧率转换(frame rate conversion,frc)电路(例如:图4的frc电路420),该frc电路用来将该第一/第二输入部分的输入帧率(60hz)转换为该第一/第二输出部分的输出帧率(120hz),在该输出帧率分之一(1/120hz)的时间内,该第一输出部分与该第二输出部分构成完整图帧。另举例而言,在前述情形(3)或(4)的情形下,当该第一/第二输出部分的尺寸与帧率为4k4k120hz时,第一影像处理电路114/第二影像处理电路124包含已知或自行开发的缩放器(scaler)(例如:图4的缩放器430),用来将该第一/第二输入部分的尺寸(1920像素

×

2160像素,或(1920+n)像素

×

2160像素)缩放成该第一/第二输出部分的尺寸(3840像素

×

4320像素),在该第一/第二输出部分的帧率分之一(1/120hz)的时间内,该第一输出部分与该第二输出部分构成完整图帧。另外,视实施需求,第一影像处理电路114可输出该第一输出部分的至少一部分经由传送电路116与接收电路122给第二影像处理电路124,和/或第二影像处理电路124输出该第二输出部分的至少一部分经由前述第二收发电路与第一收发电路给第一影像处理电路114;举例而言,两个影像处理电路可交换待送给面板以显示的数据,并加以处理,以满足该面板的特殊需求。

31.值得注意的是,前述第一输出部分与第二输出部分的组合(例如:前述情形(1)~(4)的任一种情形下,左半边画面(4k4k120hz)与右半边画面(4k4k120hz)的组合(8k4k120hz))指出输出影像的尺寸与帧率,该输出影像的尺寸与帧率所共同决定的单位时间(per unit time)数据量(亦即:输出该输出影像的数据传输率)大于第一影像处理电路114的单位时间数据量处理能力(例如:4k4k120hz),也大于第二影像处理电路124的单位时间数据量处理能力(例如:4k4k120hz)。换言之,第一soc 110与第二soc 120的组合所达到的处理性能高于这两个soc的任一个的处理性能。

32.图3显示图1的第一soc 110与第二soc 120的另一实施例,尤其显示第一影像处理电路114与第二影像处理电路124的一个实施例。根据图3,第二soc 120的电路配置与第一

soc 110相同,因此,第一soc 110包含第一收发电路310包括传送电路116(未显示于图3),第二soc 120包含第二收发电路320包括接收电路122(未显示于图3),第二soc 120还包含另一数据分流电路330对应数据分流电路112,但数据分流电路330在此无实质作用而可被禁用或省略;另外,第一影像处理电路114与第二影像处理电路124具有相同的电路配置,其中部分电路可能无实质作用而可被禁用或省略。第一影像处理电路114包含第一延迟电路1142、第一选择电路1144与第一影像处理管路(image processing pipeline)1146;第二影像处理电路124包含第二延迟电路1242、第二选择电路1244与第二影像处理管路1246。值得注意的是,若该输入影像数据是/包含编码数据,第一影像处理电路114/第二影像处理电路124可进一步包含解码器(未显示),以解码该编码数据,以便第一影像处理管路1146/第二影像处理管路1246处理该解码数据。

33.请参照图3。考虑到数据分流电路112输出该第一输入部分至第一影像处理电路114的路径通常短于数据分流电路112输出该第二输入部分至第二影像处理电路124的路径,第一延迟电路1142用来接收并延迟该第一输入部分,以使第一影像处理电路114接收该第一输入部分的时间与第二影像处理电路124接收该第二输入部分的时间实质同步,实质同步是指上述接收时间的差异小于预定阈值,而可忽略。第一选择电路1144耦接于第一延迟电路1142与第一影像处理管路1146之间,并耦接第一收发电路310(如图3的短折虚线所示);第一选择电路1144用来从第一延迟电路1142接收该第一输入部分,以输出该第一输入部分至第一影像处理管路1146。第一影像处理管路1146耦接第一选择电路1144,用来接收并处理该第一输入部分,以产生前述第一输出部分。

34.请参照图3。第二延迟电路1242耦接数据分流电路330(如图3的短折虚线所示),但在此无实质作用。第二选择电路1244耦接第二延迟电路1242(如图3的短折虚线所示),并耦接于第二收发电路320与第二影像处理管路1246之间;第二选择电路1244用来从第二收发电路320接收该第二输入部分,以输出该第二输入部分至第二影像处理管路1246。第二影像处理管路1246耦接第二选择电路1244,用来接收并处理该第二输入部分,以产生前述第二输出部分。

35.请参照图3。在一个示例性实施中,第一影像处理管路1146与该第二影像处理管路1246交换一个或多个同步信号(例如:至少一个水平同步信号和/或至少一个垂直同步信号),以实质同步该第一输出部分与该第二输出部分。在一个示例性实施中,第一影像处理管路1146与该第二影像处理管路1246之间设有专用线路(未显示)以单向地或双向地做信号传输,其中该专用线路位于这两个soc之间的部分是包含于外部电路130;本领域普通技术人员可参照本发明图5的第一收发器525、外部电路570与第二收发器555及其相关说明,以了解如何实施该专用线路。关于第一影像处理管路1146与该第二影像处理管路1246之间的传输可能会有多种做法包括:

36.(1)利用前述专用线路以实现第一影像处理管路1146与该第二影像处理管路1246之间的传输。任一影像处理电路可按该输入影像数据的时序安排,接收/存取另一影像处理电路传来的数据,以及将来自数据分流电路112的数据处理后输出,上述数据在被输出至影像处理电路前,可暂存于缓冲器(未显示)中;

37.(2)利用的既有路径(亦即:第一收发电路310、外部电路130与第二收发电路320)来实现第一影像处理管路1146与该第二影像处理管路1246之间的传输。若同一时间该既有

610包含第一cpu 612与第一收发电路614,第二soc 620包含第二cpu 622与第二收发电路624。第一soc 610与第二soc 620的每一个用来处理待处理数据的一部分,以在不超出处理能力的前提下,通过协作达到更高的数据处理性能。第一soc 610与第二soc 620的各电路说明于下。

42.请参照图6-7。第一cpu 612用来在加强处理模式下(亦即:当第一soc 610与第二soc 620同时运行时),依据该待处理数据本身或其相关信息,将该待处理数据分成多个输入部分包含第一输入部分与第二输入部分;第一cpu 612还用来在该加强处理模式下,取得并处理该第一输入部分以产生并输出第一输出数据。举例而言,第一soc 610的至少一部分运行于开放执行环境(rich execution environment,ree);第二soc 620的全部运行于可信执行环境(trust execution environment,tee);该第一输入部分是非敏感数据例如通用作业系统(例如:开源作业系统)的系统运行数据;该第二输入部分是敏感数据例如下列至少其中之一:待验证数据(例如:身份识别数据诸如指纹数据、个人身份识别码(personal identification number,pin)、付款信息等等);机密(confidential/secret)数据(例如:私钥(private key)、凭证(certificate)等等);以及受保护数据(例如:数字版权管理(drm)数据诸如加密过的压缩视频数据)。上述例子中,该第二输入部分的敏感数据是通过外部电路630以从第一soc 610传送至第二soc 620,因此,若经由外部电路630(例如:电路板上的线路)传送的数据较容易被窃取,第一soc 610与第二soc 620之间的通讯通常须符合安全传输规范(例如:数字传输内容保护(digital transmission content protection,dtcp));若经由外部电路630(例如:半导体封装内的焊垫、焊球等)传送的数据较不易被窃取,第一soc 610与第二soc 620之间的通讯不一定要符合该安全传输规范。另举例而言,第一soc 610包含二部分分别运行于ree与tee,该第一输入部分是非敏感数据和/或敏感数据,由于该二部分之间的数据传输是同一soc内的数据传输,通常无需符合前述安全传输规范。

43.请参照图6-7。第一收发电路614耦接第一cpu 612,用来在该加强处理模式下,从第一cpu 612或存储器(例如:图9的系统存储器920)取得该第二输入部分,以传送该第二输入部分经由外部电路630至第二soc 620,第一收发电路614还用来在该加强处理模式下,经由外部电路630接收第二soc 620的第二输出数据,以转送该第二输出数据。第二收发电路624用来在该加强处理模式下,经由外部电路630接收该第二输入部分,以及输出该第二输出数据经由外部电路630至第一soc 610。第二cpu 622用来在该加强处理模式下,从第二收发电路624接收该第二输入部分,处理该第二输入部分以产生该第二输出数据,从而输出该第二输出数据至第二收发电路624。

44.请参照图6-7。在一个示例性实施中,第一cpu 612包含第一缓存存储器6122,第二cpu 622包含第二缓存存储器6222;当第一cpu 612处理该第一输入部分时,第一cpu 612使用第一缓存存储器6122储存相关于该第一输入部分的第一缓存数据(例如:待处理数据或已处理数据);当第二cpu 622处理该第二输入部分时,第二cpu 622使用第二缓存存储器6222储存相关于该第二输入部分的第二缓存数据(例如:待处理数据或已处理数据);该第一缓存数据与该第二缓存数据不一致(incoherent),换言之,第一cpu 612无需在意第二cpu 622处理该第二输入部分的进度,第二cpu 622也无需在意第一cpu 612处理该第一输入部分的进度,第一缓存存储器6122的储存数据与第二缓存存储器6222的储存数据无需一

致,这一点与现有技术(例如:ccix)有别。

45.为帮助了解,以下举一个示例性实施。第一soc 610与第二soc 610协作以处理网络视频流如图8所示。图8显示下述几个处理阶段:

46.(1)s810:第一soc 610将网络视频流服务的登录数据(亦即:敏感数据)输出至第二soc 620。

47.(2)s820:第二soc 620处理使用者帐户信息并进行验证。

48.(3)s830:第二soc 620处理drm相关事宜。

49.(4)s840:第一soc 610开始播放网络视频。

50.(5)s850:第一soc 610从网络接收加密过的网络视频流数据,再将加密过的网络视频流数据(亦即:敏感数据)输出至第二soc 620。

51.(6)s860:第二soc 620解密该加密过的网络视频流数据。

52.(7)s870:第二soc 620在dtcp保护下发送该解密过的数据给第一soc 610。

53.(8)s880:第一soc 610通过安全显示路径输出视频数据。

54.由于本领域普通技术人员能依据上述说明了解如何利用图6-7的电路来实现图8的各阶段,冗余的说明在此省略。

55.图9显示图6的第一soc 610与第二soc 620的另一实施例。如图9所示,第一soc 610除包含第一cpu 612与第一收发电路614外,还包含第一系统总线910、第一系统存储器920(例如:dram)、第一存储器存取电路930、第一加解密电路940与其它电路950(例如:网络电路、usb电路、音频电路、图形处理器等等);第二soc 620除包含第二cpu 622与第二收发电路624外,还包含第二系统总线960、第二系统存储器970(例如:dram)、第二存储器存取电路980、第二加解密电路990与其它电路995(例如:网络电路、usb电路、音频电路、图形处理器等等)。另外,第一cpu 612与第二cpu 622之间可选择性地设置专用线路如图9的虚线所示,以便这两个cpu单向地或双向地做信号传输(例如:中断请求(interrupt request,irq)的传输,和/或协同运行所需的控制信号/信息的传输),其中该专用线路位于这两个soc之间的部分是包含于外部电路630;若未设置该专用线路,该信号传输会是经由前述存储器存取电路、加解密电路与收发电路等所构成的路径。

56.请参照图6与图9。第一存储器存取电路930是已知或自行开发的电路,用来接收/转送第一cpu 612的指令或数据,并用来经由第一系统总线910存取第一系统存储器920;第一cpu 612也可视实施需求直接经由第一系统总线910存取第一系统存储器920。第一加解密电路940是已知或自行开发的电路,用来从第一存储器存取电路930取得该第二输入部分并将其加密,再提供该加密过的第二输入部分给第一收发电路614以供其输出给第二收发电路624。第一加解密电路940还用来从该第一收发电路614接收该第二输出数据并将其解密,以输出解密过的该第二输出数据给第一存储器存取电路930。第二soc 620的各电路的运行与上述第一soc 610的各电路的运行相仿,重复及冗余的说明在此省略。在一个示例性实施中,该第二输入部分包含压缩数据,第二cpu 622用来解压缩该压缩数据,以产生解压缩数据包含于该第二输出数据。在一个示例性实施中,该第二输入部分包含音频数据,第二cpu 622用来对该音频数据施以均衡(equalization)处理,以产生均衡音频数据包含于该第二输出数据。值得注意的是,上述加解密电路可视实施需求被禁用或省略。

57.请参照图6、7、9。在一个示例性实施中,第一soc 610与第二soc 620的每一个为电

视soc。在一个示例性实施中,第二soc 620在该加强处理模式下被启动,并在正常处理模式下被禁用以减少功耗,各模式可依据下列至少其中之一而定:使用者设定;第一cpu 612的目前性能指标;该待处理数据的性质(例如:敏感性或独立性)。在一个示例性实施中,该第一输出数据与该第二输出数据的组合指出单位时间数据量,该单位时间数据量大于第一cpu 612的单位时间数据量处理能力,也大于第二cpu 622的单位时间数据量处理能力,这表示数据处理装置600的处理能力优于第一soc 610与第二soc 620的任一个的处理能力。

58.图10显示本公开的图形处理装置的一个实施例。图10的图形处理装置1000包含第一soc 1010、第二soc 1020以及外部电路1030。第一soc 1010作为主要soc,第二soc 1020作为性能增强soc,它们具有相同或不同的电路配置;然而,基于实施需求,第一soc 1010和/或第二soc 1020中的某些电路可能无实质作用。外部电路1030不包含于第一soc 1010与第二soc 1020的任一个中。举例而言,若第一soc 1010与第二soc 1020均为已封装芯片设于电路板(例如:印刷电路板)上,外部电路1030会是/包含该电路板的信号传输线路。另举例而言,若第一soc 1010与第二soc 1020均为未封装裸片包含于半导体封装,外部电路1030会包含于该半导体封装,并视该半导体封装的型态(例如:打线封装、覆晶封装等等)而包括下列至少其中之一:至少一连接垫;至少一连接线;至少一金属球;以及至少一线路位于基板的表面或包含于该基板。

59.图11显示图10的第一soc 1010与第二soc 1020的一个实施例。如图11所示,第一soc 1010包含第一gpu 1012以及第一收发电路1014,第二soc 1020包含第二gpu 1022以及第二收发电路1024。第一soc 1010与第二soc 1020的每一个用来处理待处理数据的一部分,以在不超出处理能力的前提下,通过协作达到更高的图形处理性能。第一soc 1010与第二soc 1020的各电路说明于下。

60.请参照图10-11。第一gpu 1012用来在一加强处理模式下(亦即:当第一soc 1010与第二soc 1020同时运行时),将该待处理数据分成多个输入部分包含第一输入部分与第二输入部分;第一gpu 1012还用来在该加强处理模式下,取得并处理该第一输入部分以产生并输出第一输出数据。第一收发电路1014用来在该加强处理模式下,从第一gpu 1012或从受控于第一gpu 1012的存储器存取电路(未显示)取得该第二输入部分,以传送该第二输入部分经由外部电路1030至第二soc 1020;第一收发电路1014还用来在该加强处理模式下,经由外部电路1030接收第二输出数据,以输出该第二输出数据。第二收发电路1024用来在该加强处理模式下,经由外部电路1030接收该第二输入部分,以及传送该第二输出数据经由外部电路1030至第一soc 1010。第二gpu 1022用来在该加强处理模式下,从第二收发电路1024接收该第二输入部分,并处理该第二输入部分以产生该第二输出数据。第二gpu 1022还用来在该加强处理模式下,输出该第二输出数据至第二收发电路1024。

61.请参照图10-11。在一个示例性实施中,第一gpu 1012包含第一缓存存储器1110,第二gpu 1022包含第二缓存存储器1120;当第一gpu 1012处理该第一输入部分时,第一gpu 1012使用第一缓存存储器1110储存相关于该第一输入部分的第一缓存数据(例如:待处理数据或已处理数据);当第二gpu 1022处理该第二输入部分时,第二gpu 1022使用第二缓存存储器1120储存相关于该第二输入部分的第二缓存数据(例如:待处理数据或已处理数据);该第一缓存数据与该第二缓存数据不一致,换言之,第一gpu 1012无需在意第二gpu 1022处理该第二输入部分的进度,第二gpu 1022也无需在意第一gpu 1012处理该第一输入

部分的进度,第一缓存存储器1110的储存数据与第二缓存存储器1120的储存数据无需一致,这一点与现有技术(例如:ccix)有别。

62.承上所述,举例而言,第一soc 1010执行第一应用程序(application)(例如:摄影应用程序或第二游戏应用程序)与第二应用程序(例如:聊天应用程序),第二soc 1020执行第三应用程序(例如:第一游戏应用程序),该第一输入部分包含该第一应用程序相关数据与该第二应用程序相关数据(亦即:待第一gpu 1012施以渲染(rendering)处理的数据),该第二输入部分包含该第三应用程序相关数据与控制该第三应用程序的执行的键盘/鼠标事件的数据(亦即:待第二gpu 1022施以渲染处理的数据),该第一输出数据包含第一渲染数据(例如:该第一应用程序的画面数据)与第二渲染数据(例如:该第二应用程序的画面数据),该第二输出数据包含第三渲染数据(例如:该第三应用程序的画面数据)与中断请求,第一soc 1010执行中断服务例程(interrupt service routine,isr)(例如:图12的中断服务例程1210),以依据该中断请求将该第三渲染数据写入数据暂存电路(例如:图12的数据暂存电路1220),此外,第一soc 1010执行软件(例如:图12的已知的阿尔法混合(alpha blending)软件1230)以从该数据暂存电路读取该第三渲染数据,并迭加该第一、第二与第三渲染数据以显示于同一层osd画面。图12为上例的示意图,其中数据暂存电路1220的一个示例包含三级暂存器以环形连接(未显示),第一soc 1010将该第三渲染数据写入数据暂存电路1220的x

th

暂存器后,会更新数据暂存电路1220的写入指针(write pointer)以使其从指向x

th

暂存器改为指向(x+1)

th

暂存器,而第一soc 1010从数据暂存电路1220的x

th

暂存器读取该第三渲染数据前,也会更新数据暂存电路1220的读取指针(read pointer)以使其从指向(x+2)

th

暂存器改为指向x

th

暂存器,x、(x+1)与(x+2)为三个连续的整数,(x+2)的下一个数字为x以构成循环。值得注意的是,上述isr与利用软件进行迭加的技术均可通过已知或自行开发的技术来实现。

63.另举例而言,该第一输入部分包含主要使用者界面数据(亦即:待第一gpu 1012施以渲染处理的数据),该第二输入部分包含二维数据/位置数据(亦即:待第二gpu 1022施以渲染处理的数据)与中断请求用来使该第二gpu 1022接收并处理该第二输入部分,该第一输出数据包含第一渲染数据,该第二输出数据包含第二渲染数据(例如:增强现实(augmented reality,ar)数据或虚拟现实(virtual reality,vr)数据),第一soc 1010通过硬件(例如:图13的已知的屏幕显示(on screen display,osd)产生硬件1310)迭加图形,将该第一渲染数据显示于第一层osd画面以及将该第二渲染数据显示于第二层osd画面。值得注意的是,上述利用通过硬件迭加图形的技术均可通过已知或自行开发的技术来实现。图13为上例的示意图。

64.请参照图10。在一个示例性实施中,第一soc 1010与第二soc 1020的每一个为电视soc。在一个示例性实施中,第二soc 1020在该加强处理模式下被启动,并在正常处理模式下被禁用以减少功耗,各模式可依据下列至少其中之一而定:使用者设定;第一gpu 1012的目前性能指标;该待处理数据的性质(例如:高运算资源需求)。在一个示例性实施中,该第一输出数据与该第二输出数据的组合指出单位时间数据量,该单位时间数据量大于第一gpu 1012的单位时间数据量处理能力,也大于第二gpu 1022的单位时间数据量处理能力,这表示数据处理装置1000的处理能力优于第一soc 1010与第二soc 1020的任一个的处理能力。

65.请参照图10,并同参照图5/图9。在一个实施示例中,第一soc 1010包含第一cpu与第一系统总线(未显示),第一gpu 1012经由该第一系统总线与该第一cpu沟通,以利用该第一cpu的运算资源;该第二soc 1020包含第二cpu与第二系统总线,第二gpu 1022经由该第二系统总线与该第二cpu沟通,以利用该第二cpu的运算资源。

66.请注意,在实施为可能的前提下,本领域普通技术人员可选择性地实施前述任一实施例中部分或全部技术特征,或选择性地实施前述多个实施例中部分或全部技术特征的组合,由此增加实施本发明的弹性。

67.综上所述,本公开的影像处理装置、数据处理装置与图形处理装置的每一个可通过协同运行的多个soc来实现较高的处理性能。

68.虽然本发明的实施例如上所述,然而这些实施例并非用来限定本发明,本领域普通技术人员可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的权利要求范围,换言之,本发明的权利要求范围须视本说明书的权利要求书所界定的为准。

69.附图标记说明

70.100:影像处理装置

71.110:第一soc

72.120:第二soc

73.130:外部电路

74.112:数据分流电路

75.114:第一影像处理电路

76.116:传送电路

77.122:接收电路

78.124:第二影像处理电路

79.310:第一收发电路

80.320:第二收发电路

81.330:数据分流电路

82.1142:第一延迟电路

83.1144:第一选择电路

84.1146:第一影像处理管路

85.1242:第二延迟电路

86.1244:第二选择电路

87.1246:第二影像处理管路

88.400:影像处理管路

89.410:影像特性调整电路

90.420:帧率转换电路

91.430:缩放器

92.510:第一系统总线

93.520:第一处理器

94.525:第一收发器

95.530:其它电路

96.540:第二系统总线

97.550:第二处理器

98.555:第二收发器

99.560:其它电路

100.570:外部电路

101.600:数据处理装置

102.610:第一soc

103.620:第二soc

104.630:外部电路

105.612:第一cpu

106.614:第一收发电路

107.622:第二cpu

108.624:第二收发电路

109.6122:第一缓存存储器

110.6222:第二缓存存储器

111.s810~s880:视频流处理阶段

112.910:第一系统总线

113.920:第一系统存储器

114.930:第一存储器存取电路

115.940:第一加解密电路

116.950:其它电路

117.960:第二系统总线

118.970:第二系统存储器

119.980:第二存储器存取电路

120.990:第二加解密电路

121.995:其它电路

122.1000:图形处理装置

123.1010:第一soc

124.1020:第二soc

125.1030:外部电路

126.1012:第一gpu

127.1014:第一收发电路

128.1022:第二gpu

129.1024:第二收发电路

130.1110:第一缓存存储器

131.1120:第二缓存存储器

132.1210:中断服务例程

133.1220:数据暂存电路

134.1230:阿尔法混合软件

135.1310:osd产生硬件

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1