C型通用串行总线转接板的制作方法

c型通用串行总线转接板

技术领域

1.本发明涉及一种转接板,特别是c型通用串行总线转接板。

背景技术:

2.目前,市面常见的c型通用串行总线转接板是由c型通用串行总线母连接器、信号转接电路板与插针端所构成,c型通用串行总线母连接器通过信号转接电路板与插针端的多个插针电性连接。c型通用串行总线母连接器连接对应线缆接入信号,插针端通过杜邦线引出使用者所需的信号,相对于直接在引脚密集的c型通用串行总线母连接器引出使用者所需的信号,十分方便。但是,在实际生产应用时,c型通用串行总线转接板每次与线缆进行连接时,需先对插针端的该些插针进行信号定义的核对(即先确定每一插针所引出的信号是何种信号),十分影响效率,且杜邦线与插针的连接极易松动,容易造成接触不良,会造成应用时极大的不便。

3.综上所述,可知现有技术中长期以来一直存在传统c型通用串行总线转接板在每次与线缆连接时需要核对每一插针的信号定义是否正确所造成的耗时问题,以及因杜邦线与插针的连接所造成连接容易松动的问题,因此实有必要提出改进的技术手段,来解决此问题。

技术实现要素:

4.为解决上述现有技术所存在的问题,本发明公开一种c型通用串行总线转接板。

5.本发明公开一种c型通用串行总线转接板,其包括:电路板、c型通用串行总线连接器与联合测试行动组(joint test action group,jtag)连接器,c型通用串行总线连接器电性连接于电路板的一侧,jtag连接器电性连接于电路板的另一侧。c型通用串行总线连接器包括第一左接地引脚、第一右接地引脚、第一时钟(test clock,tck)引脚、第一数据输入(test data in,tdi)引脚、第一数据输出(test data out,tdo)引脚、第一测试模式选择(test mode select,tms)引脚、第二左接地引脚、第二右接地引脚、第二时钟引脚、第二数据输入引脚、第二数据输出引脚与第二测试模式选择引脚;jtag连接器包括多个第三接地引脚、第三时钟引脚、第三数据输入引脚、第三数据输出引脚与第三测试模式选择引脚。其中,第一左接地引脚、第一右接地引脚、第二左接地引脚、第二右接地引脚与该些第三接地引脚通过电路板连接在一起,以形成接地线网;第一数据输入引脚、第二数据输入引脚与第三数据输入引脚通过电路板连接在一起,以形成数据输入线网;第一数据输出引脚、第二数据输出引脚与第三数据输出引脚通过电路板连接在一起,以形成数据输出线网;第一测试模式选择引脚、第二测试模式选择引脚与第三测试模式选择引脚通过电路板连接在一起,以形成测试模式选择线网;第一时钟引脚、第二时钟引脚与第三时钟引脚通过电路板连接在一起,以形成时钟线网。

6.在一实施例中,c型通用串行总线连接器支持usb 3.0的传输规格。

7.在一实施例中,jtag连接器为带锁扣的连接器或防呆连接器。

8.在一实施例中,当c型通用串行总线转接板应用在边界扫描(boundary scan)的测试环境下时,c型通用串行总线连接器用以连接接口转接板,接口转接板为治具检测双列直插式存储器模块插槽(dimm slot)时所使用的转接板;jtag连接器用以连接测试存取端口(test access port,tap)主控板卡。

9.在一实施例中,c型通用串行总线连接器为母连接器。

10.本发明所公开的c型通用串行总线转接板如上,与现有技术的差异在于本发明是通过与c型通用串行总线连接器与联合测试行动组连接器电性连接的电路板,使得c型通用串行总线连接器与联合测试行动组连接器的接地引脚形成接地线网,c型通用串行总线连接器与联合测试行动组连接器的数据输出引脚形成数据输出线网,c型通用串行总线连接器与联合测试行动组连接器的数据输入引脚形成数据输入线网,c型通用串行总线连接器与联合测试行动组连接器的时钟引脚形成时钟线网,c型通用串行总线连接器与联合测试行动组连接器的测试模式选择引脚形成测试模式选择线网。

11.通过上述的技术手段,本发明不仅可引出c型通用串行总线连接器所需的信号,还可节省传统c型通用串行总线转接板因需核对每一插针的信号定义是否正确所耗费的时间,还可提高连接稳定性。此外,当jtag连接器为带锁扣的连接器或防呆连接器时,可以保证jtag连接器与线缆进行连接时插接方向是固定的,预防插接错误,且自带锁扣的jtag连接器也保证了线缆连接的稳固性。

附图说明

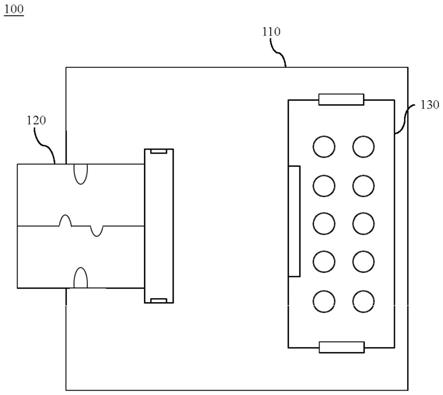

12.图1为本发明c型通用串行总线转接板的一实施例外观示意图。

13.图2为图1的c型通用串行总线连接器的一实施例示意图。

14.图3为图1的jtag连接器的一实施例示意图。

15.附图标记说明:

16.21

ꢀꢀꢀ

第一左接地引脚

17.22

ꢀꢀꢀ

第一右接地引脚

18.23

ꢀꢀꢀ

第一时钟引脚

19.24

ꢀꢀꢀ

第一数据输入引脚

20.25

ꢀꢀꢀ

第一数据输出引脚

21.26

ꢀꢀꢀ

第一测试模式选择引脚

22.27

ꢀꢀꢀ

第二左接地引脚

23.28

ꢀꢀꢀ

第二右接地引脚

24.29

ꢀꢀꢀ

第二时钟引脚

25.30

ꢀꢀꢀ

第二数据输入引脚

26.31

ꢀꢀꢀ

第二数据输出引脚

27.32

ꢀꢀꢀ

第二测试模式选择引脚

28.51

ꢀꢀꢀ

第三接地引脚

29.52

ꢀꢀꢀ

第三时钟引脚

30.53

ꢀꢀꢀ

第三数据输入引脚

31.54

ꢀꢀꢀ

第三数据输出引脚

32.55

ꢀꢀꢀ

第三测试模式选择引脚

33.100c 型通用串行总线转接板

34.110

ꢀꢀ

电路板

35.120c 型通用串行总线连接器

36.130

ꢀꢀ

联合测试行动组连接器

具体实施方式

37.以下将配合图式及实施例来详细说明本发明的实施方式,借此对本发明如何应用技术手段来解决技术问题并达成技术功效的实现过程充分理解并据以实施。

38.请参阅图1,图1为本发明c型通用串行总线转接板的一实施例外观示意图。在本实施例中,c型通用串行总线转接板100可包括:电路板110、c型通用串行总线连接器120与联合测试行动组(joint test action group,jtag)连接器130,c型通用串行总线连接器120可电性连接于电路板110的一侧,jtag连接器130可电性连接于电路板110的另一侧。其中,c型通用串行总线连接器120可支持usb 3.0的传输规格(即c型通用串行总线连接器120可支持市售usb 3.0type-c的线材)。在本实施例中,c型通用串行总线连接器120可为但不限于母连接器,换句话说,在另一实施例中,c型通用串行总线连接器120可为公连接器。

39.此外,在本实施例中,c型通用串行总线连接器120对外的连接方向为图面的左右方向,jtag连接器130对外的连接方向为垂直图面的方向(即远离图面或接近图面),但本实施例并非用以限定本发明,可依据实际需求进行调整。

40.请参阅图2,图2为图1的c型通用串行总线连接器的一实施例示意图。在本实施例中,c型通用串行总线连接器120可包括第一左接地引脚21、第一右接地引脚22、第一时钟(test clock,tck)引脚23、第一数据输入(test data in,tdi)引脚24、第一数据输出(test data out,tdo)引脚25、第一测试模式选择(test mode select,tms)引脚26、第二左接地引脚27、第二右接地引脚28、第二时钟引脚29、第二数据输入引脚30、第二数据输出引脚31与第二测试模式选择引脚32。其中,c型通用串行总线连接器120为标准c型通用串行总线连接器。

41.请参阅图3,图3为图1的jtag连接器的一实施例示意图。在本实施例中,jtag连接器130可包括多个第三接地引脚51、第三时钟引脚52、第三数据输入引脚53、第三数据输出引脚54与第三测试模式选择引脚55。其中,第三接地引脚51的数量可为但不限于五个,jtag连接器130可为具有2x5个引脚的连接器。

42.在本实施例中,c型通用串行总线连接器120的第一左接地引脚21、第一右接地引脚22、第二左接地引脚27与第二右接地引脚28以及jtag连接器130的该些第三接地引脚51可通过电路板110连接在一起,以形成接地线网;c型通用串行总线连接器120的第一数据输入引脚24与第二数据输入引脚30以及jtag连接器130的第三数据输入引脚53可通过电路板110连接在一起,以形成数据输入线网;c型通用串行总线连接器120的第一数据输出引脚25与第二数据输出引脚31以及jtag连接器130的第三数据输出引脚54可通过电路板110连接在一起,以形成数据输出线网;c型通用串行总线连接器120的第一测试模式选择引脚26与第二测试模式选择引脚32以及jtag连接器130的第三测试模式选择引脚55可通过电路板110连接在一起,以形成测试模式选择线网;c型通用串行总线连接器120的第一时钟引脚23

与第二时钟引脚29以及jtag连接器130的第三时钟引脚52可通过电路板110连接在一起,以形成时钟线网。

43.因此,c型通用串行总线转接板100不仅可引出c型通用串行总线连接器120所需的信号,还可节省了传统c型通用串行总线转接板因需要核对每一插针的信号定义是否正确所耗费的时间,还可提高连接稳定性。

44.此外,jtag连接器130可为带锁扣的连接器或防呆连接器,因此,可以保证jtag连接器130与线缆进行连接时插接方向是固定的,预防插接错误,且自带锁扣的jtag连接器130也保证了线缆连接的稳固性。

45.另外,当c型通用串行总线转接板100应用在边界扫描(boundary scan)的测试环境下时,c型通用串行总线连接器120可用以连接接口转接板(未绘制),接口转接板可为治具检测双列直插式存储器模块插槽(dimm slot)时所使用的转接板;jtag连接器130可用以连接测试存取端口(test access port,tap)主控板卡(未绘制)。

46.综上所述,可知本发明与现有技术之间的差异在于通过与c型通用串行总线连接器与联合测试行动组连接器电性连接的电路板,使得c型通用串行总线连接器与联合测试行动组连接器的接地引脚形成接地线网,c型通用串行总线连接器与联合测试行动组连接器的数据输出引脚形成数据输出线网,c型通用串行总线连接器与联合测试行动组连接器的数据输入引脚形成数据输入线网,c型通用串行总线连接器与联合测试行动组连接器的时钟引脚形成时钟线网,c型通用串行总线连接器与联合测试行动组连接器的测试模式选择引脚形成测试模式选择线网。因此,本发明不仅可引出c型通用串行总线连接器所需的信号,还可节省了传统c型通用串行总线转接板因需要核对每一插针的信号定义是否正确所耗费的时间,还可提高连接稳定性。

47.此外,当jtag连接器为带锁扣的连接器或防呆连接器时,可以保证jtag连接器与线缆进行连接时插接方向是固定的,预防插接错误,且自带锁扣的jtag连接器也保证了线缆连接的稳固性。

48.虽然本发明以前述的实施例公开如上,然而其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许更动与润饰,因此本发明的专利保护范围须视本说明书所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1