一种支持排除故障的电路切换方法及系统与流程

[0001]

本发明涉及系统设计领域,特别是涉及一种支持排除故障的电路切换方法及系统。

背景技术:

[0002]

lpc总线是因特尔在1998时作为工业标准架构体系的替代品引入,lpc总线常用于与pch物理相连,用于输出一些debug相关信息,lpc总线最大的优点是只需要7个信号,在拥挤的现代主板上是很容易布局的。

[0003]

espi接口主要用于替代lpc接口。无论是从内部架构设计还是外部pin定义二者均有差异,但是在实际应用过程中,espi未能完全实现替代lpc,兼容espi和lpc的设计还将存续一段时间。

[0004]

在服务器设计中,espi和lpc常用于传递pch的post信息,包含80debug code等,pch是发送的源头,bmc或者cpld等可以作为接收端,bmc可以在接收到数据信息后用来执行ipmi指令或者解析数据后呈现在web界面上,用于用户远程对服务器进行管理,cpld可以通过解析post信息,点led灯,方便用户及时观察post进度。

[0005]

在目前的服务器主板设计中,espi和lpc往往选择其中一种设计、不同时使用,如果要做兼容设计,需要添加逻辑切换线路,同时,目前缺乏支持灵活排除故障的切换电路设计,如果要支持排除故障,需要添加大量逻辑芯片,成本高、线路复杂,因此,目前的设计排除故障难度较高。

技术实现要素:

[0006]

本发明主要解决的技术问题是提供一种支持排除故障的电路切换方法及系统,能够使用较少数量的小型三态缓冲存储器实现增强同步串行接口技术和低引脚数数据总线的兼容设计,成本低、排除故障灵活度高,电路可靠稳定。

[0007]

为解决上述技术问题,本发明采用的一个技术方案是:提供一种支持排除故障的电路切换方法,包括以下步骤:

[0008]

s1,平台控制中心与基板管理控制中心进行信息交互,复杂可编程逻辑器件根据信息交互设定电路的运行模式,所述电路的运行模式包括同步串行接口技术模式、低引脚数数据总线模式和调试模式;

[0009]

s2,复杂可编程逻辑器件将电路的运行模式转换成电信号,复杂可编程逻辑器件将电信号传输给缓冲寄存器的第二管脚,缓冲寄存器的第二管脚根据电信号控制缓冲寄存器的开关;

[0010]

s3,当运行模式为同步串行接口技术模式时,平台控制中心将控制信号传输给缓冲寄存器,缓冲寄存器将控制信号传输给增强同步串行接口技术模块上的短接板,短接板根据同步串行接口技术模式选择第一管脚和第二管脚连接,短接板将控制信号传输给基板管理控制;

[0011]

当运行模式为低引脚数数据总线模式时,平台控制中心将控制信号传输给缓冲寄存器,缓冲寄存器将控制信号传输给基板管理控制器和调试连接器;

[0012]

当运行模式为调试模式时,平台控制中心将控制信号传输给缓冲寄存器,缓冲寄存器将控制信号传输给增强同步串行接口技术模块上的短接板,短接板根据同步串行接口技术模式选择第二管脚和第三管脚连接,短接板将控制信号传输给调试连接器。

[0013]

优选的,所述步骤s2中缓冲寄存器包括第一缓冲寄存器、第二缓冲寄存器和第三缓冲寄存器。

[0014]

优选的,所述复杂可编程逻辑器件将电信号传输给缓冲寄存器的第二管脚,电信号包括高电平电信号和低电平电信号。

[0015]

优选的,所述电信号为高电平电信号时,复杂可编程逻辑器件将高电平传输给第一缓冲寄存器和第三缓冲寄存器的第二管脚,第一缓冲寄存器和第三缓冲寄存器的第二管脚控制第一缓冲寄存器和第三缓冲寄存器打开,复杂可编程逻辑器件将高电平电信号传输给mos管,mos管将高电平电信号取反得到低电平电信号,mos管将低电平电信号传输给第二缓冲寄存器的第二管脚,第二缓冲寄存器的第二管脚控制第二缓冲寄存器关闭。

[0016]

优选的,所述电信号为低电平电信号时,复杂可编程逻辑器件将低电平传输给第一缓冲寄存器和第三缓冲寄存器的第二管脚,第一缓冲寄存器和第三缓冲寄存器的第二管脚控制第一缓冲寄存器和第三缓冲寄存器关闭,复杂可编程逻辑器件将低电平电信号传输给mos管,mos管将低电平电信号取反得到高电平电信号,mos管将高电平电信号传输给第二缓冲寄存器的第二管脚,第二缓冲寄存器的第二管脚控制第二缓冲寄存器打开。

[0017]

优选的,所述第一缓冲寄存器和第三缓冲寄存器打开,第一缓冲寄存器将控制信号传输给基板管理控制器,第三缓冲寄存器将控制信号传输给调试连接器。

[0018]

优选的,所述第二缓冲寄存器打开,第二寄存缓冲器将控制信号传输给增强同步串行接口技术模块上的短接板。

[0019]

优选的,所述第二寄存缓冲器将控制信号传输给增强同步串行接口技术模块上的短接板,当运行模式为同步串行接口技术模式时,电路里不存在故障,短接板控制第一管脚和第二管脚连接,短接板将控制信号传输给基板管理控制器;当运行模式为调试模式时,电路里存在故障,短接板控制第二管脚和第三管脚连接,短接板将控制信号传输给调试连接器。

[0020]

优选的,所述步骤s3中平台控制中心将控制信号传输给缓冲寄存器,控制信号为低引脚数数据总线模式与增强同步串行接口技术模式复用,平台控制中心将输出的控制信号传输到缓冲寄存器的输入端口。

[0021]

一种支持排除故障的电路切换系统,所述系统包括:平台控制中心、复杂可编程逻辑器件、mos管、第一缓冲寄存器、第二缓冲寄存器、第三缓冲寄存器、增强同步串行接口技术模块、基板管理控制器和调试连接器;

[0022]

所述平台控制中心分别与第一缓冲寄存器、第二缓冲寄存器和第三缓冲寄存器连接,平台控制中心与基板管理控制器连接;

[0023]

所述复杂可编程逻辑器件分别与第一缓冲寄存器和第三缓冲寄存器连接;

[0024]

所述复杂可编程逻辑器件通过mos管与第二缓冲寄存器连接;

[0025]

所述第一缓冲寄存器与基板管理控制器连接;

[0026]

所述第二缓冲寄存器与增强同步串行接口技术模块连接;

[0027]

所述第三缓冲寄存器与调试连接器连接;

[0028]

所述增强同步串行接口技术模块分别与基板管理控制器和调试连接器连接。

[0029]

本发明的有益效果是:本发明提出的方法及系统操作难度低、使用的器件数量少、电路简单、成本低,兼容了目前所需要的支持排除故障的电路切换的系统。

附图说明

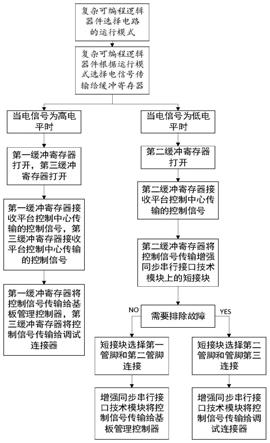

[0030]

图1是本发明一种支持排除故障的电路切换方法的流程图;

[0031]

图2是本发明一种支持排除故障的电路切换系统的架构图。

具体实施方式

[0032]

下面结合附图对本发明的较佳实施例进行详细阐述,以使本发明的优点和特征能更易于被本领域技术人员理解,从而对本发明的保护范围做出更为清楚明确的界定。

[0033]

参考图1,本发明实施例中的一种支持排除故障的电路切换方法,具体可以包括如下的步骤:

[0034]

复杂可编程逻辑器件根据平台控制中心与基板管理控制器之间的信息交互判断模式为增强同步串行接口技术、低引脚数数据总线或调试模式;

[0035]

当运行模式为增强同步串行接口技术模式时,复杂可编程逻辑器件将低电平电信号传输给mos管,mos管将接收到的低电平电信号进行取反得到高电平电信号,mos管将高电平电信号传输给第二缓冲寄存器,第二缓冲寄存器接收到高电平电信号后处于打开状态,复杂可编程逻辑器件将低电平电信号传输给第一缓冲寄存器和第三缓冲寄存器,第一缓冲寄存器和第三缓冲寄存器接收到低电平电信号后处于关闭状态;平台控制中心将控制信号传输给第二缓冲寄存器,第二缓冲寄存器将控制信号传输到增强同步串行接口技术模块中的短接板上,短接板控制增强同步串行接口技术模块第一管脚和第二管脚连接,短接板将控制信号传输给基板管理控制器;

[0036]

控制信号为低引脚数数据总线和增强同步串行接口技术模式复用,在使用增强同步串行接口技术模式时,平台控制中心将控制信号传输给缓冲寄存器的输入端;

[0037]

当运行模式为低引脚数数据总线模式时,复杂可编程逻辑器件模块将高电平信号传输给第一缓冲寄存器和第三缓冲寄存器,控制第一缓冲寄存器和第三缓冲寄存器处于打开状态,复杂可编程逻辑器件将高电平电信号传输给mos管,mos管将接收到的高电平电信号进行取反得到低电平电信号,mos管将低电平电信号传输给第二缓冲寄存器,第二缓冲寄存器接收到低电平电信号后处于关闭状态;平台控制中心将控制信号传输给第一缓冲寄存器和第三缓冲寄存器,第一缓冲寄存器将控制信号传输到基板管理控制器,第一缓冲寄存器将控制信号传输到调试连接器;

[0038]

当运行模式为调试模式时,复杂可编程逻辑器件将低电平电信号传输给mos管,mos管将接收到的低电平电信号进行取反得到高电平电信号,mos管将高电平电信号传输给第二缓冲寄存器,第二缓冲寄存器接收到高电平电信号后处于打开状态,复杂可编程逻辑器件将低电平电信号传输给第一缓冲寄存器和第三缓冲寄存器,第一缓冲寄存器和第三缓冲寄存器接收到低电平电信号后处于关闭状态;平台控制中心将控制信号传输给第二缓冲

寄存器,第二缓冲寄存器将控制信号传输到增强同步串行接口技术模块中的短接板上,短接板控制增强同步串行接口技术模块第二管脚和第三管脚连接,短接板将控制信号传输给调试连接器;

[0039]

第一缓冲寄存器和第三缓冲寄存器接收到低电平电信号后处于关闭状态,第三管脚输出高阻,高阻既不是低电平也不是高电平,高阻态无法继续传输到下一级电路,所以第一缓冲寄存器和第三缓冲寄存器接收到平台控制中心发出的控制信号后无法将控制信号传输出去;

[0040]

普通寄存器和缓冲寄存器相比,普通寄存器是寄存平时处理的数据用的,可以加快计算机的处理问题的速度;而缓冲寄存器是用于两个速度不匹配的单位之间的,作用是对高速度设备进行数据缓冲,防止低速度设备来不及处理而丢失数据;

[0041]

短接板在选择连接管脚的时候是根据电路中有无故障进行选择的,当电路中无故障时,短接板将第一管脚和第二管脚进行连接;当电路中有故障时,短接板将第二管脚和第三管脚进行连接。

[0042]

参考图2,本发明实施例中的一种支持排除故障的电路切换系统,所述系统包括:平台控制中心、复杂可编程逻辑器件、mos管、第一缓冲寄存器、第二缓冲寄存器、第三缓冲寄存器、增强同步串行接口技术模块、基板管理控制器和调试连接器;

[0043]

平台控制中心用于与基板管理控制器进行信息交互,选择电路的运行模式,平台控制中心发出控制信号来控制电路;

[0044]

复杂可编程逻辑器件将电路的运行模式转换成电信号,复杂可编程逻辑器件输出电信号控制缓冲寄存器的开关;

[0045]

mos管接收电信号,mos管将电信号进行取反得到取反后的电信号,mos管输出取反后的电信号控制第二缓冲寄存器开关;

[0046]

第一缓冲寄存器输出控制信号来控制基板管理控制器;

[0047]

第二缓冲寄存器将控制信号传输给增强同步串行接口技术模块上的短接板;

[0048]

第三缓冲寄存器输出控制信号来控制调试连接器;

[0049]

短接板根据电路是否存在故障来决定如何连接第一管脚、第二管脚和第三管脚,最终输出控制信号来控制基板管理控制器或调试连接器。

[0050]

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1