一种基于UVM的SPI验证平台的制作方法

一种基于uvm的spi验证平台

技术领域

1.本发明涉及集成电路设计中ip验证技术领域,特别涉及一种基于uvm的spi验证平台。

背景技术:

2.随着soc设计和fpga设计规模的不断扩大,soc芯片内部集成的ip模块越来越多,其功能也越来越庞大,芯片的开发周期也越来越长,验证平台的搭建也更加复杂。芯片验证在整个soc设计中占据至关重要的作用,在当今各大主流的集成电路设计公司中,验证在整个芯片研发周期中所占时间比例多达7成,传统的芯片验证方式已经不能满足当今大规模ic芯片设计的验证需求。传统的验证环境搭建基于verilog语言,编写定向测试激励,不能有效的覆盖所有的待测功能点,在不同的项目之间不能进行重用,代码调试也比较困难,验证效率比较低,增加了芯片研发的周期和成本。

3.为了解决芯片验证过程中的各种问题,提高芯片验证效率,accellra组织推出了uvm(universal verification methodology,通用验证方法学),uvm克服了传统验证方法的不足,提供了一个可复用的、分层次的验证平台框架,具有层次清晰、灵活易用、可扩展等特点。uvm基于systemverilog语言创建了通用的类库,构成了uvm验证环境的各个组件,验证人员可以在此基础上方便的进行验证平台的开发,编写受约束的随机化激励,来达到验证覆盖率的快速收敛。采用uvm和systemverilog组合的验证方法,极大地提高了验证的效率,符合当今大规模ic设计验证的需求和趋势,已经在ic设计行业得到了广泛地应用。

技术实现要素:

4.本发明的目的在于提供一种基于uvm的spi验证平台,以解决传统验证方法不能很好的覆盖全部待验证的功能点,覆盖率很难收敛、验证效率较低、可移植性较差,不能满足大规模设计验证需求的问题。

5.为解决上述技术问题,本发明提供了一种基于uvm的spi验证平台,使用uvm验证方法学和systemverilog语言搭建验证环境,所述spi验证平台包括:testbench顶层 top文件,实现整个uvm验证环境的初始化和连接操作;transaction事务数据包,产生和装载在序列发生器sequence中;序列管理sequencer负责序列发生器sequence的仲裁和调度,将序列发生器sequence中产生的item发送给驱动器driver,驱动器driver将transaction事务数据包转换后驱动到dut端口;监视器monitor,采集dut端口输出的数据,将其转换后发送给计分板scoreboard进行数据对比。

6.可选的,所述顶层testbench top文件中,例化dut端口的顶层spi_top模块,使用run_test函数来启动执行测试用例testcase,使用虚拟接口interface将spi的4个接口信号与验证环境相连接,并进行时钟复位等初始化操作;所述spi的4个接口信号包括mosi信

号、miso信号、sclk信号和ss信号。

7.可选的,transaction事务数据包中,定义了基本的transaction类,在spi_trans事务类中,定义了mosi、miso、sclk和ss信号,以及din_m、din_s、dout_m和dout_s信号,对这些变量采用field_automation机制进行注册,并对变量添加约束。

8.可选的,transaction事务数据包产生和装载在序列发生器sequence中,其继承自基类uvm_sequence_item,在spi_sequence序列类中声明对象且进行实例化,调用randomize函数进行随机化。

9.可选的,驱动器driver中,将transaction事务数据包转换成符合spi协议的信号,并将其通过vif虚拟接口驱动到dut端口。

10.可选的,所述监视器monitor采集dut端口输出的数据,在run_phase执行阶段中,监视器monitor采样虚接口vif上的mosi、miso、sclk、ss、din_m、din_s、dout_m和dout_s信号,将其转换成transaction事务级数据,发送给计分板scoreboard进行数据对比,监视器monitor进行与驱动器driver相反的数据转换操作。

11.可选的,所述计分板scoreboard中,声明并例化事务类spi_trans的实例,将监视器monitor采集到的事务级数据和期望值进行对比,并打印结果信息,验证dut端口的输出数据是否符合期望值的要求。

12.可选的,所述驱动器driver、监视器monitor和序列管理sequencer统一封装在代理器agent中,以便进行统一例化管理;使用seq_item_port和seq_item_export接口连接spi_driver组件和spi_sequencer组件。

13.可选的,代理器agent和计分板scoreboard在验证环境类env中进行例化,在connect_phase执行阶段中,使用ap_port接口连接代理器agent和计分板scoreboard,验证环境类env组件在基础测试类base_test中进行例化。

14.可选的,所述每个测试特定功能的测试用例testcase继承自基础测试类base_test,base_test类为基本的测试用例类,在base_test类的基础上,你能够扩展出各种测试case;使用run_test函数启动运行整个uvm验证环境。

15.可选的,在transaction事务类中,定义好spi正确格式的事务包,在驱动器driver中将transaction事务级数据转换成spi协议的信号,并将其驱动到dut端口上。

16.在本发明提供的基于uvm的spi验证平台中,给出搭建模块级可重用验证环境的方法,说明了验证环境内部各个组件的连接方式,给出了事务级spi数据的定义格式,在所搭建的验证环境中可方便的构造测试用例,加快了覆盖率的收敛。

17.本发明具有以下有益效果:(1)本发明采用最新的uvm验证方法学和systemverilog语言搭建验证环境;(2)所提出的uvm验证环境简洁可拓展,移植性较强,易于重用;(3)可以灵活构造各种测试场景,添加受约束随机激励,加速覆盖率收敛。

附图说明

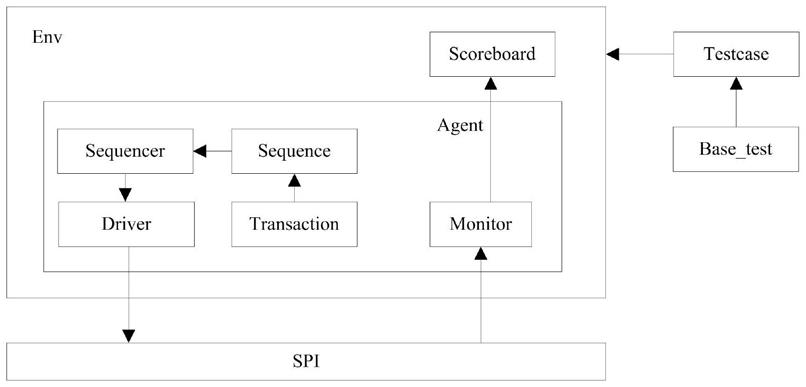

18.图1是本发明提供的基于uvm的spi验证平台结构示意图;图2是本发明提供的spi验证平台实施例芯片结构示意图。

具体实施方式

19.以下结合附图和具体实施例对本发明提出的一种基于uvm的spi验证平台作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

20.实施例一在本发明中提出一种基于uvm的spi验证平台,使用uvm搭建模块级验证环境。systemverilog是一门优秀的验证语言,但是仅仅使用systemverilog来进行验证显然不够,而uvm验证方法学提供了基础类库和基本验证结构,以便于快速高效的搭建验证平台。本发明提出的验证平台是基于uvm验证方法学和systemverilog语言来搭建的,对spi接口模块施加受约束的随机激励,可以在不同的环境中重用,提高了设计验证效率。

21.本发明使用uvm验证方法学搭建了一个spi模块的功能验证环境。spi为串行外设接口(serial peripheral interface)的缩写,具有高速、高效率和全双工的特点。spi使用了4根信号线,分别输出mosi(主设备输出/从设备输入信号)、miso(主设备输入/从设备输出信号)、sclk(同步时钟信号)和ss(从机选择信号)。本发明提供的基于uvm的spi验证平台结构如图1所示。uvm验证环境包含的基本组件有:测试用例testcase:为整个验证平台的测试激励。

22.基础测试base_test:启动测试,平台内所有的testcase都继承自base_test。

23.验证环境env:用于各个组件的例化和管理。

24.驱动器driver:用于对待测设计dut端口施加激励和数据转换。

25.监视器monitor:用于采集dut端口的数据并进行数据转换。

26.事务transaction:用于定义基本的item数据包。

27.序列发生器sequence:用于产生事务transaction。

28.序列管理sequencer:用于管理sequence,产生有效的sequence序列。

29.代理器agent:用于driver、monitor和sequencer的封装和实例化。

30.计分板scoreboard:用于对施加激励后dut端口的输出数据和期望值进行对比,并打印对比成功或失败信息。

31.testbench顶层 top文件实现整个uvm验证环境的初始化和连接操作;transaction事务数据包产生和装载在序列发生器sequence中;序列管理sequencer负责序列发生器sequence的仲裁和调度,将序列发生器sequence中产生的item发送给驱动器driver,驱动器driver将transaction事务数据包转换后驱动到dut端口;监视器monitor采集dut端口输出的数据,将其转换后发送给计分板scoreboard进行数据对比。

32.所述顶层testbench top文件中,例化dut端口的顶层spi_top模块,使用run_test函数来启动执行测试用例testcase,使用虚拟接口interface将spi的4个接口信号与验证环境相连接,并进行时钟复位等初始化操作;所述spi的4个接口信号包括mosi信号、miso信号、sclk信号和ss信号。transaction事务数据包中,定义了基本的transaction类,在spi_trans事务类中,定义了mosi、miso、sclk和ss信号,以及din_m、din_s、dout_m和dout_s信号,对这些变量采用field_automation机制进行注册,并对变量添加约束。transaction事务数据包产生和装载在序列发生器sequence中,其继承自基类uvm_sequence_item,在序列

类spi_sequence中声明对象且进行实例化,调用randomize函数进行随机化。驱动器driver中,将transaction事务数据包转换成符合spi协议的信号,并将其通过vif虚拟接口驱动到dut端口。所述监视器monitor采集dut端口输出的数据,在run_phase执行阶段中,监视器monitor采样虚接口vif上的mosi、miso、sclk、ss、din_m、din_s、dout_m和dout_s信号,将其转换成transaction事务级数据,发送给计分板scoreboard进行数据对比,监视器monitor进行与驱动器driver相反的数据转换操作。所述计分板scoreboard中,声明并例化事务类spi_trans的实例,将监视器monitor采集到的事务级数据和期望值进行对比,并打印结果信息,验证dut端口的输出数据是否符合期望值的要求。所述驱动器driver、监视器monitor和序列管理sequencer统一封装在代理器agent中,以便进行统一例化管理;使用seq_item_port和seq_item_export接口连接spi_driver组件和spi_sequencer组件。代理器agent和计分板scoreboard在验证环境类env中进行例化,在执行阶段connect_phase中,使用ap_port接口连接代理器agent和计分板scoreboard,验证环境类env组件在基础测试类base_test中进行例化。所述每个测试特定功能的测试用例testcase继承自基础测试类base_test,base_test类为基本的测试用例类,在base_test类的基础上,可以扩展出各种测试case;使用run_test函数启动运行整个uvm验证环境。在transaction事务类中,定义好spi正确格式的事务包,在驱动器driver中将transaction事务级数据转换成spi协议的信号,并将其驱动到dut端口上。

33.一款处理器soc芯片结构如图2所示,芯片包含中央处理器cpu、memory单元、spi接口、gmac接口、usb接口、i2c接口等部件,各个部件采用总线结构进行互联,该款soc芯片在网络通讯、无线设施和远程通信中具有广泛的应用,可以支持多种高速接口如gmac接口等,还支持多种低速接口如spi接口等。

34.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1