电子装置的制作方法

1.本发明涉及一种电子装置,特别是涉及一种可克服因电磁干扰而产生误动作的电子装置。

背景技术:

2.在现今的集成电路的设计中,常需要在内部设置许多不同的时钟域(clock domain),因此有许多跨频(cross clock)处理的机制,例如异步缓冲电路。当异步缓冲电路接收不同时钟源(clock source),但频率相同的时钟信号,可以采用一读一写的方式来进行运作。如果数据流是连续不断的(例如影像数据),此缓冲电路会持续地写入数据并读出数据,并维持使读写点(read/write point)间的一定的关系,并可持续执行数据的输出。

3.在当集成电路发生静电放电现象,或者因外力而产生电磁干扰时,不同时钟的时钟信号,可能因为对于干扰的耐受度不同,而产生不同的变异,例如频率飘移。这个时钟信号的变异现象,可能会造成缓冲电路读写动作间的关系产生破坏,可能使输出的数据产生错误。

技术实现要素:

4.本发明是针对一种电子装置,可避免因电磁干扰而产生误动作。

5.根据本发明的实施例,电子装置包括核心电路以及检测电路。核心电路接收不同的第一时钟信号以及第二时钟信号。核心电路根据第一时钟信号以及第二时钟信号以分别产生第一工作状态以及第二工作状态。检测电路耦接核心电路。检测电路检测第一工作状态以及第二工作状态间的关系来产生重置信号,其中重置信号用以重置第一工作状态以及第二工作状态间的关系为初始对应关系。

6.根据上述,本发明的电子装置可根据不同时钟信号分别执行不同的动作并具有不同的工作状态。本发明的电子装置并可在因电磁干扰而使工作状态间的关系产生变异时,提供重置信号以使多个工作状态间的关系恢复为正常的初始对应关系。如此一来,电子装置因电磁干扰所产生的误动作可以被避免。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

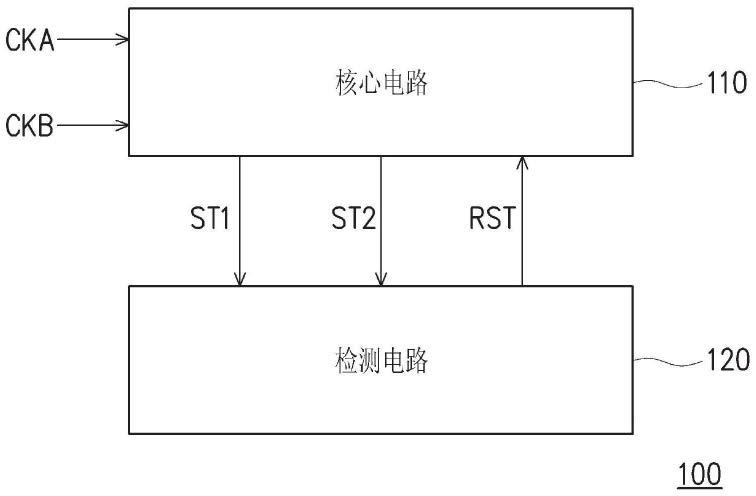

8.图1出示本发明一实施例的电子装置的示意图;

9.图2a示出本发明另一实施例的电子装置的示意图;

10.图2b示出的本发明图2a实施例的电子装置的动作示意图;

11.图3示出本发明实施例的检测电路的一实施方式的示意图;

12.图4a示出本发明另一实施例的电子装置的示意图;

13.图4b示出的本发明图4a实施例的电子装置的动作细节示意图;

14.图5示出本发明另一实施例的电子装置的示意图。

15.附图标号说明

16.100、200、400、500:电子装置;

17.110、510:核心电路;

18.120、220、300、430、520:检测电路;

19.210:数据缓冲器;

20.310:记录器;

21.320:处理器;

22.410:第一状态机电路;

23.420:第二状态机电路;

24.511~51n:子电路;

25.521、522:计数器;

26.523:判断器;

27.cka、ckb:时钟信号;

28.dataa、datab、datac、datad:数据;

29.rp:数据读出点;

30.rst:重置信号;

31.si1、si2:重置状态;

32.st1、st2:工作状态;

33.statea、stateb:工作状态;

34.wp:数据写入点。

具体实施方式

35.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

36.请参照图1,图1出示本发明一实施例的电子装置的示意图。电子装置100包括核心电路110以及检测电路120。核心电路110接收不相同的时钟信号cka以及时钟信号ckb。核心电路110并根据时钟信号cka以及时钟信号ckb以分别产生工作状态st1以及工作状态st2。检测电路120耦接核心电路110。核心电路110检测工作状态st1以及工作状态st2间的关系来产生重置信号rst。在本实施例中,核心电路110依据时钟信号cka以及时钟信号ckb分别执行两个不同的工作。且时钟信号cka以及时钟信号ckb所对应的两个不同的工作可分别具有工作状态st1以及工作状态st2。在正常状态下,核心电路110中的工作状态st1以及工作状态st2间具有一个预先设定的初始对应关系。在实际的应用上,随着电子装置100的操作,时钟信号cka以及时钟信号ckb的其中之任一可能因为例如发生静电放电现象而产生的电磁干扰的影响,而导致产生一定程度的频率飘移现象。这个频率飘移现象可能致使工作状态st1以及工作状态st2的至少其中之一产生错误,使工作状态st1以及工作状态st2间的关系有别于初始对应关系,并使核心电路110产生误动作的现象。

37.本实施例中,时钟信号cka以及时钟信号ckb可来自于不同的时钟源。

38.在本实施例中,当检测电路120判断出工作状态st1以及工作状态st2间的关系与

初始对应关系不相同时,可对应产生重置信号rst。重置信号rst可被传送至核心电路110,并用以使核心电路110重置工作状态st1以及工作状态st2间的所述关系为初始对应关系。如此一来,核心电路110可恢复正常动作,并消除产生误动作的可能。此外,当检测电路120判断出工作状态st1以及工作状态st2间的关系与初始对应关系相同时,则维持核心电路110的正常动作。

39.以下请参照图2a,图2a示出本发明另一实施例的电子装置的示意图。电子装置200包括为核心电路的数据缓冲器210以及检测电路220。数据缓冲器210分别根据时钟信号cka以及时钟信号ckb以获得数据写入点wp以及数据读出点rp,其中数据缓冲器210可以依据数据写入点wp来执行数据写入动作,数据缓冲器210可以依据数据读出点rp来执行数据读出动作。数据写入点wp可以对应所述数据缓冲器210的第一实体地址,而数据写入点rp则可以对应所述数据缓冲器210的第二实体地址。第一实体地址与第二实体地址可以相同或不相同。且数据缓冲器210的数据写入动作以及数据读出动作可以同时被执行。

40.在本实施例中,数据写入点wp以及数据读出点rp可以作为数据缓冲器210中对应时钟信号cka、ckb的二工作状态。

41.在正常状态下,数据写入点wp以及数据读出点rp分别对应的第一实体地址与第二实体地址是不可以相同的。原因在于,当数据写入点wp以及数据读出点rp对应于相同的实体地址时,可能使数据读出动作所读取的数据无法判定为旧有的数据或新写入的数据,甚至可能读取新旧交杂的数据。

42.在本实施例中,在正常状态下,数据写入点wp以及数据读出点rp间具有一初始对应关系。在运作过程中,电子装置200可使检测电路220可接收数据写入点wp以及数据读出点rp的相关信息,并检测数据写入点wp以及数据读出点rp间是否维持为上述的初始对应关系。在本实施例中,所谓的初始对应关系可以为数据写入点wp以及数据读出点rp分别对应的第一实体地址与第二实体地址间的差值。例如,为使读写动作可以稳定被执行,数据写入点wp对应的第一实体地址可被设定为与数据读出点rp所对应的第二实体地址间具有的地址差值为一个预设标准值。

43.以下请参照图2b示出的本发明图2a实施例的电子装置的动作示意图。在当电子装置200受到电磁干扰影响时,数据写入点wp以及数据读出点rp所对应的第一实体地址以及第二实体地址变更为相同。如此一来,检测电路220可检测出第一实体地址以及第二实体地址间的地址差值为0(不同于预设标准值),并获知数据写入点wp以及数据读出点rp间的关系不同于初始对应关系。同时,检测电路220可产生重置信号rst,并使数据写入点wp以及数据读出点rp被重置,并恢复为具有初始对应关系的状态。

44.如此一来,检测电路220可通过检测上述的地址差值是否产生变化。并在当地址差值产生变化时,产生重置信号rst以恢复第一实体地址以及第二实体地址间的地址差值,维持数据缓冲器210读写动作可以正常运行。

45.以下请参照图3,图3示出本发明实施例的检测电路的一实施方式的示意图。检测电路300可用以实施图2a、2b的检测电路220。检测电路300包括记录器310以及处理器320。记录器310可用以记录预设标准值。记录器310并可由核心电路接收数据写入点wp以及数据读出点rp。处理器320接收预设标准值、数据写入点wp以及数据读出点rp。处理器320获得分别对应数据写入点wp以及数据读出点rp的第一实体地址以及第二实体地址。并判断第一实

体地址以及第二实体地址的地址差值是否等于预设标准值以产生重置信号rst。

46.在硬件架构上,记录器310可以为任意形式的存储器。处理器320可以为具运算能力的处理器。或者,处理器320可以是透过硬件描述语言(hardware description language,hdl)或是其他任意本领域具通常知识者所熟知的数字电路的设计方式来进行设计,并透过现场可程序逻辑门阵列(field programmable gate array,fpga)、复杂可程序逻辑装置(complex programmable logic device,cpld)或是特殊应用集成电路(application-specific integrated circuit,asic)的方式来实现的硬件电路。

47.以下请参照图4a,图4a示出本发明另一实施例的电子装置的示意图。电子装置400包括第一状态机电路410、第二状态机电路420以及检测电路430。第一状态机电路410以及第二状态机电路420可以为核心电路,并分别接收时钟信号cka以及ckb以执行工作。其中,第一状态机电路410可根据时钟信号cka以操作在工作状态statea。同时,第二状态机电路420则可根据时钟信号ckb以操作在工作状态stateb。

48.检测电路430耦接至第一状态机电路410以及第二状态机电路420。检测电路430检测在相同时间点上的第一状态机电路410的工作状态statea以及第二状态机电路420的工作状态stateb间的关系是否符合一初始对应关系以产生重置信号rst。在当第一状态机电路410的工作状态statea以及第二状态机电路420的工作状态stateb间的关系非为初始对应关系时,检测电路430可产生重置信号rst以使第一状态机电路410以及第二状态机电路420执行重置动作,并使第一状态机电路410的工作状态statea以及第二状态机电路420的工作状态stateb间的关系恢复为初始对应关系。相对的,当第一状态机电路410的工作状态statea以及第二状态机电路420的工作状态stateb间的维持等于初始对应关系时,则维持第一状态机电路410、第二状态机电路420正常运作。

49.关于图4a实施例中,电子装置400的实施细节,可以参照图4b示出的本发明图4a实施例的电子装置的动作细节示意图。其中,第一状态机电路410以及第二状态机电路420依据重置信号rst以由重置状态si1、si2启动。第一状态机电路410依据时钟信号cka在状态a~状态d间依序循环动作。第二状态机电路420则依据时钟信号ckb在状态1~状态4间依序循环动作。

50.在动作细节上,在正常状态下,基于时钟信号cka、ckb,第一状态机电路410在状态a时,可对第二状态机电路420中,对应状态3中的缓存器进行数据dataa的数据写入动作,而第二状态机电路420则在状态1时,读取存储在对应状态1中的缓存器中的数据(数据读出动作);第一状态机电路410在状态b时,可对第二状态机电路420中,对应状态4中的缓存器进行数据datab的数据写入动作,而第二状态机电路420则在状态2时,读取存储在对应状态2中的缓存器中的数据(数据读出动作);第一状态机电路410在状态c时,可对第二状态机电路420中,对应状态1中的缓存器进行数据datac的数据写入动作,而第二状态机电路420则在状态3时,读取存储在对应状态3中的缓存器中的数据(数据读出动作);以及,第一状态机电路410在状态d时,可对第二状态机电路420中,对应状态2中的缓存器进行数据datad的数据写入动作,而第二状态机电路420则在状态4时,读取存储在对应状态4中的缓存器中的数据(数据读出动作)。

51.依据上述,在正常状态下,第一状态机电路410以及第二状态机电路420可维持在针对不同缓存器分别执行数据的读写动作,不致发生读写冲突。

52.当发生静电放电现象或其他外力所产生的电磁干扰现象时,时钟信号cka、ckb可能产生变异,而导致第一状态机电路410以及第二状态机电路420上述的工作状态的关系产生变异时,检测电路430可以通过检测工作状态statea、stateb间的关系是否维持初始对应关系来产生种置信号rst。并且,在当作状态statea、stateb间的关系与初始对应关系不相同时,检测电路430可致能重置信号rst,使第一状态机电路410以及第二状态机电路420被重置为重置状态si1、si2,并分别基于时钟信号cka、ckb以恢复正常动作。

53.值得一提的,图4b中,第一状态机电路410可以另包括状态a~状态d外的一个或多个状态。同样的,第二状态机电路420也可以另包括状态1~状态4外的一个或多个状态。图4b中第一状态机电路410以及第二状态机电路420所各具有的状态数量只是用以方便说明,不用以限缩本发明的范畴。

54.以下请参照图5,图5示出本发明另一实施例的电子装置的示意图。电子装置500包括核心电路510以及检测电路520。核心电路510则包括多个子电路511~51n。子电路511~51n中的每一均接收时钟信号cka以及ckb,并基于时钟信号cka以及ckb以进行工作。检测电路520耦接至核心电路510,通过接收时钟信号cka、ckb,经由判断时钟信号cka与时钟信号ckb间的频率关系是否等于初始对应关系来产生重置信号rst。

55.检测电路520可通过计数时钟信号cka、ckb,并根据分别获得的计数值来判断时钟信号cka与时钟信号ckb间的频率关系。检测电路520包括计数器521、522以及判断器523。计数器521、522分别接收时钟信号cka、ckb,并分别基于时钟信号cka、ckb执行计数动作,以分别产生第一计数值以及第二计数值。时钟信号cka、ckb的频率可以具有一比例关系,这个比例关系可以大于1、等于1或小于1。判断器523则可以为一数字电路的除法器,并透过使第一计数值以及第二计数值相除以判断时钟信号cka、ckb的目前频率关系。判断器523并通过比较目前频率关系与初始对应关系来产生重置信号rst。

56.在本实施例中,计数器521、522可应用任意形式的数字电路的计数器来实施,没有特别的限制。

57.根据上述,本发明实施例的电子装置检测核心电路依据不同时钟信号执行工作的不同工作状态,并通过检测这些工作状态间的关系有无符合预设的对应关系来执行重置动作。如此一来,当任一时钟信号因电磁干扰而产生变异而导致核心电路的工作状态间的关系不正常时,可以实时通过重置信号来进行修正,可免除电子装置因静电放电或其他种类的外部干扰而产生误动作的情况,维持电子装置正常运作。

58.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1