一种基于USB数据侦听系统及方法与流程

一种基于usb数据侦听系统及方法

技术领域

1.本发明涉及一种基于usb数据侦听系统及方法,属于电子与通信技术领域,特别提供一种将侦听到的图像数据用基于单片机、cpld或fpga底板做实时处理。

背景技术:

2.随着数码产品不断发展和普及,设备之间的数据交流也变得更加高频化和高速化,usb协议成为了各种设备间数据传输的主流协议之一。支持usb协议的设备不仅仅是在我们的日常生活中很常见,在科学研究中也非常的普遍,例如:各类外接检测装置、仪器仪表、望远镜、各类信号分析仪等都配有符合usb标准的接口。usb总线是常见的外部总线标准中的一种,用于usb总线模型中的主机和设备之间的数据交换和交流。usb接口因为高速稳定、即插即用、接口规范统一以及使用方便等优点,成为现代数据传输的主流趋势之一。usb接口标准有三种:usb 1.1,usb 2.0和usb 3.0。虽然现在usb3.0接口的设备很多,但目前市场中还是usb2.0设备占有份额高于3.0。

3.usb是一种便捷的,点对点的数据传输方式,但该协议不支持三个设备间的数据传输。若需要实现对usb 2.0总线上数据的实时侦听和采集功能,需要开发一个特定的设备或系统来完成这个任务。目前市场上出售的usb协议分析仪可以实现基于计算机的数据监听和分析功能。少数的文献中也是将侦听到的数据最终上传到pc端。而在计算机上通过软件实现的对usb接口的实时收发数据的监听和采集,没有很好的便携性和通用性,不同的计算机需要进行多次配置和调试;并且脱离了上位机软件的辅助,将不能够正常工作。目前并没有一种对usb 2.0总线上的两个方向的数据进行实时侦听、采集,并处理组合成一个usb事务发给底板电路,供底板电路去使用的系统。

技术实现要素:

4.本发明要解决的技术问题是:本发明提供一种基于usb数据侦听系统及方法,系统使用usb接口芯片侦听总线双向数据,使用fpga将数据组合成usb事务发送给底板电路。

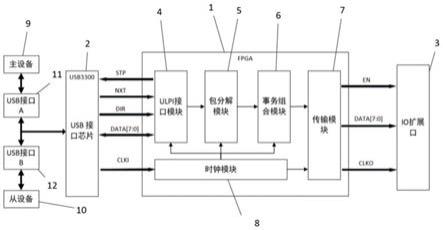

5.本发明技术方案是:一种基于usb数据侦听系统,包括fpga模块1、usb接口芯片模块2、io扩展口模块3、usb接口a11、usb接口b12;

6.所述usb接口芯片模块2通过usb接口a11、usb接口b12的usb总线无侵入式的连接主设备9和从设备10;usb接口芯片模块2还与fpga模块1连接,fpga模块1包括ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7、时钟模块8;时钟模块8均分别与usb接口芯片模块2、ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7连接;所述io扩展口模块3连接着fpga模块1的传输模块7;io扩展口模块3与底板电路对接。

7.作为本发明的进一步方案,所述ulpi接口模块4为ulpi phy接口模块,与usb接口芯片模块2建立协议层的联系,并把数据完整输出给包分解模块5;包分解模块5用于将usb数据包缓存到ram,并把包信息存入fifo中缓存;事务组合模块6用于usb事务处理,将若干个相关联的令牌包、数据包、握手包组合成一个usb事务并提供en信号;时钟模块8由usb接

口芯片模块2输入,控制着ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7的时钟;传输模块7用于将组合好的usb事务、提供给底板电路的同步时钟和en信号组合通过io扩展口模块3输出给底板电路,当en信号为高时,每一个同步时钟周期就会输出usb事务中的一个字节。

8.一种基于usb数据侦听方法,所述方法包括:

9.usb接口芯片模块2通过usb接口a11、usb接口b12的usb总线无侵入式截取主设备9和从设备10之间的信号并发送给fpga模块1处理,fpga模块1将处理完后的数据组合成一个usb事务从io扩展口模块3输出给底板电路;底板电路根据事务的头文件筛选所需要的数据去使用。

10.作为本发明的进一步方案,每个usb事务输出时,前4个字节为事务信息头,4字节的事务信息头格式为:

11.第1个字节:tid[7:0],表示该事务的类型;

[0012]

第2个字节:addr[6:0],表示该事务对应的设备地址;

[0013]

第3个字节:低4位为ep[3:0],表示该事务对应的端点号,高4位为len[3:0];

[0014]

第4个字节:len[11:4],len[11:0]表示该事务对应的数据长度;

[0015]

后面跟随0~1024字节的事务数据。

[0016]

本发明的工作原理是:

[0017]

基于usb数据侦听系统及方法使用底板5v供电。由于各个模块使用电压不同,所以使用2路ams1117低压降线性电源芯片分别产生3.3v,1.2v,供整体使用。

[0018]

所述usb接口a11用于连接进行usb通讯的主设备9、usb接口b12用于连接进行usb通讯的从设备10。两个usb接口的dm和dp直接与usb接口芯片模块2相连,并加1kω的的保护电阻与fpga相连;vbus加100kω电阻与fpga模块1相连,并加了100kω下拉电阻。

[0019]

所述usb接口芯片模块2所使用芯片是基于utmi+等级3封装而成接口为ulpi接口的usb3300;ulpi使用12个引脚将完整的otg主机/设备phy连接到系统级芯片上。一条8位双向数据总线,时钟为60mhz,允许fpga模块1访问这个内部寄存器阵列,并将usb数据包传输到物理层。剩下的3个管脚用于控制数据流和仲裁数据总线。8位数据总线的方向由ulpi接口模块4的dir输出控制。另一个输出nxt用于控制进出设备的数据流。最后,输入到ulpi接口模块4的stp终止传输,并用于启动和从挂起状态恢复。

[0020]

usb3300使用内部晶体驱动器和锁相环子系统提供无噪声、稳定的480mhz参考时钟,phy在发送和接收期间使用该时钟。usb3300需要一个稳定的、无噪声的24mhz晶体或时钟作为频率基准。usb3300可以使用晶体或外部时钟振荡器作为24mhz基准。晶体连接到usb3300引脚。一旦480mhz锁相环锁定到正确的频率,它将用60mhz时钟驱动clkout引脚。该芯片ulpi接口信号电平为3.3v。工作于高速480mbps速度模式。

[0021]

dir即direction,用于控制数据总线的传输方向;当usb接口芯片向fpga传输数据时候,驱动dir为高;没有数据传输时,驱动为低并监视fpga端的控制信号;同时,usb接口芯片会在不能接收数据时驱动dir为高。nxt即next,usb接口芯片会在传输数据时控制该信号;当fpga发送数据到usb接口芯片,usb接口芯片接收到数据时会马上拉高nxt;随后fpga会在下一个时钟周期时将下一字节放到数据总线上;相应的,当usb接口芯片正在发送数据给fpga,nxt代表此时有新字节数据要发送给fpga。stp即stop,当fpga置stp有效时在一个

时钟周期内,停止总线上当前的数据流;如果fpga正在传输数据到usb接口芯片,stp会保持为每个数据包的最后一位的数据。

[0022]

ulpi接口支持两种基本操作模式:同步模式和低功耗模式。同步模式,所有信号都相对于60mhz时钟发生变化。低功耗模式,时钟在暂停状态下关闭,数据总线的下两位包含线路状态[1:0]信号。ulpi增加了低功耗模式,这是一种中断输出,当otg比较器或id引脚改变状态时,允许链路接收异步中断。在同步模式下,数据在clkout的上升沿传输。数据总线的方向由dir的状态决定。当dir为高电平时,phy正在驱动数据[7:0]。当dir低电平时,链路正在驱动数据[7:0]。因为usb使用位填充编码,所以需要一些允许phy限制usb传输数据的方法。ulpi信号nxt用于请求链路层将下一个字节放置在数据总线上。当链路寻址phy时,单个ulpi协议块对ulpi 8位双向总线进行解码。链路必须使用dir输出来确定ulpi数据总线的方向。usb3300是“总线仲裁员”。ulpi协议块将数据/命令路由到发送器或ulpi寄存器阵列。

[0023]

usb接口芯片模块2将数据差分信号还原成为电平信号并需要解码nrzi码流,然后识别出填充位。将数据转化为位宽为8位的数据通过usb接口芯片模块2的d0~d7发送给fpga模块1。

[0024]

所述fpga模块1所使用的核心芯片为xilinx公司spartan6系列的xc6slx9

‑

2tqg144c芯片,搭配fpga外围电路连接至fpga芯片。如fpga的配置芯片spi

‑

flash,用于储存fpga配置bit流;供电电路主要给fpga芯片和spi

‑

flash提供需要的+5v、+3.3v和+1.2v电压;时钟使用usb接口芯片模块2输出的60mhz时钟作为模块的系统时钟。并配置了两个指示灯,led_1电源点亮红色指示灯,提醒接通后电源。led_2事务指示灯,每输出一次有效usb事务,蓝色指示灯亮一次。fpga模块1一端与io扩展口模块3相连,一端与usb接口芯片模块2相连。将本装置接入底板,将底板上电后,由底板提供5v电压和复位信号。fpga模块1中的ulpi接口模块4向usb接口芯片模块2的寄存器写入初始控制命令tx cmd。将usb接口a11连接进行usb通讯的主设备9、usb接口b12用于连接进行usb通讯的从设备10。usb接口芯片模块2开始侦听总线上的差分电路,并把差分信号还原成为电平信号传入fpga模块1。所述ulpi接口模块4为ulpi phy接口模块,与usb接口芯片模块2建立协议层的联系,并把数据完整输出给包分解模块5。包分解模块5将usb数据包缓存到ram,并把包信息存入fifo中缓存。事务组合模块6用于usb事务处理,将几个相关联的令牌包、数据包、握手包组合成一个usb事务并提供en信号;时钟模块8由usb接口芯片模块2输入,使用了基础时钟管理模块(dcm)和fpga内部的全局时钟分配网络紧密结合,可以用来分频倍频,消除时钟延迟差,并控制着ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7的时钟,并将时钟信号输出,可调节输出的时钟信号相位,使输出给底板的信号时序达到最佳。传输模块7用于将组合好的usb事务、提供给底板的同步时钟和en信号组合通过io扩展口模块3输出给底板,当en信号为高时,每一个同步时钟周期就会有一个字节的usb事务输出。

[0025]

本发明工作过程为:

[0026]

将本装置接入底板,将底板上电后,由底板提供5v电压和复位信号。使用2路ldo低压降线性电源芯片分别产生3.3v,1.2v电压供装置使用。复位后,fpga模块1中的ulpi接口模块4向usb接口芯片模块2的寄存器写入初始控制命令tx cmd。要写入寄存器,fpga模块1中的ulpi接口模块4需等到dir低,在第一个时钟周期,在数据总线上驱动txd cmd。在第三

个时钟周期,usb接口芯片模块2将驱动nxt高。在下一个上升时钟边缘,ulpi接口模块4将写入寄存器数据。在第五个时钟周期,usb接口芯片模块2将接受寄存器数据,并且ulpi接口模块4将驱动总线上的空闲,并驱动stp为高,以发送数据包结束的信号。最后,在第六个时钟周期,usb接口芯片模块2将把数据锁存到寄存器中,并驱动nxt为低。ulpi接口模块4将拉低stp。nxt用于控制ulpi接口模块4何时驱动总线上的寄存器数据。由于usb接口芯片模块2从ulpi接口模块4接收数据,所以整个事务中dir都是低电平。stp用于结束事务,在stp低电平后数据被寄存。写入操作完成后,ulpi接口模块4必须在数据总线上驱动ulpi空闲00h,否则usb接口芯片模块2可以将总线值解码为ulpi命令。

[0027]

将usb接口a11连接进行usb通讯的主设备9、usb接口b12连接进行usb通讯的从设备10。usb接口芯片模块2开始侦听总线上的差分电路,并把差分信号还原成为电平信号传入fpga。在传输期间,usb接口芯片模块2将使用nxt来控制进入usb接口芯片模块2的数据流速率。如果usb接口芯片模块2管道已满或位填充导致数据管道过度填充,则nxt无效(低电平),并且ulpi接口模块4将保留数据上的值,直到nxt有效(高电平)。当ulpi接口模块4中stp有效而nxt无效时,usb传输结束。由于usb接口芯片模块2期望在此状态下从ulpi接口模块4中获取另一个字节,因此ulpi接口模块4无法具有nxt无效的stp有效信号,

[0028]

一旦usb接口芯片模块2完成传输,dp/dm线路返回空闲状态,rxd cmd返回到链路,这样可以通过线路状态更新内部数据包计时。

[0029]

全速或低速情况下,一旦stp有效,每个fs/ls位转换将生成一个rxd cmd,因为位时间相对较慢。

[0030]

usb接口芯片模块2让dir有效以使usb接口芯片模块2从ulpi接口模块4控制数据总线。同一周期中dir和nxt有效中包含rxactive有效的附加信息。当nxt无效和dir有效时,rxd cmd数据被传输到fpga模块1。usb接收数据包的最后一个字节传输到usb接口芯片模块2后,线路状态将返回空闲状态。

[0031]

ulpi全速接收机根据utmi/ulpi规范运行。在全速情况下,nxt信号将仅在数据总线具有有效的接收数据字节时有效。当nxt低而dir高时,rxd命令在数据总线上驱动。

[0032]

在全速下,在dp/dm线路状态转换为空闲状态之前,usb接口芯片模块2不会在rxd cmd中发出rxactive无效的信号。这可防止fpga模块1违背两个全速位时间的最小改变时间。

[0033]

当ulpi接口模块4将包开始信号传到包分解模块5时,将8位并行数据存入8位宽的ram中,每存一个字节,计数一次可以得到包的长度。将前三组8位数据存入三个宽度为8寄存器当中,当一个完整的包传输结束后,将每一个包的信息组合成一个数据存入fifo中缓存。如果包的长度为三并且第一组数据为令牌包的pid(包识别字段),判断这个包为令牌包,则把前三组保存到寄存器里的8位数据存入宽度为64位fifo中的前24位缓存。其中前1~8位为这个包的pid,9~15位是设备的地址,16~19位是设备的端点数据,剩下的5位是crc检验位。如果包的长度大于3并且第一组数据为数据包的pid,则判断这个包为数据包。把第一组数据(pid)保存到64位fifo中的1~8位;把这个包的长度减三(除去一个字节的pid和两个字节的crc校验位,为这个包数据的长度)保存到64位fifo中的25~36位;把这个数据包在ram中的首地址加一(第一个字节是pid,从第二个字节起为这个包的数据,最后两个字节为这个包的crc)保存到64位fifo中的37~48位。如果包的长度为一并且第一组数据

为握手包的pid,判断为这个包为握手包,把第一组数据(pid)保存到64位fifo中的第一位。把这些数据保存fifo中缓存是为了便于接下来事务组合模块6处理。

[0034]

事务组合模块6中,当上一个事务的数据处理完并传输至底板后,如果fifo中有数据,则判断这个fifo中的64位数据的前8位,前8位为pid(包识别码)。如果是令牌包的pid,则将pid数据放进令牌包pid寄存器,并把此64位数据中地址放进地址寄存器,端点数据放进端点寄存器。如果是数据包的pid,则将pid数据放进数据包pid寄存器,并把此64位数据中数据长度放进数据长度寄存器,把数据在ram中的地址放进数据ram地址寄存器。如果是握手包的pid,则将pid数据放进握手包pid寄存器。根据三个pid寄存器,可以确定这次传输的是什么事务,并且将这次事务命名成相应的一个8位的事务标识符(tid)码,并将这次事务的地址、端点,长度组合成一个事务信息头。传输模块7用于将组合好的usb事务、提供给底板的同步时钟和en信号组合通过io扩展口模块3输出给底板,当en信号为高时,每一个同步时钟周期就会输出usb事务中的一个字节,前4个字节为事务信息头,4字节的事务信息头格式为:

[0035]

第1个字节:tid[7:0],表示该事务的类型;

[0036]

第2个字节:addr[6:0],表示该事务对应的设备地址;

[0037]

第3个字节:低4位为ep[3:0],表示该事务对应的端点号,高4位为len[3:0];

[0038]

第4个字节:len[11:4],len[11:0]表示该事务对应的数据长度;

[0039]

后面跟随着通过数据ram地址寄存器读出的相应长度的事务数据。并将地址、端点、pid等寄存器清零。

[0040]

数据输出到底板后,底板可根据头信息筛选所需要的信息,本设计专门用来筛选图像信息。

[0041]

本发明的有益效果是:

[0042]

1、当图像数据从usb通信的主从设备时,如果需要将数据用基于单片机、cpld或fpga底板做实时分析、处理、或者暂存时,可以将本系统连接底板系统使用。省去了再从pc端传入底板电路,提高了速度并减少了人力浪费。

[0043]

2、本发明可以不通过pc机,在接入usb传输线后,对usb总线上的数据进行无侵入式usb数据实时侦听并传给底板使用。

[0044]

3、本发明设备简单易用,成本较低,且面积较小便于携带,有很强的实用性。

[0045]

4、本发明也可以侦听其他数据,只需要在代码中稍作修改即可。

[0046]

5、本发明将几个包整合成一个事务,将没有用的数据舍弃,而且将所有事务分类,底板电路可以清楚的得到该事务的类型、该事务对应的设备地址、该事务对应的端点号、该事务对应的数据长度。底板电路可以根据这些条件来获取自己想要的数据,很方便的得到自己想要的结果。

附图说明

[0047]

图1是本发明的原理框图;

[0048]

图2是本发明的usb接口芯片到fpga芯片中data数据的双向导通的电路图;

[0049]

图3是本发明的包分解模块和事务组合模块数据传输的流程图;

[0050]

图4是本发明向底板传输的底板接收状态机。

[0051]

图1中各标号:1

‑

fpga模块,2

‑

usb接口芯片模块,3

‑

io扩展口模块,4

‑

ulpi接口模块,5

‑

包分解模块,6

‑

事务组合模块,7

‑

传输模块,8

‑

时钟模块,9

‑

主设备,10

‑

从设备,11

‑

usb接口a,12

‑

usb接口b。

具体实施方式

[0052]

下面结合附图和具体实施例,对本发明作进一步说明。

[0053]

实施例1:如图1

‑

4所示,一种基于usb数据侦听系统,包括fpga模块1、usb接口芯片模块2、io扩展口模块3、usb接口a11、usb接口b12;

[0054]

所述usb接口芯片模块2通过usb接口a11、usb接口b12的usb总线无侵入式的连接主设备9和从设备10;usb接口芯片模块2还与fpga模块1连接,fpga模块1包括ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7、时钟模块8;时钟模块8均分别与usb接口芯片模块2、ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7连接;所述io扩展口模块3连接着fpga模块1的传输模块7;io扩展口模块3与底板电路对接。

[0055]

作为本发明的进一步方案,所述ulpi接口模块4为ulpi phy接口模块,与usb接口芯片模块2建立协议层的联系,并把数据完整输出给包分解模块5;包分解模块5用于将usb数据包缓存到ram,并把包信息存入fifo中缓存;事务组合模块6用于usb事务处理,将若干个相关联的令牌包、数据包、握手包组合成一个usb事务并提供en信号;时钟模块8由usb接口芯片模块2输入,控制着ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7的时钟;传输模块7用于将组合好的usb事务、提供给底板电路的同步时钟和en信号组合通过io扩展口模块3输出给底板电路,当en信号为高时,每一个同步时钟周期就会输出usb事务中的一个字节。

[0056]

一种基于usb数据侦听方法,所述方法包括:

[0057]

usb接口芯片模块2通过usb接口a11、usb接口b12的usb总线无侵入式截取主设备9和从设备10之间的信号并发送给fpga模块1处理,fpga模块1将处理完后的数据组合成一个usb事务从io扩展口模块3输出给底板电路;底板电路根据事务的头文件筛选所需要的数据去使用。

[0058]

作为本发明的进一步方案,每个usb事务输出时,前4个字节为事务信息头,4字节的事务信息头格式为:

[0059]

第1个字节:tid[7:0],表示该事务的类型;

[0060]

第2个字节:addr[6:0],表示该事务对应的设备地址;

[0061]

第3个字节:低4位为ep[3:0],表示该事务对应的端点号,高4位为len[3:0];

[0062]

第4个字节:len[11:4],len[11:0]表示该事务对应的数据长度;

[0063]

后面跟随0~1024字节的事务数据。

[0064]

具体的,fpga模块1通过不同的i/o口连接usb接口芯片模块2和io扩展口模块3。fpga模块1与usb接口芯片模块2和io扩展口模块3之间的数据传输由位宽为8位的数据线d0~d7来实现。dir即direction,用于控制数据总线的传输方向;当usb接口芯片模块2向fpga模块1传输数据时候,驱动dir为高;没有数据传输时,驱动为低并监视fpga模块1端的控制信号;同时,usb接口芯片模块2会在不能接收数据时驱动dir为高。nxt即next,usb接口芯片模块2会在传输数据时控制该信号;当fpga模块1发送数据到usb接口芯片模块2,usb接口芯

片模块2接收到数据时会马上拉高nxt;随后fpga模块1会在下一个时钟周期时将下一字节放到数据总线上;相应的,当usb接口芯片模块2正在发送数据给fpga模块1,nxt代表此时有新字节数据要发送给fpga模块1。stp即stop,当fpga模块1置stp有效时在一个时钟周期内,停止总线上当前的数据流;如果fpga模块1正在传输数据到usb接口芯片模块2,stp会保持为每个数据包的最后一位的数据。

[0065]

如图1所示,usb接口a11为一个usb端口用于连接主设备9、usb接口b12为另一个usb端口用于连接从设备10,将两个接口的usb总线中间引线,从差分对上拉出两根线,使得信号可以直接流出,这样才能使其恢复原有的连接,在硬件层面上达到不干扰原传输线路的目的。

[0066]

如图1所示,usb接口芯片模块2通过usb接口a11、usb接口b12的usb总线无侵入式截取主设备9和从设备10之间的信号并发送给fpga模块1处理、fpga模块1将处理完后的数据组合成一个usb事务从io扩展口模块3发给底板电路。底板电路可根据事务的头文件筛选所需要的数据去使用。

[0067]

如图2所示的电路示意图解决了其中主要难度,实现了usb接口芯片模块2到fpga模块1中data数据的双向导通。其中mux是数据选择器,buft是三态输出缓冲器。当dir为高位时三态输出缓冲器为高阻态;数据选择器将data和data_in导通。实现了当usb接口芯片模块2向fpga模块1传输数据时,驱动dir为高,fpga模块1开始接收usb接口芯片模块2传进来的数据。当dir为低位时三态输出缓冲器将data_out数据传送到data。当没有数据传输时,usb接口芯片模块2驱动dir为低并监视fpga模块1的控制信号,这样fpga模块1就能将命令写入usb接口芯片模块2的寄存器中。

[0068]

如图1所示,fpga模块1包括:ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7、时钟模块8;ulpi接口模块4为ulpi phy接口模块,与usb接口芯片模块2建立协议层的联系,并把数据完整输出给包分解模块5;包分解模块5将usb数据包缓存到ram,并把包信息存入fifo中缓存;事务组合模块6用于usb事务处理,将几个相关联的令牌包、数据包、握手包组合成一个usb事务并提供en信号;时钟模块8由usb接口芯片模块2输入,控制着ulpi接口模块4、包分解模块5、事务组合模块6、传输模块7的时钟;传输模块7用于将组合好的usb事务、提供给底板的同步时钟和en信号组合通过io扩展口模块3输出给底板,当en信号为高时,每一个同步时钟周期就会输出usb事务中的一个字节。

[0069]

如图3所示,当ulpi接口模块4将包开始信号传到包分解模块5时,将8位并行数据存入8位宽的ram中,当一个完整的包传输结束后,将pid、端点,设备地址信息、数据包长度和在ram中的位置组成位宽为64的数据存入64位宽fifo中缓存。当没有数据向底板传输时,处理fifo中的数据。当一次事务传输完整时,将几个包的pid整合成一次事务的tid,把crc舍弃掉,然后将几个包的信息整合成一个事务包信息头。

[0070]

如图1所示,usb接口芯片模块2需要将usb3300芯片中写入usb协议,以使其能够把差分信号还原成为电平信号,并翻译成符合ulpi协议的信号,再通过ulpi协议将数据转化为位宽为8位的数据传入fpga处理。并将clk信号传进fpga内。

[0071]

如图1所示,io扩展口模块3连接着fpga模块1的传输模块7;io扩展口模块3将时钟信号输出给底板,使底板时钟同步;将事务有效信号en和usb事务输出给底板。

[0072]

如图4所示,是本发明向底板传输的底板接收状态机。每个usb事务输出时,当en有

效时,依次将本次事务包输出,前4个字节为事务信息头,4字节的事务信息头格式为:

[0073]

第1个字节:tid[7:0],表示该事务的类型;

[0074]

第2个字节:addr[6:0],表示该事务对应的设备地址;

[0075]

第3个字节:低4位为ep[3:0],表示该事务对应的端点号,高4位为len[3:0];

[0076]

第4个字节:len[11:4],len[11:0]表示该事务对应的数据长度;

[0077]

后面跟随0~1024字节的事务数据。

[0078]

所述底板在上电后,进入初始状态(idle),当使能信号en为1且前一个时钟en为0时,也就是有usb事务由本系统传向底板时,接收第一个八位数据的信息头并进入header_1状态。header_1状态en为1接收第二个八位数据的信息头并进入header_2状态。header_2状态en为1接收第三个八位数据的信息头并进入header_3状态。header_3状态en为1接收第四个八位数据的信息头并进入data状态。data状态只要en为1就有数据持续传下来,直到en为0,返回初始状态机(idle)。底板可根据此状态机加信息头约束去筛选所需数据。

[0079]

上面结合附图对本发明的具体实施例作了详细说明,但是本发明并不限于上述实施例,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下作出各种变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1