一种基于SPARC架构微控制器的事件记录模块的制作方法

一种基于sparc架构微控制器的事件记录模块

技术领域

[0001]

本发明属于工业过程控制技术领域,具体涉及一种事件记录模块。

背景技术:

[0002]

事件记录模块,用于记录输入开关量信号变位的准确时刻,以区分多个事件的先后顺序。事件类型可以是上升沿、下降沿或是上升沿与下降沿的组合。事件记录模块记录事件发生的时刻,并将事件类型、时间戳与其它信息组合成事件记录数据,其时间精度可达毫秒级。

[0003]

常规事件记录模块进行对时的做法是:接收1pps秒脉冲同步信号,以此同步信号为依据生成事件发生时刻的毫秒级时间戳,并组合成包含毫秒级时间戳的事件记录数据;此事件记录数据被发送至上位系统,上位系统程序对该数据补充年月日时分秒,形成包含完整时间戳的事件记录数据。这种做法的局限是:当1pps秒脉冲信号不稳定或丢失时,不能生成准确的毫秒级时间戳;且当事件记录模块与上位系统通信不稳定时,不能确保上位系统形成正确的包含完整时间戳的事件记录数据。

技术实现要素:

[0004]

为了解决现有技术中存在的上述问题,本发明提供一种基于sparc架构微控制器的事件记录模块。

[0005]

为达到上述目的,本发明采用如下技术方案:

[0006]

一种基于sparc架构微控制器的事件记录模块,包括:高速采集电路,高速存储器,微控制器电路,总线控制电路。其中,

[0007]

所述高速采集电路实时采集开关量信号,根据事件类型定义判断事件是否发生并记录事件发生时刻的时间戳,并将包含事件信息与时间戳的数据发送至高速存储器缓存。

[0008]

所述高速存储器对高速采集电路发送来的数据进行缓存,并提供给微控制器电路读取。

[0009]

所述微控制器电路对高速采集电路进行配置,并定期读取高速存储器中的事件信息与时间戳的数据,组合成事件记录数据并发送至总线控制电路。

[0010]

所述总线控制电路接收微控制器电路发送来的事件记录数据,并通过总线输出至上位系统。

[0011]

进一步地,所述高速采集电路包括fpga、flash 1。

[0012]

更进一步地,所述fpga采集开关量信号、对时信号。

[0013]

更进一步地,所述对时信号采用1pps秒脉冲同步信号和卫星导航系统授时信号中的一种或两种。

[0014]

进一步地,所述高速存储器采用sram存储。

[0015]

进一步地,所述微控制器电路包括基于sparc架构的微控制器、flash 2。

[0016]

进一步地,所述总线控制电路包括总线控制器、eeprom。

[0017]

更进一步地,所述总线控制器采用ethercat总线控制器。

[0018]

与现有技术相比,本发明具有以下有益效果:

[0019]

对时信号采用1pps秒脉冲同步信号和卫星导航系统授时信号中的一种或两种。事件记录模块采用卫星导航授时信号作为对时信号时,可对卫星导航系统授时信号进行解码获得1pps秒脉冲同步信号与包含年月日时分秒的时间信息,由此在事件记录模块内部形成包含完整时间戳的时间记录数据。这样可有效避免当1pps秒脉冲信号不稳定或丢失时不能生成准确的毫秒级时间戳、或当事件记录模块与上位系统通信不稳定时不能确保上位系统形成正确的包含完整时间戳的事件记录数据等情况的发生。模块支持多种对时方式,便于根据应用场景选择合适的对时方式,以满足实际的事件记录需求。

附图说明

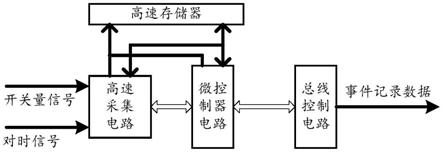

[0020]

图1为基于sparc架构微控制器的事件记录模块的组成框图。

[0021]

图2为基于sparc架构微控制器的事件记录模块的详细组成框图。

具体实施方式

[0022]

下面结合附图和实施例对本发明做进一步说明。

[0023]

一种基于sparc架构微控制器的事件记录模块,其组成框图如图1所示,包括:高速采集电路,高速存储器,微控制器电路,总线控制电路。

[0024]

事件记录模块记录输入开关量信号变位的准确时刻,以区分多个事件的先后顺序,其详细组成框图如图2所示,包括:

[0025]

高速采集电路实时采集开关量信号,根据事件类型定义判断事件是否发生并记录事件发生时刻的时间戳,并将包含事件信息与时间戳的数据通发送至高速存储器缓存。

[0026]

高速采集电路包括fpga、flash 1。

[0027]

flash 1用于存储fpga的固件与配置信息。fpga通过spi接口与flash 1通信。

[0028]

fpga用于采集开关量信号、对时信号。

[0029]

对时信号采用1pps秒脉冲同步信号和卫星导航系统授时信号中的一种或两种。当采用1pps秒脉冲同步信号作为对时信号时,fpga可生成毫秒级时间戳。当采用卫星导航授时信号作为对时信号时,fpga可对卫星导航系统授时信号进行解码获得1pps秒脉冲同步信号与包含年月日时分秒的时间信息,由此形成完整时间戳。包含事件信息与时间戳的数据通过地址总线与数据总线发送至高速存储器缓存。

[0030]

高速存储器采用sram存储,对高速采集电路发送来的数据进行缓存,并提供给微控制器电路读取。

[0031]

微控制器电路对高速采集电路进行配置,并定期读取高速存储器中包含事件信息与时间戳的数据,组合成事件记录数据并发送至总线控制电路。

[0032]

微控制器电路包括基于sparc架构的微控制器、flash 2。

[0033]

flash 2用于存储微控制器的固件与配置信息。微控制器通过spi接口与flash 2通信。

[0034]

微控制器通过地址总线与数据总线从高速存储器读取包含事件信息与时间戳的数据。微控制器通过spi接口将事件类型、对时方式等配置发送至fpga,进而明确从高速存

储器读取的数据中的时间戳是毫秒级时间戳或完整时间戳,并由此选择将组合成的事件记录数据通过总线控制电路发送至上位系统的方式与周期。微控制器通过spi接口将事件记录数据发送至总线控制电路。

[0035]

总线控制电路接收微控制器电路发送来的事件记录数据,并通过总线输出至上位系统。总线控制电路包括总线控制器、eeprom。总线控制器采用ethercat总线控制器。eeprom通过i2c接口与总线控制器相连,eeprom用于存储总线控制器的工作模式配置信息。总线控制器采用ebus通信接口将事件记录数据通过ethercat总线输出。

[0036]

本发明不限于上述实施方式,本领域技术人员所做出的对上述实施方式任何显而易见的改进或变更,都不会超出本发明的构思和所附权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1