支持清空写入未命中条目的受害者高速缓存的制作方法

支持清空写入未命中条目的受害者高速缓存

背景技术:

1.在多核相干系统中,多个处理器及系统组件共享相同存储器资源,例如芯片上及芯片外存储器。存储器高速缓存(例如高速缓存)可提供可操作地定位于处理器附近(例如,靠近处理器)(相较于主存储器)的一定量的高速存储器。一般来说,高速缓存可操作地越接近处理器,延时就越低,即,更少处理器时钟循环用于实现存储器请求。一般来说,最靠近处理器的高速缓存存储器包含通常直接在具有处理器的裸片上的1级(l1)高速缓存。许多处理器还包含更大的2级(l2)高速缓存。此l2高速缓存通常比l1高速缓存慢,但仍可在具有处理器核心的裸片上。l2高速缓存可为每处理器核心高速缓存或跨多个核心共享。通常,在裸片上作为单独组件或单芯片系统(soc)的另一部分的更大、更慢l3高速缓存也可用于处理器核心。

2.例如高速缓存的存储器系统可能易受数据损坏影响,例如由于来自宇宙射线、太阳粒子或恶意存储器存取的电子或磁性干扰。随着处理器越来越多地用于临界及/或其它不容错系统,例如自动驾驶车辆及自主系统,保护存储器系统免受数据损坏影响的技术越来越多地被应用到存储器系统。一种此技术是使用错误校正码(ecc)来检测及校正存储器损坏。在高速度的高速缓存存储器中实施ecc是具挑战性的,这是由于ecc可引入需要被考虑在内的额外时序开销。举例来说,高速度的高速缓存存储器系统可具有用于确定所存取存储器地址是否在高速缓存中及检索高速缓存存储器的内容的五级存储器管线。每一级可能花费一个时钟循环,在1ghz下,一个时钟循环是约1纳秒。错误校验高速缓存存储器的内容可基本上占用一个完整时钟循环。需要的是用于提高容错高速缓存的高速缓存性能的技术。

技术实现要素:

3.此描述涉及一种高速缓存系统。更特定来说(而非通过限制),此描述的方面涉及一种高速缓存系统,其包含第一子高速缓存及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述线类型位冲刷所存储写入未命中数据。

4.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中;及基于所述指示冲刷所述所存储数据。

5.此描述的另一方面涉及一种装置,其包含第一子高速缓存及与所述第一子高速缓存并行的第二子高速缓存;其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的

指示;及逐出控制器,其经配置以基于所述线类型位冲刷所存储写入未命中数据。

6.此描述的另一方面涉及一种高速缓存系统,其包含第一子高速缓存及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述高速缓存线已被完全写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

7.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中;及基于所述高速缓存线已被完全写入的指示逐出存储所述写入未命中的所述第二子高速缓存的高速缓存线。

8.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述高速缓存线被完全写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

9.此描述的另一方面涉及一种高速缓存系统,其包含:第一子高速缓存;及第二子高速缓存,其与所述第一高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且其中所述第二子高速缓存包含:色标位,其经配置以存储存储写入未命中数据的所述第二子高速缓存的对应高速缓存线与色标相关联的指示;及逐出控制器,其经配置以基于与所述高速缓存线相关联的所述色标逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

10.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收用于存储器地址的写入存储器命令;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述写入存储器命令相关联的数据存储于所述第二子高速缓存中;将与所述数据相关联的色标位存储于所述第二子高速缓存中;及基于所述色标位逐出所述所存储数据。

11.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且其中所述第二子高速缓存包含:色标位,其经配置以存储存储写入未命中数据的所述第二子高速缓存的对应高速缓存线与色标相关联的指示;及逐出控制器,其经配置以基于与所述高速缓存线相关联的所述色标逐出存储写入未命中数据的所述第二子高速缓存的所述高速缓存线。

12.此描述的另一方面涉及用于通过高速缓存系统高速缓存数据的技术,所述高速缓

存系统包含:第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:色标位,其经配置以存储所述第二子高速缓存的对应线与色标相关联的指示;及逐出控制器,其经配置以基于与所述线相关联的所述色标逐出存储写入存储器数据的所述第二子高速缓存的高速缓存线,且其中所述第二子高速缓存进一步经配置以:接收对存储器地址的第一写入存储器命令,所述写入存储器命令与第一色标相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

13.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收用于存储器地址的写入存储器命令,所述写入存储器命令与第一色标相关联;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

14.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且所述第二子高速缓存包含:色标位,其经配置以存储所述第二子高速缓存的对应线与色标相关联的指示;及逐出控制器,其经配置以基于与所述线相关联的所述色标逐出存储写入存储器数据的所述第二子高速缓存的高速缓存线,且其中所述第二子高速缓存进一步经配置以:接收对存储器地址的第一写入存储器命令,所述写入存储器命令与第一色标相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

15.此描述的另一方面涉及一种高速缓存系统,其包含:第一子高速缓存;第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:特权位,其经配置以存储所述第二子高速缓存的对应高速缓存线与特权等级相关联的指示,且其中所述第二子高速缓存进一步经配置以接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将与所述高速缓存线相关联

的所述特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

16.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

17.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:特权位,其经配置以存储所述第二子高速缓存的对应高速缓存线与特权等级相关联的指示,且其中所述第二子高速缓存进一步经配置以接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将与所述高速缓存线相关联的所述特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

18.此描述的另一方面涉及一种高速缓存系统,其包含第一子高速缓存及与所述第一子高速缓存并行耦合的第二子高速缓存;其中所述第二子高速缓存包含线类型位,其经配置以存储所述第二子高速缓存的对应线经配置以存储写入未命中数据的指示。

19.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,所述第二子高速缓存与所述第一子高速缓存并行耦合;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;及将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中。

20.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存;及与所述第一子高速缓存并行耦合的第二子高速缓存;其中所述第二子高速缓存包含线类型位,其经配置以存储所述第二子高速缓存的对应线经配置以存储写入未命中数据的指示。

21.此描述的另一方面涉及一种高速缓存系统,其包含:第一子高速缓存;第二子高速

缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;及高速缓存控制器,其经配置以:接收两个或更多个高速缓存命令;确定在所述接收到的两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到所述第一子高速缓存及所述第二子高速缓存。

22.此描述的另一方面涉及一种用于高速缓存数据的方法,其包含:接收两个或更多个高速缓存命令;确定在所述两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到第一子高速缓存及第二子高速缓存,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令。

23.此描述的另一方面涉及一种装置,其包含:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;及高速缓存控制器,其经配置以:接收两个或更多个高速缓存命令;确定在所述接收到的两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到所述第一子高速缓存及所述第二子高速缓存。

附图说明

24.为了详细描述各个实例,现将参考附图,其中:

25.图1是计算机系统的框图。

26.图2是说明用于处理读取请求的简化高速缓存存储器管线的框图。

27.图3是根据此描述的方面的具有存储队列的高速缓存存储器管线的框图。

28.图4是说明包含受害者高速缓存的高速缓存架构的框图。

29.图5是说明根据此描述的方面的包含并行受害者高速缓存的高速缓存架构的框图。

30.图6是说明根据此描述的方面的受害者高速缓存存储器管线的框图。

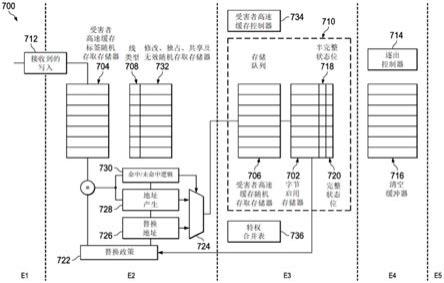

31.图7是说明根据此描述的方面的包含写入未命中缓冲器的受害者高速缓存管线的框图。

32.图8是根据此描述的方面的mesi ram的框图。

33.图9是根据此描述的方面的包含写入未命中缓冲器的高速缓存系统的架构框图。

34.图10到16是说明根据此描述的方面的用于高速缓存数据的技术的流程图。

具体实施方式

35.图1是计算机系统100的框图。计算机系统100包含数据高速缓存102,例如一级(l1)数据高速缓存。数据高速缓存102存储系统数据的子集以减少存取(例如读取及/或写入)经高速缓存子集的时间。通过有效地高速缓存最常使用的数据,数据高速缓存102可显著改进系统性能。

36.数据高速缓存102可经耦合到一或多个处理资源104(例如处理器核心)及扩展存

储器106。扩展存储器106包含存储器阶层的其它层级,例如l2高速缓存、存储装置等。数据高速缓存102可经并入到与处理资源104相同的裸片中(例如裸片上高速缓存)或可在单独裸片上。在任一情况中,高速缓存102通过用于在高速缓存102与每一处理资源104之间交换数据的一或多个接口耦合到所述处理资源。在此实例中,高速缓存102通过标量接口及矢量接口耦合到每一处理资源104。在具有多于一个接口的实例中,在一个接口忙的情况下,命令可使用另一接口服务。举例来说,当标量读取命令由高速缓存经由标量接口接收时,相关联数据可经由矢量接口基于接口利用率、数据大小及/或其它考虑提供到处理资源104。类似地,高速缓存102还可通过一或多个接口耦合到扩展存储器106。在存在多于一个接口的情况下,可基于利用率、数据大小及/或其它考虑来选择接口。

37.每一接口可具有任何合适宽度。接口的宽度可彼此不同,尽管在许多实例中,其是最窄接口的整数倍。在一个此实例中,标量接口是64位宽,矢量接口是512位宽,且扩展存储器接口是1024位宽。

38.接口可为双向或单向的。双向接口可包含两个独立单向接口,使得数据可同时地传输及接收。在一个此实例中,矢量接口包含两个512位单向总线,一个用于从处理资源104接收数据及操作,且一个用于将数据发送到处理资源104。

39.数据高速缓存102可包含用于处理经由这些接口接收到的操作的数个管线。图2是说明用于处理读取请求的简化高速缓存存储器管线200的框图。如在高速缓存存储器管线200中展示,处理器202将存储器请求发送到高速缓存存储器204。虽然高速缓存存储器204在l1高速缓存的上下文中描述,但本文中描述的概念可适用于任何类型的高速缓存存储器。在特定情况中,存储器请求可经由高速缓存或存储器控制器发送,在图中未展示。在此实例中,高速缓存存储器管线包含五个级e1、e2、e3、e4及e5。每一高速缓存存储器管线级可被分配特定数目个时钟循环来完成,且在一些实例中,每一级被分配一个时钟循环,使得经高速缓存数据可在五个时钟循环中的e5存储器管线级之后被传回到处理器202。在e1存储器管线级中,存储器请求由高速缓存存储器204接收。存储器请求包含要从其检索数据的存储器地址。在e2管级中,标签随机存取存储器(ram)206经读取以确定哪些存储器地址当前被存储于高速缓存存储器中。标签ram206存储记录存储器208中的哪些条目对应于扩展存储器中的哪些存储器地址的表。标签ram可为用于保持存储器地址表的存储器的组或部分。在特定情况中,高速缓存可为n路关联高速缓存,其中每一高速缓存组可保持n行存储器地址。随着n增加,搜查的地址数也增加,此继而增加确定所请求存储器地址是否在标签ram中所需的时间量。在e3存储器管线级中,比较接收到的存储器地址与从标签ram读取的所存储地址以确定是否存在高速缓存命中或未命中。高速缓存命中在与所请求存储器地址相关联的数据被存储于高速缓存中时发生,且高速缓存未命中在与所请求存储器地址相关联的数据未被存储于高速缓存中时发生。在e4存储器管线级中,与所请求存储器地址相关联的存储器208的部分被读取,且在e5存储器管线级处,所请求存储器地址被提供到处理器202。存储器208可为适于高速缓存存储器的任何类型的存储器,例如动态随机存取存储器(dram)、静态随机存取存储器(sram)、寄存器等。管线级说明存储器管线可被如何配置,且因而,省略特定子步骤及特征。在特定实施方案中,在其中执行例如存储器存取的特定活动的级可不同。

40.图3是说明根据此描述的方面的支持用错误校正码存储队列架构进行读取

‑

修改

‑

写入的高速缓存管线300的框图。管线300包含读取路径(具有读取路径锁存器302、标签ram 306、存储器308等)及写入路径(写入路径锁存器304、存储队列314等)。

41.关于读取路径,管线300包含标签ram 306及存储器308(例如dram或其它合适存储器)。高速缓存可具有任何程度的关联性,且在实例中,高速缓存是直接映射高速缓存,使得每一扩展存储器地址对应于高速缓存存储器308中的恰好一个条目。

42.在特定情况中,高速缓存管线300可包含支持ecc及存储器308可经耦合到错误检测及校正电路310。在ecc实例中,存储器308以块存储数据以及对应于所述块的一组ecc校验子位。当接收到读取操作时,存储器308可将所存储数据块及对应ecc校验子位提供到错误检测及校正电路310。错误检测及校正电路310可基于如从存储器208所读取的数据块重新产生ecc校验子位及比较经重新产生ecc校验子位与先前存储的ecc校验子位。任何差异可指示数据块已被不正确地读取,且ecc校验子位可用于校正数据块中的错误。检测及校正错误的能力使高速缓存非常适于任务关键应用。

43.仲裁单元312可经耦合到存储器308以在存储器308的冲突存取之间作出仲裁。当多个操作尝试在同一循环中存取存储器308时,仲裁单元312可根据优先级方案选择哪一(些)操作被准许存取存储器308。可使用许多不同优先级方案。作为优先级方案的实例,仲裁使读取操作优先于写入操作,这是因为即使在写入数据例如经由存储队列314的数据转发多路复用器318被写入到存储器308之前,在管线300中的写入数据也可用于被后续操作使用,如下文将更详细描述。因此,在允许写入数据在管线300中等待时具有最小性能影响。然而,随着管线300用尚未被写回的写入数据填充,写入操作的优先级可增加直到其比完成读取操作优先。

44.读取路径可与存储队列314并行延伸。因为读取操作可指代可能尚未完成的写入操作中的数据,所以管线300可包含写入转发功能性,其允许读取路径从存储队列314获得尚未被写回到存储器308的数据。在实例中,管线300包含:未决存储地址表316,其记录存储队列314的每一级处的操作的地址;数据转发多路复用器318,其从存储队列314的一个级选择数据用于转发;及存储队列命中多路复用器320,其在存储器308的输出(通过错误检测及校正电路310)与来自数据转发多路复用器318的所转发存储队列314数据之间作出选择。

45.现将描述通过管线300的读取操作的实例流程。在由级e1指示的第一循环中,高速缓存从标签ram 306检索与读取操作的地址相关联的记录以确定数据是否被存储于高速缓存的存储器308中。在直接映射实例中,高速缓存在从存储器308请求数据之前无需等待标签ram比较,且因此,读取操作的地址与经高速缓存地址的记录之间的标签ram比较无需延伸到第二(e2)或第三(e3)循环。

46.在第二循环中,在级e2中,如果仲裁单元312准许,那么高速缓存可从存储器308请求数据及ecc校验子位。在此循环中,高速缓存还可通过比较读取地址与未决存储地址表316来确定较新数据是否可用于存储队列314中。如果可用,那么数据转发多路复用器318被设置以从存储队列314转发适当数据。

47.数据及ecc校验子位可由存储器308在级e3中的第三循环中提供。然而,此数据可对应于或可不对应于由读取操作指定的存储器地址,这是因为高速缓存可分配到高速缓存的存储器308中的同一条目的多个扩展存储器地址。因此,在第三循环中,高速缓存在读取操作(例如高速缓存命中)中基于标签ram记录的比较确定来自存储器308的所提供数据及

ecc是否对应于存储器地址。在高速缓存命中的情况下,数据及ecc位由在级e4中的第四循环中校正数据中的任何错误的错误检测及校正电路310接收。

48.如上文描述,尚未被写入到存储器308中的较新数据可存在于存储队列314中,且可由数据转发多路复用器318从存储队列314转发。如果是这样的话,那么存储队列命中多路复用器320选择经转发数据而非来自存储器308的经校正数据。

49.来自存储器308的经校正数据或来自存储队列314的经转发数据在级e5中的第五循环中被提供到请求处理器。以此方式,实例高速缓存可在约5个循环中在高速缓存命中的情况下以完整ecc校验及校正将数据提供到处理器,

50.在数据及ecc位不存在于存储器308中(例如高速缓存未命中)的情况下,管线300可暂停直到可从扩展存储器检索数据,此时,数据可被写入到存储器308,且标签ram306可经更新,使得数据的后续读取命中于高速缓存中。

51.高速缓存也可支持从高速缓存读取数据的数个操作及在重写数据之前对数据作出改变。举例来说,高速缓存可支持读取

‑

修改

‑

写入(rmw)操作。rmw操作读取现存数据、修改所述数据的至少一部分及重写所述数据的那个部分。在ecc实施例中,rmw操作可在写入少于完整组宽度时执行。由于写入不是针对完整组宽度,所以仅对所写入数据的部分执行ecc操作将导致不正确ecc校验子。因此,因为组中将不被重写的数据的部分仍贡献于ecc校验子位,所以使用rwm的读取功能性。

52.rmw操作可分成写入操作及读取操作,且管线300可经结构化使得读取路径中的读取操作与存储队列314中的写入操作保持同步。读取操作及写入操作保持同步直到读取

‑

修改

‑

写入合并电路322用写入数据重写读取数据的至少一部分以产生经合并数据。经合并数据被提供到产生经合并数据的新ecc校验子位的ecc产生电路324,且接着,经合并数据及ecc校验子位可被提供到仲裁单元312用于存储于存储器308中。

53.现将描述通过管线300的rmw操作的实例流程。操作的读取部分基本上如上文在级e1到e4中描述那样继续进行,其中高速缓存比较读取操作的地址与标签ram 306的记录,且高速缓存从存储器308及/或存储队列314请求数据及ecc校验子位。因为rmw操作将修改数据,所以在跟踪存储器308中的条目的mesi(修改、独占、共享及无效)状态的实例中,未处于修改或独占状态的高速缓存命中可被视为高速缓存未命中。当数据在正确状态中被获得且任何错误被校正时,其在循环e4中(或稍后在高速缓存未命中的情况下)被提供到读取

‑

修改

‑

写入合并电路322。在此相同循环中,读取

‑

修改

‑

写入合并电路322可用写入数据重写经校正数据的至少一部分以产生经合并数据。ecc产生电路324在级e5中(或稍后在高速缓存未命中的情况下)产生经合并数据的新ecc校验子位。经合并数据及ecc校验子位被提供到仲裁单元312用于写入到高速缓存存储器308。

54.在一些实例中,接收涉及同一地址的顺序rmw操作。取代等待来自先前rmw操作的经合并数据被写入到存储器308,存储队列314可包含用于写入转发的地址比较器326,其可将经合并数据馈送回到存储队列314的前一级以由后一rmw操作使用。此可称为“捎带(pigging

‑

backing)”。数据可在ecc产生电路324之前或之后被馈送回。由于反馈有效地合并rmw操作,所以最终rmw操作具有一组完整数据及ecc校验子位。因此,在时间上居先的rmw操作可在其被写回到存储器308之前被取消。此可避免因写入过时数据而暂停其它操作。

55.在特定情况中,存储器308可表示整个数据高速缓存。仅通过实例,在此实施例中,

数据高速缓存(其可为l1数据高速缓存)与单个存储队列结构314相关联。作为实例,数据高速缓存可包含256个行,其中每一行具每行有1024位(1kb)。

56.在其它实例中,高速缓存可经划分成多个独立可寻址的组,且每一个别组可具有其自身相应存储队列结构314。例如,考虑以下实施例:其中上文提及的数据高速缓存具有256个行,其中每一行具有1024位的线宽度,但被划分成16个组,其中在给定组中每行具有64位。在此实施例中,将存在16个存储队列,每一个存储队列用于数据高速缓存的每一组。因此,读取及写入操作可经并行发送到组,且每一组响应于读取及/或写入操作仲裁其自身过程。通过允许多组高速缓存中的每一组单独操作,高速缓存的操作更有效,因为整个高速缓存线在接收到请求时不被锁定。确切来说,仅被分配到接收到此请求的组的高速缓存线的部分将被锁定。当然,上文描述的高速缓存大小仅是一个实例,且描述不限于任何特定高速缓存线宽度、组数或行等。

57.上文实例也有助于写入及/或读取矢量数据。例如,矢量数据可为512位宽。针对多组高速缓存,含有作为高速缓存中的命中的矢量数据的写入请求可被处理为8次并行写入到8个组(例如,8x64位=512位)。类似地,对此多组高速缓存的读取请求可被执行为从8个组的8次并行读取。

58.可存在于高速缓存系统的预期实施例中的另一特征是支持在途转发及失效。例如,假设在一个实例中高速缓存是两路组关联高速缓存。在两路组关联实施方案中,高速缓存内的每一高速缓存线可映射到更高级存储器(例如(举例来说)l2高速缓存或主系统存储器)中的两个不同地址。

59.考虑以下情况:其中在此实例中被称为“行1”的给定高速缓存线是两路组关联高速缓存中的高速缓存线且映射到存储器中的两个不同地址,其被称为“地址a”及“地址b”。现在,假设高速缓存接收到第一请求被接收,所述第一请求是部分写入(例如,到不足整个高速缓存线的写入)且在读取请求之后,像这样:

60.write(address a):data 1//将data1写入到对应于地址a的高速缓存线

61.read(address b)//读取对应于//地址b的高速缓存线中所含的数据

62.在此实例中,让我们假设写入请求是命中,这意味着对应于地址a的高速缓存线(在此实例中我们将假设是行1)在高速缓存中。作为响应,高速缓存系统将开始将数据1写入到行1的过程。

63.随后,让我们假设读取请求是未命中。换句话说,虽然行1可被映射到此两路组关联高速缓存中的地址a或地址b,但在此例子中,其目前被映射到地址a。未命中因此而发生,因为地址b未被发现于标签ram 306中。响应于未命中,高速缓存系统将通过将从例如l2高速缓存的更高级存储器检索数据来服务于未命中,且当在此实例中被称为“数据2”的数据被传回时,当前在行1中的数据将被逐出以便存储数据2。此可在先前写入已完成之前发生。在此情况中,无需完成写入操作,因为行1无论如何都将被逐出。因此,写入可在其完成之前(被称为“在途”)失效。

64.例如原子比较及交换的原子操作是包含读取的存储器操作的进一步实例。原子比较及交换操作可提供地址、键值及将要写入的一组新数据。比较所述地址处的当前数据与键,且如果它们匹配,那么地址处的当前数据被新数据重写。因此,在一些实例中,管线300包含原子比较及交换电路328以在当前数据匹配键值的情况下,执行比较并转发新数据用

于写入。原子比较及交换电路328可与读取

‑

修改

‑

写入合并电路322并行耦合,且功能多路复用器330可用于确定哪一输出被提供到ecc产生电路324。

65.现将描述通过管线300的原子操作及交换操作的实例流程。操作的读取部分基本上如上文在级e1到e4中描述那样继续进行,其中高速缓存比较读取操作的地址与标签ram 306的记录,且高速缓存从存储器308及/或存储队列314请求数据及ecc校验子位。因为原子比较及交换操作可修改数据,所以在跟踪存储器308中的条目的mesi状态的实例中,未处于修改或独占状态的高速缓存命中可被视为高速缓存未命中。当数据在正确状态中被获得时,其在级e4中(或稍后在高速缓存未命中的情况下)被提供到原子比较及交换电路328。在这些循环期间,新数据及键可经存储于写入路径锁存器304中。在级e4期间,原子比较及交换电路328可接收经校正读取数据、键及新数据。如果经校正读取数据匹配键,那么原子比较及交换电路328将新数据提供到ecc产生电路324。如果读取数据匹配键,那么原子比较及交换电路328还可将新数据的状态改变成修改。ecc产生电路324在级e5中(或稍后在高速缓存未命中的情况下)产生新数据的新ecc校验子位。新数据及ecc校验子位被提供到仲裁单元312用于写入到高速缓存存储器308。

66.当接收到顺序原子比较及交换操作时,类似于在rmw操作的上下文中描述那样,管线300还可使用地址比较器326执行写入转发。

67.读取现存数据的存储器操作的进一步实例包含直方图操作。直方图操作可指定值以添加到现存数据或从现存数据减去。为了支持直方图操作,管线300可包含与读取

‑

修改

‑

写入合并电路322及/或原子比较及交换电路328并行耦合的算术单元332。算术单元332可支持任何大小的操作数,且在一个此实例中,算术单元332支持来自64位组的16位值的加法及减法。多路复用器330可用于在算术单元332、读取

‑

修改

‑

写入合并电路322与原子比较及交换电路328之间作出选择。

68.现将描述通过管线300的直方图操作的实例流程。操作的读取部分基本上如上文在级e1到e4中描述那样继续进行,其中高速缓存比较读取操作的地址与标签ram 306的记录,且高速缓存从存储器308及/或存储队列314请求数据及ecc校验子位。因为直方图操作将修改数据,所以在跟踪存储器308中的条目的mesi状态的实例中,未处于修改或独占状态的高速缓存命中可被视为高速缓存未命中。当数据在正确状态中被获得时,其在级e4中(或稍后在高速缓存未命中的情况下)被提供到算术单元332。在这些循环期间,将添加到经校正数据的值可经存储于写入路径锁存器304中。在级e4期间,算术单元332可接收经校正读取数据及将要添加到读取数据或将要从读取数据减去的值。算术单元332执行指定加法或减法且将新数据提供到ecc产生电路324。ecc产生电路324在级e5中(或稍后在高速缓存未命中的情况下)产生新数据的新ecc校验子位。新数据及ecc校验子位被提供到仲裁单元312用于写入到高速缓存存储器308。

69.当接收到顺序直方图操作时,类似于在rmw操作的上下文中描述那样,管线300还可使用地址比较器326来执行写入转发。

70.虽然图3说明具有存储队列314、锁存器302及304、错误检测及校正电路310等的单个例子的单个管线300。然而,如上文描述,存储器308可经布置以支持管线300的多于一个独立副本。因此,管线300可重现多次。在一个此实例中,存储器308条目是基于扩展存储器接口的宽度的1024位块,且存储器308经布置成16个并行组,其中在16个组中的每一者中,

每一1024位块包含64位。在此特定实例中,16个组中的每一者具有其自身独立管线300。从处理器进行的读取或写入操作被划分成数个组级操作,且每一者被提供到其相应管线300,使得其可被同时处理。举例来说,512位矢量读取操作可被划分成被提供到八个独立管线300以并行处理的八个64位读取操作。同时,另一操作可经由另一处理器的标量接口或矢量接口接收且被划分成被提供到剩余管线300的操作。因此,数据高速缓存可同时服务于多个独立操作,其中每一操作被分配管线300的子集。

71.在特定情况中,高速缓存管线300可经耦合到受害者高速缓存。受害者高速缓存可有助于改进高速缓存未命中率,例如由于冲突未命中的高速缓存未命中率。在特定情况中,受害者高速缓存对高速缓存性能可能有影响,类似于增加n路关联数(例如,高速缓存关联性程序)。此益处在其中受害者高速缓存被添加到直接映射高速缓存的情况中更加明显,这是由于直接映射高速缓存通常具有最高的冲突未命中率。受害者高速缓存的添加可有助于改进整体高速缓存命中率。

72.图4是说明包含受害者高速缓存的高速缓存架构400的框图。在此,高速缓存架构400包含耦合到受害者高速缓存402的主高速缓存404,其中受害者高速缓存402驻留在主高速缓存404之后。当一行数据被逐出主高速缓存404时,取代将一行数据移动到下一级高速缓存(例如l2),一行数据被移动到受害者高速缓存402且被保持在那里直到有理由将其逐出,例如由于容量或其它理由。在此高速缓存架构400中,在来自主高速缓存404的高速缓存未命中的情况中,受害者高速缓存402可服务于未命中且将所述行传回到处理器414,从而减小读取未命中所经历的整体延时。

73.作为实例,假设处理器414尝试存取主高速缓存404及受害者高速缓存402中的地址a,从而导致高速缓存未命中。接着,主高速缓存404可从主高速缓存404逐出地址b,且在受害者高速缓存402中创建受害者高速缓存(地址b)线。接着,地址b的读取未命中前往406到将要被服务的更高级存储器412,例如l2高速缓存、另一高速缓存及/或其它存储器。一旦地址a被存取,地址a的内容就可被传回410且被存储于主高速缓存404中。

74.如果发出对地址b的后续存取尝试,那么校验主高速缓存404以查看地址b是否被高速缓存,从而导致高速缓存未命中。接着,校验408受害者高速缓存402,其在地址b在从主高速缓存404被逐出之后被存储于受害者高速缓存402中时传回命中。接着,地址b可被重新存储410到主高速缓存404且作为结果被传回到处理器414。此系统中的读取延时,虽然比必须从更高级存储器414(例如l2高速缓存、主存储器等)提取地址更快,但仍大于在主高速缓存404中存在高速缓存命中时的延时。

75.为了帮助解决在将受害者高速缓存放置于主高速缓存之后的高速缓存架构中经历的延时,在特定情况中,受害者高速缓存可经放置成与主高速缓存并行。图5是说明根据此描述的方面的包含并行受害者高速缓存的高速缓存架构500的框图。高速缓存架构500可被视为具有多个并行子高速缓存。主高速缓存504及受害者高速缓存502中的每一者具有其自身独立关联性,且整体高速缓存系统500可具有混合路高速缓存系统的外观。在特定情况中,主高速缓存504或受害者高速缓存502可为n路关联,而其它高速缓存可为完全关联。在此实例中,主高速缓存504可为直接映射(1路关联)高速缓存,且受害者高速缓存502可为完全关联。

76.在此实例中,如果处理器514发出读取到地址a,其在主高速缓存504中未命中,那

706中的条目相关联的线类型708的额外位。线类型708指示受害者高速缓存ram 706的特定线是高速缓存线还是写入未命中缓冲线。在特定情况中,线类型708可被添加到另一存储器,例如受害者高速缓存标签ram 704而非mesi ram 718。

81.而且,例如如结合图6所描述的受害者高速缓存系统可通过在读取及写入未命中状态机中添加控制逻辑来解决受害者高速缓存内部的写入未命中条目的分配以及支持在如同对与受害者高速缓存内部的写入未命中条目相同的行的读取的情况中处理各种地址危害的逻辑及支持解析受害者高速缓存的数据路径中的相同地址负载/存储的逻辑来配置为写入未命中缓冲器。存储队列710结构还可被提供以实现对rmw的支持及对写入未命中的ecc支持。在特定情况中,存储队列710可用于实现对rmw的支持及对写入未命中操作以及高速缓存操作的ecc支持。

82.作为在高速缓存中执行写入未命中缓冲器操作的实例,当在框712处接收到写入时,对照存储于受害者高速缓存标签ram 704中的每一位置中的存储器地址校验写入的地址。写入未命中在写入的地址未发现于受害者高速缓存标签ram 704中时发生。当操作为写入未命中高速缓存时,对将写入未命中存储于受害者高速缓存中的位置进行确定。在特定情况中,此确定可基于受害者高速缓存标签ram 704中的条目进行。如果在受害者高速缓存标签ram 704中存在空位置时,那么写入未命中的地址被存储于受害者高速缓存标签ram 704中的空位置中。如果不存在空位置,那么线可基于逐出方案被逐出用于分配写入未命中缓冲器空间。在其它情况中,线先前可能已被用作写入未命中缓冲器或高速缓存线。对应于写入未命中的受害者高速缓存标签ram 704中的位置的线类型708可经更新以指示位置被用作写入未命中缓冲器。举例来说,线类型708中的0可指示对应线是高速缓存条目,而线类型708中的1可指示对应线是写入未命中缓冲条目。在特定情况中,线类型708可经存储于例如mesi ram 732的另一存储器位置中或例如一组寄存器的专用存储器空间中。写入未命中的数据经存储于对应于所使用的受害者高速缓存标签ram 704位置的受害者高速缓存ram 706的线中。字节启用逻辑可经存储于字节启用存储器702的对应槽中。在特定情况中,字节启用存储器702可包含指示字节启用存储器702的哪些位置是有效的位。线类型位有助于实现将写入未命中条目存储于受害者高速缓存ram 706的线中,而无需将受害者高速缓存ram 706的部分专用为写入缓冲器。

83.根据此描述的方面,例如逐出控制器714中的受害者高速缓存逐出逻辑可经更新以处理存储于受害者高速缓存中的写入未命中条目以优先逐出写入未命中条目以支持存储高速缓存条目。而且,用于受害者高速缓存控制器734的读取及写入状态机的控制逻辑可经配置以确定传入读取请求可命中经配置以存储写入未命中的受害者高速缓存的高速缓存线。在此类情况中,受害者高速缓存控制器734可经配置以如同读读取未命中那样来处理此读取命中且将所存储写入未命中命令逐出到更高级存储器且接着将读取未命中发送出到更高级存储器。而且,高速缓存系统通常经配置以在未命中时暂停,而写入未命中缓冲器通常在其缓冲写入未命中时不暂停处理器。为了有助于解决此差异,受害者高速缓存控制器734可经配置以通过推测性地读取传入写入数据,使得如果数据是写入未命中那么数据可被直接存储到受害者高速缓存中而无需暂停来将写入未命中条目分配到受害者高速缓存而无需暂停cpu。

84.在特定情况中,通过将写入未命中放置于高速缓存系统中,写入未命中可保持被

高速缓存直到需要将其逐出到更高级存储器为止。在特定情况中,存储于受害者高速缓存中的写入未命中可保持在高速缓存系统中直到经定义条件被满足、栅栏操作被请求或存在需要逐出特定写入未命中条目的地址/硬件冲突为止。

85.维持写入未命中缓冲器直到明确栅栏操作被请求可能是有问题的,例如,如果栅栏操作在操作结束时未被抬高,且存储于受害者高速缓存中的任何写入未命中可被卡在受害者高速缓存内部。而且,栅栏操作可能存在延时问题,这是由于仅响应于栅栏操作冲刷出(例如,逐出所有)写入未命中缓冲器存储可导致延迟,因为高速缓存需要将所存储写入未命中清空到适当存储器且接着等待传回确认。在特定情况中,可提供存储于受害者高速缓存中的写入未命中条目的自动冲刷或清空。自动冲刷可经实施以有助于从受害者高速缓存清空写入未命中条目同时减小在清空过程中可能引发的潜在延时。在特定情况中,逐出控制器714可监测处理器接口上的活动。如果逐出控制器714检测到处理器接口上的空闲活动,那么逐出控制器714可继续进行以起始从受害者高速缓存清空写入未命中条目。举例来说,如果逐出控制器714检测到处理器在n个时钟循环内尚未发出任何命令,那么逐出控制器714可在内部起始自动冲刷过程来起始清空高速缓存于受害者高速缓存内部的存储。在特定情况中,n可为预定的。在其它情况中,n可为可配置的。在特定情况中,自动冲刷过程可遍历(例如按顺序检查)vtag ram,从而查找写入未命中条目及冲刷对应于写入未命中条目的条目。在其它情况中,自动冲刷过程可包含基于fifo、最近最少使用(lru)、随机或其它基础冲刷条目的逻辑。

86.在自动冲刷写入未命中条目时,逐出控制器714可将逐出触发请求发送到所选择的写入缓冲高速缓存线的受害者高速缓存控制器734。受害者高速缓存控制器734校验存储队列以查看在对应于将要被冲刷的写入缓冲高速缓存线的存储队列中是否存在任何条目。如果在存储队列中存在对应条目,那么受害者高速缓存控制器734可等待存储队列完成。一旦存储队列为空,那么受害者高速缓存控制器734可逐出所选择的高速缓存线。受害者高速缓存控制器734设置将要发送到更高级高速缓存或其它存储器的存储未命中数据包的创建。这些存储未命中数据包可包含存储于受害者高速缓存标签ram 704中的对应存储器地址、字节启用存储器702中的字节启用逻辑及受害者高速缓存ram 706中的数据。接着,受害者高速缓存可将存储未命中数据包发送例如到更高级高速缓存或其它存储器的高速缓存控制器。当冲刷写入未命中条目时,写入未命中数据包可被发送出到其它存储器,且可使受害者高速缓存ram 706、受害者高速缓存标签ram 704及字节启用存储器702中的对应条目失效。写入未命中数据包可被暂时放置于清空缓冲器716中,直到写入未命中数据包被其它存储器接受(例如确认)。一旦写入未命中缓冲高速缓存线失效,逐出控制器714就可选择要逐出的下一写入未命中缓冲高速缓存线且继续进行以逐出下一写入未命中缓冲高速缓存线。如果随后在处理器接口上检测到活动,那么可取消此自动冲刷操作。这样,受害者高速缓存能够利用空闲周期且通过尝试清空写入未命中缓冲条目来当在接口上存在活动时,避免影响处理器性能。

87.在特定情况中,存储于受害者高速缓存中的写入未命中可基于存储特定写入未命中的写入未命中线的状态(而非基于高速缓存线被分配的顺序的fifo、lru、随机或其它方案)被逐出。在高速缓存经配置以合并高速缓存中的数据的情况下,从处理器到存储器线的高速缓存写入并不暗含处理器需要从存储器线的其它部分进行读取。此外,与其中处理器

已写入存储器线的仅小部分的情况相比,在处理器已写出存储器线的大部分(例如一半存储器线或整个存储器线)的情况下,处理器不太可能需要再次存取(例如,将额外数据合并到)存储器线的那个部分。由于处理器不太可能需要在写出一半或完整写入未命中高速缓存线之后存取给定写入未命中高速缓存线,所以此写入未命中高速缓存线可以对性能的较少潜在影响被逐出。因此,一旦写入未命中高速缓存线被完全写入或一半被写入,且写入已在另一写入未命中高速缓存线上的受害者高速缓存中的下一条目上起始,就可逐出完整或半完整高速缓存线。此有助于解决其中处理器正发出集体大于受害者高速缓存的高速缓存写入未命中流的情况。而且,积极逐出完整或半完整写入未命中高速缓存线有助于避免在存储于受害者高速缓存中的大量写入未命中项由于操作结束时的栅栏操作而一次全部被冲刷时出现的性能问题。

88.为了帮助支持移除完整或半完整写入未命中高速缓存线,字节启用存储器702可包含两个状态位:半完整线状态位718及完整线状态位720。字节启用存储器702的每一线与受害者高速缓存ram 206中的高速缓存线对应,且字节启用存储器702的每一线可包含半完整线状态位718及完整线状态位720。这些状态位可在每一写入循环被更新,其中位被写入到配置为写入未命中缓冲器的高速缓存线中且状态位可基于已经存储于受害者高速缓存ram 706的对应线中的位以及在写入循环中被写入到受害者高速缓存ram 706的位来计算。在特定情况中,此更新可针对字节启用存储器702的每一高速缓存线在每一循环内执行,且可在不存在写入循环时省略更新。如上文指示,字节启用存储器702的每一线可包含指示字节启用存储器702的哪些位置(例如字节)是有效(例如,被写入到)的位掩码。确定哪些线是完整还是半完整可使用对位掩码的对应部分的xor执行。半完整线状态位718可在给定高速缓存线的一半已被写入时被设置为最低有效位或最高有效位。类似地,完整线状态位720可在整个高速缓存线已被写入时设置。接着,高速缓存线可被遍历(例如,按顺序检查)以确定传回具有完整或半完整高速缓存线的地址。在特定情况中,对应于完整高速缓存线的地址首先被选择,且如果不存在完整高速缓存线,那么与半完整高速缓存线对应的地址被传回。如果多个高速缓存线是完整的(或,如果不存在完整高速缓存线,那么是半完整的),那么可选择当遍历高速缓存线时被发现为完整(或半完整)的第一高速缓存线。如果无高速缓存线是完整或半完整的,那么写入未命中高速缓存线可基于fifo、lru来选择,或其它逻辑可用于在存在多个可用线时确定选择哪一高速缓存线。

89.逐出写入未命中条目可类似于自动冲刷那样操作,除了以下外:不校验存储队列以查看是否存在对应于被逐出的完整或半完整写入未命中高速缓存线的任何条目,这是由于此操作是由读取或写入未命中启动且在线已被写入之后执行。一旦已选择要逐出的完整或半完整写入未命中高速缓存线,逐出控制器714就向受害者高速缓存控制器734指示逐出所选择的高速缓存线。受害者高速缓存控制器734设置将要发送到更高级高速缓存或其它存储器的存储未命中数据包的创建。这些存储未命中数据包可包含存储于受害者高速缓存标签ram 704中的对应存储器地址、字节启用存储器702中的字节启用逻辑及受害者高速缓存ram 706中的数据。存储未命中数据包被发送例如到更高级高速缓存或其它存储器的高速缓存控制器,且可使受害者高速缓存ram 706、受害者高速缓存标签ram 704及字节启用存储器702中的对应条目失效。存储未命中数据包可被暂时放置于清空缓冲器716中,直到存储未命中数据包被其它存储器接受(例如确认)。

90.一旦已使写入未命中高速缓存线失效,高速缓存线的地址就可在每一写入循环被发送到替换政策逻辑722。可用的高速缓存线地址可被馈送到替换地址线726中的mux 724中。地址产生线728可包含指派给接收到的写入指令的地址。如果命中/未命中逻辑730确定接收到的写入指令的地址是命中,那么地址已被存储于受害者高速缓存的线中且来自写入指令的数据被合并到所述线。如果命中/未命中逻辑730确定接收到的写入指令的地址是未命中,那么来自替换地址线728的地址可用于将写入未命中命令写入到受害者高速缓存/写入未命中缓冲器。如果在受害者高速缓存/写入未命中缓冲器中不存在用于分配写入未命中的空高速缓存线,那么可触发逐出过程。在逐出过程中,集中式控制器可检测到已接收到需要被存储到受害者高速缓存中的写入未命中。集中式控制器可指示受害者高速缓存控制器734确保存在可用高速缓存线。此高速缓存线可基于由替换地址726或地址产生728提供的位置。如果已经存在存储于经识别位置中的写入未命中,那么可逐出写入未命中。

91.图8是根据此描述的方面的mesi ram 800的框图。mesi ram 800可为用于跟踪对应高速缓存线的mesi状态的存储器(例如sram)或一组寄存器(例如寄存器文件)。作为实例,在特定情况中,受害者高速缓存可针对高速缓存条目跟踪mesi ram 800中的mesi状态位802中的mesi状态作为写入数据的部分。在特定情况中,mesi ram 800包含对应于对应高速缓存(此处,受害者高速缓存)的每一线的线。主高速缓存可包含对应mesi ram。在特定情况中,单个mesi ram可被主高速缓存及受害者高速缓存两者共享。mesi ram 800可具有用于跟踪存储于受害者高速缓存中的每一高速缓存线的mesi状态的一组位。在特定情况中,mesi ram 800可用额外位来扩展以跟踪受害者高速缓存中的高速缓存线的其它状态。mesi ram 800可通过包含用于额外状态的额外列来扩展以跟踪额外状态。在此实例中,mesi ram已经扩展以在位字段中包含状态位来跟踪每一高速缓存线的特权等级804、红色标签806、蓝色标签808,无论线是否有效810,且无论线是写入未命中缓冲器还是受害者高速缓存线812。应注意,虽然展示为mesi ram的部分,但在其它实施例中,状态位可经放置于例如标签ram 704的其它存储器内或被一起放置于单独存储器中。mesi ram可经配置以跟踪此处未展示的额外状态。

92.在特定情况中,可能有用的是,冲刷存储于受害者高速缓存中的特定类型的所有写入未命中条目。如下文描述,写入未命中缓冲器中的条目可与“色”标相关联。此色标可由一或多位表示,使得当位经设置用于写入未命中缓冲条目时,与写入未命中缓冲条目相关联的颜色可为“蓝色”,且当位未被设置或另一位被设置时,写入未命中缓冲条目可为“红色”。加标签有助于允许特定写入未命中缓冲条目与在处理器上运行的特定过程相关联,而其它写入未命中缓冲条目可与在处理器上运行的另一过程相关联。在特定情况中,处理器可能希望冲刷与特定过程相关联的所有写入未命中缓冲条目(例如选择性栅栏操作),但不冲刷与另一过程相关联的写入未命中缓冲条目。

93.为了执行选择性栅栏操作,处理器可断言清空信号。与经断言清空信号一起,处理器可提供特定标签应优先被清空(红色或蓝色标签)的指示。返回参考图7,清空信号被传递到逐出控制器714。逐出控制器714可校验更高级高速缓存或存储器的可用性以查看更高级高速缓存或存储器是否忙。如果更高级高速缓存或存储器不可用,那么逐出控制器714可暂停处理器。如果更高级高速缓存或存储器可用,那么逐出控制器714可将指示优先标签的逐出触发请求发送到受害者高速缓存控制器734。接着,受害者高速缓存控制器734可校验存

储队列以查看在受害者高速缓存ram 706的任何组的存储队列中是否存在任何突出条目。受害者高速缓存控制器734也可向存储队列710指示升级清空存储队列的优先级。如果例如在存储队列中存在尚未被存储到受害者高速缓存的数据,那么逐出控制器714可等待存储队列710完成。一旦存储队列710为空,逐出控制器714就向受害者高速缓存控制器指示逐出所选择的高速缓存线。受害者高速缓存控制器734设置将要发送到更高级高速缓存或其它存储器的存储未命中数据包的创建。这些存储未命中数据包可包含存储于受害者高速缓存标签ram 704中的对应存储器地址、字节启用存储器702中的字节启用逻辑及受害者高速缓存ram 706中的数据。接着,受害者高速缓存可将存储未命中数据包发送例如到更高级高速缓存或其它存储器的高速缓存控制器。当冲刷写入未命中条目时,写入未命中数据包可被发送出到其它存储器,且可使受害者高速缓存ram 706、受害者高速缓存标签ram 704及字节启用存储器702中的对应条目失效。写入未命中数据包可被暂时放置于清空缓冲器716中,直到写入未命中数据包被其它存储器接受(例如确认)。此冲刷继续直到处理器停止断言清空信号。如果处理器在所指示颜色的所有写入未命中缓冲条目都已被清空之前停止断言清空信号,那么写入未命中缓冲器的清空在清空信号停止被断言时,受害者高速缓存所处的清空过程中的任何时候停止。一旦所指示色标的所有写入未命中缓冲条目都已被清空,空闲信号就被断言回到处理器。如果处理器继续断言清空信号,那么可清空与另一色标相关联的其它写入未命中缓冲条目。

94.将写入未命中放置于高速缓存系统中有助于提供将额外写入未命中合并到已经在高速缓存系统中的写入未命中的机会。由于写入未命中可在高速缓存内部保持更长时间,所以高速缓存具有将任何未来写入未命中合并到高速缓存系统中已经存在的写入未命中,从而减少离开到更高级存储器的写入未命中流量。减少被发送到更高级存储器的写入未命中可减小那些存储器上的压力且有助于改进整体性能。

95.写入合并可在处理器在框712处发出第二存储或写入命令到特定地址时发生。在受害者高速缓存是完全关联的情况下,第二写入的地址可由命中/未命中逻辑730对照存储于受害者高速缓存标签ram 704中的每一位置中的一组存储器地址校验。替换政策722逻辑并行地确定受害者高速缓存内部的写入事务可在写入未命中情况中被分配的位置。通常,当写入未命中被存储于受害者高速缓存中时,写入未命中被分配整个高速缓存线,即使写入未命中中的数据不需要整个高速缓存线。因此,一组存储器地址可与存储于受害者高速缓存中的每一写入未命中(包含写入未命中中的存储器地址)连同写入未命中中的存储器地址之前、之后或既在其之前又在其之后的一组存储器地址相关联。如果第二写入的地址被确定为在与存储于受害者高速缓存中的写入未命中相关联的一组存储器地址内,那么高速缓存命中被检测到且命中/未命中逻辑传回受害者高速缓存中的写入未命中当前被存储的位置。在e3管级中,与第二写入相关联的颜色类型及特权等级例如通过受害者高速缓存控制器734与当前存储的颜色类型及特权等级合并,且mesi ram732被更新。在特定情况中,合并特权等级可参考特权合并表736执行。第二写入的数据也可例如通过受害者高速缓存控制器734合并到受害者高速缓存706的对应线及基于与第二写入相关联的字节启用逻辑更新的字节启用存储器702的对应条目中。在特定情况中,存储队列710也可包含写入合并功能性。举例来说,当背靠背写入被发出到同一地址时,存储队列710可在内部合并其以有助于最小化发出到受害者高速缓存ram 706的写入数。

96.在特定情况中,写入合并可跨特权等级执行。合并特权等级可在执行写入合并时执行。举例来说,存储于受害者高速缓存中的第一写入未命中可与第一特权等级相关联。与第二特权等级相关联的第二写入可与所存储第一写入未命中合并。为了执行合并,特权等级也应被合并。在特定情况中,特权等级可通过将特权等级合并到特权等级的较低等级来合并。举例来说,在实施例中,写入操作可与两部分特权等级(例如根/访客用户/监督者)相关联。第一写入未命中可以根用户的特权等级接收。此第一写入未命中可经写入到受害者高速缓存中的写入未命中缓冲器。具有访客监督者的特权等级的第二写入可被接收,第二写入被引导到与第一写入未命中相关联的一组地址内的地址。当合并两个写入的特权等级时,可使用较低特权等级,从而导致访客用户的经合并特权等级。在特定情况中,合并特权等级可在针对多个数据路径执行合并时以相同方式操作。在特定情况中,特权等级合并可经编码于特权合并表736中,从而指示可如何合并不同的特权等级。在特定情况中,可预定义特权合并表736。在表1中展示经预定义特权合并表736的实例。在特定情况中,特权合并表736是可配置的。

97.表1

[0098][0099][0100]

在特定情况中,可针对色标执行写入合并。举例来说,存储于受害者高速缓存中的第一写入未命中可与例如红色的第一色标相关联。参考图8,第一写入未命中可与具有设置

于位字段的红色标签806中的位的mesi ram 800中的条目相关联。与第二色标相关联的第二写入可与所存储第一写入未命中合并。为了执行合并,色标也应被合并。在特定情况中,色标可通过组合写入的色标来合并。举例来说,如果两个写入都是加红色标签,那么经合并写入保持加红色标签。类似地,如果两个写入都被加蓝色标签,那么经合并写入将被加蓝色标签。如果一个写入被加红色标签且另一写入被加蓝色标签,那么经合并写入既被加红色标签也被加蓝色标签。因此,如果将要合并的第二写入与蓝色标签相关联,那么经合并写入可具有设置于位字段的红色标签806中的位及设置于位字段的蓝色标签808中的位。在特定情况中,如果接着执行清空操作,例如针对蓝色标签,那么将清空经合并写入。类似地,如果针对红色标签执行清空操作,那么经合并写入也将被清空,这是由于经合并写入既被加红色标签又被加蓝色标签。

[0101]

图9是根据此描述的方面的包含写入未命中缓冲器的高速缓存系统900的架构框图。如展示,高速缓存902可经由处理器接口906接收来自处理器904的高速缓存请求。在特定情况中,高速缓存902可经配置以处理标量或矢量数据或两者。高速缓存902被逻辑划分成包含主高速缓存908及受害者高速缓存910的并行子高速缓存。虽然展示单个主高速缓存908及受害者高速缓存910,但特定实施例可包含多个主高速缓存908及受害者高速缓存910对。在特定情况中,可存在不同数目个主高速缓存908及受害者高速缓存910。关于主高速缓存908,主高速缓存标签ram存取控制器912存取主高速缓存标签ram 914且对照包含于高速缓存请求中的存储器地址校验主高速缓存标签ram 914以确定存储器地址是否存储于主高速缓存908中。主高速缓存控制器916引导适当分配、逐出、仲裁、合并等过程及读取/写入到主高速缓存存储器918中。结合图3所描述的主高速缓存存储队列结构920提供例如rmw、ecc、写入合并等的特征。

[0102]

受害者高速缓存910的整体架构类似于主高速缓存908的整体架构。举例来说,针对接收到的存储器请求,受害者高速缓存标签ram存取控制器922存取受害者高速缓存标签ram 924且对照包含于高速缓存请求中的存储器地址校验受害者高速缓存标签ram 924以确定存储器地址是否存储于受害者高速缓存910中。受害者高速缓存控制器926类似地引导适当分配、逐出、仲裁、合并等过程及读取/写入到受害者高速缓存存储器928中。受害者高速缓存存储队列930提供rmw、ecc及其它特征,如结合图3描述。受害者高速缓存逻辑932有助于协调受害者高速缓存910与主高速缓存908之间的操作。虽然受害者高速缓存逻辑932被单独展示,但受害者高速缓存逻辑932可与其它元件集成或可为其它元件的部分,例如受害者高速缓存控制器926。在特定情况中,受害者高速缓存908包含特定元件,所述特定元件有助于启用受害者高速缓存908来支持写入未命中缓冲功能性。举例来说,自动冲刷逻辑934可监测处理器接口906且经由一或多个存储器接口936引导将经分配用于写入未命中缓冲的受害者高速缓存存储器928的部分清空例如到更高级高速缓存及存储器。作为另一实例,mesi ram 938或受害者高速缓存标签ram可经配置以包含一或多位字段来存储关于存储于受害者高速缓存910中的写入未命中缓冲条目的状态信息。

[0103]

在特定情况中,受害者高速缓存及主高速缓存可包含多个数据路径同时经配置为对处理器来说表现为单个高速缓存的并行高速缓存。每一数据路径经配置以与其它数据路径并行地处理特定命令。举例来说,第一数据路径910可正处理到主高速缓存的读取命令,而第二数据路径942处理到受害者高速缓存的写入未命中。在具有用于受害者高速缓存的

两个数据路径的实施例中,可存在用于第一数据路径940及第二数据路径942的高速缓存命令的四种组合:读取/读取、读取/写入、写入/读取及写入/写入。另外,每一命令组合可导致高速缓存命中/命中、命中/未命中、未命中/命中或未命中/未命中。另外,两个命令可潜在地被寻址到具有不同特权等级及色标的相同存储器地址。在特定情况中,为了促进控制并行高速缓存,集中式控制器944可有助于协调主高速缓存908与受害者高速缓存910之间的读取及写入请求的处理。在特定情况中,集中式控制器944可经配置以处理主高速缓存908与受害者高速缓存910之间的协调及将主高速缓存908及受害者高速缓存910的任务分别交给主高速缓存控制器916及受害者高速缓存控制器926。集中式控制器944同样也可检测及处理潜在冲突。举例来说,在从处理器接收到读取请求的情况下,集中式控制器944可校验主高速缓存908及受害者高速缓存910以确定读取请求的经寻址存储器位置既未被存储于主高速缓存908也未被存储于受害者高速缓存910中且因此是读取未命中。集中式控制器944也可校验受害者高速缓存910以确定经寻址存储器地址并未作为写入未命中被存储于受害者高速缓存910中,或被冲刷出受害者高速缓存910。如果经寻址存储器位置作为写入未命中被存储于受害者高速缓存910中,那么集中式控制器944可暂停冲刷经寻址存储器位置的读取请求。接着,集中式控制器944可发出对经寻址存储器位置的请求到更高级高速缓存或存储器。

[0104]

在特定情况中,如果读取或写入请求是主高速缓存908中的命中,那么可忽视受害者高速缓存910的结果。在主高速缓存908经配置为单路关联高速缓存的情况下,多个数据路径的高速缓存请求冲突是明确的。来自多个数据路径的高速缓存请求冲突可为受害者高速缓存910中的问题,其中受害者高速缓存910是完全关联的且可存储写入未命中条目以及高速缓存条目。两个数据路径的高速缓存请求冲突可如在以下实例中描述那样被处理。值得注意的是,在以下实例中,高速缓存操作在特定数据路径的上下文中描述。然而,实例涉及特定高速缓存操作的组合,且特定高速缓存操作在哪一数据路径上无关紧要。

[0105]

在第一实例中,存在针对第一数据路径的高速缓存读取未命中,及针对第二数据路径的高速缓存写入命中,具有两个不同存储器地址。在其中受害者高速缓存910是完全关联的特定情况中,高速缓存请求可到达受害者高速缓存910内的任何位置。参考图7,针对受害者高速缓存内的位置的地址产生928在e2管级中连同受害者高速缓存标签ram 904中的地址查找一起发生,因此针对受害者高速缓存内的位置的地址产生728在已知高速缓存请求的地址是命中还是未命中之前被执行。一旦集中式控制器944确定在主高速缓存908上存在读取未命中,那么获得读取请求的存储器地址的请求被发出到更高级高速缓存或存储器。在主高速缓存908是单路关联的情况下,第一数据路径的读取请求的存储器地址映射到主高速缓存908中的单个位置。如果在单个位置中存在已经高速缓存的数据,那么已经高速缓存的数据从主高速缓存908被逐出到受害者高速缓存910到受害者高速缓存910内的预产生位置。如果此预产生位置与第二数据路径的高速缓存写入命中所处的位置相同,那么发生冲突。此冲突可由集中式控制器944检测。如上文指示,针对受害者高速缓存910内的位置的地址产生在已知高速缓存请求地址是命中还是未命中之前发生,因此在确定高速缓存写入是命中之前针对第二数据路径的高速缓存写入存在针对受害者高速缓存910内的第二位置产生的地址。基于冲突的检测,受害者高速缓存内的此第二位置可用于存储因读取未命中而从主高速缓存908逐出的数据。

[0106]

在另一实例中,如同第一实例,可存在针对第一数据路径的高速缓存读取未命中及针对第二数据路径的高速缓存写入命中,但在此实例中,高速缓存读取在主高速缓存中未命中且高速缓存写入在主高速缓存中也命中。在特定情况中,主高速缓存是单路关联高速缓存(例如直接映射高速缓存),其中特定存储器地址经映射到主高速缓存内的特定位置。在具有直接映射高速缓存的此实例中,高速缓存读取及高速缓存写入经映射到主高速缓存中的同一位置。在此实例中,由于读取未命中,获得读取请求的存储器地址的请求经发出到更高级高速缓存或存储器,且已经高速缓存的数据从主高速缓存908逐出到受害者高速缓存910到受害者高速缓存910内的预产生位置,此处是位置a。在此实例中,第二数据路径的高速缓存写入命中被逐出的主高速缓存中的同一位置。对此冲突的一种可能解决方案是将所请求读取未命中从更高级高速缓存或存储器直接加载到受害者高速缓存的单独位置中。对冲突的另一解决方案是使集中式控制器944暂停读取未命中,使得已经高速缓存的数据不被逐出到受害者高速缓存910直到第二数据路径的高速缓存写入完成到达主高速缓存中的位置a且接着位置a被逐出到受害者高速缓存之后。在特定情况中,暂停可在等待存储器写入及逐出完成时发生。

[0107]

作为另一实例,第一高速缓存写入可在用于受害者高速缓存910的第一数据路径上接收,且第二高速缓存写入也在用于受害者高速缓存910的第二数据路径上接收。如果第一高速缓存写入及第二高速缓存写入被寻址到不同存储器地址,那么两个高速缓存写入可与受害者高速缓存910并行地继续进行。如果第一高速缓存写入及第二高速缓存写入两者都被寻址到相同存储器地址且两者都是高速缓存未命中,那么受害者高速缓存控制器926分配受害者高速缓存写入未命中存储器928中的单个位置且合并受害者高速缓存存储队列930中的第一高速缓存写入及第二高速缓存写入。接着,经合并数据可连同经合并字节启用、特权及色标信息一起被写入到受害者高速缓存写入未命中存储器928。如果第一高速缓存写入及第二高速缓存写入两者都被寻址到相同存储器地址且两者都是高速缓存命中,那么第一高速缓存写入及第二高速缓存写入两者经合并到高速缓存中的命中位置处。

[0108]

作为另一实例,高速缓存读取可在用于受害者高速缓存910的第一数据路径上接收,且高速缓存写入可在用于受害者高速缓存910的第二数据路径上接收。在其中对于受害者高速缓存910中的不同位置,高速缓存读取是命中且高速缓存写入是命中的情况中,高速缓存读取及高速缓存写入在不存在冲突的情况下并行继续进行。在对于受害者高速缓存910中的不同位置,高速缓存读取是命中且高速缓存写入是未命中的情况中,高速缓存读取及高速缓存写入也在不存在冲突的情况下并行继续进行。在对于受害者高速缓存910中的不同位置,高速缓存读取是未命中且高速缓存写入是命中的情况中,高速缓存读取可使用针对受害者高速缓存910内的位置产生的地址用于如上文描述的高速缓存写入。在对于受害者高速缓存910中的不同位置,高速缓存读取是未命中且高速缓存写入是未命中的情况中,高速缓存读取及高速缓存写入两者都使用针对受害者高速缓存910内的位置产生的地址。

[0109]

在另一实例中,高速缓存读取可在用于主高速缓存908的第一数据路径上接收,且高速缓存写入可在用于主高速缓存908的第二数据路径上接收。在特定情况中,高速缓存读取可为针对主高速缓存908的位置(例如高速缓存线或槽)的命中。高速缓存写入也可为针对主高速缓存908的同一位置的命中。在此情况中,高速缓存读取及高速缓存写入可在不存

在冲突的情况下并行继续进行,这是由于高速缓存读取可相对快速地执行且在随着高速缓存写入通过存储队列继续进行高速缓存写入需要存取主高速缓存位置之前结束。在另一情况中,高速缓存读取可为针对主高速缓存908中的位置的命中。高速缓存写入可为针对主高速缓存908中的同一位置的未命中。在此情况中,高速缓存命令通常并行继续进行,这是由于高速缓存读取可在高速缓存写入需要存取高速缓存位置之前完成。在另一情况中,高速缓存读取可为针对主高速缓存908中的位置的未命中。高速缓存写入可为针对主高速缓存910中的同一位置的命中。在此情况中,类似于上文所描述,高速缓存读取可被暂停直到第二数据路径的高速缓存写入完成到达主存储器908中的位置且被逐出到受害者高速缓存908之后。接着,高速缓存读取继续进行将一组地址从更高级高速缓存或存储器读取到主高速缓存910中。在另一情况中,高速缓存读取可为针对主高速缓存908中的第一位置的未命中。高速缓存写入也可为针对主高速缓存908中的同一位置的未命中。在此情况中,高速缓存读取及高速缓存写入可在不存在冲突的情况下并行继续进行。

[0110]

在另一实例中,高速缓存读取可在用于受害者高速缓存910的第一数据路径上接收,且高速缓存写入可在用于受害者高速缓存910的第二数据路径上接收。在特定情况中,高速缓存读取可为针对存储于受害者高速缓存910中的地址的命中。高速缓存写入也可为针对存储于受害者高速缓存910中的同一地址的命中。在此情况中,高速缓存读取首先可继续进行且高速缓存写入可被暂停直到高速缓存读取完成之后。替代地,高速缓存写入及高速缓存读取的顺序可基于高速缓存写入及高速缓存读取在其上被接收的数据路径,其中到达更低(或更高)编号的数据路径上的高速缓存命令在另一高速缓存命令之前完成。在特定情况中,高速缓存读取可为针对存储于受害者高速缓存910中的地址的未命中。高速缓存写入也可为针对存储于受害者高速缓存910中的同一地址的未命中。在此情况中,高速缓存写入命令可经转发到更高级高速缓存或存储器,且接着高速缓存读取可在高速缓存写入命令完成存储到受害者高速缓存910中之后从更高级高速缓存或存储器获得数据。

[0111]

在另一实例中,第一高速缓存读取可在用于受害者高速缓存910的第一数据路径上接收,且第二高速缓存读取可在用于受害者高速缓存910的第二数据路径上接收。如果第一高速缓存读取及第二高速缓存读取是针对不同存储器地址,那么命中或未命中不存在冲突。在特定情况中,第一高速缓存读取可为针对一组地址中的第一地址的未命中。第二高速缓存读取也可为针对同一组地址中的第二地址的未命中。如果第一高速缓存读取及第二高速缓存读取具有不同优先级,那么更高级高速缓存或存储器基于不同优先级中的更高者被存取。否则,更高级高速缓存或存储器被存取且获得一组存储器地址用于存储于受害者高速缓存910中。其中第一高速缓存读取及第二高速缓存读取是针对同一地址的情况被相同地处理。

[0112]

图10是说明根据此描述的方面的用于高速缓存数据1000的技术的流程图。在框1002,高速缓存系统接收对存储器地址的写入存储器请求。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。在框1004,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对未含于高速缓存系统内的存储器地址的写入请求被接收时发生。在框1006,高速缓存系统的第二子高速缓存

确定存储器地址未被高速缓存于第二子高速缓存中。在框1008,将与写入存储器请求相关联的数据存储于第二子高速缓存中。举例来说,写入存储器请求的数据可经存储于受害者高速缓存中。而且,与写入存储器请求相关联的地址可经存储于受害者高速缓存的标签ram中,且与写入存储器请求相关联的字节启用逻辑可经存储于受害者高速缓存的字节启用存储器中。在框1010,将所存储数据对应于写入未命中的指示存储于第二子高速缓存的线类型位中。举例来说,受害者高速缓存包含与受害者高速缓存的线相关联的线类型位。位可经设置于指示受害者高速缓存的特定线包含写入未命中的线类型位中。在框1012,可基于指示冲刷所存储数据。举例来说,所存储写入未命中数据可通过校验高速缓存线的线类型位及冲刷与写入未命中相关联的线来从受害者高速缓存被冲刷到更高级存储器。

[0113]

图11是说明根据此描述的方面的用于高速缓存数据1100的技术的流程图。在框1102,高速缓存系统接收对存储器地址的写入存储器请求。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。在框1104,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对未含于高速缓存系统内的存储器地址的写入请求被接收时发生。在框1106,高速缓存系统的第二子高速缓存确定存储器地址未被高速缓存于第二子高速缓存中。在框1108,将与写入存储器请求相关联的数据存储于第二子高速缓存中。举例来说,写入存储器请求的数据可经存储于受害者高速缓存中。而且,与写入存储器请求相关联的地址可经存储于受害者高速缓存的标签ram中,且与写入存储器请求相关联的字节启用逻辑可经存储于受害者高速缓存的字节启用存储器中。在框1110,将所存储数据对应于写入未命中的指示存储于第二子高速缓存的线类型位中。举例来说,受害者高速缓存包含与受害者高速缓存的线相关联的线类型位。位可经设置于指示受害者高速缓存的特定线包含写入未命中的线类型位中。在框1112,基于线已被完全写入的指示逐出存储写入未命中的第二子高速缓存的线。举例来说,线可基于指示是高速缓存线的字节的全部或一半已用写入数据填充的字节启用逻辑来计算。被填充或半填充的高速缓存线可基于位从受害者高速缓存逐出。

[0114]

图12是说明根据此描述的方面的用于高速缓存数据1200的技术的流程图。在框1202,高速缓存系统接收对存储器地址的写入存储器命令,写入存储器命令与第一特权等级相关联。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。在框1204,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对既不含于主高速缓存内也不含于受害者高速缓存内的存储器地址的写入请求被接收时发生。在框1206,高速缓存系统的第二子高速缓存确定存储器地址未被高速缓存于第二子高速缓存中,且第二子高速缓存经配置以与第一子高速缓存平行地存储从第一子高速缓存逐出的高速缓存数据及未高速缓存于第一子高速缓存中的写入存储器命令。在框1208,将与写入存储器命令相关联的数据存储于第二子高速缓存中。在框1210,将与数据相关联的色标位存储于第二子高速缓存中。举例来说,色标位可经存储于例如mesi ram的第二子高速缓存的存储器的位字段内。在框1212,基于色标位逐出所存储数据。

举例来说,存储与特定色标位相关联的写入未命中数据的高速缓存线可在处理器断言清空信号及色标优先级指示时被逐出。在具有特定色标位的所有高速缓存线已被清空之后,高速缓存系统可断言空闲信号。如果处理器继续断言清空信号,那么存储与其它色标相关联的写入未命中数据的其它高速缓存线也可被逐出。

[0115]

图13是说明根据此描述的方面的用于高速缓存数据1300的技术的流程图。在框1302,高速缓存系统接收对存储器地址的写入存储器命令,写入存储器命令与第一色标相关联。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。写入请求可包含与写入请求相关联的色标的指示中。在框1304,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对未含于高速缓存系统内的存储器地址的写入请求被接收时发生。在框1306,高速缓存系统的第二子高速缓存确定存储器地址未被高速缓存于第二子高速缓存中。在框1308,将与写入存储器命令相关联的数据存储于第二子高速缓存的高速缓存线中。举例来说,写入请求的数据可经存储于受害者高速缓存的高速缓存线中。而且,与写入存储器请求相关联的地址可经存储于受害者高速缓存的标签ram中,且与写入存储器请求相关联的字节启用逻辑可经存储于受害者高速缓存的字节启用存储器中。在框1310,将第一色标存储于第二子高速缓存中。举例来说,色标可使用例如mesi ram的第二子高速缓存的存储器的位字段内的2位存储。在框1312,接收用于高速缓存线的第二写入存储器命令,写入存储器命令与第二色标相关联。举例来说,可接收对以与第一写入请求相同的高速缓存线为目标的存储器地址的第二写入请求。第二写入请求与第二色标相关联。第二色标可与第一色标相同或不同。在框1314,合并第二色标与第一色标。举例来说,在第一色标及第二色标表示相同颜色的情况下,合并两个标签继续设置那个色标。在两个色标不同的情况下,合并可设置两个色标。在框1316,存储经合并色标。在框1318,可基于经合并色标逐出高速缓存线。举例来说,在第一色标及第二色标表示相同颜色的情况下,逐出可基于那个色标。在两个色标不同的情况下,逐出可基于任一色标。

[0116]

图14是说明根据此描述的方面的用于高速缓存数据1400的技术的流程图。在框1402,高速缓存系统接收对存储器地址的第一写入存储器命令,第一写入存储器命令与第一特权等级相关联。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。在框1404,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对既不含于主高速缓存内也不含于受害者高速缓存内的存储器地址的写入请求被接收时发生。在框1406,高速缓存系统的第二子高速缓存确定存储器地址未被高速缓存于第二子高速缓存中,且第二子高速缓存经配置以与第一子高速缓存平行地存储从第一子高速缓存逐出的高速缓存数据及未高速缓存于第一子高速缓存中的写入存储器命令。在框1408,将与第一写入存储器命令相关联的第一数据存储于第二子高速缓存的高速缓存线中。在框1410,将第一特权等级存储于第二子高速缓存中。举例来说,第一特权等级可包括两部分特权等级,例如根/访客用户/监督者。此两部分特权等级可使用

例如mesi ram的第二子高速缓存的存储器的位字段内的2位存储。在框1412,接收用于高速缓存线的第二写入存储器命令,第二写入存储器命令与第二特权等级相关联。举例来说,可接收对以与第一写入请求相同的高速缓存线为目标的存储器地址的第二写入请求。第二写入请求与第二特权等级相关联,其可与第一写入请求相同或不同。在框1414,合并第一特权等级与第二特权等级。举例来说,特权等级可基于特权合并表合并或可通过选择被合并的特权等级中的较低特权等级来合并。在框1416,存储经合并特权等级。在框1418,用高速缓存线输出经合并特权等级。举例来说,包含经合并第一写入请求及第二写入请求的高速缓存线可在包含经合并特权等级的存储未命中数据包中被逐出到更高级高速缓存或存储器。

[0117]

图15是说明根据此描述的方面的用于高速缓存数据1500的技术的流程图。在框1502,高速缓存系统接收对存储器地址的写入存储器请求。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口接收来自处理器的写入请求。在框1504,高速缓存系统的第一子高速缓存确定存储器地址未被高速缓存于第一子高速缓存中。举例来说,高速缓存系统可包含两个并行高速缓存:主高速缓存及受害者高速缓存。高速缓存请求的存储器地址可对照主高速缓存及受害者高速缓存两者并行地校验。写入未命中在对未含于高速缓存系统内的存储器地址的写入请求被接收时发生。在框1506,高速缓存系统的第二子高速缓存确定存储器地址未被高速缓存于第二子高速缓存中。在框1508,将与写入存储器请求相关联的数据存储于第二子高速缓存中。举例来说,写入存储器请求的数据可经存储于受害者高速缓存中。而且,与写入存储器请求相关联的地址可经存储于受害者高速缓存的标签ram中,且与写入存储器请求相关联的字节启用逻辑可经存储于受害者高速缓存的字节启用存储器中。在框1510,将所存储数据对应于写入未命中的指示存储于第二子高速缓存的线类型位中。举例来说,受害者高速缓存包含与受害者高速缓存的线相关联的线类型位。位可经设置于指示受害者高速缓存的特定线包含写入未命中的线类型位中。

[0118]

图16是说明根据此描述的方面的用于高速缓存数据1600的技术的流程图。在框1602,高速缓存系统接收两个或更多个高速缓存命令。举例来说,例如l1高速缓存的高速缓存系统可经由处理器接口使用例如两个或更多个数据路径接收多个高速缓存命令。在框1604,确定在两个或更多个高速缓存命令之间存在冲突。举例来说,高速缓存控制器可确定高速缓存冲突存在于两个高速缓存命令之间。当两个高速缓存命令致使对同一高速缓存位置的冲突改变时,可出现冲突。在框1606,确定接收到的两个或更多个高速缓存命令之间的冲突解决。在框1608,将两个或更多个高速缓存命令发送到第一子高速缓存及第二子高速缓存,且第二子高速缓存经配置以与第一子高速缓存平行地存储从第一子高速缓存逐出的高速缓存数据及未高速缓存于第一子高速缓存中的写入存储器命令。

[0119]

实例:

[0120]

在以下段落中,提供进一步示范性实施例。

[0121]

实例1包含一种高速缓存系统,其包括:第一子高速缓存;及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述线类型位冲刷所存储写入未命中数据。

[0122]

实例2包含实例1所述的高速缓存系统,其中所述第二子高速缓存进一步包括:标签随机存取存储器(ram),其经配置以存储与所述所存储写入未命中数据相关联的存储器

地址;及字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑,且其中所述逐出控制器经配置以通过基于所述所存储存储器地址及所存储字节启用逻辑将存储器写入请求传输到更高级存储器来冲刷所存储写入未命中数据。

[0123]

实例3包含实例1所述的高速缓存系统,其中所述高速缓存系统进一步包含处理器接口,且其中所述逐出控制器进一步经配置以:监测所述处理器接口上的活动;及基于所述监测到的活动冲刷所存储写入未命中数据。

[0124]

实例4包含实例3所述的高速缓存系统,其中监测所述处理器接口上的活动包括检测所述处理器接口上的空闲活动。

[0125]

实例5包含实例4所述的高速缓存系统,其中检测空闲活动包括确定存储器请求是否已在预定数目个时钟循环内被接收。

[0126]

实例6包含实例4所述的高速缓存系统,其中所述逐出控制器进一步经配置以:确定所述处理器接口上的活动已恢复;及取消所述所存储写入未命中数据的冲刷。

[0127]

实例7包含实例6所述的高速缓存系统,其中确定所述处理器接口上的活动已恢复包括检测从处理器的高速缓存请求接收。

[0128]

实例8包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中;及基于所述指示冲刷所述所存储数据。

[0129]

实例9包含实例8所述的方法,其中冲刷所述所存储数据包括由所述第二子高速缓存将存储器写入请求传输到更高级存储器。

[0130]

实例10包含实例8所述的方法,其进一步包括监测处理器接口上的活动,且其中冲刷所述所存储数据是进一步基于所述监测到的活动。

[0131]

实例11包含实例10所述的方法,其中监测所述处理器接口上的活动包括检测所述处理器接口上的空闲活动。

[0132]

实例12包含实例11所述的方法,其中检测空闲活动包括确定存储器请求在预定数目个时钟循环内尚未被接收。

[0133]

实例13包含实例11所述的方法,其进一步包括:确定所述处理器接口上的活动已恢复;及取消所述所存储写入未命中数据的冲刷。

[0134]

实例14包含实例13所述的方法,其中确定所述处理器接口上的活动已恢复包括检测高速缓存请求接收。

[0135]

实例15包含一种装置,其包括:处理器;第一子高速缓存:及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述线类型位冲刷所存储写入未命中数据。

[0136]

实例16包含实例15所述的装置,其中所述第二子高速缓存进一步包括:标签随机存取存储器(ram),其经配置以存储与所述所存储写入未命中数据相关联的存储器地址;及字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑,

且其中所述逐出控制器经配置以通过基于所述所存储存储器地址及所存储字节启用逻辑将存储器写入请求传输到更高级存储器来冲刷所存储写入未命中数据。

[0137]

实例17包含实例15所述的装置,其中高速缓存系统进一步包含处理器接口,且其中所述逐出控制器进一步经配置以:监测所述处理器接口上的活动;及基于所述监测到的活动冲刷所存储写入未命中数据。

[0138]

实例18包含实例17所述的装置,其中监测所述处理器接口上的活动包括检测所述处理器接口上的空闲活动。

[0139]

实例19包含实例18所述的装置,其中检测空闲活动包括确定存储器请求是否已在预定数目个时钟循环内被接收。

[0140]

实例20包含实例18所述的装置,其中所述逐出控制器进一步经配置以:确定所述处理器接口上的活动已恢复;及取消所述所存储写入未命中数据的冲刷。

[0141]

实例21包含一种高速缓存系统,其包括:第一子高速缓存;及第二子高速缓存,其与所述第一高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且其中所述第二子高速缓存包含:色标位,其经配置以存储存储写入未命中数据的所述第二子高速缓存的对应高速缓存线与色标相关联的指示;及逐出控制器,其经配置以基于与所述高速缓存线相关联的所述色标逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0142]

实例22包含实例21所述的高速缓存系统,其中所述第二子高速缓存包含经配置以存储所述色标的状态的位字段。

[0143]

实例23包含实例22所述的高速缓存系统,其中所述位字段包含存储每一色标的所述状态的位。

[0144]

实例24包含实例23所述的高速缓存系统,其中所述位字段经存储于跟踪所述第二子高速缓存中的条目的修改、独占、共享及无效(mesi)状态的存储器中。

[0145]

实例25包含实例24所述的高速缓存系统,其中所述mesi存储器经配置以存储所述第二子高速缓存的所述对应高速缓存线正存储写入未命中数据的指示。

[0146]

实例26包含实例21所述的高速缓存系统,其中所述高速缓存系统进一步包含处理器接口,且其中所述逐出控制器进一步经配置以:在所述处理器接口上接收色标优先级指示;及基于所述接收到的色标优先级指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0147]

实例27包含权利要求6所述的高速缓存系统,其中所述逐出控制器进一步经配置以:在存储具有对应于所述色标优先级指示的色标位的写入未命中数据的所述第二子高速缓存的所有高速缓存线已被逐出之后在所述处理器接口上断言空闲信号。

[0148]

实例28包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收用于存储器地址的写入存储器命令;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述写入存储器命令相关联的数据存储于所述第二子高速缓存中;将与所述数据相关联的色标位存储于所述第二子高速缓存

中;及基于所述色标位逐出所述所存储数据。

[0149]

实例29包含实例28所述的方法,其进一步包括:接收来自处理器的色标优先级指示;接收来自所述处理器的清空信号;且其中逐出所述所存储数据是基于所述接收到的色标优先级指示。

[0150]

实例30包含权利要求实例29所述的方法,其进一步包括:在存储具有对应于所述色标优先级指示的色标位的写入未命中数据的所述第二子高速缓存的所有高速缓存线已被逐出之后断言空闲信号。

[0151]

实例31包含实例30所述的方法,其进一步包括:继续接收来自所述处理器的所述清空信号;及逐出具有不对应于所述色标优先级指示的色标位的所存储数据。

[0152]

实例32包含实例39所述的方法,其进一步包括:确定存储所述数据尚未完成;及等待直到所述数据已被存储。

[0153]

实例33包含实例38所述的方法,其进一步包括将所述色标位存储于与对应色标位相关联的位字段中。

[0154]

实例34包含一种装置,其包括:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且其中所述第二子高速缓存包含:色标位,其经配置以存储存储写入未命中数据的所述第二子高速缓存的对应高速缓存线与色标相关联的指示;及逐出控制器,其经配置以基于与所述高速缓存线相关联的所述色标逐出存储写入未命中数据的所述第二子高速缓存的所述高速缓存线。

[0155]

实例35包含实例34所述的装置,其中所述第二子高速缓存包含经配置以存储所述色标的状态的位字段。

[0156]

实例36包含实例35所述的装置,其中所述位字段包含存储每一色标的所述状态的位。

[0157]

实例37包含实例36所述的装置,其中所述位字段经存储于跟踪所述第二子高速缓存中的条目的修改、独占、共享及无效(mesi)状态的存储器中。

[0158]

实例38包含实例37所述的装置,其中所述mesi存储器经配置以存储所述第二子高速缓存的所述对应高速缓存线正存储写入未命中数据的指示。

[0159]

实例39包含实例34所述的装置,其中所述高速缓存系统进一步包含处理器接口,且其中所述逐出控制器进一步经配置以:在所述处理器接口上接收色标优先级指示;及基于所述接收到的色标优先级指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0160]

实例40包含实例39所述的装置,其中所述逐出控制器进一步经配置以:在存储具有对应于所述色标优先级指示的色标位的写入未命中数据的所述第二子高速缓存的所有高速缓存线已被逐出之后在所述处理器接口上断言空闲信号。

[0161]

实例41包含一种高速缓存系统,其包括:第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:色标位,其经配置以存储所述第二子高速缓存的对应线与色标相关联的指示;及逐出控制器,其经配置以基于与所述线相关联的所述色标逐出存储写入存储器数据的所述第二子高速

缓存的高速缓存线,且其中所述第二子高速缓存进一步经配置以:接收对存储器地址的第一写入存储器命令,所述写入存储器命令与第一色标相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

[0162]

实例42包含实例41所述的高速缓存系统,其中所述第一色标及所述第二色标表示同一色标。

[0163]

实例43包含实例41所述的高速缓存系统,其中所述第一色标及所述第二色标表示不同色标,且其中所述经合并色标包括表示所述第一色标的第一位及表示所述第二色标的第二位。

[0164]

实例44包含实例43所述的高速缓存系统,其中所述第二子高速缓存进一步经配置以基于所述第一色标逐出所述高速缓存线。

[0165]

实例45包含实例44所述的高速缓存系统,其中所述第二子高速缓存进一步经配置以基于所述第二色标逐出所述高速缓存线。

[0166]

实例46包含实例41所述的高速缓存系统,其中所述第一色标及第二色标经存储于跟踪所述第二子高速缓存数据中的条目的修改、独占、共享及无效(mesi)状态的存储器中的位字段中。

[0167]

实例47包含实例46所述的高速缓存系统,其中所述位字段包含存储每一色标的状态的位。

[0168]

实例48包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收用于存储器地址的写入存储器命令,所述写入存储器命令与第一色标相关联;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

[0169]

实例49包含实例48所述的方法,其中所述第一色标及所述第二色标表示同一色标。

[0170]

实例50包含实例48所述的方法,其中所述第一色标及所述第二色标表示不同色标,且其中所述经合并色标包括表示所述第一色标的第一位及表示所述第二色标的第二位。

[0171]

实例51包含实例50所述的方法,其中所述逐出是基于所述第一色标。

[0172]

实例52包含实例51所述的方法,其中所述逐出是基于所述第二色标。

[0173]

实例53包含实例48所述的方法,其中所述第一色标及第二色标经存储于跟踪所述第二子高速缓存数据中的条目的修改、独占、共享及无效(mesi)状态的存储器中的位字段

中。

[0174]

实例54包含权利要求实例53所述的方法,其中所述位字段包含存储每一色标的状态的位。

[0175]

实例55包含一种装置,其包括:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,且所述第二子高速缓存包含:色标位,其经配置以存储所述第二子高速缓存的对应线与色标相关联的指示;及逐出控制器,其经配置以基于与所述线相关联的所述色标逐出存储写入存储器数据的所述第二子高速缓存的高速缓存线,且其中所述第二子高速缓存进一步经配置以:接收对存储器地址的第一写入存储器命令,所述写入存储器命令与第一色标相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一色标存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述写入存储器命令与第二色标相关联;合并所述第二色标与所述第一色标;存储所述经合并色标;及基于所述经合并色标逐出所述高速缓存线。

[0176]

实例56包含实例55所述的装置,其中所述第一色标及所述第二色标表示同一色标。

[0177]

实例57包含实例55所述的装置,其中所述第一色标及所述第二色标表示不同色标,且其中所述经合并色标包括表示所述第一色标的第一位及表示所述第二色标的第二位。

[0178]

实例58包含实例57所述的装置,其中所述第二子高速缓存进一步经配置以基于所述第一色标逐出所述高速缓存线。

[0179]

实例59包含实例58所述的装置,其中所述第二子高速缓存进一步经配置以基于所述第二色标逐出所述高速缓存线数据。

[0180]

实例60包含实例55所述的装置,其中所述第一色标及第二色标经存储于跟踪所述第二子高速缓存数据中的条目的修改、独占、共享及无效(mesi)状态的存储器中的位字段中。

[0181]

实例61包含一种高速缓存系统,其包括:第一子高速缓存;第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:特权位,其经配置以存储所述第二子高速缓存的对应高速缓存线与特权等级相关联的指示,且其中所述第二子高速缓存进一步经配置以:接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将与所述高速缓存线相关联的所述特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

[0182]

实例62包含实例61所述的高速缓存系统,其中特权等级信息经存储于跟踪所述第二子高速缓存数据中的条目的修改、独占、共享及无效(mesi)状态的存储器中的位字段中。

[0183]

实例63包含实例62所述的高速缓存系统,其中所述特权等级包括两部分特权等

级。

[0184]

实例64包含实例63所述的高速缓存系统,其中所述位字段包含用于存储所述特权等级的2位。

[0185]

实例65包含实例61所述的高速缓存系统,其中所述第二子高速缓存包含特权合并表,所述特权合并表指示不同特权等级如何被合并。

[0186]

实例66包含实例65所述的高速缓存系统,其中所述特权合并表经预定义。

[0187]

实例67包含实例61所述的高速缓存系统,其中合并所述第一特权等级与所述第二特权等级包括选择较低特权等级。

[0188]

实例68包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将所述第一特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

[0189]

实例69包含实例67所述的方法,其中所述特权等级包括两部分特权等级。

[0190]

实例70包含实例69所述的方法,其中所述第二子高速缓存包含用于存储所述特权等级的位字段中的2位。

[0191]

实例71包含实例68所述的方法,其中所述合并是基于指示不同特权等级如何被合并的特权合并表。

[0192]

实例72包含实例71所述的方法,其中所述特权合并表经预定义。

[0193]

实例73包含实例68所述的方法,其中合并所述第一特权等级与所述第二特权等级包括选择较低特权等级。

[0194]

实例74包含一种装置,其包括:处理器;第一子高速缓存;及第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令,所述第二子高速缓存包含:特权位,其经配置以存储所述第二子高速缓存的对应高速缓存线与特权等级相关联的指示,且其中所述第二子高速缓存进一步经配置以:接收用于存储器地址的第一写入存储器命令,所述第一写入存储器命令与第一特权等级相关联;将与所述第一写入存储器命令相关联的第一数据存储于所述第二子高速缓存的高速缓存线中;将与所述高速缓存线相关联的所述特权等级存储于所述第二子高速缓存中;接收用于所述高速缓存线的第二写入存储器命令,所述第二写入存储器命令与第二特权等级相关联;合并所述第一特权等级与所述第二特权等级;存储所述经合并特权等级;及用所述高速缓存线输出所述经合并特权等级。

[0195]

实例75包含实例74所述的装置,其中特权等级信息经存储于跟踪所述第二子高速缓存数据中的条目的修改、独占、共享及无效(mesi)状态的存储器中的位字段中。

[0196]

实例76包含实例75所述的装置,其中所述特权等级包括两部分特权等级。

[0197]

实例77包含实例76所述的装置,其中所述位字段包含用于存储所述特权等级的2位。

[0198]

实例78包含实例75所述的装置,其中所述第二子高速缓存包含特权合并表,所述特权合并表指示不同特权等级如何被合并。

[0199]

实例79包含实例78所述的装置,其中所述特权合并表经预定义。

[0200]

实例80包含实例75所述的装置,其中合并所述第一特权等级与所述第二特权等级包括选择较低特权等级。

[0201]

实例81包含一种高速缓存系统,其包括第一子高速缓存;及与所述第一子高速缓存并行耦合的第二子高速缓存;其中所述第二子高速缓存包含线类型位,其经配置以存储所述第二子高速缓存的对应线经配置以存储写入未命中数据的指示。

[0202]

实例82包含实例81所述的高速缓存系统,其中所述第二子高速缓存进一步包括标签随机存取存储器(ram),其经配置以存储与所述所存储写入未命中数据相关联的存储器地址。

[0203]

实例83包含实例81所述的高速缓存系统,其中所述第二子高速缓存进一步包括字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑。

[0204]

实例84包含实例83所述的高速缓存系统,其中所述字节启用存储器包含与所述第二子高速缓存的每一高速缓存线对应的存储器位置。

[0205]

实例85包含实例81所述的高速缓存系统,其中所述所存储指示指示所述第二子高速缓存的所述对应高速缓存线是正存储写入未命中条目还是高速缓存条目。

[0206]

实例86包含实例81所述的高速缓存系统,其中所述线类型位经存储于跟踪所述第二子高速缓存中的条目的修改、独占、共享及无效(mesi)状态的存储器中。

[0207]

实例87包含实例81所述的高速缓存系统,其中所述第一子高速缓存是n路组关联高速缓存且其中所述第二子高速缓存是完全关联高速缓存。

[0208]

实例88包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中,所述第二子高速缓存与所述第一子高速缓存并行耦合;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;及将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中。

[0209]

实例89包含实例88所述的方法,其进一步包括将与所述所存储写入未命中数据相关联的存储器地址存储于标签随机存取存储器(ram)中。

[0210]

实例90包含实例88所述的方法,其进一步包括将与所述所存储写入未命中数据相关联的字节启用逻辑存储于字节启用存储器中。

[0211]

实例91包含实例88所述的方法,其中所述线类型位经存储于跟踪所述第二子高速缓存中的条目的修改、独占、共享及无效(mesi)状态的存储器中。

[0212]

实例92包含实例88所述的方法,其进一步包括:从所述第二子高速缓存的线逐出高速缓存条目,且其中存储与所述写入存储器请求相关联的数据包括将所述数据存储于所述线中。

[0213]

实例93包含实例88所述的方法,其中所述所存储指示指示所述第二子高速缓存的所述对应高速缓存线是正存储写入未命中条目还是高速缓存条目。

[0214]

实例94.一种装置,其包括:处理器:第一子高速缓存;及与所述第一子高速缓存并行耦合的第二子高速缓存;其中所述第二子高速缓存包含线类型位,其经配置以存储所述第二子高速缓存的对应线经配置以存储写入未命中数据的指示。

[0215]

实例95包含实例94所述的装置,其中所述第二子高速缓存进一步包括标签随机存取存储器(ram),其经配置以存储与所述所存储写入未命中数据相关联的存储器地址。

[0216]

实例96包含实例94所述的装置,其中所述第二子高速缓存进一步包括字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑。

[0217]

实例97包含实例96所述的装置,其中所述字节启用存储器包含与所述第二子高速缓存的每一高速缓存线对应的存储器位置。

[0218]

实例98包含实例94所述的装置,其中所述所存储指示指示所述第二子高速缓存的所述对应高速缓存线是正存储写入未命中条目还是高速缓存条目。

[0219]

实例99包含实例94所述的装置,其中所述线类型位经存储于跟踪所述第二子高速缓存中的条目的修改、独占、共享及无效(mesi)状态的存储器中。

[0220]

实例100包含权利要求94所述的装置,其中所述第一子高速缓存是n路组关联高速缓存且其中所述第二子高速缓存是完全关联高速缓存。

[0221]

实例101包含一种高速缓存系统,其包括:第一子高速缓存;及与所述第一子高速缓存并行的第二子高速缓存,其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述高速缓存线已被完全写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0222]

实例102包含实例101所述的高速缓存系统,其中所述逐出控制器进一步经配置以基于所述高速缓存线的一半已被写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0223]

实例103包含实例102所述的高速缓存系统,其中所述逐出控制器经配置以基于所述高速缓存线的一半已被写入的所述指示确定在逐出所述高速缓存线之前存储写入未命中数据的所述第二子高速缓存中无高速缓存线被完全写入。

[0224]

实例104包含实例102所述的高速缓存系统,其中所述第二子高速缓存进一步包括字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑,且其中所述字节启用存储器包含存储所述高速缓存线已被完全写入的所述指示的第一位。

[0225]

实例105包含实例104所述的高速缓存系统,其中所述字节启用存储器包含存储所述高速缓存线的一半已被写入的所述指示的第二位。

[0226]

实例106包含实例105所述的高速缓存系统,其中所述第一及第二位基于与所述所存储写入未命中数据相关联的所述字节启用逻辑确定。

[0227]

实例107包含实例106所述的高速缓存系统,其中所述第一及第二位在写入未命中数据每一次被存储于所述第二子高速缓存中时基于所述字节启用逻辑确定。

[0228]

实例108包含一种用于高速缓存数据的方法,其包括:由高速缓存系统接收对存储器地址的写入存储器请求;由所述高速缓存系统的第一子高速缓存确定所述存储器地址未

被高速缓存于所述第一子高速缓存中;由所述高速缓存系统的第二子高速缓存确定所述存储器地址未被高速缓存于所述第二子高速缓存中;将与所述写入存储器请求相关联的数据存储于所述第二子高速缓存中;将所述所存储数据对应于写入未命中的指示存储于所述第二子高速缓存的线类型位中;及基于所述高速缓存线已被完全写入的指示逐出存储所述写入未命中的所述第二子高速缓存的高速缓存线。

[0229]

实例109包含实例108所述的方法,其进一步包括基于所述高速缓存线的一半已被写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0230]

实例110包含实例109所述的方法,其进一步包括基于所述高速缓存线的一半已被写入的所述指示确定在逐出所述高速缓存线之前存储写入未命中数据的所述第二子高速缓存中无高速缓存线被完全写入。

[0231]

实例111包含实例109所述的方法,其进一步包括存储指示所述高速缓存线已被完全写入于所述第二子高速缓存的字节启用存储器中的第一位。

[0232]

实例112包含实例111所述的方法,其进一步包括存储指示所述高速缓存线一半被写入于所述第二子高速缓存的所述字节启用存储器中的第二位。

[0233]

实例113包含实例112所述的方法,其中所述第一及第二位基于与所述所存储写入未命中数据相关联的所述字节启用逻辑确定。

[0234]

实例114包含实例113所述的方法,其中所述第一及第二位在写入未命中数据每一次被存储于所述第二子高速缓存中时基于所述字节启用逻辑确定。

[0235]

实例115包含一种装置,其包括:处理器;第一子高速缓存;及与所述第一子高速缓存并行的第二子高速缓存;其中所述第二子高速缓存包含:一组高速缓存线;线类型位,其经配置以存储所述一组高速缓存线中的对应高速缓存线经配置以存储写入未命中数据的指示;及逐出控制器,其经配置以基于所述高速缓存线已被完全写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0236]

实例116包含实例115所述的装置,其中所述逐出控制器进一步经配置以基于所述高速缓存线的一半已被写入的指示逐出存储写入未命中数据的所述第二子高速缓存的高速缓存线。

[0237]

实例117包含实例116所述的装置,其中所述逐出控制器经配置以基于所述高速缓存线的一半已被写入的所述指示确定在逐出所述高速缓存线之前存储写入未命中数据的所述第二子高速缓存中无高速缓存线被完全写入。

[0238]

实例118包含实例118所述的装置,其中所述第二子高速缓存进一步包括字节启用存储器,其经配置以存储与所述所存储写入未命中数据相关联的字节启用逻辑,且其中所述字节启用存储器包含存储所述高速缓存线已被完全写入的所述指示的第一位。

[0239]

实例119包含实例118所述的装置,其中所述字节启用存储器包含存储所述高速缓存线的一半已被写入的所述指示的第二位。

[0240]

实例120包含实例119所述的装置,其中所述第一及第二位基于与所述所存储写入未命中数据相关联的所述字节启用逻辑确定。

[0241]

实例121包含一种高速缓存系统,其包括:第一子高速缓存;第二子高速缓存,其与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;及高速缓存控制器,其经配置以:

接收两个或更多个高速缓存命令;确定在所述接收到的两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到所述第一子高速缓存及所述第二子高速缓存。

[0242]

实例122包含实例121所述的高速缓存系统,其中所述高速缓存命令是读取命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的存储器地址确定所述存储器地址未被高速缓存于所述第一子高速缓存中;基于所述存储器地址确定所述存储器地址作为写入存储器命令被存储于所述第二子高速缓存中;及暂停所述读取命令直到所述写入存储器命令从所述第二子高速缓存清空。

[0243]

实例123包含实例121所述的高速缓存系统,其中所述高速缓存控制器进一步经配置以并行接收两个或更多个高速缓存命令。

[0244]

实例124包含实例123所述的高速缓存系统,其中所述两个或更多个高速缓存命令包含读取命令及写入命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;接收与所述读取命令相关联的所述第二子高速缓存中的第二高速缓存位置;基于所述写入命令的第二存储器地址确定所述第二存储器地址作为写入存储器命令被存储于所述第二子高速缓存中的所述第二高速缓存位置处;接收与所述写入命令相关联的所述第二子高速缓存中的第三高速缓存位置;及将经高速缓存存储器项从所述第一子高速缓存中的所述第一高速缓存位置逐出到所述第二子高速缓存中的所述第三高速缓存位置。

[0245]

实例125包含实例123所述的高速缓存系统,其中所述两个或更多个高速缓存命令包含读取命令及写入命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;基于所述写入命令的第二存储器地址确定所述第二存储器地址被存储于所述第一子高速缓存中的所述第一位置处;暂停所述读取命令;执行所述写入命令;将所述经执行写入命令逐出到所述第二子高速缓存;及在所述逐出之后恢复所述读取命令。

[0246]

实例126包含实例123所述的高速缓存系统,其中所述两个或更多个高速缓存命令包含第一写入命令及第二写入命令,且其中所述高速缓存控制器进一步经配置以:确定所述第一写入命令的第一存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第二写入命令的第二存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第一存储器地址与所述第二存储器地址匹配;合并所述第一写入命令与所述第二写入命令;及将所述经合并命令存储到所述第二子高速缓存。

[0247]

实例127包含实例123所述的高速缓存系统,其中所述两个或更多个高速缓存命令包含读取命令及写入命令,且其中所述高速缓存控制器进一步经配置以:确定所述读取命令的第一存储器地址未被高速缓存于所述第一子高速缓存中;确定所述写入命令的第二存储器地址被高速缓存于所述第一子高速缓存中;确定所述第一存储器地址与所述第二存储器地址匹配;暂停所述写入命令直到所述读取命令完成;及恢复所述写入命令。

[0248]

实例128包含一种用于高速缓存数据的方法,其包括:接收两个或更多个高速缓存命令;确定在所述两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更

多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到第一子高速缓存及第二子高速缓存,其中所述第二子高速缓存经配置以与所述第一子高速缓存并行地存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令。

[0249]

实例129包含权利要求8所述的方法,其中所述高速缓存命令是读取命令且所述方法进一步包括:基于所述读取命令的存储器地址确定所述存储器地址未被高速缓存于所述第一子高速缓存中;基于所述存储器地址确定所述存储器地址作为写入存储器命令被存储于所述第二子高速缓存中;及暂停所述读取命令直到所述写入存储器命令从所述第二子高速缓存清空。

[0250]

实例130包含实例128所述的方法,其中所述两个或更多个高速缓存命令被并行接收。

[0251]

实例131包含实例130所述的方法,其中所述两个或更多个高速缓存命令包含读取命令及写入命令且所述方法进一步包括:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;接收与所述读取命令相关联的所述第二子高速缓存中的第二高速缓存位置;基于所述写入命令的第二存储器地址确定所述第二存储器地址作为写入存储器命令被存储于所述第二子高速缓存中的所述第二高速缓存位置处;接收与所述写入命令相关联的所述第二子高速缓存中的第三高速缓存位置;将经高速缓存存储器项从所述第一子高速缓存中的所述第一高速缓存位置逐出到所述第二子高速缓存中的所述第三高速缓存位置。

[0252]

实例132包含实例130所述的方法,其中所述两个或更多个高速缓存命令包含读取命令及写入命令且所述方法进一步包括:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;基于所述写入命令的第二存储器地址确定所述第二存储器地址被存储于所述第一子高速缓存中的所述第一位置处;暂停所述读取命令;执行所述写入命令;将所述经执行写入命令逐出到所述第二子高速缓存;及在所述逐出之后恢复所述读取命令。

[0253]

实例133包含实例130所述的方法,其中所述两个或更多个高速缓存命令包含第一写入命令及第二写入命令,且其中所述高速缓存控制器进一步经配置以:确定所述第一写入命令的第一存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第二写入命令的第二存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第一存储器地址与所述第二存储器地址匹配;合并所述第一写入命令与所述第二写入命令;及将所述经合并命令存储到所述第二子高速缓存。

[0254]

实例134包含实例130所述的方法,其中所述两个或更多个高速缓存命令包含读取命令及写入命令且所述方法进一步包括:确定所述读取命令的第一存储器地址未被高速缓存于所述第一子高速缓存中;确定所述写入命令的第二存储器地址被高速缓存于所述第一子高速缓存中;确定所述第一存储器地址与所述第二存储器地址匹配;暂停所述写入命令直到所述读取命令完成;及恢复所述写入命令。

[0255]

实例135包含一种装置,其包括:处理器;第一子高速缓存;及第二子高速缓存,其

与所述第一子高速缓存并行耦合用于存储从所述第一子高速缓存逐出的高速缓存数据及未被高速缓存于所述第一子高速缓存中的写入存储器命令;及高速缓存控制器,其经配置以:接收两个或更多个高速缓存命令;确定在所述接收到的两个或更多个高速缓存命令之间存在冲突;确定所述接收到的两个或更多个高速缓存命令之间的冲突解决;及将所述两个或更多个高速缓存命令发送到所述第一子高速缓存及所述第二子高速缓存。

[0256]

实例136包含实例135所述的装置,其中所述高速缓存命令是读取命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的存储器地址确定所述存储器地址未被高速缓存于所述第一子高速缓存中;基于所述存储器地址确定所述存储器地址作为写入存储器命令被存储于所述第二子高速缓存中;及暂停所述读取命令直到所述写入存储器命令从所述第二子高速缓存清空。

[0257]

实例137包含实例135所述的装置,其中所述高速缓存控制器进一步经配置以并行接收两个或更多个高速缓存命令。

[0258]

实例138包含实例137所述的装置,其中所述两个或更多个高速缓存命令包含读取命令及写入命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;接收与所述读取命令相关联的所述第二子高速缓存中的第二高速缓存位置;基于所述写入命令的第二存储器地址确定所述第二存储器地址作为写入存储器命令被存储于所述第二子高速缓存中的所述第二高速缓存位置处;接收与所述写入命令相关联的所述第二子高速缓存中的第三高速缓存位置;及将经高速缓存存储器项从所述第一子高速缓存中的所述第一高速缓存位置逐出到所述第二子高速缓存中的所述第三高速缓存位置。

[0259]

实例139包含实例137所述的装置,其中所述两个或更多个高速缓存命令包含读取命令及写入命令,且其中所述高速缓存控制器进一步经配置以:基于所述读取命令的第一存储器地址确定所述第一子高速缓存中的第一高速缓存位置;确定所述第一存储器地址未被高速缓存于所述第一子高速缓存中的所述第一高速缓存位置处;基于所述写入命令的第二存储器地址确定所述第二存储器地址被存储于所述第一子高速缓存中的所述第一位置处;暂停所述读取命令;执行所述写入命令;将所述经执行写入命令逐出到所述第二子高速缓存;及在所述逐出之后恢复所述读取命令。

[0260]

实例140包含实例137所述的装置,其中所述两个或更多个高速缓存命令包含第一写入命令及第二写入命令,且其中所述高速缓存控制器进一步经配置以:确定所述第一写入命令的第一存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第二写入命令的第二存储器地址未被高速缓存于所述第一子高速缓存中;确定所述第一存储器地址与所述第二存储器地址匹配;合并所述第一写入命令与所述第二写入命令;及将所述经合并命令存储到所述第二子高速缓存。

[0261]

贯穿说明书使用术语“耦合”。术语可涵盖实现与本描述的描述一致的功能关系的连接、通信或信号路径。举例来说,如果装置a产生信号以控制装置b执行动作,那么在第一实例中,装置a经耦合到装置b,或在第二实例中,如果中介组件c基本上未更改装置a与装置b之间的功能关系,那么装置a通过中介组件c耦合到装置b,使得装置b由装置a经由装置a产生的控制信号控制。

[0262]

在所描述实施例中,修改是可能的,且在权利要求书的范围内,其它实施例是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1