在超导电路设计中确定关键定时路径的制作方法

在超导电路设计中确定关键定时路径

背景技术:

1.在诸如数字处理器的电子设备中使用的基于半导体的集成电路包括基于互补金属氧化物半导体(cmos)技术的数字电路。然而,cmos技术在器件尺寸方面正达到其极限。另外,基于cmos技术的数字电路在高时钟速度的功耗越来越成为高性能数字电路和系统的限制因素。作为示例,数据中心中的服务器消耗越来越大量的功率。即使在cmos电路处于非活动状态时,功率消耗也部分是能量耗散造成的功率损耗的结果。这是因为,即使当这种电路处于非活动状态并且不消耗任何动态功率时,由于需要维持cmos晶体管的状态,它们仍会消耗功率。

2.基于cmos技术使用处理器和有关组件的另一种方法是使用基于超导逻辑的组件和设备。基于超导逻辑的电路也可以被用来处理诸如量子位的量子信息。许多超导逻辑电路包括约瑟夫森结(josephson junction),其可以使用高速时钟或微波信号而被控制。这样的电路可以包括有源传输元件,有源传输元件会使正确定时(timing)设计的创建复杂化。

技术实现要素:

3.在一个方面,本公开涉及一种由处理器实现的用于在超导电路设计中确定关键定时路径的方法,其中超导电路设计包括至少一个逻辑门,该至少一个逻辑门包括至少一个约瑟夫森结,并且其中至少一个逻辑门具有被指派的第一相位,该第一相位与用于对至少一个逻辑门进行计时(clocking)的时钟信号相关联。该方法可以包括:提供关于至少一个逻辑门的多个源端子的定时信息,该多个源端子与至少一个逻辑门的第一汇端子耦合。该方法还可以包括:使用处理器,基于被指派给至少一个逻辑门的第一相位,鉴于定时信息,确定在预定的到达时间范围内第一汇端子的是否由单通量量子(sfq)脉冲可抵达。

4.在另一方面,本公开涉及一种由处理器实现的用于在超导电路设计中确定关键定时路径的方法,其中超导电路设计包括多个逻辑门,并且其中多个逻辑门中的每个逻辑门包括至少一个约瑟夫森结。该方法可以包括提供关于与多个逻辑门相关联的多个源端子的定时信息。该方法还可以包括接收从与目标逻辑门相关联的多个汇端子之中对第一汇端子的选择,该目标逻辑门是从多个逻辑门中被选择的。该方法还可以包括接收对目标逻辑门的相位的指派。该方法还可以包括针对多个汇端子中的每个汇端子:使用处理器,确定在预定的到达时间范围内多个汇端子中的每个汇端子是否由相应的单通量量子(sfq)脉冲可抵达,以及如果在预定的到达时间范围内第一汇端子不可抵达,则在与目标逻辑门相关联的源端子与被确定在预定的到达时间范围内不可抵达的第一汇端子之间插入约瑟夫森传输线(jtl),以及在确定第一汇端子在jtl的插入之后、在预定的到达时间范围内可抵达后,从被认为与关键定时路径相关联的多个汇端子之中移除第一汇端子。

5.在又一方面,本公开涉及一种被配置为在超导电路设计中确定关键定时路径的系统,其中超导电路设计包括至少一个逻辑门,至少一个逻辑门包括至少一个约瑟夫森结,并且其中至少一个逻辑门具有被指派的第一相位,该第一相位与用于对至少一个逻辑门进行

计时的时钟信号相关联。该系统可以包括第一子系统,第一子系统被配置为提供关于至少一个逻辑门的多个源端子的定时信息,该多个源端子与至少一个逻辑门的第一汇端子耦合。该系统还可以包括第二子系统,第二子系统包括处理器,被配置为:基于被指派给至少一个逻辑门的第一相位,鉴于定时信息,确定在预定的到达时间范围内第一汇端子是否由单通量量子(sfq)脉冲可抵达。

6.在另一方面,本公开涉及一种由处理器实现的用于在超导电路设计中确定定时路径和调和拓扑的方法,其中超导电路设计包括第一定时路径,第一定时路径包括第一组定时引脚,并且其中第一组定时引脚的第一子集与包括第一定时端点和第二定时端点的第一定时约束群组相关联。该方法可以包括使用处理器来处理第一定时约束群组,以将第一合法开始时间指派给第一定时端点以及将第二合法开始时间指派给第二定时端点。该方法还可以包括在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在第一定时端点之前或在第二定时端点之后。该方法还可以包括解决由于在定时路径上插入第一影子元件而引起的对第一合法开始时间或第二合法开始时间的任何改变。

7.在又一方面,本公开涉及由处理器实现的用于在超导电路设计中确定定时路径和调和拓扑的方法,其中超导电路设计包括第一定时路径,第一定时路径包括与第一电路组件相关联的第一定时端点和与第二电路组件相关联的第二定时端点,并且其中第一电路组件和第二电路组件中的每个电路组件都包括约瑟夫森结,并且其中第一电路组件被指派第一相位并且第二电路组件被指派第二相位。该方法可以包括使用处理器来确定定时路径上的第一定时端点的第一合法开始时间、以及确定定时路径上的第二定时端点的第二合法开始时间。该方法还可以包括在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在定时路径上在第一电路组件之前。该方法还可以包括在定时路径上插入第二影子元件,第二影子元件表示第二物理连接的组件,其中第二影子元件在定时路径上在第二电路组件之后。该方法还可以包括解决由于在定时路径上插入第一影子元件和第二影子元件而引起的对第一合法开始时间和第二合法开始时间的任何改变。

8.在又一方面,本公开涉及一种被配置为在超导电路设计中确定定时路径和调和拓扑的系统,其中超导电路设计包括第一定时路径,第一定时路径包括与第一电路组件相关联的第一定时端点以及与第二电路组件相关联的第二定时端点,并且其中第一电路组件和第二电路组件中的每个电路元件都包括约瑟夫森结,并且其中第一电路组件被指派第一相位并且第二电路组件被指派第二相位。该系统可以包括处理器和包括指令的存储器。该指令可以被配置为:(1)确定定时路径上的第一定时端点的第一合法开始时间以及确定定时路径上的第二定时端点的第二合法开始时间,(2)在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在定时路径上在第一电路组件之前,(3)在定时路径上插入第二影子元件,第二影子元件表示第二物理连接的组件,其中第二影子元件在定时路径上在第二电路组件之后,并且(4)解决由于在定时路径上插入第一影子元件和第二影子元件而引起的对第一合法开始时间和第二合法开始时间的任何改变。

9.本发明内容被提供来以简化的形式介绍在以下具体实施方式中进一步描述的一系列概念。本发明内容不旨在识别要求保护的主题的关键特征或必要特征,也不旨在被用于限制要求保护的主题的范围。

附图说明

10.本公开以示例的方式图示并且不受附图限制,其中相同的附图标记指示相似的元件。附图中的元件是为了简单和清楚而图示的并且不一定按比例绘制。

11.图1是根据一个示例的系统环境的框图;

12.图2是根据一个示例的对象模型的框图;

13.图3示出根据一个示例的包括定时组件及其与对象模型的关系的图解;

14.图4示出根据一个示例的计算平台,该计算平台可以被用来实现与图1的系统环境相关联的功能;

15.图5示出根据一个示例的正在被定时的示例逻辑电路的示意图;

16.图6是根据一个示例的方法的流程图600,该方法用于确定超导电路设计中的定时路径的有效性;

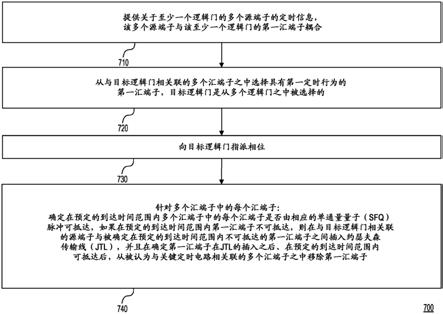

17.图7是根据另一示例的方法的流程图700,该方法用于确定关键定时路径以及用于在超导电路设计中求解该关键定时路径;

18.图8示出表示定时约束群组(tcg)的示例的电路的图解,该定时约束群组包括作为约束群组一部分的定时引脚;

19.图9示出根据一个示例的包括与作为超导电路设计的一部分在图8的定时约束群组(tcg)之前或之后的tcg对应的影子组件的图解;

20.图10是示出向图8的tcg添加有源传输元件的图解;

21.图11是示出针对其他定时约束群组所填充的定时信息和相位指派以及额外的jtl(根据需要)的图解;

22.图12是示出根据一个示例的针对图8的tcg的头部(head)的定时变化的图解;

23.图13是示出根据一个示例的图8的tcg的其余组件的定时变化的图解,该定时变化是求解步骤的结果;

24.图14是示出根据一个示例的其他tcg的定时变化的图解。

25.图15是根据一个示例的方法的流程图,该方法用于在超导电路设计中确定定时路径和调和拓扑;以及

26.图16是根据一个示例的方法的流程图,该方法用于在超导电路设计中确定定时路径以及调和拓扑。

具体实施方式

27.本公开中描述的示例涉及用于确定用于超导电路设计的关键定时路径的系统和方法。某些其他示例涉及用于超导电路设计中确定定时路径以及调和拓扑的系统和方法。超导电路可以使用约瑟夫森结来实现与电路相关联的功能性。示例性的约瑟夫森结可以包括经由阻碍电流的区域耦合的两个超导体。阻碍电流的区域可以是超导体本身、金属区域、或薄绝缘势垒的物理变窄。例如,超导体-绝缘体-超导体(sis)类型的约瑟夫森结可以作为超导电路的一部分被实现。作为示例,超导体是可以在没有电场的情况下输送直流电(dc)的材料。超导体具有临界温度(tc),低于该临界温度时,它们的电阻为零。一种这样的超导体铌具有9.3开尔文度的临界温度(tc)。在低于tc的温度,铌是超导的;然而,在高于tc的温度,它表现为具有电阻的普通金属。因此,在sis类型的约瑟夫森结中,超导体中可以是铌超

导体,而绝缘体可以是al2o3势垒。在sis类型的结中,超导电子由量子力学波函数描述。两个超导体之间的超导电子波函数的相位随时间变化的相位差与两个超导体之间的电位差对应。

28.根据需要,包括传输线的各种超导电路可以通过由电感器或其他组件耦合多个约瑟夫森结而形成。微波脉冲可以在至少一个时钟的控制下经由这些传输线行进。微波脉冲可以是正或负,或者是其组合。微波脉冲可以具有高达10ghz或更高的频率。时钟也可以具有高达10ghz或更高的频率。

29.在一个示例中,电路的逻辑可以被称为行波流水线逻辑(wave pipelined logic)并且数字数据可以使用一对正负sfq脉冲被编码。作为示例,逻辑1(one)位可以被编码为在正弦时钟的正相位和负相位中所生成的一对sfq脉冲。逻辑0(zero)位可以通过在时钟周期期间不存在正/负脉冲对而被编码。正sfq脉冲可以在时钟的正部分期间到达,而负脉冲可以在时钟的负部分期间到达。正sfq脉冲可以在时钟的正部分之前到达,但它在正时钟到达之前不会被传播。类似地,负sfq脉冲可以在时钟的负部分之前到达,但它不会在负脉冲到达之前被传播。

30.某些示例还涉及基于相位模式逻辑的超导电路的定时设计。这些超导电路还可以使用基于相位模式逻辑(pml)的设备。在基于pml的设备中,逻辑“1”可以被编码为相位高,而逻辑“0”可以被编码为相位低。相位高与相位低之间的转变可以由单通量量子(sfq)脉冲事件触发。在基于相位模式逻辑的超导电路中,数字值可以被编码为约瑟夫森结(jj)相位。高相位可以指示逻辑“1”,并且低相位可以指示逻辑“0”。与行波流水线逻辑编码不同,这些值在各时钟周期中保持不变,因为不需要负脉冲来重置jj相位。作为示例,如果使用具有四个相位的ac时钟为相位模式逻辑超导电路供电,则相位模式逻辑电路的输出可以在ac时钟的所有四个相位中都保持不变。在一个示例中,四相时钟可以从两个交流时钟源被导出。时钟的四个相位可以为单通量量子(sfq)脉冲提供方向性。因此,作为示例,对于四相时钟,正脉冲可以从一个相位到下一个相位跨越时钟的前沿,并且在一个周期的延迟后到达输出,并且负脉冲可以跟随半个周期的分离。也可以使用其他类型的计时布置,包括利用多于四个的相位的计时。

31.超导电路的构建块可以包括各种类型的逻辑门。示例逻辑门包括与门、或门、逻辑a与非b(aanb)门、以及逻辑与或(andor)门。a与非b门可以具有两个输入和一个输出(q)。除非输入脉冲b先出现,否则输入脉冲a可以传播到输出q。与或门可以有两个输入和两个输出(q1和q2)。第一输入脉冲,输入脉冲a或输入脉冲b去往输出q1,并且第二输入脉冲去往输出q2。这些门的逻辑行为可以基于前面提到的互易数据编码或基于前面提到的基于相位模式逻辑的数据编码。

32.图1是根据一个示例的系统环境100的框图。系统环境100示出示例块,用于执行与超导电路的定时确定和相位指派有关的方法和系统。系统环境100可以包括用户接口(ui)块110、设计块120、定时和相位块(tpb)130、对象模型150、组件类型系统160、以及定时库170。ui块110可以包括用于启用用户接口的代码,该接口允许设计者或其他用户与系统交互。例如,ui块110可以包括允许用户进行以下动作的代码和数据结构:确定超导电路中的关键路径,指派相位,以及修改超导电路的定时有关的设计。设计块120可以包括至少一个对象,该对象可以指定与各种参数有关的设计定义,各种参数与定时有关的设计相关联。例

如,设计块120可以是指定与定时设计相关联的频率的对象。作为另一示例,设计块120可以指定哪个定时库应该与超导电路或与集成电路有关的一组超导电路一起使用。

33.继续参考图1,tpb 130可以包括定时引擎132、定时结果134、电路分析器136和延迟确定138。定时引擎132可以基于定时数据来计算脉冲传播和定时约束。在这个示例中,定时引擎132的输出可以是针对每个方向上的定时引脚(也被称为定时端子)之间每个弧的一组最小保持时间和最大建立时间。该信息可以作为定时结果134的一部分被存储。电路分析器136可以确定正被定时的电路的拓扑以及存储该拓扑以供延迟确定138处理。延迟确定138可以处理包括定时路径中的门的拓扑,以确定定时引脚之间的延迟。如此被确定的延迟可以被存储在查找表或另一数据结构中。定时引擎132可以从查找表或另一数据结构中查找引脚之间的各个延迟以及对结果求和。另外,如稍后所述,定时引擎132还可以提供附加信息,包括与关键定时路径、拓扑、具有裕量(slack)的路径、以及所添加的约瑟夫森传输线(jtl)元件的数目有关的数据。在这个示例中,定时引擎132可以被实现为一组可调用方法,其允许进行与定时有关的计算以及生成输出以用于电路设计。定时引擎132的高级方面可以包括下表1中所示的特征:

[0034][0035]

表1

[0036]

仍然参考图1,对象模型150可以包括数据结构和代码,该数据结构和代码用于支持用于抽象化需要定时设计的实体(例如,逻辑门或电路)的与定时有关的定义。下表2列出了数据结构的示例及其示例说明。

[0037]

[0038][0039]

表2

[0040]

继续参考图1,组件类型系统(cts)160可以被用来存储与相关定时库(例如,定时库170)有关的数据。在这个示例中,添加或改变与定时库相关联的数据将需要一次性重新初始化cts 160。定时库170可以包括关于频率、ac幅度、和关于与设计相关联的逻辑门类型的其他参数的信息。例如,逻辑门可以与行波流水线逻辑门或相位模式逻辑门对应。在这个示例中,定时库可以包括逻辑门的json和verilog定义。这些定义可以包括与时钟一致的上升/下降表和信号类型(归零/不归零等)。在一个示例中,这些定义可以是针对门的verilog中的属性。尽管图1示出作为系统环境100的一部分被包括的某些块,但是可以有更多或更少的块。作为示例,系统环境100可以包括报告块,该报告块可以被用来生成关于定时设计的报告。作为另一示例,系统环境100可以包括附加定时库,该附加定时库可以包括类似的信息,这些类似的信息可以被用来支持被构建为在不同温度运行的超导电路或使用不同制造工艺构建的超导电路。其他定时库可以仅被用于测试目的。

[0041]

图2示出根据一个示例的对象模型200的框图。对象模型200是图1的对象模型150的示例。对象模型200可以包括定时图220。在对象模型的这个示例中,示出了定时图(例如,定时图220),但是没有示出定时组件。定时组件以及它们与对象模型的关系关于图3被描述。在一个示例中,定时图220可以被实现为表3中所示的数据结构。

[0042][0043]

表3

[0044]

继续参考图2,定时约束群组(timingconstraintgroup)210可以包括一组连接的定时约束(timingconstraint)(例如,定时约束212、定时约束214和定时约束216)。与定时约束对应的数据结构所包含的示例信息可以包括:begintimingpin(开始定时引脚)、endtimingpin(结束定时引脚)、hold(保持)和setup(建立)。因此,在这个示例中,数据结构可以包括关于定时约束开始处的定时引脚(例如,与逻辑门相关联的端子)和定时约束结束处的定时引脚的信息。数据结构还可以包括关于保持和建立时间的信息。表4示出在用于实现定时约束群组210的数据结构中所包括的信息的一个示例。

[0045][0046]

表4

[0047]

仍然参考图2,定时约束群组210可以包括与定时约束有关的信息的集合,该集合包括定时约束212、定时约束214和定时约束216。这些定时约束中的每个定时约束可以使用数据结构来实现,并且每个可以指向与定时引脚有关的数据结构以指示该定时约束与该特定的定时引脚或该组定时引脚有关。下表5示出在数据结构定时约束中包括的一组示例信息。

[0048][0049][0050]

表5

[0051]

每个定时引脚(或定时端子)也可以具有对应的数据结构,该数据结构可以包括关于诸如额外jtl(extrajtl)的项的信息和关于它是什么引脚(或端子)类型的信息。例如,每个引脚可以是用于门的源引脚或汇引脚。图2中所示的对象模型200包括定时引脚:定时引脚221、222、223、224、225、226、227、228和229,它们中的每个定时引脚都可以具有从timingpinbase(定时引脚基础)数据结构导出的对应数据结构。在一个示例中,timingpinbase数据结构可以包括下表6中所示的信息。

[0052][0053]

表6

[0054]

继续参考图2,表7示出在与源引脚对应的数据结构中包含的信息。在这个示例表中,弧(arc)指的是每个引脚的输入时间与输出时间之间的定时关系。

[0055][0056][0057]

表7

[0058]

如上所示,表8是在与汇引脚对应的数据结构中包含的信息的示例。

[0059][0060]

表8

[0061]

图3示出根据另一示例的另一定时对象模型300的框图。对象模型300是图1的对象模型150的示例。在这个示例中,定时图和定时组件都被示出。在这个示例中,与前面关于图2所描述的数据结构类似的数据结构被用来对与对象模型相关联的引脚和定时约束进行建模,该对象模型与包括有源传输元件(诸如jtl)的电路设计对应。因此,定时图(timinggraph)310可以以与前面关于表3所描述的类似的方式和类似的信息来实现。类似

地,可以用前面关于表4所描述的信息类似的信息来实现定时约束群组320。在这个示例中,定时约束群组320可以指向定时约束对(timingconstraintpair)330。在一个示例中,在与定时约束对330对应的数据结构中所包括的信息在下表9中被示出。

[0062][0063]

表9

[0064]

继续参考图3,对象模型300可以包括定时组件,包括:定时组件340、350、360和370可以表示要被定时的组件,并且可以被用来在调和步骤中找到针对不同定时图中的物理连接的组件的相关定时约束群组。这些图利用定时路径上所有物理连接的组件的定时组件被构建。每个图的映射可以包含该图拥有的所有定时组件。除了头部之外,定时路径上的所有组件都由其定时图拥有。头部归其前身的定时图所有。图3中所示的对象模型300包括定时引脚:定时引脚342、344、346、348、362、366和368,其中每个定时引脚都可以具有从timingpinbase导出的对应的数据结构,这在前面关于表6进行了描述。

[0065]

图4示出计算平台400,其可以被用来实现与图1的系统环境100相关联的功能。计算平台400可以包括(多个)处理器402、(多个)i/o组件404、存储器406、(多个)呈现组件408、(多个)传感器410、(多个)数据库412、(多个)联网接口414和(多个)i/o端口416,它们可以经由总线420互连。(多个)处理器402可以执行在存储器406中存储的指令或代码。这些指令可以与本公开中描述的各种算法对应。因此,这些算法可以使用编程语言来实现并被编译成进而可以被执行的可执行文件。(多个)i/o组件404可以包括诸如键盘、鼠标、语音识别处理器或触摸屏的组件。存储器406可以是非易失性存储装置或易失性存储装置(例如,闪存、dram、sram或其他类型的存储器)的任何组合。(多个)呈现组件408可以是诸如lcd、led的任何类型的显示器,或者其他类型的显示器,或者包括音频或触觉输出组件的其他类型的输出组件。(多个)传感器410可以包括音频传感器、光学传感器或其他类型的传感器。

[0066]

继续参考图4,(多个)数据库412可以被用来存储定时库和其他与定时有关的信息。另外,(多个)数据库412还可以存储用于生成与定时库有关的报告的数据。(多个)联网接口414可以包括通信接口,诸如以太网、蜂窝无线电、蓝牙无线电、uwb无线电、或者其他类型的无线或有线通信接口。(多个)i/o端口416可以允许计算平台400与总线420或(多个)其他i/o组件404通信。尽管图4将计算平台400示出为包括以某种方式布置和耦合的一定数目的组件,但是它也可以包括不同地布置和耦合的更少或附加的组件。另外,根据需要,与计算平台400相关联的功能性可以是分布式或组合的。此外,可能不需要计算平台400的所有方面来实现本文描述的各种方法。

[0067]

图5示出根据一个示例正被定时的示例逻辑电路500的示意图。示例逻辑电路500

可以包括与门510和几个jtl。与门510可以包括两个输入端子:ai和bi,以及输出端子:ao。jtl 512和514可以被耦合到输入端子ai,如图5中所示。jtl 516和jtl 518可以被耦合到输入端子bi,如图5中所示。jtl 520可以被耦合到输出jtl 516。虽然未在该图中示出,但是jtl 520可以被用来将逻辑电路500耦合到(多个)其他的逻辑电路。jtl 524可以被耦合到输出端子ao,如图5中所示。根据需要,附加的jtl可以被耦合;例如,jtl 526和jtl 528可以被耦合到jtl 524。jtl 526和jtl 528可以被用来将逻辑电路500耦合到(多个)其他的逻辑电路。如图5中所示,逻辑电路500中包括的每个jtl和逻辑门可以具有初始的相位指派。假设这个示例电路以四相时钟运行,使得相位指派包括0度、90度、180度和270度。也可以设计由包括更少或更多相位的时钟驱动的逻辑电路。单通量量子脉冲可以经由耦合到相应输入端子的jtl到达与门510的输入端子。在由与门510处理之后,表示逻辑与值的sfq脉冲可以经由输出端子被输出。为了确保逻辑电路500的正确操作,与被存储在存储器406中的算法对应的指令在由(多个)处理器402执行时可以帮助设计者设计逻辑电路510的定时方面和相位指派方面。示例算法如下表10所示。

[0068][0069]

表10

[0070]

可以针对设计中所包括的每个逻辑门(例如,逻辑电路500的逻辑门510)执行表10中所示的步骤。表10中示出的步骤与任何包含c个汇引脚的门g有关。第一步骤可以包括从

一组c个汇引脚中找到对于任何到达sfq脉冲具有最大上升时间(mrt)的汇引脚。在一个示例中,mrt可以通过处理器执行对其中存储有mrt值的表进行查找的步骤而被确定。在表10的步骤2中,与门相关联的相位可以根据需要被改变为p+。作为示例,虽然相位0的指派可能适用于门的一个汇引脚,但是它可能不适用于另一汇引脚。在这种情况下,指派给门的相位可以被增加90度(假设正在被设计的逻辑电路由四相ac时钟计时,其中下一相位指派是90度)。如果被指派给门的相位变化(例如,增加90度),则指派给下游门和jtl的相位被无效。

[0071]

继续参考表10,在步骤3中,t的针对所选相位指派的目标时间可以被指派给逻辑门。在步骤4中,针对每个汇引脚,从没有jtl被插入路径开始,该算法可以确定汇引脚是否在时间t前可抵达。如果汇引脚不可抵达,则额外的jtl可以被插入。因此,如果逻辑门510最初被指派90度的相位并且如果逻辑门510的输入端子ai(门的汇引脚中的一个汇引脚)在时间t内不可抵达(即,mrt大于t),则额外的jtl可以被插入。作为示例,附加的缓冲器(例如,jtl 514)可以被插入通向汇引脚中的一个汇引脚的路径中。可以在查找表中查找与添加了jtl的缓冲器序列相关联的延迟。如果mrt仍然大于t,则汇引脚在仍然在时间t前不可抵达。对于逻辑门,以源引脚的相位开始,相位可以被指派给每个缓冲器(例如,每个jtl)。例如,如果为逻辑门指派0度相位不起作用,则其可以被指派90度相位。

[0072]

继续表10中的算法描述,使用createcomponentgraph方法,可以针对正在设计的逻辑电路创建组件图。作为示例,可以创建针对逻辑电路500的组件图。接下来,该算法可以包括调用runlengthchecker方法,该方法可以基于为定时而被添加的jtl来创建不同的报告。接下来,该算法可以包括调用withinreach方法以确定在目标时间t前汇引脚是否可抵达。如果汇引脚可抵达,则可以将其从c个门中移除。如果c为空并且与逻辑门g相关联的所有汇引脚都已经被处理,则在步骤5中,关键路径被标识为已经从c中移除的最后一个汇引脚。如果c不为空,则(在这个示例中)作为步骤6的一部分,算法的处理返回步骤2。在确定关键路径后,逻辑门和jtl需要相位指派。关于表11描述了用于相位指派的示例算法。

[0073][0074]

表11

[0075]

如表11中所示,除非已经被确定,否则第一步骤需要确定针对正在被处理的门的关键路径。接下来,在步骤2中,可以基于该关键路径将相位指派给各种jtl和门。作为示例,如前面关于表10所描述的,在关键路径确定期间相位指派可以被改变。使用这些相位指派,在步骤3中,调用被称为arepinrelativephasesvalid的方法来确定相位指派是否有效。该

方法可以考虑超导电路的逻辑,包括考虑该逻辑是行波流水线逻辑还是相位模式逻辑。

[0076]

仍然参考表11,下一步骤涉及添加具有被指派相位的额外jtl以关闭对关键引脚的约束。如果需要或期望相位变化,则这可以改变门的最初相位指派。这里的失败包括未能路由或未能添加另一需要的jtl以便满足时间。另一失败可能与超过合法到达时间范围的定时有关(例如,由于添加了jtl以覆盖距离)。下一步骤包括添加具有被指派相位的额外jtl,以关闭非关键引脚。作为示例,关于逻辑电路500,如果与输入ai对应的汇引脚被确定为关键路径,则此步骤包括根据需要添加额外的jtl以确保关于对应于与门510的输入bi的汇引脚的定时是正确的。

[0077]

图6是根据一个示例的方法的流程图600,该方法用于确定超导电路设计中的定时路径的有效性。在这个示例中,作为流程图600的一部分列举的各个步骤可以由图1的定时引擎132执行。步骤610可以包括提供定时信息,该定时信息关于与至少一个逻辑门的第一汇端子耦合的该至少一个逻辑门的多个源端子。在一个示例中,该信息可以经由图1的定时库170被提供。

[0078]

步骤620可以包括:基于被指派给至少一个逻辑门的第一相位,鉴于定时信息,确定在预定的到达时间范围内第一汇端子是否由单通量量子(sfq)脉冲可抵达。在这个示例中,当与定时引擎132有关的代码/算法(例如,在图4的存储器406中所存储的代码或算法)由处理器(例如,图4的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。当定时引擎132被加载到存储器(例如,图4的存储器406)中时,定时引擎132可以访问定时库170。作为示例,定时引擎132可以执行表10中所示步骤的步骤4,以基于被指派给至少一个逻辑门的第一相位、鉴于定时信息来确定在预定的到达时间范围内第一汇端子是否由单通量量子(sfq)脉冲可抵达。虽然图6示出以特定顺序执行的特定数目的步骤,但方法600可以包括以不同顺序执行的更多或更少的步骤。

[0079]

图7是根据另一示例的方法的流程图700,该方法用于确定关键定时路径以及用于在超导电路设计中求解关键定时路径。在这个示例中,作为流程图700的一部分陈述的各个步骤可以由图1的定时引擎132执行。步骤710可以包括:提供关于与多个逻辑门相关联的多个源端子的定时信息。在一个示例中,该信息可以经由与图1的系统100相关联的定时库170被提供给定时引擎132。

[0080]

步骤720可以包括:接收从与目标逻辑门相关联的多个汇端子之中对第一汇端子的选择,该目标逻辑门是从多个逻辑门之中被选择的。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行表10中所示的步骤1。因此,作为示例,定时引擎132可以在一组c个汇引脚中找到具有最小的最大上升时间(mrt)的汇引脚。在一个示例中,定时引擎132可以通过对查找表(其可以被存储在图4的存储器406中)进行查找来找到汇引脚。

[0081]

步骤730可以包括接收对目标逻辑门的相位指派。在这个示例中,当与定时引擎132有关的代码/算法(例如,在图4的存储器406中所存储的代码或算法)由处理器(例如,图4的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行表10中所示的步骤1。因此,作为示例,定时引擎132可以将初始相位指派给目标逻辑门。作为示例,关于逻辑电路500,逻辑门510初始被指派180度的相位。该相位指派可

以基于逻辑电路500设计的拓扑变化而经历变化。

[0082]

步骤740可以包括针对多个汇端子中的每个汇端子:(1)确定在预定的到达时间范围内多个汇端子中的每个汇端子是否由相应的单通量量子(sfq)脉冲可抵达,以及(2)如果在预定的到达时间范围内第一汇端子不可抵达,则在与目标逻辑门相关联的源端子和被确定在预定的到达时间范围内不可抵达的第一汇端子之间插入约瑟夫森传输线(jtl),并且在确定第一汇端子在jtl的插入之后、在预定的到达时间范围内可抵达后,从被认为与关键定时路径相关联的多个汇端子之中移除第一汇端子。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行表10中所示的步骤4。尽管图7示出以特定顺序执行的特定数目的步骤,但是该方法可以包括以不同顺序执行的更多或更少的步骤。

[0083]

为了将定时引脚分解成可以异步处理的运行集,定时约束群组可以由连接的定时约束的集形成。针对一个设计可以有多个定时约束群组。针对每个设计可以有一个大的定时约束群组,还有一些较小的定时约束群组。正如前面关于图2和表4和表5所解释的,定时约束群组210可以包括与定时约束有关的信息的集合,包括定时约束212、定时约束214和定时约束216。这些信息中的每个项可以使用数据结构来实现,并且每个项可以指向与定时引脚有关的数据结构以指示定时约束与该特定时引脚或该组定时引脚有关。定时图可以指向定时约束群组内的定时引脚的图。

[0084]

定时图可以利用定时路径上的所有物理连接组件的定时组件来构建。针对每个图都有映射,其中包含该图所拥有的所有定时组件。除了头部之外,定时路径上的所有组件都由其定时图拥有。头部由其前身的定时图拥有。表12提供用于求解和调和约束群组的算法示例。

[0085][0086]

表12

[0087]

步骤1包括:针对与正被分析的所有约束群组(例如,可以是定时路径的一部分的

定时约束群组)相关联的一组定时端点,确定关键路径以及指派相位。在这个示例中,定时端点是定义单独的定时“轮次(run)”的引脚,可以根据它们的定时和相位约束对其进行独立地定时和验证。它们由电路设计者定义,并且是电路设计中的显式组件。取决于与电路相关联的逻辑是使用相位模式逻辑还是行波流水线逻辑来实现的,可以指定不同类型的定时端点。对于行波流水线逻辑电路或相位模式逻辑电路,库数据中弧的存在与否将指示定时引脚是开始定时端点还是结束定时端点。在这个示例中,该组定时端点包括与是同一定时约束群组的一部分的定时引脚相关联的定时端点。例如,与逻辑电路500相关联的定时引脚可以是同一定时约束群组的一部分。这组定时端点还可以包括与在特定跳数内的定时约束群组相关联的定时端点。在一个示例中,这些群组可以包括向后两跳和向前一跳、或者向前两跳和向后一跳的群组。为了分析这些定时引脚,可以创建“影子”元件来表示定时路径上的物理连接的元件。

[0088]

仍然参考表12,步骤2可以:包括针对所有定时组件(timingcomponent)进行调和。调和步骤的获胜方是“拥有”用于定时的引脚的定时约束群组中的值。对于路径中的所有定时组件和尾部,它是它们的定时约束群组。对于头部,当它是尾部时是定时组件的定时约束群组。因此,总而言之,该步骤可以包括:使用门的定时路径来设置物理连接到该门的其他定时路径的值,调和到达时间和信号传播元件(例如,jtl的插入)中的差异。

[0089]

继续参考表12,步骤3包括:确定关于定时和相位指派是否有任何改变。如果有变化,则算法的处理返回步骤3。如果没有变化,则处理包括求解定时约束群组以确保针对在定时约束群组中的额外组件(例如,额外jtl)的定时信息和相位指派是准确的。因此,使用表12中描述的算法,可以朝向收敛的解决方案进行迭代,其中迭代导致定时和相位指派固定并且不再需要改变。关于作为图8-图13的一部分的示例电路提供了关于表12描述的算法的应用。

[0090]

图8示出表示示例定时约束群组(tcg)800的电路的图解,定时约束群组(tcg)800包括作为约束群组一部分的定时引脚,其可以使用关于表12描述的求解和调和算法来处理。tcg 800可以包括缓冲器812、814和816,这些缓冲器可以被耦合到如图8中所示的门810的输入端子和输出端子。从定时分析的角度来看,tcg 800包括三个定时端点。前两个定时端点与缓冲器812和814的输入对应,第三定时端点与缓冲器816的输出对应。定时约束群组数据结构可以被用来表示tcg 800定时分析的相关细节。求解和调和算法可以鉴于由设计中其他电路施加的定时约束来处理定时设计。在一个示例中,作为该分析的一部分,在三个定时端点的深度内的组件(被称为影子组件)可以被包括。另外,作为该分析的一部分,三个定时端点深度内的真实组件也可以被包括。这是因为定时不仅会作为对影子组件的改变的结果而变化,还会作为对真实组件的改变的结果而变化。

[0091]

图9示出包括与作为超导电路设计一部分的在定时约束群组(tcg)800之前或之后的tcg对应的影子组件的图解900。除了需要考虑它们来求解和调和tcg 800之外,这些影子组件是其他定时约束群组的一部分并且没有被定时。在这个示例中,包括向后的两个定时端点和向前的一个定时端点作为分析的一部分。在这个示例中,tcg 910可以包括缓冲器918、920和922,它们如图9中所示被耦合和布置。tcg 910还可以包括逻辑门912、914和916,它们如图9中所示被耦合和布置。tcg 930可以包括缓冲器934和936以及门932,它们可以如图9中所示被耦合和布置。图9还示出对与两定时端点相关联的缓冲器812和缓冲器814的初

始相位指派。在这个示例中,缓冲器812和缓冲器814的相位指派都是0。这两个定时端点的0度相位指派的第一合法开始时间被确定为13皮秒(ps),如图9中所标记的。在这个示例中,合法开始时间是基于定时约束而被确定的,该定时约束是基于对所实现的缓冲器和门的硬件分析而被标识的。

[0092]

图10是示出向tcg 800添加有源传输元件的图解1000。在图10中,tcg 800经受使用关键路径和相位指派初始求解步骤(这个步骤与表12中的算法的步骤1对应)。在这个示例中,该步骤涉及针对与tcg 800的门810相关联的定时引脚而执行表11中所示的步骤1-4。执行这些步骤的结果是在缓冲器812与门810的一个输入之间添加了有源传输元件(例如,jtl 1012、1014和1016)。另外,在缓冲器814与门810的另一输入之间添加了jtl 1018和1020。门810的相位指派也从0度被改变为90度。类似地,缓冲器816的相位指派从0度被改变为90度。另外,针对缓冲器816的90度相位的第一合法开始时间被计算为57皮秒(ps)。在这个示例中,tcg 800的定时/相位信息的改变和附加jtl的插入需要受这些改变影响的其他定时约束群组的定时信息发生改变。

[0093]

图11是示出定时信息和相位指派以及为其他定时约束群组填充的额外jtl(根据需要)的图解1100。因此,在这个示例中,tcg 910被示为包括在门912与缓冲器918之间所添加的额外jtl 1110、1112和1114。另外,门912已经被指派60ps的合法开始时间和180度的相位。缓冲器918已经被指派97ps的合法开始时间和270度的相位。门916已经被指派108ps的合法开始时间和0度的相位。此外,tcg910包括额外的jtl 1116、1118和1120,它们已经被添加在门914与tcg 800的缓冲器814的输入之间。门914已经被指派90ps的合法开始时间。额外的jtl 1122、1124、1126和1128已经被添加到缓冲器922的输出与门914的汇引脚中的一个汇引脚之间。缓冲器920已经被指派88ps的合法开始时间和270度的相位,并且缓冲器922已经被指派51ps的合法开始时间和90度的相位。

[0094]

继续参考图11,tcg 930被示出具有额外的jtl 1132和1134。门932已经被指派89ps的合法开始时间和270度的相位。缓冲器934已经被指派60ps的合法开始时间和90度的相位。缓冲器936已经被指派75ps的合法开始时间和180度的相位。针对tcg 930,定时和相位指派可以以与针对tcg 800的方式类似的方式被确定。

[0095]

图12是示出根据一个示例的tcg 800的头部的定时变化的图解1200。因此,在这个示例中,缓冲器812的合法开始时间已从13ps被改变为18ps,而缓冲器814的合法开始时间已从13ps被改变为16ps。这些定时变化可以作为调和步骤的一部分被确定(例如,表12中算法的步骤3)。接下来,与其余组件相关联的定时和相位信息:tcg 800中的门810和缓冲器816被清理。接下来,tcg 800再次经受求解步骤。

[0096]

图13是示出根据一个示例的tcg 800的其余组件的定时变化的图解1300,该定时变化是求解步骤的结果。在这个示例中,门810的合法开始时间从54ps改变为56ps,缓冲器816的合法开始时间从57ps改变为58ps。尽管求解步骤不会改变门810和缓冲器816的相位指派,但是如果需要,它们可以改变。接下来,与其他tcg中的影子组件相关联的定时和相位指派被更新。

[0097]

图14是示出根据一个示例的其他tcg(例如,tcg 910和tcg930)的定时变化的图解1400。在这个示例中,该步骤作为关于表12描述的算法的、用以更新影子组件的定时和相位指派一部分的应用被执行。在这个示例中,门912的合法开始时间从60ps被改变为61ps;914

门的合法开始时间从90ps被改变为91ps;并且门916的合法开始时间从108ps被改变为109ps。缓冲器918的合法开始时间目前没有变化(97ps);缓冲器920的合法起始时间从88ps被改变为89ps;并且缓冲器922的合法起始时间从51ps被改变为52ps。关于tcg930,门932的合法开始时间从89ps被改变为90ps。缓冲器934的合法开始时间从60ps被改变为61ps,缓冲器936的合法开始时间从75ps被改变为76ps。涉及调和步骤的步骤可以被重复,直到不存在与定时和相位指派有关的冲突。例如,除了与缓冲器918相关联的合法开始时间从97ps被改变为98ps之外,后续的调和步骤可以保持所有的定时相同。因此,在这个示例中,图8-图14示出应用表12中所示的算法来找到收敛解决方案,其中算法的迭代导致定时和相位指派固定且不再需要改变。

[0098]

图15是根据一个示例的方法的流程图1500,该方法用于在超导电路设计中确定定时路径和调和拓扑。在这个示例中,超导电路设计可以包括第一定时路径,第一定时路径包括第一组定时引脚,并且第一组定时引脚的第一子集可以与包括第一定时端点和第二定时端点的第一定时约束群组相关联。步骤1510可以包括:处理第一定时约束群组,以将第一合法开始时间指派给第一定时端点并且将第二合法开始时间指派给第二定时端点。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行关于表12描述的算法的步骤1。作为示例,这个步骤可以包括使用先前描述的关键定时路径算法,可以针对定时端点中的每个定时端点来确定(多个)合法开始时间。

[0099]

步骤1520可以包括:在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在第一定时端点之前或这在第二定时端点之后。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以以与关于图9描述的方式类似的方式来执行该步骤。因此,鉴于由设计中的其他电路施加的定时约束,定时引擎132可以处理定时设计。在一个示例中,作为该分析的一部分,在三个定时端点的深度内的组件(被称为影子元件或影子组件)可以被包括。这些端点的合法开始时间和作为影子元件的一部分的门或缓冲器的相位指派可以以与前面描述的方式类似的方式被获得。

[0100]

步骤1530可以包括:解决由于在定时路径上插入第一影子元件而引起的对第一合法开始时间或第二合法开始时间的任何改变。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行表12中描述的步骤2和3。作为示例,在图8的示例定时约束群组800的帮助下,关于图10-图14描述了这些步骤。尽管图15示出以特定顺序执行的特定数目的步骤,但是该方法可以包括以不同顺序执行的更多或更少的步骤。

[0101]

图16是根据一个示例的方法的流程图1600,该方法用于在超导电路设计中确定定时路径并调和拓扑。在这个示例中,超导电路设计可以包括第一定时路径,第一定时路径包括与第一电路组件相关联的第一定时端点和与第二电路组件相关联的第二定时端点,并且其中第一电路组件和第二电路组件中的每个电路组件包括约瑟夫森结。第一电路组件被指

派第一相位并且第二电路组件被指派第二相位。步骤1610可以包括:使用处理器,确定针对定时路径上的第一定时端点的第一合法开始时间,以及确定针对定时路径上第二定时端点的第二合法开始时间。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行关于表12描述的算法的步骤1。作为示例,这个步骤可以包括使用前面描述的关键定时路径算法,可以针对定时端点中的每个定时端点来确定(多个)合法开始时间。

[0102]

步骤1620可以包括:在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在定时路径上的第一电路组件之前。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以以与关于图9描述的方式类似的方式来执行该步骤。因此,鉴于由设计中的其他电路施加的定时约束,定时引擎132可以处理定时设计。在一个示例中,作为该分析的一部分,在三个定时端点的深度内的组件(被称为影子元件或影子组件)可以被包括。作为步骤1620的一部分,第一影子元件可以是在定时路径上的第一电路组件之前的定时约束群组的一部分。因此,在这个示例中,第一影子元件可以是图9的门914。作为影子元件的一部分包括的这些端点的合法开始时间和门或缓冲器的相位指派可以用与前面描述的方式类似的方式被获得。

[0103]

步骤1630可以包括:在定时路径上插入第二影子元件,第二影子元件表示第二物理连接的组件,其中第二影子元件在定时路径上的第二电路组件之后。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以以与关于图9描述的方式类似的方式来执行该步骤。因此,鉴于由设计中的其他电路施加的定时约束,定时引擎132可以处理定时设计。在一个示例中,作为该分析的一部分,在三个定时端点的深度内的组件(被称为影子元件或影子组件)可以被包括。作为步骤1630的一部分,第二影子元件可以是在定时路径上在第二电路组件之后的定时约束群组的一部分。因此,在这个示例中,第二影子元件可以是图9的门934。作为影子元件的一部分包括的这些端点的合法开始时间和门或缓冲器的相位指派可以用与前面描述的方式类似的方式被获得。

[0104]

步骤1640可以包括解决由于在定时路径上插入第一影子元件和第二影子元件而引起的对第一合法开始时间和第二合法开始时间的任何改变。在这个示例中,当与定时引擎132有关的代码/算法(例如,图4的存储器406中所存储的代码或算法)由处理器(例如,图4中的(多个)处理器402)执行时,该步骤可以由定时引擎132执行。在这个示例中,定时引擎132可以执行表12中描述的步骤2和3。作为示例,在图8的示例定时约束群组800的帮助下,关于图10-图14描述了这些步骤。尽管图16示出以特定顺序执行的特定数目的步骤,但是该方法可以包括以不同顺序执行的更多或更少的步骤。

[0105]

总之,本公开涉及一种由处理器实现的用于在超导电路设计中确定关键定时路径的方法,其中超导电路设计包括至少一个逻辑门,该至少一个逻辑门包括至少一个约瑟夫森结,并且其中至少一个逻辑门具有被指派的第一相位,该第一相位与用于对至少一个逻

辑门进行计时的时钟信号相关联。该方法可以包括提供关于至少一个逻辑门的多个源端子的定时信息,该多个源端子与至少一个逻辑门的第一汇端子耦合。该方法还可以包括:使用处理器,基于被指派给至少一个逻辑门的第一相位,鉴于定时信息,确定在预定的到达时间范围内第一汇端子是否由单通量量子(sfq)脉冲可抵达。

[0106]

该方法还可以包括,如果在预定的到达时间范围内第一汇端子由单通量量子(sfq)脉冲不可抵达,则在多个源端子中的至少一个源端子与第一汇端子之间插入约瑟夫森传输线(jtl)元件。该方法还可以包括:确定第一汇端子在jtl元件的插入之后、在预定的到达时间范围内是否由sfq脉冲可抵达。该方法还可以包括:在确定第一汇端子在jtl元件的插入之后、在预定的到达时间范围内由sfq脉冲可抵达后,从与至少一个逻辑门相关联的、被认为与关键定时路径相关联的多个汇端子之中移除第一汇端子。

[0107]

该方法还可以包括:基于预定行为,从与至少一个逻辑门相关联的多个汇端子之中选择第一汇端子。基于预定行为选择第一汇端子可以包括:选择具有与多个汇端子相关联的相应sfq脉冲的最大上升时间值中的最小值的汇端子作为第一汇端子。

[0108]

该方法可以包括:在确定步骤之前,通过向第一相位添加相位偏移,将第二相位指派给至少一个逻辑门。定时信息可以经由定时库而被提供,定时库至少包括定时约束和受允许的信号类型,其中受允许信号类型是从包括信号的行波流水线逻辑类型或信号的相位模式逻辑类型的群组中被选择的。

[0109]

在另一方面,本公开涉及一种由处理器实现的用于在超导电路设计中确定关键定时路径的方法,其中超导电路设计包括多个逻辑门,并且其中多个逻辑门中的每个逻辑门包括至少一个约瑟夫森结。该方法可以包括提供关于与多个逻辑门相关联的多个源端子的定时信息。该方法还可以包括接收从与目标逻辑门相关联的多个汇端子之中对第一汇端子的选择,该目标逻辑门是从多个逻辑门之中被选择的。该方法还可以包括接收对目标逻辑门的相位的指派。该方法还可以包括针对多个汇端子中的每个汇端子:使用处理器,确定在预定的到达时间范围内多个汇端子中的每个汇端子是否由相应的单通量量子(sfq)脉冲可抵达,以及如果第一汇端子在预定的到达时间范围内不可抵达,则在与目标逻辑门相关联的源端子与被确定在预定的到达时间范围内不可抵达的第一汇端子之间插入约瑟夫森传输线(jtl),并且在确定第一汇端子在jtl的插入之后、在预定的到达时间范围内可抵达后,从被认为与关键定时路径相关联的多个汇端子之中移除第一汇端子。

[0110]

该方法还可以包括基于预定行为从与目标逻辑门相关联的多个汇端子之中选择第一汇端子。基于预定行为选择第一汇端子可以包括:选择具有与多个汇端子相关联的相应sfq脉冲的最大上升时间值中的最小值的第一汇端子作为第一汇端子。

[0111]

该方法还可以包括:在确定步骤之前,通过向第一相位添加相位偏移来将第二相位指派给目标逻辑门。定时信息可以经由定时库而被提供,定时库至少包括定时约束和受允许的信号类型,其中受允许信号类型是从包括信号的行波流水线逻辑类型或信号的相位模式逻辑类型的群组中被选择的。

[0112]

在又一方面,本公开涉及一种被配置为在超导电路设计中确定关键定时路径的系统,其中超导电路设计包括至少一个逻辑门,该逻辑门包括至少一个约瑟夫森结,并且其中至少一个逻辑门具有被指派的第一相位,第一相位与用于对至少一个逻辑门进行计时的时钟信号相关联。该系统可以包括第一子系统,第一子系统被配置为提供关于至少一个逻辑

门的多个源端子的定时信息,该多个源端子与至少一个逻辑门的第一汇端子耦合。该系统还可以包括第二子系统,第二子系统包括处理器,第二子系统被配置为:基于被指派给至少一个逻辑门的第一相位,鉴于定时信息,确定在预定的到达时间范围内第一汇端子是否由单通量量子(sfq)脉冲可抵达。

[0113]

该系统还可以被配置为:如果在预定的到达时间范围内第一汇端子由sfq脉冲不可抵达,则允许在多个源端子中的至少一个源端子与第一汇端子之间插入约瑟夫森传输线(jtl)元件。该系统还可以被配置为:在插入jtl元件之后,确定在预定的到达时间范围内第一汇端子是否由sfq脉冲可抵达。该系统还可以被配置为:在确定第一汇端子在插入jtl元件之后、在预定的到达时间范围内由sfq脉冲可抵达后,从与至少一个逻辑门相关联的、被认为与关键定时路径相关联的多个汇端子之中移除第一汇端子。该系统还可以被配置为选择具有与多个汇端子相关联的相应sfq脉冲的最大上升时间值中的最小值的汇端子作为第一汇端子。

[0114]

该系统还可以被配置为:通过向第一相位添加相位偏移,将第二相位指派给至少一个逻辑门。该系统还可以包括定时库,定时库至少包括定时约束和受允许的信号类型,其中受允许的信号类型是从包括信号的行波流水线逻辑类型或信号的相位模式逻辑类型的群组中被选择的。

[0115]

在另一方面,本公开涉及由处理器实现的用于在超导电路设计中确定定时路径和调和拓扑的方法,其中超导电路设计包括第一定时路径,第一定时路径包括第一组定时引脚,并且其中第一组定时引脚的第一子集与包括第一定时端点和第二定时端点的第一定时约束群组相关联。该方法可以包括:使用处理器来处理第一定时约束群组,以将第一合法开始时间指派给第一定时端点以及将第二合法开始时间指派给第二定时端点。该方法还可以包括在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在第一定时端点之前或在第二定时端点之后。该方法还可以包括解决由于在定时路径上插入第一影子元件引起的对第一合法开始时间或第二合法开始时间的任何改变。

[0116]

在该方法中,处理第一定时约束群组以将第一合法开始时间指派给第一定时端点可以包括:确定在第一到达时间范围内第一定时端点是否由单通量量子(sfq)脉冲可抵达,并且其中处理第一定时约束群组以将第二合法开始时间指派给第二定时端点包括:确定在第二到达时间范围内第二定时端点是否由sfq脉冲可抵达。该方法还可以包括:如果在第二到达时间范围内第二定时端点由sfq脉冲不可抵达,则在第一定时端点与第二定时端点之间插入约瑟夫森传输线(jtl)元件。

[0117]

定时路径可以包括第二定时约束群组和第三定时约束群组,其中第二定时约束群组包括第三定时端点和第四定时端点,并且第三定时约束群组包括第五定时端点和第六定时端点,并且其中该方法还包括:处理第二定时约束群组,以将第三合法开始时间指派给第三定时端点并且将第四合法开始时间指派给第四定时端点,以及,处理第三定时约束群组,以将第五合法开始时间指派给第五定时端点并且将第六合法开始时间指派给第六定时端点。

[0118]

该方法还可以包括:在定时路径上插入第二影子元件,第二影子元件表示第二物理的连接组件,其中第二影子元件在第一定时端点之前或在第二定时端点之后。解决对第一合法开始时间或第二合法开始时间的任何改变可以包括:修改第一合法开始时间以生成

第一经修改的合法开始时间或修改第二合法开始时间以生成第二经修改的合法开始时间。

[0119]

该方法还可以包括解决由于在定时路径上插入第二影子元件而引起的对第一经修改的合法开始时间或第二经修改的合法开始时间的任何改变。可以经由至少包括定时约束和受允许的信号类型的定时库来提供关于定时路径的定时信息,其中受允许的信号类型是从包括信号的行波流水线逻辑类型或信号的相位模式逻辑类型的群组中被选择的。

[0120]

在又一方面,本公开涉及由处理器实现的用于在超导电路设计中确定定时路径和调和拓扑的方法,其中超导电路设计包括第一定时路径,第一定时路径包括与第一电路组件相关联的第一定时端点和与第二电路组件相关联的第二定时端点,并且其中第一电路组件和第二电路组件中的每个电路组件都包括约瑟夫森结,并且其中第一电路组件被指派第一相位并且第二电路组件被指派第二相位。该方法可以包括:使用处理器,确定定时路径上的第一定时端点的第一合法开始时间以及确定定时路径上的第二定时端点的第二合法开始时间。该方法还可以包括在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在定时路径上在第一电路组件之前。该方法还可以包括在定时路径上插入第二影子元件,第二影子元件表示第二物理连接的组件,其中第二影子元件在定时路径上在第二电路组件之后。该方法还可以包括解决由于在定时路径上插入第一影子元件和第二影子元件而引起的对第一合法开始时间和第二合法开始时间的任何改变。

[0121]

确定第一定时端点的第一合法开始时间可以包括:确定在第一到达时间范围内第一定时端点是否由单通量量子(sfq)脉冲可抵达;并且其中确定对第二定时端点的第二合法开始时间包括:确定在第二到达时间范围内第二定时端点是否由sfq脉冲可抵达。该方法还可以包括:如果在第二到达时间范围内第二定时端点由sfq脉冲不可抵达,则在第一电路组件与第二电路组件之间插入约瑟夫森传输线(jtl)元件并且向jtl指派相位。解决对第一合法开始时间或第二合法开始时间的任何改变可以包括:修改第一合法开始时间以生成第一经修改的合法开始时间或修改第二合法开始时间以生成第二经修改的合法开始时间。

[0122]

该方法还可以包括解决由于在定时路径上插入第二影子元件而引起的对第一经修改的合法开始时间或第二经修改的合法开始时间的任何改变。可以经由至少包括定时约束和受允许信号类型的定时库来提供关于定时路径的定时信息,其中受允许信号类型是从包括行波流水线逻辑类型的信号或相位模式逻辑类型的信号的群组中被选择的。

[0123]

在又一方面,本公开涉及一种被配置为在超导电路设计中确定定时路径和调和拓扑的系统,其中超导电路设计包括第一定时路径,第一定时路径包括与第一电路组件相关联的第一定时端点以及与第二电路组件相关联的第二定时端点,并且其中第一电路组件和第二电路组件中的每个电路组件都包括约瑟夫森结,并且其中第一电路组件被指派第一相位并且第二电路组件被指派第二相位。该系统可以包括处理器和包括指令的存储器。该指令可以被配置为:(1)确定定时路径上的第一定时端点的第一合法开始时间以及确定定时路径上的第二定时端点的第二合法开始时间,(2)在定时路径上插入第一影子元件,第一影子元件表示第一物理连接的组件,其中第一影子元件在定时路径上在第一个电路组件之前,(3)在定时路径上插入第二影子组件,第二影子组件表示第二物理连接的组件,其中第二影子元件在定时路径上在第二电路组件之后,并且(4)解决由于在定时路径上插入第一影子元件和第二影子元件而引起的对第一合法开始时间和第二合法开始时间的任何改变。

[0124]

第一影子元件可以经由第一有源传输元件被耦合到第一电路组件,并且第二电路

组件可以经由第二有源传输元件被耦合到第二影子元件。第一有源传输元件可以包括第一约瑟夫森传输线(jtl)并且第二有源传输元件可以包括第二jtl。

[0125]

第一有源传输元件可以被指派第三相位,并且第二有源传输元件可以被指派第四相位。第一相位、第二相位、第三相位和第四相位中的每个相位可以从由0度相位、90度相位、180度相位和270度相位组成的群组中被选择。该系统还可以包括定时库,该定时库包括关于定时路径的定时信息,其中定时信息至少包括定时约束和受允许的信号类型,其中受允许的信号类型是从包括信号的行波流水线逻辑类型或信号的相位模式逻辑类型的群组中被选择的。

[0126]

应当理解,本文描述的方法、模块和组件仅仅是示例性的。备选地或附加地,本文描述的功能性可以至少部分地由一个或多个硬件逻辑组件来执行。例如但不限于,可以使用的硬件逻辑组件的说明性类型包括现场可编程门阵列(fpga)、专用集成电路(asic)、专用标准产品(assp)、片上系统(soc)、复杂可编程逻辑器件(cpld)等。在抽象但仍然明确的意义上,达成相同功能性的任何组件布置都有效地“相关联”,以使得实现所需的功能性。因此,本文中组合实现特定功能的任何两个组件可以被视为彼此“相关联”,以使得达成期望的功能性,而与架构或中间组件无关。同样,任何两个如此相关联的组件也可以被视为彼此“可操作地连接”或“耦合”以达成期望的功能性。

[0127]

与本公开中描述的示例相关联的功能性还可以包括非瞬态介质中存储的指令。本文使用的术语“非瞬态介质”是指存储使机器以特定方式操作的数据和/或指令的任何介质。示例性的非瞬态介质包括非易失性介质和/或易失性介质。非易失性介质包括例如硬盘、固态驱动器、磁盘或磁带、光盘或磁带、闪存、eprom、nvram、pram或其他这样的介质,或这样的介质的网络版本。易失性介质包括例如动态存储器,诸如dram、sram、高速缓存或其他这样的介质。非瞬态介质与传输介质不同,但可以与传输介质结合使用。传输介质被用于将数据和/或指令传送给机器(例如,图4中的(多个)处理器402)或从机器传送数据和/或指令。示例传输介质包括同轴电缆、光纤电缆、铜线和诸如无线电波的无线介质。

[0128]

此外,本领域技术人员将认识到,上述操作的功能性之间的界限仅仅是说明性的。多个操作的功能性可以被组合成单个操作,和/或单个操作的功能性可以在附加操作中分布。此外,备选实施例可以包括特定操作的多个实例,并且在各种其他实施例中可以更改操作的顺序。

[0129]

尽管本公开提供了具体的示例,但是在不脱离如以下权利要求中阐述的本公开范围的情况下可以进行各种修改和改变。因此,说明书和附图被认为是说明性的而不是限制性的,并且所有这样的修改都旨在包括在本发明的范围内。本文关于具体示例描述的任何益处、优点或问题的解决方案不应被解释为任何或所有权利要求的关键、必需或基本的特征或要素。

[0130]

此外,本文所用的术语“一”或“一个”被定义为一个或多于一个。而且,即使同一权利要求包括介绍性短语“一个或多个”或“至少一个”以及诸如“一”或“一个”之类的不定冠词,在权利要求中使用诸如“至少一个”和“一个或多个”的介绍性短语也不应被解释为暗示由不定冠词“一”或“一个”引入的另一权利要求元素将包含这样引入的权利要求元素的任何特定权利要求限制为仅包含一个这种要素的发明。这同样适用于定冠词的使用。

[0131]

除非另有说明,否则使用诸如“第一”和“第二”之类的术语来任意区分这样的术语

所描述的元素。因此,这些术语不一定旨在指示这种元素的时间或其他优先级。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1