串行化神经网络计算单元的制作方法

串行化神经网络计算单元

1.相关申请

2.本技术要求于2019年12月3日所提出名称为“serialized nonvolatile neural network computing unit”的美国临时专利申请62/942,923的优先权。

技术领域

3.本发明涉及一种串行化神经网络计算单元,其输入、加权及输出模式被串行化,使得可以使用数字输入信号、低精密度的存储元件(memory cell)及传统的1位(1-bit)感测放大器实现神经网络计算单元,并且不需要在具有高精密度存储元件的内存阵列的列电路及行电路中的复杂的高精密度数位模拟转换器电路及模拟数字转换器电路。

背景技术:

4.神经网络计算单元越来越多地用于人工智能及机器学习的应用。计算的主要部分为输入数据与对应的训练加权值之间的大量的乘法与累加(multiply-and-accumulate,mac)运算。为了有效地实现上述mac运算而提出的一种方法为内存中计算(compute-in-memory)架构,其在储存数据的位置执行计算。在现有技术中,配置有内存中计算架构的mac计算块(computing block)使用存储元件作为神经网络的突触存储元件,其用于执行模拟输入数据与模拟加权值的乘法运算以产生最终的模拟输出电流。可以通过对模拟领域中的内存阵列的位在线的电流求和以执行累加运算。

5.然而,由于计算系统的其余部分与数字领域中的mac计算块之间进行通讯,因此先前的mac计算装置需要复杂的高精度(例如4、8、16或32位)数字模拟转换器电路及模拟数字转换器电路,以在数字领域与模拟领域之间转换关联的信号。数字领域数据可以表示最大为4、8、16或32位的信息。并且,先前的mac计算块需要高精度(例如4、8、16或32位)的突触组件,其中4、8、16或32位的信息可以储存在单个突触组件中。因此,配置有内存中计算架构的mac引擎的效率显著地受限于高精度数位模拟转换器电路及模拟数字转换器电路以及高精度突触组件的可利用性。

技术实现要素:

6.本发明提供了一种神经网络计算单元。根据本发明,神经网络计算单元包括:位线;内存阵列,其具有多个记忆块,各记忆块具有一个或多个的存储元件,各存储元件连接至位线;以及控制电路,其配置为:依序施加串行化输入至存储元件,使得存储元件响应于串行化输入依序产生多个输出,其中各输出对应于输入与储存在存储元件中的权重值的乘积;以及为该控制电路设定一组参考电流位准,此组参考电流位准中的每一个具有特定的电流量,以控制存储元件产生与对应于此组参考电流位准的个别输出电流。

7.在一种实施方式中,控制电路进一步配置为依序施加的串行化电压输入至存储元件,使得存储元件对应于串行化电压输入依序产生各个输出电流,其中输出电流对应于串行化电压输入与储存在存储元件中的权重值的乘积。在一种实施方式中,计算单元进一步

包含感测电路,用以依序接收该位线中的存储元件的输出电流。在一种实施方式中,该计算单元进一步包含累加器电路,其耦接至感测电路,并且累加器电路配置为将所接收的温度计码形式的输出电流之值转换为二进制码。在一种实施方式中,累加器电路进一步配置为以控制电路所定义的位移位方式(bit-shifted manner)累加经转换的值。

8.在一种实施方式中,计算单元进一步包含:主突触阵列,其包含连接至通用位线的多个存储元件;并且控制电路进一步配置为:将对应于多个串行输入数据的多个流电压输入串行化地施加至主突触阵列中对应的多个存储元件。在一种实施方式中,串行输入数据的最高有效位是最先输入至对应的存储元件中。在一种实施方式中,神经网络计算单元在不完全计算最低有效位的情况下完成计算。在一种实施方式中,计算单元进一步包含:参考突触阵列,其包含连接至位线的多个参考元件,其中参考元件是程序化为产生相同或不同的预定义输出电流至位线;并且控制电路进一步配置为:施加对应于多个串行输入数据的多个输入电压至选定的参考突触阵列的多个参考元件。

9.在一种实施方式中,控制电路进一步配置为关闭或者启动零个、一个或多个参考元件,以产生对应于由控制电路所定义的参考位准的个别输出。在一种实施方式中,来自参考元件的输出电流为二进制加权的。在一种实施方式中,感测电路进一步配置为感测第一记忆块中的存储元件的输出电流与第二记忆块中的存储元件的输出电流之和。

10.在一种实施方式中,感测电路进一步配置为获取以下各项之和:(i)对应于施加至第一记忆块的串行输入数据中的一位的输出电流,以及(ii)在施加至第二记忆块中的串行输入数据的一位的持续时间内,对应于各参考位准相的参考元件的输出电流。在一种实施方式中,感测电路进一步配置为:获取位线中的总输出电流;产生特定的阈值电流位准与总输出电流位准之间的比较结果;以及转换比较结果为对应的二进制信号。在一种实施方式中,感测电路进一步配置以为下列步骤设定迭代次数:(i)阈值电流位准与总输出电流位准之间的比较,以及(ii)根据结果将比较结果转换为对应的二进制信号。

11.在本发明的一种实施方式中,一种装置包含:存储元件阵列,其包含:位线;第一组存储元件,其分别连接至位线;第二组存储元件,其分别连接至位线;控制电路;第一组控制线,其连接控制电路至第一组存储元件,其中控制电路配置为依序以串行格式施加电压输入数据至第一组存储元件,使其响应于电压输入数据依序产生输出电流,其中输出电流对应于电压输入数据与储存于各存储元件中的权重的乘积;以及,第二组控制线,其连接控制电路至第二组存储元件,其中控制电路配置为设定一组参考电流位准,此组参考电流位准中的每一个具有特定的电流量,使得控制电路控制第二组存储元件产生对应于此组参考电流位准的个别输出电流;以及,感测电路,用以接收来自位线中的第一组存储元件及第二组存储元件的输出电流。

12.在一种实施方式中,存储元件为闪存、可变电阻式内存、铁电场效内存或具有权重内存的逻辑晶体管,其中的每一个皆经过程序化以产生预定义的特定输出电流。在一种实施方式中,此装置进一步包含累加器电路,其耦接至感测电路,其中累加器电路配置为以控制电路定义的位移位方式从感测电路接收经处理的信号值。在一种实施方式中,感测电路进一步配置为串行化地接收位线中的相应一个输出电流,并将其与预定义的阈值进行比较。在一种实施方式中,累加器电路进一步配置为执行将所接收的信号值从温度计码转换为二进制码,并且以控制电路定义的位移位方式累加经转换的二进制码。

附图说明

13.通过以下对于附图的说明,本发明的特征对于本领域普通技术人员将变得显而易见。应当理解的是,附图仅描述了本发明的典型实施例,且因此不应将附图视为对本发明范围的限制,并且将通过使用附图以附加的特征及细节来说明本发明。

14.图1为根据本发明一种实施方式的神经网络计算单元的方块图。

15.图2a至图2h为使用各种存储元件的根据本发明一种实施方式的例示性突触存储元件的示意图。

16.图3为根据本发明一种实施方式的突触内存阵列的简化方块图。

17.图4为根据本发明的一种实施方式的图1的计算电路的操作的时序图。

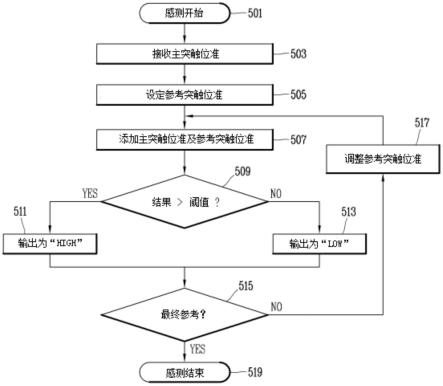

18.图5为说明根据本发明一种实施方式的串行化感测操作的过程的流程图。

19.图6为根据本发明一种实施方式的比较位线中所测量的总电流与预设阈值电流组的过程的流程图。

20.图7为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。

21.图8为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。

22.图9为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。

具体实施方式

23.图1为根据本发明一种实施方式的神经网络计算单元的方块图。神经网络计算单元(computing unit)100包含控制器(controller)110、主突触阵列(main synapse array)120、参考突触阵列(reference synapse array)130、感测电路(sensing circuit)140及累加器电路(accumulator circuit)150。

24.控制器110与主突触阵列120、参考突触阵列130、感测电路140及累加器电路150进行通讯。主突触阵列120可以包含单个或多个突触存储元件以共同表现特定的参数值。参考突触阵列130可以包含单个或多个突触存储元件以共同表现特定的参考值。主突触阵列120及参考突触阵列130可以从控制器110接收串行化的数字输入序列信号。来自主突触阵列120及参考突触阵列130的对应于输入序列信号的输出可以在连接至感测电路140的共享的位线bl中累加。

25.感测电路140配置为应用一个或多个的通过控制器110校正的阈值位准。感测电路140依序地从位线(bit line)bl接收串行化信号,并且使用通过控制器110配置的阈值位准以产生其串行化输出(serialized output)so序列。累加器电路150从感测电路140接收串行化输出so的值,并将这些值以通过控制器110的另一个控制信号配置的位移位方式累加在其输出节点(accumulator output)ao中。

26.此外,控制器110可以包含关键子区块(key subblock),例如缓存器、数据存储器、程序代码内存(code memory)、一次可程序内存或只读存储器或其他非挥发性内存、时序电路或数字处理电路。缓存器可以储存用于使控制器110执行预期操作的关键配置(key configuration)。数据存储器可以储存数字输入数据以提供至主突触阵列120及参考突触

阵列130。程序代码内存配置为储存控制器110的操作顺序。一次可程序内存或只读存储器或其他非挥发性内存可以储存感测电路140的参考电流位准,并且可以进一步配置为储存输入数字序列信号的串行化序列顺序(serialization sequence order)或时序信息(例如,msb优先、csb优先或lsb优先)、参数选择序列(parameter selection sequence)信号(例如,msb优先、csb优先或lsb优先)或者参考数字序列(reference digital sequence)信号(例如,低位准优先、中位准优先或高位准优先)。由于来自msb资料的结果对整个结果的贡献最大,因此可以优先输入msb输入数字信号及msb参数选择信号,使得控制器110能够在用lsb数据完成完整的运算序列信号之前停止发送数字序列信号,以在输出精度可牺牲的情况下取得更高的性能表现。当在lsb数据的运算结束前停止了输入序列,累加器输出ao节点上的中间累加器输出信号可以大约足够好地表示(represent approximately good enough)来自计算单元的总体输出。

27.时序电路可以检查操作顺序并且根据特定的时序以调制关键信号脉冲(modulate key signal pulses)(例如,图4中示出的操作时序)。数字处理电路可以从缓存器、数据存储器或程序代码内存、一次性可编程内存或只读存储器或其他非挥发性内存或时序电路中检索信息,并且具有错误检测或修正、压缩或解压缩、加密或解密,模式检测或计数、过滤、调制,布尔逻辑运算等能力,使得控制器110可以弹性地(resiliently)且高效率地发送位串行化(bit-serialized)数字序列信号至主突触阵列120及参考突触阵列130,以及发送控制信号至感测电路140及累加器电路150。控制器110的关键子区块的定义及使用为本领域普通技术人员了解的,并且不限定于在此阐述的具体说明或形式。

28.虽然将单条位线bl定义为用于神经网络计算单元100中相关联的电路组件的单条线,但是可以将复数条位线bl并联连接以同时计算多个行。因此,各个行可以共享通用串行化数字输入及参考序列信号以及来自控制器110的控制信号。另一方面,位线bl上的信号可以表示信息的正值或者负值。尽管在图1中描述了单条位线(例如,位线bl),但是突触阵列可以具有两条不同的输出位线(例如,bl_p及bl_n),使得一条线(例如,bl_p)携带正值的信息并且另一条线(例如,bl_n)携带负值的信息。在此情况下,感测电路140将两线信号之间的差作为输入。

29.此外,即使在图1中示出了单组的主突触阵列120,也可以将多组的主突触阵列120并联连接以表示多个参数,并且同时在共享的位线bl中累加多组的输出。因此,各组主突触阵列120可以分别具有串行化的数字输入序列信号。

30.进一步地,主突触阵列120及参考突触阵列130可以具有来自控制器110的多条输入信号线,使得输入数据的符号信息及其大小信息可以被携带至突触阵列。在一种实施方式中,主突触阵列120中的一组存储元件从控制器110依序接收多个输入信号。控制器110依序传送n位(二进制)输入数据至主突触阵列120中的各个突触存储元件,使得对应的存储元件产生对应于输入乘以所储存的存储元件权重的函数的输出电流信号。当提供n位输入信号至主突触阵列120中选定的存储元件中时,控制器110同步化主突触阵列120及参考突触阵列130中的存储元件的操作。控制器110同时传输多个参考序列信号至参考突触阵列130中的参考元件组,其中此信号启动零个、一个或多个对应的参考元件,以在各步骤中依序设定参考突触电流位准。

31.多个参考突触电流位准依序施加,通过传送多个参考序列信号至参考突触阵列

130,同时将n位输入中的一位提供至主突触阵列120中选定的存储元件而实现。控制器110控制参考突触阵列130中的参考元件组,使其一旦当输入的n位中的一个由主突触阵列120中选定的存储元件处理时,则会将各参考突触位准依序加以调整。

32.图2a至图2h为使用各种存储元件的根据本发明一种实施方式的例示性突触存储元件的示意图,其使用例如逻辑闪存、逻辑与非门闪存、与非门闪存、或门闪存、具有晶体管的可变电阻内存、不具有晶体管的可变电阻内存、铁电场效(ferroelectric field-effect transistor,fefet)内存以及具有权重内存w的逻辑晶体管。各突触存储元件可以根据控制线输入信号(例如,cg或cgx)以及以阈值电压(用于闪存)、电阻(用于可变式电阻内存)、极化(用于铁电场效内存)或电导(用于具有权重内存的逻辑晶体管)等形式储存于内存的加权值,以使适当的电流位准(例如,cur_w)流向位线bl。

33.图2a示出设定(programmed)在电流位准cur_w的使用逻辑闪存的突触存储元件。电流位准表示输入信号及权重参数的乘积。在此,通过一对信号线cg1及cg2施加输入信号。权重参数储存在逻辑闪存组件中。输出电流位准cur_w提供至位线bl。

34.图2b示出设定在电流位准cur_w的使用逻辑与非门(nand)闪存的突触存储元件。电流位准表示输入信号及权重参数的乘积。在此,通过从多对信号线中选定的一对信号线以施加输入信号(例如,信号线cg1/信号线cg2及信号线cg3/信号线cg4中的一组)。权重参数储存在选定的逻辑与非门(nand)闪存组件中。通过开启(turning on)所有其他的未选定的存储元件以及连接至信号线sg1/信号线sg2的顶部/底部开关晶体管,以提供输出电流位准cur_w至位线bl。

35.图2c示出设定在电流位准cur_w的使用与非门(nand)闪存的突触存储元件。电流位准表示输入信号及权重参数的乘积。在此,通过从多条信号线(信号线cg1至信号线cg4)中选定的一条信号线以施加输入信号。权重参数储存在选定的与非门(nand)闪存组件中。通过开启所有其他的未选定的存储元件以及连接至信号线sg1/信号线sg2的顶部/底部开关晶体管,以提供输出电流位准cur_w至位线bl。

36.图2d示出设定在电流位准cur_w的使用或非门(nor)闪存的突触存储元件。电流位准表示输入信号及权重参数的乘积。在此,通过信号线cg以施加输入信号。权重参数储存在或非门(nor)闪存组件中。通过开关连接至信号线sg的开关晶体管,以提供输出电流位准cur_w至位线bl。

37.图2e示出设定在电流位准cur_w的使用可变式电阻(resistive change)内存的突触存储元件,其具有晶体管。电流位准表示输入信号及权重参数的乘积。在此,通过信号线cg以施加输入信号。权重参数储存在可变电阻r_w中。通过开关连接至信号线cg的开关晶体管,以提供输出电流位准cur_w至位线bl。

38.图2f示出设定在电流位准cur_w的使用可变式电阻内存的突触存储元件,其不具有晶体管。电流位准表示输入信号及权重参数的乘积。在此,通过信号线cg以施加输入信号。权重参数储存在可变电阻r_w中。输出电流位准cur_w提供至位线bl。

39.图2g示出设定在电流位准cur_w的使用铁电场效内存的突触存储元件。电流位准表示输入信号及权重参数的乘积。在此,通过信号线cg以施加输入信号。权重参数储存在铁电场效内存中。输出电流位准cur_w提供至位线bl。

40.图2h示出设定在电流位准cur_w的使用具有权重内存w的逻辑晶体管的突触存储

元件。电流位准表示输入信号及权重参数的乘积。在此,通过信号线cg以施加输入信号。权重参数储存在权重内存w中。通过开关连接至信号线cg的开关晶体管,以提供输出电流位准cur_w至位线bl。

41.除了上述的突触存储元件之外,可以进一步配置有其他种类的突触存储元件,这些突触存储元件经过仔细地设定以达到对应于神经网络的权重参数的目标电流位准。

42.图3为根据本发明一种实施方式的突触内存阵列的简化方块图。

43.在一种实施方式中,主突触阵列120包含四个突触存储元件wa、wb、wc及wd。这些突触存储元件wa、wb、wc及wd通过通用位线bl连接,并且通过信号线cg_wa、cg_wb、cg_wc及cg_wd分别接收输入序列信号。进一步地,参考突触阵列130包含六个参考元件r0、r1、r2、r3、r4及r5,其通过位线bl连接,并且通过耦接的信号线cg_r0、cg_r1、cg_r2、cg_r3、cg_r4及cg_r5接收参考序列信号。感测放大器(感测电路140)连接至位线bl,并且产生其串行化输出so至连接至累加器(累加器电路150)的线。累加器(累加器电路150)配置为累加串行化的部分和(serialized partial sums)以产生累加器输出(accumulator output)ao。

44.值得一提的是,主突触阵列120及参考突触阵列130的数量可以大于一个,并且沿着行及列扩展。主突触阵列120及参考突触阵列130中的一个或两者可以根据各种特定的技术需求,以行或列的单一或多种形式布置。在此,主突触阵列120包含四个突触存储元件wa、wb、wc及wd,并且参考突触阵列130包含六个参考元件r0、r1、r2、r3、r4及r5。虽然图3中的主突触阵列120及参考突触阵列130描述为分别具有四个或六个存储元件,但是其可以根据存储元件用于储存权重值的容量以及阵列的可用面积,而包含多于或少于在此所述的存储元件。

45.在两个阵列主突触阵列120及参考突触阵列130中的突触存储元件以串联连接,并且共享通用位线bl。主突触阵列120及参考突触阵列130中的各突触存储元件可以储存固定或可调的突触权重并且产生输出,其为输入乘以权重的函数。进一步地,在本发明的一种实施方式中,通过信号线(信号线cg_wa、cg_wb、cg_wc及cg_wd)施加至多个存储元件的各输入具有特定的时间间隔。因此,对应于输入的输出电流将以特定的时间间隔分别在位线bl上流动。

46.主突触阵列120中的突触存储元件的总量可以根据各存储元件的容量而调整。举例来说,当将8位权重分配至主突触阵列120时,且如果可用存储元件可以储存具有四个逻辑状态的两位信息,则主突触阵列120可能总共需要四个存储元件以执行相关的乘法运算。然而,如果主突触阵列120可以储存具有十六个逻辑状态的四位信息,则主突触阵列120可能只需要两个存储元件。并且,如果各存储元件储存具有两个逻辑状态的1位信息,则需要八个突触存储元件。

47.图3标出设置有8位权重的情形;各存储元件配置为储存2位信息;因此,主突触阵列120中总共布置有4个存储元件以执行相关的对应乘法。在一种实施方式中,参考突触阵列130包含一组参考元件r0、r1、r2、r3、r4及r5。这些参考元件r0、r1、r2、r3、r4及r5可以与主突触阵列120中的存储元件相同或者相似。这些参考元件r0、r1、r2、r3、r4及r5分别耦接至参考信号线(例如,参考信号线cg_r0至参考信号线cg_r5),并且共享通用位线bl。各参考元件r0、r1、r2、r3、r4及r5在输出线bl上输出特定的参考电流,因为当经由对应的信号线接收电压时,各参考元件r0、r1、r2、r3、r4及r5具有其自己的特定突触权重。在此,参考突触阵

列130中的六个参考元件r0、r1、r2、r3、r4及r5中的每一个可以设定为产生渐增的不同电流(incrementally different current)。例如,从字符串的最高位至最低位的顺序,启动(activated)的参考元件r5配置为输出6μa;启动的参考元件r4可以输出5μa;启动的参考元件r3可以输出4μa;启动的参考元件r2可以输出3μa;启动的参考元件r1可以输出2μa;并且,启动的参考元件r0可以输出1μa。

48.感测电路140可以确认在位线bl中感测到的输出电流是否大于或小于阈值,其为控制器110所定义的预定值或校准值。在一种实施方式中,关于主突触阵列120中的突触存储元件与参考突触阵列130中的参考元件(或称参考存储元件)之间的交互作用,控制器110可以被配置为:

49.1.选择主突触阵列120中的突触存储元件之间的操作的顺序以进行启动。

50.2.定义一组参考突触位准(通过零个、一个或多个参考突触存储元件获得的输出电流设定值)。

51.3.选择性地操作参考突触阵列130中的参考元件,使得选择性组合的参考元件(selectively combined reference cells)可以同时产生与所定义的参考位准相同电流的输出电流。

52.4.在主突触阵列120中选定的突触存储元件正在处理中(under progress)之时控制参考元件的操作。

53.5.通过在参考突触阵列130中不启动参考元件中的任何一个、选择性地启动部分的参考元件或者启动的所有参考元件,以取得(pursue)通过参考位准设定的位线bl中的各个不同的电流。

54.在另一种实施方式中,根据所储存的默认顺序,控制器110可以以预定顺序逐个提供序列操作输入及参考信号至主突触阵列120及参考突触阵列130。这些存储元件的依序启动为预先确定的,或者可以由使用者重新设置。通过选择性地在信号在线施加电压输入,控制器110控制选定的主突触存储元件(例如,权重a)以产生输出,其为输入乘以储存在主突触存储元件中参数的函数。控制器110同步化参考元件组的启动与选定权重存储元件的操作。也就是说,当选定的突触存储元件产生对应于经由信号线施加的输入电压的输出电流时,控制器110可以逐步启动参考元件组(参考元件r0至参考元件r5)。可以一起启动多个突触列,以使累加电流流经位线bl。

55.图4为根据本发明的一种实施方式的图1的计算电路的操作的时序图。

56.在此,从图式的顶部到第四行表示信号线(信号线cg_wd、cg_wc、cg_wb及cg_wa),信号线携带用于主突触阵列120中的存储元件(突触存储元件wa、wb、wc及wd)的3位输入信号。3数元输入值(3-digit input value)通过最高有效位(most significant bit,msb)、中心有效位(center significant bit,csb)及最低有效位(least significant bit,lsb)表示。此外,第五列(标为“cg_r5”)与图式底部(标为“cg_r0”)之间的六个行中的每一行示出了经由信号线(信号线cg_r5、cg_r4、cg_r3、cg_r2、cg_r1及cg_r0)分别输入至参考元件组(参考元件r5、r4、r3、r2、r1及r0)的串行二进制输入数据。

57.在一种实施方式中,控制器110依序启动零个、一个或多个参考元件(参考元件r0、r1、r2、r3、r4及r5),以在位线bl中产生预定义的参考突触位准,而选定存储元件(突触存储元件wd、wc、wb及wa)中的一个接收3位输入信号以产生对应的输出电流,此输出电流为3位

输入乘以储存在存储元件中的权重的函数。

58.更具体的是,在时间段t1期间,控制器110传送占用最高有效位(in_msb)的二进制输入至突触存储元件wd,以通过位线产生二进制输入乘以储存在突触存储元件wd中的权重的电流。在时间段t2期间,控制器110通过信号线cg_wd传送占用中间有效位(in_csb)的二进制输入至突触存储元件wd,且因此,突触存储元件wd通过位线产生二进制输入乘以储存在突触存储元件wd中的权重的电流。在时间段t3期间,控制器110通过信号线cg_wd传送占用最低有效位(in_lsb)的二进制输入至突触存储元件wd,且因此,突触存储元件wd通过位线产生二进制输入乘以储存在突触存储元件wd中的权重的电流。在时间段t4至时间段t6期间执行发送3位输入信号至突触存储元件wc;在时间段t7至时间段t9期间执行发送3位输入信号至突触存储元件wb;并且,在时间段t10至时间段t12期间执行发送3位输入信号至突触存储元件wa。如图4所示,所执行的对突触存储元件wa、wb及wc的3位输入信号的传输与上述对突触存储元件wd的3位输入信号的传输相似。

59.如图4所示,当时间段t1被分割为7个子时间段t1至子时间段t7时,控制器110可以控制与7个子时间段中的每一个相对应的零个、一个或多个参考元件组(参考元件r0、r1、r2、r3、r4及r5)的操作。换句话说,控制器110可以传送信号组至参考元件组(参考元件r0、r1、r2、r3、r4及r5),使得具有信号1的参考元件被共同启动以在位线bl中设定电流的预定参考突触位准,上述电流为添加至来自选定参考元件的输出电流,选定参考元件为被3位输入信号启动的突触存储元件wd、wc、wb及wa中的一个。在用于参考元件(参考元件r5、r4、r3、r2、r1及r))的二进制序列输入数据中,“1”表示赋能信号,而“0”表示对应参考元件的闲置信号。

60.在子时间段t1期间,控制器操作突触存储元件wd(通过提供in_msb输入信号)以及参考元件r5(通过提供赋能1数据信号)以输出。因此,在子时间段t1期间产生这些参考元件的输出电流的总和。并且,在子时间段t2至子时间段t7中的每一个时间段期间,控制器110持续传输in-msb输入信号至突触存储元件wd,并且使得能够依序操作参考元件r4、r3、r2、r1、r0及无以输出对应的输出电流。

61.在时间段t2期间,控制器110传送in_csb信号至突触存储元件wd并依序传输输入信号1至参考元件r5至参考元件r0中的每一个,并且在构成时间段t2的子时间段t8至t14期间传送所有“0”至参考元件。在时间段t3期间,控制器110传送in_lsb信号至突触存储元件wd并依序传输输入信号1至参考元件r5至参考元件r0中的每一个,并且在构成时间段t3的子时间段t15至子时间段t21期间传送所有“0”至参考元件。并且,控制器110在剩余的时间段t4至时间段t12中,将与在时间段t1至时间段t3期间所执行的控制器操作的相同方式应用于剩余的存储元件(突触存储元件wc、wb及wa)。

62.图5为说明根据本发明一种实施方式的串行化感测操作的过程的流程图。应注意的是,在神经网络计算单元100中多个主突触阵列120及多个参考突触阵列130排列成多列及多行。应注意的还有,主突触阵列120及参考突触阵列130中存储元件的数量为控制器110或者用户通过与神经网络计算单元100相关联的接口(未示出)以预先设置或确定的。

63.在步骤501中,感测电路140设定为“开启(on)”模式以开始感测/校正操作。在步骤503中,主突触位准表示主突触阵列120中对应的突触存储元件所获得的特定输出电流。当接收到时,感测电路140可以识别对应于输入(施加至突触存储元件的n位输入中的一个)乘

以储存在选定存储元件中的权重的函数的输出电流量。

64.在步骤505,控制器110可以设定参考突触位准(通过零个、一个或多个的参考元件所获得的一组输出电流值)。为了获取突触位准指定的输出电流,控制器110可以在参考突触阵列130中设定零个、一个或多个的参考元件。当通过组合参考元件获得设定的输出电流时,控制器110可以计算参考元件的理想数量。例如,为了产生3位格式的输出,其为输入(例如,3位输入)乘以储存在主突触阵列120的突触存储元件中的权重的函数,控制器110可以设定总共七个参考突触位准(7个输出电流设定值),并且根据于程序化等式,例如总参考突触位准s=2^(3)-1,即7,以执行相关的操作。控制器110的操作决定(1)执行感测步骤的次数,以及(2)通过预定义的程序代码或者可以根据使用者的需求手动输入实现参考突触位准的数量。

65.在步骤507中,控制器110可以操作主突触阵列120及参考突触阵列130中的存储元件以结合(1)来自参考突触阵列130的输出电流,以及(2)来自主突触阵列120的输出电流。换句话说,由特定的参考突触位准所定义的输出电流被添加至来自位线bl中的主突触阵列120中选定的突触存储元件的输出电流。

66.在步骤509中,感测电路140可以比较在特定时间段t测量的添加输出电流与预设阈值电流值。感测电路140可以储存阈值电流值或者允许使用者输入新的阈值电流值或重设预设阈值电流值。

67.在步骤511中,当发现测量到的输出电流和大于预设阈值时,感测电路140可以将比较结果记录为二进制信号,例如h。相反地,在步骤513中,当发现测量到的输出电流和未大于预设阈值时,控制器110将比较结果纪录为二进制信号,例如l。

68.在步骤515中,感测电路140可以检查所有的预定义参考突触位准是否经过了添加及比较步骤507及509。如图4中所述,例如,当完成与参考元件r5相关联的参考突触位准的添加/比较步骤时,这些步骤将应用于与参考元件r4相关联的参考突触位准,并且接着用于参考元件r3、r2、r1、r0及无。

69.在步骤517中,当发现比较操作并未施加至所有的预设参考突触位准时,感测电路140在重复步骤507至步骤515的操作之前,通过启动不同的参考元件组以继续调整参考突触位准。步骤519为当所有的预设参考突触位准的操作完成时。

70.在步骤519中,已经完成所有选定的主突触存储元件的预设操作。然而,应注意的是,当突触存储元件wd处理3位输入数据的一位(msb)时,在图4中的时间段(例如,t1)期间实现针对相关存储元件的添加、比较及循环步骤。因此,如图4所示,整个步骤501至步骤519可以应用于时间段t2至时间段t12中的每一个。

71.图6为图5中所示的串行化电流位准感测的示例的示意图。在一种实施方式中,感测电路140可以配置为获取以下各项之和:(i)来自主突触阵列120中的一个选定存储元件的电流,以及(ii)如图4所示,在预设时间段(例如,子时间段t1、t2、t3

…

)期间来自参考突触阵列130中的零个、一个或多个参考元件的电流。感测电路140可以根据参考突触位准实施求和比较步骤。在本发明的另一种实施方式中,控制器110可以进一步配置为将比较结果转换为指定的特定二进制码。

72.图6为根据本发明一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。在图6中,突触阵列控制器110通过控制线cg_wa传送in_lsb位输入电压

值high至突触列中选定的突触存储元件wa。并且,如图3所示,存储元件wa输出2μa,其为输出high乘以两位权重的函数。与突触存储元件wa相关联(例如,权重参数的权重位0及1)的cur_wa为2μa。参考单位中的一组参考突触存储元件(参考元件r0、r1、r2、r3、r4及r5)中的每一个皆使用与主突触存储元件相同类型的突触存储元件实现。这些突触存储元件耦接至对应的参考信号线(例如,信号线cg_r0至信号线cg_r5),彼此并联连接,并且共享通用位线。因为当通过对应的信号线接收电压时各参考突触存储元件具有特定的突触权重,各参考突触存储元件在输出线(位线bl)上输出特定参考电流。在此,六个参考突触存储元件中的每一个配置为产生渐增的不同电流。例如,从阵列的顶部至底部的顺序,启动的参考元件r5配置为输出6μa;启动的参考元件r4可以输出5μa;启动的参考元件r3可以输出4μa;启动的参考元件r2可以输出3μa;启动的参考元件r1可以输出2μa;并且,启动的参考元件r0可以输出1μa。感测放大器的阈值位准可以定义为7μa。当通用位线电流位准cur大于阈值位准时,感测电路140的串行化输出so为高。当通用位线电流位准cur未大于阈值位准时,感测电路140的串行化输出so为低。

73.在步骤s1中,感测电路140感测到总电流值8μa(等于2μa的电流位准cur_wa加上6μa的电流位准cur_r5)大于参考阈值位准7μa,且因此产生二进制码high或h的判断结果。接下来,在步骤s2中,感测电路140接续感测到总电流值7μa(等于2μa的电流位准cur_wa加上5μa的电流位准cur_r4)等于参考阈值位准7μa,且因此产生二进制码low或l的判断结果。接下来,在步骤s2中,感测电路140感测到总电流值6μa(等于2μa的电流位准cur_wa加上4μa的电流位准cur_r3)小于参考阈值位准7μa,且因此产生二进制码l的判断结果。接下来,在步骤s4中,感测电路140感测到总电流值5μa(等于2μa的电流位准cur_wa加上3μa的电流位准cur_r2)小于参考阈值位准7μa,且因此产生二进制码l的判断结果。

74.接下来,在步骤s5中,感测电路140感测到总电流值4μa(等于2μa的电流位准cur_wa加上2μa的电流位准cur_r1)小于参考阈值位准7μa,且因此产生二进制码l的判断结果。接下来,在步骤s6中,感测电路140感测到总电流值3μa(等于2μa的电流位准cur_wa加上1μa的电流位准cur_r0)小于参考阈值位准7μa,且因此产生二进制码l的判断结果。接下来,在步骤s7中,感测电路140感测到总电流值2μa(等于2μa的电流位准cur_wa)小于参考阈值位准7μa,且因此产生二进制码l的判断结果。

75.在另一种实施方式中,以这种方式,从感测电路140串行化地感测位线电流位准cur,且因此通过七个步骤以产生序列“hllllll”。尽管在图6中针对特定的感测电路140描述了特定位线中的用于电流位准cur的一个特定序列,但是各感测电路140可以根据各位线电流位准cur以在各串行化输出so节点中产生不同的序列。然后,通过对数量进行计数,可以将温度计码转换为二进制码,并且因为温度计码具有一个高信号,在此处的阵列的行中产生用于温度计码“hllllll”的二进制码“001”。相较于温度计码,二进制码仅需较少的位数以储存相同的信息。然后,可以通过适当的移位以将二进制码适当地累加至累加器电路150的缓存器位置,以更新累加器输出ao。

76.如图6所示,当在输入lsb(in_lsb)与加权位0、1之间进行计算时,不可以进行位(bits)的移位(shift)。当计算为用于输入lsb(in_lsb)及加权位2、3时,可以进行2位移位(2-bit shift)。在输入lsb(in_lsb)与加权位4、5之间进行计算时,可以移位4位。在计算用于输入lsb(in_lsb)及加权位6、7时,可以进行6位移位(6-bit shift)。在输入csb(in_csb)

与加权位0、1之间进行计算时,可以进行1位移位。在输入csb(in_csb)与加权位2、3之间进行计算时,可以进行3位移位。在输入csb(in_csb)与加权位4、5之间进行计算时,可以进行5位移位。在输入csb(in_csb)与加权位6、7之间进行计算时,可以进行7位移位。在输入msb(in_msb)与加权位0、1之间进行计算时,可以进行2位移位。在输入msb(in_msb)与加权位2、3之间进行计算时,可以进行4位移位。在输入msb(in_msb)与加权位4、5之间进行计算时,可以进行6位移位。在输入msb(in_msb)与加权位6、7之间进行计算时,可以进行8位移位。对于权重及输入位的其他精度,可以通过适当的位移位(bit shift)计数以进行类似地串连化地累加。

77.图7为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。如图6中所述,感测电路140根据指定的参考突触位准以执行求和比较步骤。

78.在步骤s1中,当发现输出电流和13μa(包含第一参考突触位准6μa)大于参考阈值7μa时,感测电路140产生二进制码h。接下来在步骤s2中,当发现输出电流和12μa(包含第二参考突触位准5μa)大于参考阈值位准7μa时,感测电路140产生二进制码h。

79.接下来在步骤s3中,当发现输出电流和11μa(包含第三参考突触位准4μa)大于参考阈值位准7μa时,感测电路140产生二进制码h。接下来在步骤s4中,当发现输出电流和10μa(包含第四参考突触位准3μa)大于参考阈值位准7μa时,感测电路140产生二进制码h。

80.接下来在步骤s5中,当发现输出电流和9μa(包含第五参考突触位准2μa)大于参考阈值位准7μa时,感测电路140产生二进制码h。接下来在步骤s6中,当发现输出电流和8μa(包含第六参考突触位准1μa)大于参考阈值位准7μa时,感测电路140产生二进制码h。最后,在步骤s7中,当发现输出电流和7μa(包含第七参考突触位准0μa)等于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。

81.在另一种实施方式中,以这种方式,串行化地从感测电路140感测位线电流位准cur,并通过七个步骤产生序列“hhhhhhl”。通过对数量进行计数,可以将温度计码转换为二进制码,并且因为温度计码具有六个高信号,在此处的行中产生用于温度计码“hhhhhhl”的二进制码“110”。然后,可以通过适当的移位以将二进制码适当地累加至累加器电路150的缓存器位置,以更新累加器输出ao。如图7所示,当在输入lsb(in_lsb)与加权位0、1之间进行计算时,不可以进行位的移位。当在输入lsb(in_lsb)与加权位2、3之间进行计算时,可以进行二位移位。当在输入lsb(in_lsb)与加权位4、5之间进行计算时,可以进行四位移位。当在输入lsb(in_lsb)与加权位6、7之间进行计算时,可以进行六位移位。

82.图8为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。如图6及图7中所述,感测电路140根据指定的参考突触位准以执行求和比较步骤。在此情况下,突触阵列控制器110通过控制线cg_wa传送in_lsb位输入电压值low至突触列中选定的突触存储元件wa。并且,如图3所示,突触存储元件wa的输出接近0μa,其为输入low乘以两位的权重的函数。电流位准cur_wa与突触存储元件wa(例如,权重参数的加权位0及1)相关联。

83.在步骤s1中,当发现总输出电流接近6μa,其仅包第一参考突触位准6μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。接下来在步骤s2中,当发现总输出电流接近5μa,其仅包含第二参考突触位准5μa,而小于参考阈值位准7μa时,感测电路

140产生二进制码l的判断结果。

84.接下来在步骤s3中,当发现总输出电流接近4μa,其仅包含第二参考突触位准4μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。接下来在步骤s4中,当发现总电流值大约为3μa,其仅包含第二参考突触位准3μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。

85.下来在步骤s5中,当发现总电流值大约为2μa,其仅包含第二参考突触位准2μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。接下来在步骤s6中,当发现总电流值大约为1μa,其仅包含第二参考突触位准1μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。接下来,在步骤s7中,当发现总电流值大约为0μa,其仅包含第七参考突触位准0μa,而小于参考阈值位准7μa时,感测电路140产生二进制码l的判断结果。

86.在另一种实施方式中,以这种方式,串行化地从感测电路140感测位线电流位准cur,并且如图8所示,从七个步骤中产生序列“lllllll”。通过对数量进行计数,可以将温度计码转换为二进制码,并且因为温度计码具有零个高信号,因此产生用于温度计码“lllllll”的二进制码“000”。然后,因为此添加不会改变累加器输出ao,所以此二进制码可以不被添加至累加器电路150的缓存器位置。

87.图9为根据本发明另一种实施方式的比较位线中所测量的总电流与一组预设阈值电流的过程的流程图。

88.在此情况中,突触阵列控制器110通过控制线cg_wa传送in_lsb位输入电压值high至突触列中选定的突触存储元件wa。并且,参考突触位准为通过参考突触阵列130中的零个、单个参考元件或者参考元件的组合以获得的。来自参考元件的输出位准为二进制加权的(例如,电流位准cur_r2为电流位准cur_r1的两倍,并且电流位准cur_r1为电流位准cur_r0的两倍)。当使用二进制加权的参考元件时,用于执行与图7相同的操作所需的参考元件的数量从六个(例如,图7中的电流位准cur_r5至电流位准cur_r0)减少至三个(图9中的电流位准cur_r2至电流位准cur_r0)。这样可以减少参考元件阵列所需要的面积,并增加神经网络计算单位的面积效率。

89.在步骤s1中,感测电路140感测到总电流值8μa(包含(i)通过电流位准cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r2、r1的组合以获取的突触位准1的6μa)大于参考阈值位准7μa,并且产生二进制码h的判断结果。在步骤s2中,感测电路140接续感测到总电流值7μa(包含(i)通过电流位准cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r2、r0的组合以获取的突触位准2的5μa)等于参考阈值位准7μa,并且产生二进制码l的判断结果。

90.接下来,在步骤s3中,感测电路140感测到总电流值6μa(包含(i)通过电流位准cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r2以获取的突触位准3的4μa)小于参考阈值位准7μa,并且产生二进制码l的判断结果。接下来,在步骤s4中,感测电路140感测到总电流值5μa(包含(i)通过电流位准cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r1、r0的组合以获取的突触位准4的3μa)小于参考阈值位准7μa,并且产生二进制码l的判断结果。

91.接下来,在步骤s5中,感测电路140感测到总电流值4μa(包含(i)通过电流位准

cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r1以获取的突触位准5的2μa)小于参考阈值位准7μa,并且产生二进制码l的判断结果。接下来,在步骤s6中,感测电路140感测到总电流值3μa(包含(i)通过电流位准cur_wa的突触存储元件的2μa,以及(ii)通过参考元件r0以获取的突触位准6的1μa)小于参考阈值位准7μa,并且产生二进制码l的判断结果。接下来,在步骤s7中,感测电路140感测到总电流值2μa(包含不通过参考元件获取的突触位准7的0μa),其仅包含电流位准cur_wa的2μa,小于参考阈值位准7μa,并且产生二进制码l的判断结果。

92.在另一种实施方式中,以这种方式,串行化地从感测电路140感测位线电流位准cur,并且如图9所示,从七个步骤中产生序列“hllllll”。通过对数量简单地进行计数,可以将温度计码转换为二进制码,并且因为温度计码具有一个高信号,因此在所示的行中产生用于温度计码“hllllll”的二进制码“001”。然后,因为此添加不会改变累加器输出ao,所以此二进制码可以不被添加至累加器电路150的缓存器位置。可以通过适当的移位以将二进制码适当地累加至累加器电路150的缓存器位置,以更新累加器输出ao。如图9所示,当在输入lsb(in_lsb)与加权位0、1之间进行计算时,不可以进行位的移位。当在输入lsb(in_lsb)与加权位2、3之间进行计算时,可以进行二位移位。当在输入lsb(in_lsb)与加权位4、5之间进行计算时,可以进行四位移位。当在输入lsb(in_lsb)与加权位6、7之间进行计算时,可以进行六位移位。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1