一种基于分离字线的四管存内计算装置的制作方法

1.本发明涉及存内计算技术领域,特别是涉及一种基于分离字线的四管存内计算装置。

背景技术:

2.深度卷积神经网络(dcnns)证明了推理精度能够进一步提高,深度学习正在向边缘计算转移。dcnns中最常见的运算是乘法和累加(mac),它控制着功率和延迟。mac操作具有很高的规则性和并行性,因此非常适合硬件加速。然而,内存访问量严重限制了传统数字加速器的能源效率,因此,内存计算(imc)对dcnn加速越来越有吸引力。

3.现在的存内计算单元基本都是基于六管或者更多管子,显然上述结构面积大、计算过程较慢且功耗也很大。

技术实现要素:

4.本发明的目的是提供一种基于分离字线的四管存内计算装置,以加速计算过程,减小结构面积。

5.为实现上述目的,本发明提供了一种基于分离字线的四管存内计算装置,所述装置包括:列译码驱动器、行译码驱动器、存内计算阵列、n个开关和n个模拟数字转换器;所述存内计算阵列包括阵列设置的m

×

n个存内计算位单元;所述列译码驱动器的n个第一位线端分别与n根位线bl连接;所述列译码驱动器的n个第二位线端分别与n根位线blb连接;所述行译码驱动器的m个第一字线端分别与m根字线wll连接;所述行译码驱动器的m个第二字线端分别与m根字线wlr连接;第j+1列的m个存内计算位单元对应的第一位线端均与第j根位线bl连接,第j+1列的m个存内计算位单元对应的第二位线端均与第j根位线blb连接,第i+1行的n个存内计算位单元对应的第一字线端均与第i根字线wll连接,第i+1行的n个存内计算位单元对应的第二字线端均与第i根字线wlr连接;其中,i为大于等于0且小于m的正整数,j为大于等于0且小于n的正整数;第j个开关与第j根位线blb连接,第j个模拟数字转换器的第一输入端分别与第j个开关和第j根位线bl连接;所述存内计算位单元包括:晶体管t1、晶体管t2、晶体管t3和晶体管t4;晶体管t1的源极和晶体管t2的源极均与电源连接,晶体管t1的漏极与晶体管t2的栅极连接,晶体管t1的栅极与晶体管t2的漏极连接;晶体管t3的源极与位线bl连接,晶体管t3的漏极与晶体管t1的栅极连接,晶体管t3的栅极与字线wll连接;晶体管t4的源极与位线blb连接,晶体管t4的漏极与晶体管t2的栅极连接,晶体管

t4的栅极与字线wlr连接。

6.可选地,所述晶体管t1和晶体管t2均为pmos,晶体管t3和晶体管t4均为nmos。

7.可选地,当输入激活信号为+1时,字线wll为vdd,字线wlr为0;当输入激活信号为

‑

1时,字线wll为0,字线wlr为vdd;其中,vdd=1v。

8.可选地,当q=0时,权重值为

‑

1;当q=vdd时,权重值为+1,其中,vdd=1v,q为晶体管t1的栅极、晶体管t2的漏极与晶体管t3的漏极的公共点。

9.可选地,当输入激活信号为+1且权重值为+1时,则对位线bl进行充电;当输入激活信号为

‑

1且权重值为+1时,则对位线blb进行放电;当输入激活信号为+1且权重值为

‑

1,则对位线bl进行放电;当输入激活信号为

‑

1且权重值为

‑

1,则对位线blb进行充电。

10.根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明中存内计算位单元采用4个晶体管进行存内计算,进一步优化了阵列结构,减小了阵列面积,而且此装置直接节省了计算电路,使用两条字线的结构来实现字线分离,进一步降低了存算装置的面积,同时实现快速推理时间和鲁棒性。

附图说明

11.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

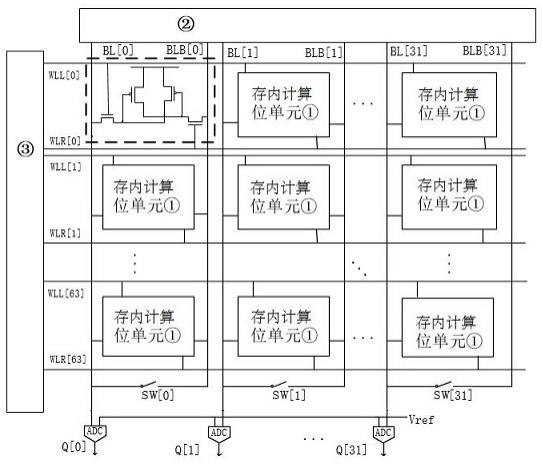

12.图1为本发明存内计算装置结构示意图;图2为本发明存内计算位单元结构示意图。

具体实施方式

13.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

14.本发明的目的是提供一种基于分离字线的四管存内计算装置,以加速计算过程,减小结构面积。

15.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

16.如图1所示,本发明公开一种基于分离字线的四管存内计算装置,所述装置包括:列译码驱动器

②

、行译码驱动器

③

、存内计算阵列、n个开关和n个模拟数字转换器;所述存内计算阵列包括阵列设置的m

×

n个存内计算位单元

①

。列译码驱动器

②

具有列译码功能和读/写位线控制功能;行译码驱动器

③

具有行译码功能和字线驱动功能。

17.所述列译码驱动器

②

的n个第一位线端分别与n根位线bl连接;所述列译码驱动器

②

的n个第二位线端分别与n根位线blb连接;所述行译码驱动器

③

的m个第一字线端分别与m根字线wll连接;所述行译码驱动器

③

的m个第二字线端分别与m根字线wlr连接;第j+1列的m个存内计算位单元

①

对应的第一位线端均与第j根位线bl(即位线bl[j])连接,第j+1列

的m个存内计算位单元

①

对应的第二位线端均与第j根位线blb(即位线blb[j])连接,第i+1行的n个存内计算位单元

①

对应的第一字线端均与第i根字线wll(即位线wll[i])连接,第i+1行的n个存内计算位单元

①

对应的第二字线端均与第i根字线wlr(即位线wlr[i])连接;其中,i为大于等于0且小于m的正整数,j为大于等于0且小于n的正整数;第j个开关(即sw[j])与第j根位线blb(即blb[j])连接,第j个模拟数字转换器(即q[j])的第一输入端分别与第j个开关和第j根位线bl连接,第j个模拟数字转换器的第二输入端与给定值vref连接,最终累积电压通过第j个模拟数字转换器的输出端输出。

[0018]

本发明的存内计算装置可在两种模式下工作:第一种为权重存取的存取模式。第二种为二进制乘累加bmac操作的计算模式。

[0019]

在存取模式中,存内计算装置的读/写操作与常规6t sram单元的读/写操作相同。即:地址信号经过所述行译码驱动器

③

译码后输入到字线wll[i]和字线wlr[i],并对第i+1行n个存内计算位单元

①

选中,所述列译码驱动器

②

输出的位线bl[j]和位线blb[j]对第j+1列m个存内计算位单元

①

选中,位线bl[j]和位线blb[j]闭合开关sw[j],以使第i+1行第j+1列的存内计算位单元

①

计算的电压输入到位线bl[j]上和位线blb[j]上进行电压合并后通过模拟数字转换器q[j]的输出端输出。

[0020]

在计算模式下,m行存内计算位单元

①

同时被激活,每行输入激活信号input被预编码为字线wll和字线wlr,权重值存储在各存内计算位单元

①

中。当输入激活信号input[i]为'+1 '时,相应的字线wll[i]被置为' 1 ',相应的字线wlr[i]被置为' 0 '。当输入激活信号input[i]=

ꢀ‘‑1’

时,字线wll[i] 被置为 0,字线wlr[i]被置为 1。位线bl[j]和位线blb[j]被预充电为0.5v。当输入激活信号input[i]和权重值之间的乘运算结果为“+1”时,对位线bl[j]或位线blb[j]充电,当结果为

’‑1’

时,则对位线bl[j]或位线blb[j]放电,第j+1列的乘积结果以电压形式累加在位线bl[j]和位线blb[j]上。然后打开开关sw[j],将位线bl[j]和位线blb[j]上的电压合并后生成总电压值vbl[j]通过模拟数字转换器q[j]的输出端进行数字化输出。本发明多个位线bl被并行输出,实现完全并行计算和高吞吐量。

[0021]

如图2所示,所述存内计算位单元

①

包括:晶体管t1、晶体管t2、晶体管t3和晶体管t4;晶体管t1的源极和晶体管t2的源极均与电源vdd连接,晶体管t1的漏极与晶体管t2的栅极连接,晶体管t1的栅极与晶体管t2的漏极连接;晶体管t3的源极与位线bl连接,晶体管t3的漏极与晶体管t1的栅极连接,晶体管t3的栅极与字线wll连接;晶体管t4的源极与位线blb连接,晶体管t4的漏极与晶体管t2的栅极连接,晶体管t4的栅极与字线wlr连接。q为晶体管t1的栅极、晶体管t2的漏极与晶体管t3的漏极的公共点,qb为晶体管t2的栅极、晶体管t1的漏极与晶体管t4的漏极的公共点。

[0022]

存内计算位单元

①

计算时包括以下步骤:第一步预充电使位线bl[j]、位线blb[j]充电至0.5v,第二步充电关闭,输入激活信号通过行译码驱动器

③

传输到字线wll[i]/wlr[i],输入的激活信号与权重值的乘结果在位线bl[j]/blb[j]上产生充放电;第三步通过模拟数字转换器q[j]进行模数转换后输出结果,具体乘累加操作数表如表1所示。

[0023]

表1 乘累加操作数表

如表1所示,input为输入激活信号,weight为权重值,value为两部分合并后的电压值,q为晶体管t1的栅极、晶体管t2的漏极与晶体管t3的漏极的公共点。表1中以字线wll和字线wlr的电平高低组合来表示输入激活信号input的数值,当输入激活信号为+1时,字线wll端电压为vdd(1v),字线wlr为0v;当输入激活信号为为

‑

1 时,字线wll端电压为0v,字线wlr为vdd;当输入激活信号为0时,字线wll与字线wlr都为vrst,即0.5v。当q=0时,权重值为

‑

1;当q=vdd时,权重值为+1。当输入激活信号为+1且权重值为+1时,则对位线bl进行充电,此时value电压值为1;当输入激活信号为

‑

1且权重值为+1时,则对位线blb进行放电,此时value电压值为

‑

1;当输入激活信号为+1且权重值为

‑

1,则对位线bl进行放电,此时value电压值为

‑

1;当输入激活信号为

‑

1且权重值为

‑

1,则对位线blb进行充电,此时value电压值为1。

[0024]

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

[0025]

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1