闪存及其写入方法与流程

1.本发明是有关于一种闪存及其写入方法,且特别是有关于一种可执行擦除时编程动作的闪存及其写入方法。

背景技术:

2.在或非门闪存中,执行擦除动作的速度,远低于执行编程动作的速度。而在于物联网的应用上,针对闪存以进行所谓的空中固件的更新(on-the-air firmware update),是一个很重要的功能。因此,如果可以有效降低闪存所进行的数据更新所需的时间,将可有效的降低闪存的内容因电源的丧失或有缺陷的软件版本而产生的风险。

技术实现要素:

3.本发明提供一种闪存及其写入方法,通过执行擦除时编程动作以加速存储器的数据写入速度,并可节省功率消耗。

4.本发明的闪存包括多个存储区块以及多个多任务电路。存储区块区分为多个存储库。多任务电路分别耦接至存储库。各多任务电路用以传送多个擦除电压或多个编程电压以使对应的各存储库执行擦除动作或编程动作。其中,依据擦除时编程指令,当存储库的其中之一执行擦除动作时,存储库的其中之另一执行编程动作。

5.本发明的闪存的写入方法包括:区分多个存储区块为多个存储库;提供多个多任务电路以分别对应至存储库,使各多任务电路传送多个擦除电压或多个编程电压以使对应的各存储库执行擦除动作或编程动作;以及,依据擦除时编程指令,使些存储库的其中之一执行擦除动作时,并使存储库的其中之另一执行该编程动作。

6.基于上述,本发明通过使存储区块被区分为多个存储库。并通过多任务电路提供不同的电压供应管道,依据擦除时编程指令提供其中之一的存储库多个擦除电压以执行擦除动作,并提供多个编程电压以使其中之另一的存储库以执行编程动作。在本发明实施例中,不同的存储库间,可分别同步执行编程动作以及擦除动作,有效降低存储器写入所需的时间。

附图说明

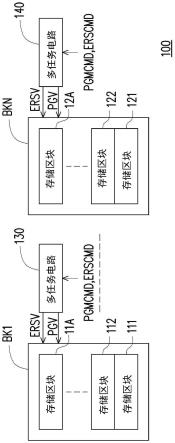

7.图1a绘示本发明一实施例的闪存的示意图。

8.图1b绘示本发明一实施例的闪存芯片的方块图。

9.图2a至图2c的本发明实施例的存储区块区分方式的示意图。

10.图3绘示本发明另一实施例的闪存的示意图。

11.图4a、图4b绘示的本发明实施例的闪存中的多任务电路的多个实施方式的示意图。

12.图5绘示本发明实施例的闪存中,对应不同存储库的多个多任务电路的实施方式的示意图。

13.图6绘示本发明实施例的闪存执行擦除时的写入动作的动作流程图。

14.图7绘示本发明一实施例的闪存的写入方法的流程图。

15.图8绘示本发明另一实施例的闪存的写入方法的流程图。

16.图9绘示本发明一实施例的闪存以及主机芯片的方块图。

17.【符号说明】

18.100、300:闪存

19.111~11a、121~12a、2101~2116:存储区块

20.2101-l~2108-l、2101-r~2108-r:子区块

21.130、140、321、322、400、510、520:多任务电路

22.331、332:位线选择开关驱动器

23.341、342:字线驱动器

24.351、361、352、362:驱动器

25.bk1、bk2、bkn:存储库

26.ersv:擦除电压

27.mx11~mx56、mx11a~mx56a、mx11b~mx56b:电压选择器

28.pgv:编程电压

29.pgmcmd:编程指令

30.erscmd:擦除指令

31.vdd:电源电压

32.vss:参考接地电压

33.vpcp、vpcp_bk1、vpcp_bk2:正向升压电压

34.vncp、vncp_bk1、vncp_bk2:负向升压电压

35.vpcp_inh:正向屏蔽电压

36.vncp_inh:负向屏蔽电压

37.rdp:读取电压

38.spwi:选中pwi区

39.dspwi:未选中pwi区

40.gwl:全区字线标识

41.lwl:区域字线标识

42.s601~s6130、s710~s730:步骤

具体实施方式

43.请参照图1a,图1a绘示本发明一实施例的闪存的示意图。闪存100包括多个存储区块111~11a、121~12a以及多个多任务电路130、140。其中,存储区块111~11a被区分为存储库bk1,存储区块121~~12a则被区分为存储库bkn。多任务电路130、140分别耦接至存储库bk1、bkn。各多任务电路130、140用以传送多个擦除电压ersv或多个编程电压pgv以使对应的各该存储库执行一擦除动作或一编程动作。

44.在本实施例中,多任务电路130、140可依据编程指令pgmcmd或擦除指令erscmd以传导合适的操作电压。多任务电路130、140的其中之一可依据擦除指令erscmd来使对应的

存储库(存储库bk1及bkn的其中之一)执行擦除动作,并且,多任务电路130、140的另一可同时依据编程指令pgmcmd来使对应的存储库(存储库bk1及bkn的其中之另一)执行编程动作。

45.举例来说明,以下请同步参照图1a以及图1b,其中图1b绘示本发明一实施例的闪存芯片的方块图。闪存芯片102包括地址产生器1021、数据缓存器1022、模式逻辑电路1023、频率产生器1024、静态存储器缓冲器1025、状态机1026、高电压(hv)产生器1027、感测放大器1028、输出缓冲器1029、存储器阵列1030、x译码器1031以及y译码器1032。输出缓冲器1029通过输入输出接口电路1033来输出信号so或信号sio0~sio3。数据缓存器1022以及模式逻辑电路1023可通过输入输出接口电路1033来接收信号si、sio0~sio3、wp#、hold#、reset#以及cs#。在此,图1a中的多任务电路130、140可以为高电压产生器1027、x译码器1031以及y译码器1032的部分电路。模式逻辑电路1023可决定通过输入输出接口电路1033所接收的命令并将命令传送至状态机1026以产生指令来据以操作闪存芯片102。

46.当闪存芯片102接收到擦除指令erscmd,多任务电路130可提供擦除电压ersv至存储库bk1,并使存储库bk1可执行擦除动作。在此同时,如果编程指令pgmcmd伴随着非存储库bk1(被擦除的存储库)的地址(例如对应存储库bkn)被接收,多任务电路140可提供编程电压pgv至存储库bkn,以使存储库bkn可执行编程动作。在此请注意,在本范例中,对应存储库bk1以及bkn可分别设置多个状态标识以记录多个记行中的位。以存储库bk1为范例,一个状态标识记录对应的存储库bk1的进行中的一擦除状态,另一个状态标识记录对应的存储库bk1的进行中的一编程状态。多任务电路130、140可依据状态标识数值,来使对应的存储库bk1、bkn执行擦除动作或编程动作。

47.特别值得注意的,在本发明实施例中,承继上述的范例,由于存储库bkn的编程动作,是与存储库bk1的擦除动作同步被执行的。在擦除动作需要相对长的操作时间的前提下,存储库bkn的编程动作并不需要额外的操作时间。也因此,存储库bkn的编程动作不需要急于完成,而可以通过降级式编程(degraded program)动作来进行。在此,所谓降级式编程动作,是通过使被编程的存储单元的位数减少,及/或减低(相对于一般式的编程动作)产生热载子注入效应的编程电压的电压值,并从而减低编程动作中所需的编程电流,并使编程电流可以小于一期望值(期望值可等于一般式的编程动作所需的编程电流的电流值),可有较减低功率耗损。

48.关于本发明实施例中,存储区块的区分方式,可参照图2a至图2c的本发明实施例的存储区块区分方式的示意图。在图2a中,闪存中具有实体地址连续的存储区块2101~2116。存储区块2101~2116可区分为存储库bk1以及bk2。其中,在图2a的实施方式中,存储库bk1可以包括实体地址连续的存储区块2101~2108,存储库bk2则可以包括实体地址连续的存储区块2109~2116。

49.在图2b中,存储库bk1与存储库bk2分别包括的多个存储区块中,彼此间的实体地址可以是相互交错的。例如,依据存储区块2101~2116的实体地址的排列顺序,存储库bk1中可包括第奇数个的存储区块2101、2103...、2015;存储库bk1中则可包括第偶数个的存储区块2102、2104...、2016。存储库bk1、bk2可以交错配置方式进行安排,如果连续地址的存储区块通过擦除以及后编程动作进行更新,上述的交错配置在应用编程中擦除操作是有帮助的。也就是说,在闪存中,在进程中(in progress),个别的分别执行编程操作以及擦除操作是可以达到的。

50.此外,在图2c中,对应图2a的实施方式,存储库bk1中所包括的各存储区块2101~2108,可区分为多个子区块2101-l、2101-r~2108-l、2108-r;存储库bk2中所包括的各存储区块2109~2116,可区分为多个子区块2109-l、2109-r~2116-l、2116-r。在集成电路的实体布局上,以存储库bk1为范例,子区块2101-l~2108-l可以设置在对应的多任务电路的第一侧边,子区块2101-r~2108-r则可以设置在对应的多任务电路的第二侧边,第一侧边与第二侧边是相对的。

51.以下请参照图3,图3绘示本发明另一实施例的闪存的示意图。闪存300一或非门(nor)闪存。闪存300的多个存储区块可区分为存储库bk1以及存储库bk2。闪存300包括分别对应存储库bk1、bk2的多任务电路321以及322。存储库bk1中另包括位线选择开关驱动器331、字线驱动器341以及用以分别驱动n型深阱中的p型阱区(p-type well inside deep n-type well,pwi区)以及n型深阱区(deep n-type well,nwd区)的驱动器351及361。存储库bk2中则另包括位线选择开关驱动器332、字线驱动器342以及用以分别驱动pwi区以及nwd区的驱动器352及362。

52.另外,多任务电路321用以提供擦除电压ersv或编程电压pgv至位线选择开关驱动器331、字线驱动器341以及驱动器351及361,以使存储库bk1中的多个存储区块执行擦除动作或编程动作。多任务电路322用以提供擦除电压ersv或编程电压pgv至位线选择开关驱动器332、字线驱动器342以及驱动器352及362,以使存储库bk2中的多个存储区块执行擦除动作或编程动作。其中,位线选择开关驱动器331、332用以控制多个位线开关的开启或关闭;字线驱动器341、342分别提供多个字线电压至多条字线;驱动器351、352用以提供偏压至多个pwi区,驱动器361、362用以提供多个偏压至多个nwd区。

53.关于多任务电路321、322的实施细节,可参照图4a、图4b绘示的本发明实施例的闪存中的多任务电路的多个实施方式的示意图。在图4a、图4b中,多任务电路400包括多个电压选择器mx11~mx56。多任务电路400接收电源电压vdd、参考接地电压vss、正向升压电压vpcp、负向升压电压vncp、正向屏蔽电压vpcp_inh、负向屏蔽电压vncp_inh以及读取电压rdp。

54.在图4a中,多任务电路400执行编程动作。在此时,多任务电路400通过电压选择器mx11~mx56来针对电源电压vdd、参考接地电压vss、正向升压电压vpcp、负向升压电压vncp、正向屏蔽电压vpcp_inh、负向屏蔽电压vncp_inh以及读取电压rdp进行选择,并输出电源电压vdd、正向升压电压vpcp、负向屏蔽电压vncp_inh以及参考接地电压vss以作为多个编程电压。

55.细节上来说明,在多任务电路400对应的存储区块中,具有选中pwi区spwi以及多个未选中pwi区dspwi。在对应选中pwi区spwi的部分,通过电压选择器mx41、mx31、mx21、mx11形成的第一路径,多任务电路400通过电压选择器mx11的输出,来提供正向升压电压vpcp至选中pwi区spwi中的选中存储单元的字线。对应图3的实施例,电压选择器mx11输出的正向升压电压vpcp可先被提供至字线驱动器341,并从而驱动选中存储单元的字线。另外,通过电压选择器mx42、mx32、mx12形成的第二路径;通过电压选择器mx42、mx32、mx22、mx13形成的第三路径;以及电压选择器mx42、mx32、mx22、mx14形成的第四路径,多任务电路400可分别提供负向屏蔽电压vncp_inh至选中pwi区spwi中的未选中存储单元的字线。其中上述的四个路径可以通过译码存储单元的字线对应的全区字线标识gwl以及区域字线标识

lwl来对应,并通过对应的路径以接收正向升压电压vpcp或负向屏蔽电压vncp_inh对应关系如下表1所示:

56.gwllwl对应的路径11第一路径10第二路径01第三路径00第四路径

57.表1

58.其中,上述第一路径所连接的存储单元为选中存储单元,第二路径至第四路径所连接的存储单元,皆为未被选中存储单元。

59.另外,在对应未选中pwi区dspwi的部分,通过电压选择器mx34、mx15形成的第五路径;通过电压选择器mx34、mx16形成的第六路径;通过电压选择器mx34、mx17形成的第七路径;通过电压选择器mx34、mx18形成的第八路径以输出参考接地电压vss。基于未选中pwi区dspwi中的存储单元皆为未选中存储单元,因此,可通过上述的第七路径至第八路径以提供参考接地电压vss至未选中pwi区dspwi中的所有的未选中存储单元的字线。

60.在另一方面,电压选择器mx51选择正向升压电压vpcp来进行输出,并通过传送至对应的位线选择开关驱动器以导通选中位线选择开关。电压选择器mx52选择参考接地电压vss以进行输出,并从而切断未选中位线选择开关。电压选择器mx53选择电源电压vdd进行输出,并通过对应的驱动器,以驱动选中nwd区。电压选择器mx54选择参考接地电压vss以进行输出,并通过对应的驱动器,以驱动选中pwi区。电压选择器mx55、mx56分别选择电源电压vdd、参考接地电压vss以进行输出。其中电压选择器mx55、mx56的输出用以分别驱动未选中nwd区以及未选中pwi区。

61.以下,在图4b中,多任务电路400用以执行擦除动作。在此时,多任务电路400通过电压选择器mx11~mx56来针对电源电压vdd、参考接地电压vss、正向升压电压vpcp、负向升压电压vncp、正向屏蔽电压vpcp_inh、负向屏蔽电压vncp_inh以及读取电压rdp进行选择,并输出电源电压vdd、正向升压电压vpcp、负向升压电压vncp、正向屏蔽电压vpcp_inh以及参考接地电压vss以作为多个擦除电压。

62.细节上来说明,在多任务电路400对应的存储区块中,具有选中pwi区spwi以及多个未选中pwi区dspwi。在对应选中pwi区spwi的部分,通过电压选择器mx42、mx32、mx11形成的第一路径,多任务电路400通过电压选择器mx11的输出,来提供负向升压电压vncp至选中pwi区spwi中的选中存储单元的字线。电压选择器mx11输出的负向升压电压vncp可先被提供至字线驱动器,并从而驱动选中存储单元的字线。通过电压选择器mx42、mx32、mx12形成的第二路径,通过电压选择器mx12的输出,来提供负向升压电压vncp至选中pwi区spwi中的选中存储单元的字线。另外,通过电压选择器mx41、mx31、mx22、mx13形成的第三路径;以及电压选择器mx41、mx31、mx22、mx14形成的第四路径,多任务电路400可分别提供正向屏蔽电压vpcp_inh至选中pwi区spwi中的未选中存储单元的字线。其中上述的四个路径可以通过译码存储单元的字线对应的全区字线标识gwl以及区域字线标识lwl来对应,并通过对应的路径以接收负向升压电压vncp或正向屏蔽电压vpcp_inh对应关系如下表2所示:

63.gwllwl对应的路径

11第三路径、第四路径01第一路径、第二路径

64.表2

65.其中,上述第一路径、第二路径所连接的存储单元为选中存储单元,第三路径、第四路径所连接的存储单元,皆为未被选中存储单元。

66.另外,在对应未选中pwi区dspwi的部分,通过电压选择器mx34、mx15形成的第五路径;通过电压选择器mx34、mx16形成的第六路径;通过电压选择器mx34、mx17形成的第七路径;通过电压选择器mx34、mx18形成的第八路径以输出参考接地电压vss。基于未选中pwi区dspwi中的存储单元皆为未选中存储单元,因此,可通过上述的第七路径至第八路径以提供参考接地电压vss至未选中pwi区dspwi中的所有的未选中存储单元的字线。

67.在另一方面,电压选择器mx51选择参考接地电压vss来进行输出,并通过传送至对应的位线选择开关驱动器以切断选中位线选择开关。电压选择器mx52选择参考接地电压vss以进行输出,并从而切断未选中位线选择开关。电压选择器mx53选择正向升压电压vpcp进行输出,并通过对应的驱动器,以驱动选中nwd区。电压选择器mx54选择正向升压电压vpcp以进行输出,并通过对应的驱动器,以驱动选中pwi区。电压选择器mx55、mx56分别选择电源电压vdd、参考接地电压vss以进行输出。其中电压选择器mx55、mx56的输出用以分别驱动未选中nwd区以及未选中pwi区。

68.以下请参照图5,图5绘示本发明实施例的闪存中,对应不同存储库的多个多任务电路的实施方式的示意图。图5中具有多任务电路510以及520,其中多任务电路510包括电压选择器mx11a~mx56a,多任务电路520则包括电压选择器mx11b~mx56b。在本实施方式中,多任务电路510可执行如图4a所绘示的编程动作,而多任务电路520则可同步执行如图4b所绘示的擦除动作。如此一来,可顺利完成在一存储库执行擦除动作(通过多任务电路520提供擦除电压)的同时,对另一存储库执行编程动作(通过多任务电路510提供编程电压)。可有效减低闪存的数据写入所需的时间。

69.附带一提的,本实施方式中,电压选择器mx41a输出的正向升压电压vpcp_bk1用以提供给对应多任务电路510的存储库;电压选择器mx41b输出的正向升压电压vpcp_bk2用以提供给对应多任务电路520的存储库;电压选择器mx42a输出的负向升压电压vncp_bk1用以提供给对应多任务电路510的存储库;电压选择器mx42b输出的负向升压电压vncp_bk2用以提供给对应多任务电路520的存储库。

70.另外,在图4a至图5的实施方式中,所谓的正向升压电压vpcp是基于一基准电压,通过一升压机制(例如电荷泵(charge pump))的方式来产生的一大于0伏特的电压。负向升压电压vncp同样是基于一基准电压,通过负向的一升压机制(例如电荷泵(charge pump))的方式来产生的一小于0伏特的电压。而正向屏蔽电压vpcp_inh以及负向屏蔽电压vncp_inh则是依据闪存中,适于针对未选中存储单元进行屏蔽的电压值来设计。在本发明中,皆可应用本领域技术人员所熟知的方式来设定并实施,没有特定的限制。

71.另外,电压选择器mx11a~mx56a以及mx11b~mx56b所接收的控制信号,可通过对应闪存所设置的控制器来产生。而关于电压选择器mx11a~mx56a以及mx11b~mx56b的实施细节,则可应用本领域技术人员所熟知的任意的电压选择电路来实施,没有特定的限制。

72.接着请参照图6,图6绘示本发明实施例的闪存执行擦除时的写入动作的动作流程

图。在图6中,步骤s610~s6130用以执行擦除动作,步骤s601~s605则执行编程动作。其中,擦除动作以及编程动作分别应用于不同的存储库。

73.在细节上,在步骤s610中,针对第一存储库的擦除动作被启动,步骤s620中则先执行预编程动作,然后,在步骤s630中设定阶段i=0以及枪数j=0。在此请注意,本实施例的擦除动作是通过多阶段以及多枪的方式来执行的。在此,所谓的一个枪,指的是针对执行擦除动作的存储单元施加一个擦除电压脉冲。而所谓的多阶段多枪的方式,则是针对各个擦除阶段均设置一个目标电压,并在各个擦除阶段中,通过施加一个或多个擦除电压脉冲(枪),来使被擦除的存储单元的阈值电压可以小于所设定的目标电压。并在多个擦除阶段后,可使存储单元的阈值电压小于最终设定的擦除目标电压。

74.接着,在步骤s640中,针对擦除电压的电压值进行设定,并且,在步骤s650以依据步骤s640设定的电压值来对存储单元施加擦除电压脉冲。在此请注意,擦除电压脉冲可以维持一个的时间区间。在这个时间区间中,可同步针对第二存储库执行步骤s601~s605的编程动作。

75.首先,步骤s601可依据先前有无发生编程动作的行为,来判断使否再次的启动编程动作。若判断结果为是,则可直接执行步骤s603以启动编程流程。相对的,若判断结果为非,则在步骤s602中判断是否须执行新的编程动作。在此,若步骤s602的判断结果为是,则执行步骤s603;相对的,若步骤s602的判断结果为否,则执行步骤s670。

76.在此请注意,步骤s603可针对被编程的存储单元施加一次或多次的编程电压脉冲,接着,通过步骤s604以判断被编程的存储单元的阈值电压vt是否已大于编程目标电压。若存储单元的阈值电压vt已大于编程目标电压,表示编程动作已完成,可执行步骤s670。相对的,若存储单元的阈值电压vt在时间区间中未大于编程目标电压,表示编程动作未完成,并通过步骤s605以通过标识方式来进行重试的标示动作。

77.在此请注意,基于步骤s650中,施加擦除电压脉冲的时间区间是有限的,所以,若发生擦除电压脉冲的时间区间不够长以足以完成存储单元的编程动作时,可通过步骤s605的重试的标示动作,以在下一次的擦除电压脉冲被施加的另一时间区间中,来执行未完成的存储单元的编程动作。

78.更值得一提的,当擦除电压脉冲被稳定提供时,闪存对于擦除动作所耗去的电能是相对低的,也因此,在此时同步执行另一存储库的编程动作,不会造成功率过度消耗的问题。

79.而由上述的说明可以得知,本发明实施例中,擦除时编程动作中的编程动作,由于是通过嵌入在擦除动作中执行的,并不需要额外的时间区间。也因此,并不需要非常快速的完成编程动作,而可以通过降级式编程(degraded program)动作来进行,并从而减低编程动作中所需的编程电流,并使编程电流可以小于一期望值,可有较减低功率耗损。

80.步骤s670承继在步骤s650之后,并用以执行擦除验证。在步骤s680中,判断被擦除存储单元的阈值电压vt是否小于此阶段的目标电压v1,或判断j是否大于一预设的最大值。若上述两者判断有一者为是时,则执行步骤s6100,若判断结果皆为否,则执行步骤s690。

81.步骤s690中使j递增1(j++),并执行步骤s650以施加下一次的擦除电压脉冲。

82.步骤s6100则判断被擦除存储单元的阈值电压vt是否小于擦除不小于擦除目标电压,或判断j是否大于最大值。若上述两者判断有一者为是时,则完成擦除动作(步骤

s6130),若判断结果皆为否,则执行步骤s6120,以使i递增1(i++);使j归零;并执行擦除动作的下一个阶段。

83.接着请参照图7,图7绘示本发明一实施例的闪存的写入方法的流程图。其中,步骤s710中区分多个存储区块为多个存储库。并且,在步骤s720中,提供多个多任务电路以分别对应至存储库,使各多任务电路传送多个擦除电压或多个编程电压以使对应的各该存储库执行擦除动作或编程动作。并且,在步骤s730中,依据擦除时编程指令,使存储库的其中之一执行擦除动作时,并使存储库的其中之另一执行编程动作。

84.请参照图8,图8绘示本发明另一实施例的闪存的写入方法的流程图。其中,步骤s810中,主机启动编程中擦除操作(pwe)。主机可以为闪存外的电子装置。在步骤s820中,主机询问闪存是否有任一擦除动作被执行。如果步骤s820中的询问结果为是,pwe操作结束。如果步骤s820中的询问结果为否,执行步骤s830。

85.在步骤s830中,主机发送出伴随着目标存储器区块地址的区块擦除命令,闪存在步骤s840中启动以擦除目标地址的区块。然后,在步骤s850中,主机询问闪存是否有任一编程动作被执行。如过步骤s850的询问结果为是,pwe操作结束。如果步骤s850中的询问结果为否,步骤s860可以被执行。步骤s860中,闪存发出伴随目标区块地址的编程命令,并在步骤s870中检查被编程的地址是否被擦除。

86.如果步骤s870的检查结果为是,pwe操作可以被结束,若如果步骤s870的检查结果为否,闪存在步骤s880中启动以编程目标地址的区块。

87.请参照图9,图9绘示本发明一实施例的闪存以及主机芯片的方块图。闪存910具有与图1b的闪存102相同的硬件架构。主机芯片920耦接至闪存910。闪存910具有包括快闪阵列库0以及快闪阵列库1。快闪阵列库0以及快闪阵列库1的每一具有多个区块(区块0~区块n+2)。主机芯片920具有至串列周边(spi)接口921,串列周边接口921耦接至闪存910的串列周边(spi)接口912以传输一个或多个命令。主机芯片920以及闪存910可用以执行图8的多个步骤,在此,闪存910可以为一闪存芯片。

88.综上所述,本发明提供擦除时编程指令,以使一存储库执行擦除动作时,对另一存储库进行编程动作。在大量数据更新的条件下,通过将可相对快完成的编程动作,插入至具有相对慢速度的擦除动作中,有效降低闪存的写入动作所需的时间。进一步的,本发明实施例可在擦除时编程动作,通过提供降级式编程动作来降低所需要的功率消耗,进一步提升闪存的工作效能。

89.至此,已经结合附图对本公开实施例进行了详细描述。

90.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1