用于双时钟架构的超导RSFQ电路布局方法

用于双时钟架构的超导rsfq电路布局方法

技术领域

1.本发明涉及超导电路领域,尤其涉及一种用于双时钟架构的超导rsfq电路布局方法。

背景技术:

2.超导单磁通量子(single flux quantum,sfq)电路技术被itrs列为极具前景的下一代集成电路技术。超导快速单磁通量子(rapid single flux quantum,rsfq)电路是sfq电路的一种,具有超高速度和超低功耗的优点。研究证实,用亚微米约瑟夫森结(josephson junction,jj)技术制造的简单rsfq电路最高可以工作在770ghz的频率,这种高速是半导体集成电路所难以企及的。而且,在相同工艺条件下,rsfq电路中逻辑门延迟和位操作功耗都比对应的半导体电路低两个数量级。

3.rsfq电路中最基本的器件是由jj构成的超导环,jj是开关元件。与cmos电路不同,rsfq电路的存储部件是电感而不是电容。超导环中的磁通量子化为φ=n*φ0,其中φ0=2.07

×

10

‑

15

wb。信息以磁通量子的形式存储,以sfq电压脉冲的形式传输。脉冲存在表示逻辑“1”,不存在表示逻辑“0”。与cmos电路不同,在rsfq逻辑电路中,几乎所有的逻辑单元都需要时钟驱动,以将存储的磁通量子传播到输出端。由于一个rsfq逻辑门可以看成是一级流水,为此rsfq电路是完全门级流水的电路,而逻辑深度是指带时钟逻辑门的级数。

4.为充分发挥rsfq器件的超高频(几十甚至几百ghz)优势,研究人员提出了适用于rsfq电路的时钟机制,包括时钟跟随数据(clock

‑

follow

‑

data clocking)、零偏差时钟(zero

‑

skew clocking)、并发时钟(concurrent

‑

flow clocking)。其中零偏差时钟是半导体电路中采用的时钟机制,而并发时钟,即时钟和数据沿相同方向流动,是能够获得最高的电路频率的时钟机制。

5.为保证rsfq逻辑门的功能正确,其所有输入端所连接的逻辑门的逻辑深度应相同,该约束称为路径平衡。若扇入门的逻辑深度不同,则应在具有较小逻辑深度的扇入门的输出端插入触发器(d

‑

flip

‑

flops,dff)。因此,rsfq电路的传统设计方法是通过插入大量的触发器来保证电路的正确运行。最近,研究人员提出了使用快、慢时钟信号来实现rsfq电路的新架构,被称为双时钟架构,具体请参见中国专利申请公开cn112116094a。在这种新架构中,通过双时钟来控制数据的流动,使得无需插入任何路径平衡dff就可以确保rsfq电路的正确运行。考虑到典型的rsfq电路中插入的路径平衡dff的数量是普通逻辑门的数倍,因此这种新架构可以节省大量的电路面积和功耗成本。

6.一方面,虽然针对双时钟超导rsfq电路的布局方法已经存在一些研究,但这些工作都是沿用半导体电路的零偏差时钟,没有考虑rsfq电路的并发时钟机制,使得布局后的电路工作频率不够高。另一方面,传统超导rsfq电路(即非双时钟架构的rsfq电路)布局方法,没有考虑双时钟架构中各个逻辑深度的单元数相差很大的电路特点,使得布局后的电路面积开销大。因此现有的布局方法均不适用于双时钟架构超导rsfq电路。

技术实现要素:

7.基于现有技术的上述缺陷,本发明提供一种用于双时钟架构的超导rsfq电路的布局方法,所述电路中除输入io以及输出io之外的逻辑单元总数为n,布局所述电路的芯片的宽高比为α,

8.所述布局方法包括:

9.基于逻辑深度对n个逻辑单元进行初始布局,包括:

10.计算布局列的参考高度

11.从逻辑深度为1开始依次布置逻辑单元,使得每个逻辑深度的单元按照垂直方向递增的顺序依次布置,且每一列的高度不大于h0,不同的逻辑深度从新的一列开始布置;

12.将单元数小于h0的列依序进行合并,且合并后的列的高度不大于h0;以及

13.移除空的列,并输出所述n个逻辑单元在芯片上的初始坐标以及可布局的列;以及

14.基于模拟退火布局框架对所述初始布局进行扰动和优化。

15.优选地,所述基于模拟退火布局框架对所述初始布局进行扰动和优化的步骤包括:

16.计算所述初始布局的代价;

17.对所述初始布局进行扰动,生成新的布局解;

18.计算所述新的布局解的代价,并用代价更低的布局解更新所述n个逻辑单元的坐标值直到得到代价最小的布局解作为最终的电路布局。

19.优选地,所述初始布局还包括:

20.对每一个逻辑深度i,计算所述逻辑深度的单元需要满高度布局的列其中blk_num[i]是逻辑深度为i的单元数,从当前列开始的c列中的每一列都布置h0个未布局的逻辑深度为i的单元,更新每一列的单元数为h0,并将当前列更新为当前列+c。

[0021]

优选地,所述初始布局还包括:

[0022]

将所述逻辑深度为i的剩余的未被布局的blk_num[i]%h0个单元布置在当前列,更新当前列的单元数为blk_num[i]%h0,并将当前列更新为当前列+1。

[0023]

优选地,所述初始布局还包括:

[0024]

将单元数小于h0的列的列编号存储至数组array中,将第array[i+1]~array[i+j]列的单元位置调整到第array[i]列,并将array[i+1]~array[i+j]列的单元数置为0,其中合并之前的array[i]列、array[i+1]列...array[i+j]列的单元数之和≤h0<合并之前的array[i]列、array[i+1]列、...array[i+j]列、array[i+j+1]列的单元数之和。

[0025]

优选地,所述对所述初始布局进行扰动的步骤还包括:

[0026]

将输入io布置在芯片左侧的格点位置,将输出io布置在芯片右侧的格点位置。

[0027]

优选地,所述对所述初始布局进行扰动的步骤还包括:

[0028]

当某一逻辑单元可布局在多个列时,首先在只包含同一逻辑深度的单元的列中随机选择一个列,然后在选中的列上随机选择一个格点位置,将所述某一逻辑单元与所述格点的单元进行交换,并确定新的坐标。

[0029]

优选地,所述对所述初始布局进行扰动的步骤还包括:

[0030]

当某一逻辑单元可布局的列数为1,且与所述某一逻辑单元具有相同逻辑深度的单元数大于1时,则以一定的概率p,将所述某一逻辑单元和与其逻辑深度相同的单元进行交换,并确定新的坐标,其中0≤p≤1。

[0031]

优选地,所述对所述初始布局进行扰动的步骤还包括:

[0032]

当某一逻辑单元可布局的列数为1,且与所述某一逻辑单元具有相同逻辑深度的单元数大于1时,当布局列中存在两个及以上单元数相等且逻辑深度不等的宏模块,则以一定的概率1

‑

p将这两个宏模块整体进行交换,确定宏模块中所有单元的新的坐标,其中0≤p≤1。

[0033]

优选地,所述对所述初始布局进行扰动的步骤还包括:

[0034]

当某一逻辑单元可布局的列数为1,且与所述某一逻辑单元具有相同逻辑深度的单元数为1时,如果布局列上有空位,则将所述某一逻辑单元移动到随机选择的一个空位上,得到新的坐标。

[0035]

本发明还提供一种计算机可读存储介质,其上包含有计算机程序,所述计算机程序可被处理器执行以实现上述一种用于双时钟架构的超导rsfq电路布局方法的步骤。

[0036]

本发明还提供一种电子设备,包括:一个或多个处理器;以及存储器,其中存储器用于存储一个或多个可执行指令;一个或多个处理器被配置为经由执行一个或多个可执行指令以实现上述一种用于双时钟架构的超导rsfq电路布局方法的步骤。

[0037]

本发明的用于双时钟架构的超导rsfq电路布局方法,采用并发时钟,以提高电路的工作频率,并提出基于逻辑深度的初始布局方法和满足逻辑深度约束的布局解扰动方法,以减少电路的面积。相比于已有的超导rsfq电路布局方法,本发明提出的用于双时钟架构的超导rsfq电路的布局方法,可在满足逻辑深度约束的条件下获得面积较优的布局结果,减小电路的面积。而且相比于零偏差时钟,本发明的布局结果由于考虑了单元的逻辑深度,使得布局后的布线阶段更容易实现并发时钟下的时序约束,从而提高电路的工作频率。

附图说明

[0038]

图1a是并发时钟分布网络的示意图;

[0039]

图1b是图1a中的并发时钟分布网络中的两个逻辑门的示例;

[0040]

图2是并发时钟时序约束的示意图;

[0041]

图3是本发明一个实施例的基于格点的芯片布局区域的示意图;

[0042]

图4是本发明一个实施例的4位加法器电路的电路门级网表示意图;

[0043]

图5是采用传统的并发时钟的超导rsfq布局算法得到的图4中的4位加法器电路的布局结果示意图;

[0044]

图6是本发明一个实施例的基于逻辑深度的双时钟超导rsfq电路初始布局算法流程图;

[0045]

图7是图4中的4位加法器电路的初始布局的一个示例;

[0046]

图8是一个含10个端点的线网边界框的示意图;

[0047]

图9是图4中的4位加法器电路的最终布局示意图。

具体实施方式

[0048]

为了使本发明的目的、技术方案以及优点更加清楚明白,下面结合附图通过具体实施例对本发明作进一步详细说明。

[0049]

图1a是并发时钟分布网络的示意图,其中时钟源和数据通过不同的信号网络传输至逻辑门中。图1b是图1a中的并发时钟分布网络中其中两个逻辑门的示例,用于说明并发时钟的时序。如图1b所示,门1和门2是rsfq逻辑门,黑色的圆点101和102是分离器(splitter),简称spl。数据传输至门1,并在时钟脉冲到达门1之后,将数据输出至门2。时钟脉冲传输至spl 101,假设spl 101输出时钟脉冲的时刻为0,则门2的时钟脉冲到达时间(tclk)等于线路2、spl 102和线路3的延迟之和;门2的数据脉冲到达时间(tdata)等于线路1、门1和线路4的延迟之和。

[0050]

对于并发时钟时序,数据脉冲比时钟脉冲更晚到达,即tdata>tclk,在下一个时钟脉冲到达门2时,门2对数据脉冲进行处理并输出。因此,如果数据在具有n级逻辑门的rsfq电路中进行传输,就需要n个时钟周期(n+1个时钟脉冲)。这样,数据就能够在门级流水线之间依次连续地进行处理。在rsfq电路中,并发时钟时序能够获得较高的电路频率。

[0051]

图2是并发时钟时序约束的示意图。在并发时钟的时序设计中,需要满足图2所示的时序约束。其中,t

c

是时钟到达逻辑门的时间,t

d

是数据到达逻辑门的时间,t

cycle

是时钟周期,t

hold

是逻辑门的保持时间(hold time),t

setup

是逻辑门的建立时间(setup time)。在采用并发时钟进行时序设计时,每个逻辑门必须满足时序约束:t

c

+t

hold

<t

d

<t

c

+t

cycle

–

t

setup

。因此在超导rsfq电路布局中,需要通过合理的逻辑单元布局以及布线以满足上述时序约束。在满足上述时序约束的同时还要尽量使得布局更加紧凑,总线长更短,以减小电路的面积。本发明的用于双时钟架构的超导rsfq电路布局方法可以实现基于逻辑深度的布局,使得最终的布局结果易于满足并发时钟时序约束,并且可获得面积较优的布局结果。

[0052]

布局是确定电路中的逻辑单元在芯片上的物理位置的过程,其一般包含两个输入:1)工艺库文件,用于描述逻辑单元的形状、大小、端口位置、时序参数等;2)电路门级网表,用于描述电路中的逻辑单元之间的连接关系。布局的输出是逻辑单元在芯片上的具体坐标位置。本发明采用基于格点的布局方式,逻辑单元只能放置在格点位置,格点之间的区域用于电路的布线。

[0053]

图3是本发明一个实施例的基于格点的芯片布局区域的示意图。图3中的布局包括三个布局列,布局列0、布局列1以及布局列2,每个布局列包括3个格点。图3中的方框表示格点,其用于放置rsfq逻辑单元(即rsfq逻辑器件)。格点的位置由平面直角坐标系中的坐标(x,y)进行定位。例如,左下角的格点位置为(0,0),其表示该格点位于x=0,且y=0的格点位置。

[0054]

图4是本发明一个实施例的4位加法器的电路门级网表示意图,其包括电路输入(cin,a0

‑

a3,b0

‑

b3),即输入io;电路输出(s0

‑

s4),即输出io;以及逻辑单元(g0

‑

g19)。带箭头的线表示电路中的逻辑单元之间的连接关系。图4中的4位加法器电路采用双时钟架构,因此不需要插入dff器件以实现时钟对齐。在本发明中,逻辑深度(level)是指带时钟的逻辑门的级数。一个逻辑单元gi的逻辑深度level(gi)等于其所有输入端所连接的单元g

si

的逻辑深度的最大值加1,即level(gi)=1+max{level(g

si

)}。其中,定义输入io的逻辑深度为0。例如,由于g0的所有输入均为输入io,即max{level(g

s0

)}=0,因此level(g0)=1;再例

如,g8有两个输入,其第一输入来自输入io,而第二输入来自g0,即max{level(g

s8

)}=1,因此level(g8)=2,以此类推。图4中的电路门级网表的20个逻辑单元分为9个逻辑深度,level 1~level 9。最大逻辑深度为level 9。level 1的逻辑单元数量为8个,即g0

‑

g7,level 2的逻辑单元数量为2个,即g8

‑

g9,以此类推。为了清楚起见,图4中的逻辑单元均用圆圈表示,该圆圈可代表不同的rsfq逻辑器件。

[0055]

图5是采用传统的并发时钟的超导rsfq布局算法得到的图4中的4位加法器电路的布局结果示意图。图中的连线仅表示信号的连接关系。由图5可以看出,传统方法是严格将逻辑深度相同的单元摆放在同一个布局列中,如果将该传统方法直接应用于采用双时钟架构的4位加法器电路,会导致电路面积很大,造成空间浪费。

[0056]

本发明提出一种用于双时钟架构的超导rsfq电路布局方法,已有该方向的研究都是采用半导体电路中的零偏差时钟机制,而本发明的布局方法是采用并发时钟,可以获得更高的电路工作频率。同时,本发明允许将不同逻辑深度的单元摆放在同一个布局列,可以减小电路的面积开销。

[0057]

在现有技术中,模拟退火布局框架包含以下步骤:首先生成一个初始布局,根据该初始布局计算出初始温度;然后进入退火阶段,分为内外两重循环。内循环在同一个温度上通过执行多次逻辑单元的交换来实现解的扰动,从而获得一个新解,外循环则判断算法退出准则是否满足,若不满足,就根据退火表更新温度。本发明在模拟退火布局框架的基础上,针对双时钟超导电路的特性,提出新的初始布局方法和布局解的扰动方法。

[0058]

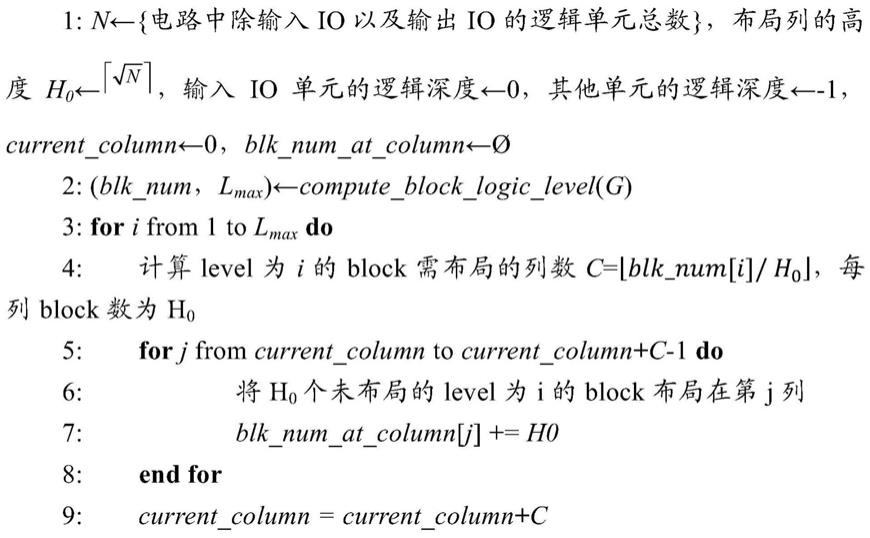

以下将结合图6和算法1、算法2对本发明的基于逻辑深度的双时钟超导电路初始布局方法和满足逻辑深度约束的布局解扰动方法进行详细描述。图6是本发明一个实施例的基于逻辑深度的双时钟超导rsfq电路初始布局算法流程图,算法1描述了本发明一个实施例的基于逻辑深度的双时钟超导电路初始布局。

[0059]

算法1.基于逻辑深度的双时钟超导电路初始布局

[0060]

输入:工艺库文件、电路门级网表g(v,e),v表示逻辑单元,e表示单元之间的信号连接。

[0061][0062]

输出:逻辑单元在芯片上的初始坐标位置、逻辑单元可布局的列信息。

[0063]

如算法1以及图6所示,以n表示电路中的不包括输入io和输出io的逻辑单元总数,h0表示布局列的参考高度,在算法1的初始布局中,每一列的高度都不会超过h0。假设要布局的芯片的宽高比为α,则α*h0*h0=n,因此当期望布局后的芯片接近方形时,α=1,算法1即以α=1,为例进行说明。初始化所有逻辑单元的逻辑深度,例如将输入io单元的逻辑深度初始化为0,其他逻辑单元的逻辑深度初始化为

‑

1(步骤s100)。current_column用于标记当前布局列,初始值为0。blk_num_at_column[current_column]用于存储当前布局列已经布局的单元数,初始值为空。根据电路网表的连接关系,从输入io单元开始,计算每个逻辑单元的逻辑深度,得出所有逻辑单元的最大逻辑深度l

max

,并将逻

辑深度为i的单元编号存储到blk_num[i]中(步骤s101以及算法1的第2行的子程序compute_block_logic_level(g)),例如参照图4,blk_num[2]=[g8,g9]。

[0064]

根据逻辑深度为i的单元(block)数的多少,确定该逻辑深度为i的单元可以布局的列。从逻辑深度i=1开始,直到逻辑深度为i=l

max

,对每一个逻辑深度i计算level为i的block需要满高度布局的列c=[blk_num[i]/h0],即c列中的每一列的block数均为h0(步骤s103)。从当前布局列开始,直到current_column+c

‑

1列,每一列都布置h0个未布局的level为i的block(步骤s105),其中,该h0个block是从未布局的level为i的block中随机选取的,更新每一列的block数blk_num_at_column[j]+=h0。然后将当前布局列更新为current_column+c。逻辑深度为i的剩余的未被布局的单元数为blk_num[i]%h0,将该未被布局的blk_num[i]%h0个level为i的block放置在当前列,按照y坐标递增的顺序依次向上摆放,其中,该未被布局的blk_num[i]%h0个block之间的顺序也是随机的。更新当前列的block数blk_num_atcolumn[current_column]+=blk_num[i]%h0,然后将当前布局列更新为current_column+1(步骤s107)。

[0065]

此时完成的布局,单元数小于h0的level均被布局在单独的列中,且blk_num[i]%h0所得到的剩余的单元也被布局在单独的列中,这些列的单元数比较少,且可能远小于h0。因此需要进行列的合并,将单元数较少的列合并在一起。

[0066]

如算法第13

‑

27行所示,从第0列开始,如果列编号为col的block数<h0,则将该列的列编号col存储至数组array中,直到current_column

‑

1列(步骤s108

‑

s110)。因此数组array中存储了所有的block数<h0的列编号。将多列进行合并,即把array[i+1]~array[i+j]列的block位置调整到array[i]列,使得array[i]列的block数不超过h0且最接近于h0(步骤s112)。其中最接近h0指的是合并之前的array[i]列、array[i+1]列

…

array[i+j]列的单元数之和≤h0<合并之前的array[i]列、array[i+1]列、

…

array[i+j]列、array[i+j+1]列的单元数之和。合并完成后更新array[i]列的block数,并将array[i+1]~array[i+j]列的block数置为0,i=i+j+1,直到i=array.size()

‑

1。从第0列开始,如果col列的block数不等于0,则计算从第0列到第col列中,block数为0的列数,记为s,将第col列的所有block的x坐标减去s,直到最后一列(即current_column

‑

1列),更新所有block的x坐标(步骤s114

‑

s116)。

[0067]

最后输出除了输入io以及输出io以外的逻辑单元在芯片上的初始坐标以及逻辑单元可布局的列。储存在map<block_id,t_block_inf>中,其中block_id用于储存逻辑单元的编号,t_block_inf用于储存逻辑单元的名字,逻辑单元所连接的net,x坐标,y坐标,逻辑单元可布局的列。

[0068]

下面将结合图4的加法器的具体示例对本发明的用于双时钟架构的超导rsfq电路初始布局方法进行说明。在该示例中,n为19,假设α=1,则h0为5。其初始布局过程如下:

[0069]

第一步:i=1时,判断blk_num[1]=8,c=1,因此随机选取g0

‑

g7中的5个单元布置至第0列,这5个单元的位置是随机的,current_column=1,blk_num[i]%h0=3,在第1列y=0,1,2的位置随机布置g0

‑

g7中的剩余的3个单元;此时current_column=2;g0

‑

g7的可布局的列为第0列和第1列;

[0070]

第二步:i=2时,判断blk_num[2]=2,c=0,blk_num[2]%h0=2,在第2列y=0,1的位置随机布置g8

‑

g9 2个单元,即g8和g9 2个单元的顺序是随机的;此时current_column

=3;

[0071]

第三步:i=3时,判断blk_num[3]=1,c=0,blk_num[3]%h0=1,在第3列y=0的位置布置g10;此时current_column=4;

[0072]

第四步:i=4时,判断blk_num[4]=2,c=0,blk_num[4]%h0=2,在第4列y=0,1的位置随机布置g11

‑

g12 2个单元;此时current_column=5;以此类推,在第5列y=0的位置布置g13,在第6列y=0,1的位置随机布置g14和g15,在第7列y=0的位置布置g16,在第8列y=0,1的位置随机布置g17和g18,在第9列y=0的位置布置g19。

[0073]

然后进行列的合并,合并之后的初始布局如图7所示。第0列的单元数为5因此不需要合并,第1列的单元数为3,第2列的单元数为2,因此将第1列和第2列合并至第1列,将第2列的单元数置为0,以此类推,第3列、第4列和第5列合并至第3列,第4列和第5列的单元数置为0,第6列、第7列和第8列合并至第6列,第7列和第8的单元数置为0。之后将所有单元的x坐标减去其之前所有列中单元数为0的列的数量,以去除单元数为0的列,并更新所有单元的x坐标。合并之后的初始布局的一个示例如图7所示,但是应当注意,图7仅仅是初始布局的一个示例,由于布局的过程中,同一逻辑深度中的单元的布局是随机的,因此初始布局并不是唯一的。

[0074]

本发明的基于逻辑深度的电路初始布局方法,首先根据电路中的逻辑单元总数确定布局列的初始高度,通过判断同一逻辑深度的逻辑单元的数量与布局列初始高度的关系,确定该逻辑深度的单元可以分配的布局列,若同一布局列中包含多个逻辑深度的单元,则按照与逻辑深度的排序相同的顺序布置单元,以方便在并发时钟下的布线;然后在布局列内为单元随机选择一个位置,从而获得满足超导电路的门级流水特性的初始布局。

[0075]

根据初始坐标位置计算初始布局的代价(cost)。本发明的cost等于所有线网的边界框线长之和,即

[0076][0077]

其中i代表线网编号,num_nets是线网数量,对于每条线网i,bb

x

(i)和bb

y

(i)分别表示其边界框的水平和垂直跨度。图8示出了一个含10个端点的线网边界框的示意图。其中虚线框中包括42个格点,深色的方框代表端点,图8中共有10个端点。端点之间的水平跨度bb

x

(i)=x

max

‑

x

min

+1=7,垂直跨度bb

y

(i)=y

max

‑

y

min

+1=6。当线网端点数目大于3时,边界框线长模型低估了线网的长度,故通常会定义补偿因子q(i),其值取决于线网i的端点数目。通常,补偿因子q(i)是提前计算好的,并存入一个数组中,根据相应的端点数即可得到不同的q(i)值。需要说明的是,本发明中虽然以线长为优化目标,但本发明不以此为限,实际应用中根据需要,也可以定义其他的优化目标,例如延时、功耗等。

[0078]

得到初始布局的cost之后,通过算法2对布局解扰动,以得到cost最小的布局解作为最终的布局。

[0079]

算法2.满足逻辑深度约束的布局解扰动方法

[0080]

输入:电路门级网表g(v,e),v表示逻辑单元,e表示单元之间的信号连接,初始布局结果。

[0081][0082][0083]

输出:新的布局解s

new

。

[0084]

如算法2所示,为电路中的所有逻辑单元找到新的坐标位置。以m表示电路中包括输入io和输出io的逻辑单元总数。如果单元是输入io,则在芯片左侧选择一个格点位置,如果单元是输出io,则在芯片右侧选择一个格点位置(算法2第1

‑

6行)。如果是其他单元,则需要根据该单元可布局列的数量分别处理。

[0085]

如果该单元(block j)可布局在多个列(大于1列)时,这些列可能只包含同一逻辑深度的单元,也可能包含不同逻辑深度的单元。此时,本发明在只包含同一逻辑深度的单元

的那些列上进行布局解的扰动,首先在只包含同一逻辑深度的单元的列中随机选择一个列,然后在选中的列上随机选择一个格点位置,将block j与该格点的block进行交换,确定他们的x

new

、y

new

坐标(算法2第8行)。

[0086]

如果block j可布局的列数为1,且与block j具有相同逻辑深度的单元数大于1(算法2第9行),可以产生0

‑

1之间的一个随机数r,以一定的概率p(0≤p≤1),即r<p时,将block j和与其逻辑深度相同的block进行交换,确定他们的x

new

、y

new

坐标(算法2第10行);当r≥p时,如果布局列中存在两个及以上block数相等且逻辑深度不等的宏模块,则将这两个宏模块整体进行交换,确定宏模块中所有block的x

new

、y

new

坐标(算法2第11行)。需要说明的是,这里的宏模块指的是由位于同一布局列且逻辑深度相同的多个block构成的电路块,例如图7中的g11和g12可以是一个宏模块。另外,连续的多个空格点也可以看作一个宏模块,与同一列的block数相等的宏模块交换位置。如果与block j具有相同逻辑深度的单元数也为1时,即与block j逻辑深度相同的单元只有它本身,这时如果布局列上有空位,则将该单元移动到随机选择的一个空位上,得到新的坐标x

new

和y

new

坐标(算法2第12行)。

[0087]

在算法2中,不同的概率值(即不同的p值)能够均衡计算时间和cost的收敛。假设在同一列中,逻辑深度为1的单元数为2,逻辑深度为2的单元数为2,逻辑深度为3的单元数为1。那么逻辑深度为1的2个单元可以内部互相交换位置,逻辑深度为1的2个单元组成的宏模块也可以整体与逻辑深度为2的2个单元组成的宏模块进行交换。整体交换使得cost减小的速度较快,但需要的计算时间也较长,因此通过概率p来判断进行内部互相交换,与进行宏模块整体交换的时机,不同的概率值能够均衡计算时间和cost的收敛速度。

[0088]

然后,根据等式(1)计算新的布局解s

new

的cost。如果初始布局的cost更低,则初始布局得到的逻辑单元的坐标值不变,如果新的布局解s

new

的cost更低,则根据新的布局解s

new

更新逻辑单元的坐标值。循环遍历所有可布局的x和y坐标,以得到cost最小的布局解作为最终的布局。图9即为图4中的4位加法器电路的最终布局示意图,其可在图7的基础上通过位置交换得到。

[0089]

应当注意的是,在本发明的上述实施例中是以列的方向(即垂直方向)为例按照与逻辑深度的排序相同的顺序布置单元,但本领域的普通技术人员应该明白,本发明应不限于此,也可以采用以行的方向(即水平方向)按照与逻辑深度的排序相同的顺序布置单元。即在本发明的上述布局过程中,可以将列替换为行,将垂直方向替换为水平方向,最终在芯片上的布局结果相当于将以列的方向进行布局所得到的结果顺时针旋转90度。本领域技术人员可根据实际的应用来选择布局的方向,这些选择和修改都在本发明的保护范围之内。

[0090]

本发明的满足逻辑深度约束的布局解扰动方法,通过约束电路的输入单元只能摆放在芯片的左侧一列,输出单元只能摆放在芯片的右侧一列,可使输出尽可能地在同一个时钟周期内到达。在进行逻辑单元的位置优化时,只允许将其摆放到与逻辑深度相对应的布局列,并以总线长为优化目标,可获得面积较优的布局结果,同时满足逻辑深度的约束。需要说明的是,本发明中是以线长为优化目标,但根据需要,也可以定义其他的优化目标,例如延时、功耗等。

[0091]

相比于已有的超导rsfq电路布局方法,本发明提出的用于双时钟架构的超导rsfq电路的布局方法,可在满足逻辑深度约束的条件下获得面积较优的布局结果,减小电路的面积;而且由于考虑了单元的逻辑深度,更容易实现并发时钟下的布线,从而提高电路的工

作频率。

[0092]

本发明还提供一种计算机可读存储介质,其上包含有计算机程序,所述计算机程序可被处理器执行以实现上述用于双时钟架构的超导rsfq电路布局方法的步骤。

[0093]

本发明还提供一种电子设备,包括:一个或多个处理器;以及存储器,其中存储器用于存储一个或多个可执行指令;一个或多个处理器被配置为经由执行一个或多个可执行指令以实现上述用于双时钟架构的超导rsfq电路布局方法的步骤。

[0094]

最后应该说明的是,以上示例仅用以解释本发明的技术方案而非限制。尽管上文参照示例对本发明进行了详细的说明,本领域的普通技术人员应当理解,此处所描述的具体示例仅仅用以解释本发明,并不构成对本发明保护的限定。任何在本发明的精神和原则之内的所做的修改、等同替换和改进等,均应包含在本发明的权利要求保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1