一种基于忆阻的操作性条件反射电路

1.本发明涉及数模电路的技术领域,涉及一种基于忆阻的操作性条件反射电路,是基于斯金纳操作性条件反射的思想实现。

背景技术:

2.1971年,美国加州大学伯克利分校蔡少棠教授提出了忆阻这个概念,2008年美国惠普实验室成功研制了首个能工作的忆阻器。忆阻的特性非常类似于生物神经中的突触,可以对大脑的部分功能进行模仿,从而进行生物行为的仿真记忆学习,生物记忆行为的电路仿真已经成为忆阻研究极其重要的一部分。忆阻在非易失性存储、逻辑运算、新型计算、存储融合架构计算和新型神经形态计算等方面,呈现出了极有潜力的应用前景。

3.行为学家skinner通过实验提出了操作性条件反射理论体系,国内也有团队把操作性条件反射运用到犬的训练中,随后,vollmer等人提出了即时性和饱腹感等因素对操作性条件反射的影响,但没有通过电路实现。

技术实现要素:

4.针对现有的操作性条件反射理论,本发明提出了一种基于忆阻的操作性条件反射电路,通过两组忆阻正反并联电路,实现了操作性条件反射的过程;通过促进抑制电路,实现了不同情绪之间的促进抑制关系;通过电压控制电路,实现了即时性和饱腹感对操作性条件反射的影响。

5.本发明的技术方案是这样实现的:

6.一种基于忆阻的操作性条件反射电路,包括输入模块、电压控制模块、促进模块i、促进模块ii、抑制模块i、抑制模块ii、突触神经元模块i、突触神经元模块ii和突触神经元模块iii;输入模块分别与脉冲电源信号、促进模块i、促进模块ii、抑制模块i、抑制模块ii、突触神经元模块i和突触神经元模块ii相连接,突触神经元模块ii分别与促进模块i、促进模块ii、抑制模块i和抑制模块ii相连接,突触神经元模块i分别与促进模块ii和抑制模块ii相连接;所述脉冲电源信号分别与电压控制模块和抑制模块i相连接,电压控制模块与突触神经元模块iii相连接。

7.优选地,所述输入模块包括第一压控单元、第二压控单元和加法运算单元;突触神经元模块i包括电压模块i和突触模块i;突触神经元模块ii包括电压模块ii和突触模块ii;抑制模块i包括抑制信号判断模块i、抑制信号接收处理模块i和抑制信号恢复模块i;抑制模块ⅱ包括抑制信号判断模块ii和抑制信号接收处理模块ii;促进模块i包括促进信号判断模块i、促进信号接收处理模块i和促进信号恢复模块i;促进模块ⅱ包括促进信号判断模块ii和促进信号接收处理模块ii;电压控制模块包括电压判断模块和电压接收处理模块;

8.所述第一压控单元的输入端与非门d1的输出端相连接,非门d1的输入端与脉冲电源信号相连接,脉冲电源信号分别与第二压控单元的输入端、抑制信号判断模块i和电压判断模块相连接,电压判断模块与电压接收处理模块相连接,电压接收处理模块与突触神经

元模块iii相连接;第一压控单元的输出端、第二压控单元的输出端分别与加法运算单元的输入端相连接;加法运算单元的输出端分别与促进信号接收处理模块i、促进信号接收处理模块ii、抑制信号接收处理模块i、抑制信号接收处理模块ii、电压模块i和电压模块ii相连接,电压模块i与突触模块i相连接,突触模块i分别与促进信号判断模块ii、抑制信号判断模块ii相连接,电压模块ii与突触模块ii相连接,突触模块ii分别与抑制信号判断模块i、抑制信号接收处理模块ii、促进信号判断模块i、促进信号接收处模块ii相连接;促进信号判断模块i分别与非门d1的输出端、促进信号接收处理模块i、促进信号恢复模块i相连接,促进信号判断模块ii与促进信号接收处理模块ii相连接;抑制信号判断模块i分别与脉冲电源信号、抑制信号接收处理模块i、抑制信号恢复模块i相连接;抑制信号判断模块ii与抑制信号接收处理模块ii相连接。

9.优选地,所述第一压控单元包括压控开关s1、电源v1和电阻r1;所述第二压控单元包括压控开关s2、电源v2和电阻r2;所述加法运算单元包括电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r9、电阻r

10

、电阻r

11

、运算放大器op1和运算放大器op2;

10.压控开关s1的正相输入端与非门d1的输出端相连接,压控开关s1的第一触点分别与电阻r1的一端、电阻r3的一端相连接,压控开关s1的第二触点与电源v1的正极相连接,电源v1的负极、电阻r1的另一端和压控开关s1的反相输入端均接地;

11.压控开关s2的正相输入端与脉冲电源信号相连接,压控开关s2的第一触点分别与电阻r2的一端、电阻r4的一端相连接,压控开关s2的第二触点与电源v2的正极相连接,电源v2的负极、电阻r2的另一端和压控开关s2的反相输入端均接地;

12.电阻r3的另一端分别与电阻r5的一端、电阻r7的一端和运算放大器op1的正相输入端相连接,电阻r5的另一端与抑制信号接收处理模块i相连接,电阻r7的另一端与抑制信号接收处理模块ii相连接;电阻r4的另一端分别与电阻r6的一端、电阻r8的一端和运算放大器op1的正相输入端相连接,电阻r6的另一端与促进信号接收处理模块i相连接,电阻r8的另一端与促进信号接收处理模块ii相连接,运算放大器op1的正相输入端与运算放大器op1的输出端之间连接有电阻r9,运算放大器op1的输出端与电阻r

10

的一端相连接,电阻r

10

的另一端与运算放大器op2的反相输入端相连接,运算放大器op2的反相输入端与运算放大器op2的输出端之间连接有电阻r

11

,运算放大器op2的输出端分别与电压模块i、电压模块ii相连接,运算放大器op2的正相输入端和运算放大器op1的反相输入端均接地。

13.优选地,所述电压模块i包括忆阻m1、忆阻m2、电容c1、电阻r

12

和运算放大器op3,所述突触模块i包括忆阻m5、电阻r

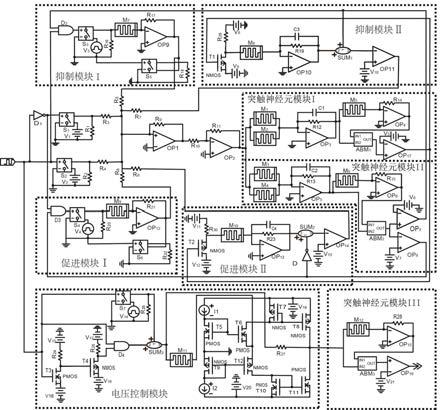

14

、运算放大器op4、数学运算单元abm1、运算放大器op

17

和电源v5;所述忆阻m1的k极和忆阻m2的k极均与运算放大器op2的输出端相连接,忆阻m1的a极和忆阻m2的a极均与运算放大器op3的反相输入端相连接,运算放大器op3的反相输入端与运算放大器op3的输出端之间连接有电阻r

12

,电阻r

12

上并联有电容c1,运算放大器op3的输出端分别与忆阻m5的k极、数学运算单元abm1的in2输入端相连接,忆阻m5的a极与运算放大器op4的反相输入端相连接,运算放大器op4的反相输入端与运算放大器op4的输出端之间连接有电阻r

14

,运算放大器op4的输出端与数学运算单元abm1的in1输入端相连接,数学运算单元abm1的out输出端与运算放大器op

17

的正相输入端相连接,运算放大器op

17

的反相输入端与电源v5的正极相连接,运算放大器op

17

的输出端分别与抑制信号判断模块ii、促进信号判断模块ii相连接;运算放大器op3的正相输入端、运算放大器op4的正相输入端和电源v5的负极

均接地。

14.优选地,所述电压模块ii包括忆阻m3、忆阻m4、电容c2、电阻r

13

、运算放大器op5,所述突触模块ii包括忆阻m6、电阻r

15

、运算放大器op6、数学运算单元abm2、运算放大器op7、运算放大器op8、电源v6和电源v7;忆阻m3的k极和忆阻m4的k极均与运算放大器op2的输出端相连接,忆阻m3的a极和忆阻m4的a极均与运算放大器op5的反相输入端相连接,运算放大器op5的反相输入端与运算放大器op5的输出端之间连接有电阻r

13

,电阻r

13

上并联有电容c2,运算放大器op5的输出端分别与忆阻m6的k极、数学运算单元abm2的in2输入端相连接,忆阻m6的a极与运算放大器op6的反相输入端相连接,运算放大器op6的反相输入端与运算放大器op6的输出端之间连接有电阻r

15

,运算放大器op6的输出端与数学运算单元abm2的in1输入端相连接,数学运算单元abm2的out输出端分别与运算放大器op7的正相输入端、运算放大器op8的反相输入端相连接,运算放大器op7的反相输入端与电源v6的正极相连接,运算放大器op7的输出端分别与抑制信号判断模块i、抑制信号接收处理模块ii相连接,运算放大器op8的正相输入端与电源v7的正极相连接,运算放大器op8的输出端分别与促进信号判断模块i、促进信号接收处理模块ii相连接;运算放大器op5的正相输入端、运算放大器op6的正相输入端、电源v6的负极和电源v7的负极均接地。

15.优选地,所述抑制信号判断模块i包括与门d2、压控开关s3、电压脉冲源v3和电阻r

16

;所述抑制信号接收处理模块ⅰ包括忆阻m7、运算放大器op9和电阻r

17

;所述抑制信号恢复模块i包括压控开关s5和电阻r

18

;所述与门d2的输入端分别与脉冲电源信号、运算放大器op7的输出端相连接,与门d2的输出端与压控开关s3的正相输入端相连接,压控开关s3的反相输入端接地,压控开关s3的第一触点分别与忆阻m7的k极、电阻r

16

的一端相连接,压控开关s3的第二触点与电压脉冲源v3的正极相连接,电压脉冲源v3的负极分别与电阻r

16

的另一端、压控开关s5的正相输入端相连接,电压脉冲源v3的负极接地,忆阻m7的a极与运算放大器op9的反相输入端相连接,运算放大器op9的反相输入端与运算放大器op9的输出端之间连接有电阻r

17

,运算放大器op9的正相输入端接地,运算放大器op9的输出端与电阻r5的另一端相连接,压控开关s5的第一触点与电阻r

18

的一端相连接,压控开关s5的第二触点与电阻r5的另一端相连接,电阻r

18

的另一端和压控开关s5的反相输入端均接地;

16.所述抑制信号判断模块ii包括nmos管t1、电阻r

29

、电源v8和电源v9;所述抑制信号接收处理模块ii包括忆阻m8、电容c3、电阻r

19

、运算放大器op

10

、电压求和单元sum1、运算放大器op

11

和电源v

10

;所述nmos管t1的栅极与运算放大器op

17

的输出端相连接,nmos管t1的漏极分别与电阻r

29

的一端、忆阻m8的a极相连接,电阻r

29

的另一端与电源v8的正极相连接,电源v8的负极接地,nmos管t1的源极与电源v9的正极相连接,电源v9的负极接地,忆阻m8的k极与运算放大器op

10

的反相输入端相连接,运算放大器op

10

的反相输入端与运算放大器op

10

的输出端之间连接有电阻r

19

,电阻r

19

上并联有电容c3,运算放大器op

10

的正相输入端接地,运算放大器op

10

的输出端与电压求和单元sum1的第一输入端相连接,电压求和单元sum1的第二输入端与运算放大器op7的输出端相连接,电压求和单元sum1的输出端与运算放大器op

11

的反相输入端相连接,运算放大器op

11

的正相输入端与电源v

10

的正极相连接,运算放大器op

11

的输出端与电阻r7的另一端相连接,电源v

10

的负极接地。

17.优选地,所述促进信号判断模块i包括与门d3、压控开关s4、电压脉冲源v4和电阻r

20

;所述促进信号接收处理模块i包括忆阻m9、运算放大器op

12

和电阻r

21

;所述促进信号恢

复模块i包括压控开关s6和电阻r

22

;促进信号判断模块ii包括nmos管t2、电阻r

30

、电源v

11

和电源v

12

;所述抑制信号接收处理模块ii忆阻m

10

、电容c4、电阻r

23

、运算放大器op

13

、电压求和单元sum2、非门d5、运算放大器op

14

和电源v

13

;

18.所述与门d3的输入端分别与非门d1的输出端、运算放大器op8的输出端相连接,与门d3的输出端与压控开关s4的正相输入端相连接,压控开关s4的反相输入端接地,压控开关s4的第一触点分别与忆阻m9的k极、电阻r

20

的一端相连接,压控开关s4的第二触点与电压脉冲源v4的正极相连接,电压脉冲源v4的负极分别与电阻r

20

的另一端、压控开关s6的正相输入端相连接,电压脉冲源v4的负极接地,忆阻m9的a极与运算放大器op

12

的反相输入端相连接,运算放大器op

12

的反相输入端与运算放大器op

12

的输出端之间连接有电阻r

21

,运算放大器op

12

的正相输入端接地,运算放大器op

12

的输出端与电阻r6的另一端相连接,压控开关s6的第一触点与电阻r

22

的一端相连接,压控开关s6的第二触点与电阻r6的另一端相连接,电阻r

22

的另一端和压控开关s6的反相输入端均接地;

19.所述nmos管t2的栅极与运算放大器op

17

的输出端相连接,nmos管t2的漏极分别与电阻r

30

的一端、忆阻m

10

的a极相连接,电阻r

30

的另一端与电源v

11

的正极相连接,电源v

11

的负极接地,nmos管t2的源极与电源v

12

的正极相连接,电源v

12

的负极接地,忆阻m

10

的k极与运算放大器op

13

的反相输入端相连接,运算放大器op

13

的反相输入端与运算放大器op

13

的输出端之间连接有电阻r

23

,电阻r

23

上并联有电容c4,运算放大器op

13

的正相输入端接地,运算放大器op

13

的输出端与电压求和单元sum2的第一输入端相连接,电压求和单元sum2的第二输入端与非门d5的输出端相连接,非门d5的输入端与运算放大器op8的输出端相连接,电压求和单元sum2的输出端与运算放大器op

14

的反相输入端相连接,运算放大器op

14

的正相输入端与电源v

13

的正极相连接,运算放大器op

14

的输出端与电阻r8的另一端相连接,电源v

13

的负极接地。

20.优选地,所述电压判断模块包括pmos管t3、电阻r

24

、电源v

15

、电源v

16

、nmos管t4、电阻r

25

、电源v

17

、电源v

18

、与门d4、压控开关s7、电压脉冲源v

14

、电阻r

26

和电压求和单元sum3;

21.所述脉冲电源信号分别与pmos管t3的栅极、与门d4的输入端和压控开关s7的正相输入端相连接,pmos管t3的漏极分别与电阻r

24

的一端、nmos管t4的栅极相连接,电阻r

24

的另一端与电源v

15

的正极相连接,电源v

15

的负极接地,pmos管t3的源极与电源v

16

的正极相连接,电源v

16

的负极接地,nmos管t4的漏极分别与电阻r

25

的一端、与门d4的输入端相连接,电阻r

25

的另一端与电源v

17

的正极相连接,电源v

17

的负极接地,nmos管t4的源极与电源v

18

的正极相连接,电源v

18

的负极接地;压控开关s7的第一触点分别与电阻r

26

的一端、电压求和单元sum3的第一输入端相连接,压控开关s7的第二触点与电压脉冲源v

14

的正极相连接,压控开关s7的反相输入端、电压脉冲源v

14

的负极和电阻r

26

的另一端均接地;与门d4的输出端与电压求和单元sum3的第二输入端相连接,电压求和单元sum3的输出端与电压接收处理模块相连接。

22.优选地,所述电压接收处理模块包括忆阻m

11

、电流源i1、电流源i2、pmos管t5、pmos管t6、nmos管t7、nmos管t8、nmos管t9、pmos管t

10

、pmos管t

11

、nmos管t

12

、电阻r

27

、电源v

19

和电源v

20

;所述电压求和单元sum3的输出端分别与忆阻m

11

的a极、电阻r

27

的一端相连接,忆阻m

11

的k极分别与pmos管t6的源极、nmos管t

12

的源极相连接,pmos管t6的栅极与电流源i1的负极相连接,电流源i1的正极分别与nmos管t7的源极、电源v

19

的正极和nmos管t8的源极相连接,

电源v

19

的负极接地,电流源i1的负极分别与pmos管t5的漏极、pmos管t5的栅极相连接,pmos管t5的源极和nmos管t9的源极均接地,nmos管t9的漏极、nmos管t9的栅极和nmos管t

12

的栅极均与电流源i2的正极相连接,电流源i2的负极分别与电源v

20

的正极、pmos管t

10

的源极和pmos管t

11

的源极相连接,电源v

20

的负极接地,pmos管t

10

的漏极、pmos管t

10

的栅极和pmos管t

11

的栅极均与nmos管t

12

的漏极相连接,pmos管t

11

的漏极分别与电阻r

27

的另一端、nmos管t8的漏极和突触神经元模块iii相连接,nmos管t8的栅极、nmos管t7的栅极、nmos管t7的漏极均与pmos管t6的漏极相连接。

23.优选地,所述突触神经元模块iii包括忆阻m

12

、电阻r

28

、运算放大器op

15

、数学运算单元abm3、电源v

21

和运算放大器op

16

,电阻r

27

的另一端分别与忆阻m

12

的k极、数学运算单元abm3的in2输入端相连接,忆阻m

12

的a极与运算放大器op

15

的反相输入端相连接,运算放大器op

15

的反相输入端与运算放大器op

15

的输出端之间连接有电阻r

28

,运算放大器op

15

的正相输入端接地,运算放大器op

15

的输出端与数学运算单元abm3的in1输入端相连接,数学运算单元abm3的out输出端与运算放大器op

16

的正相输入端相连接,运算放大器op

16

的反相输入端与电源v

21

的正极相连接,电源v

21

的负极接地。

24.与现有技术相比,本发明产生的有益效果为:

25.1)本发明通过忆阻电路实现操作性条件反射,对生物个体做出的行为结果给予不同类型的刺激可以改变这一结果在未来发生的频率,为类脑神经更加智能化提供了重要意义。

26.2)能够实现鸽子在不同状态下对于正性奖励与负性惩罚的不同反应,并且能够实现正性奖励与负性惩罚之间的相互促进抑制关系。

27.3)通过两组忆阻正反并联电路,实现了操作性条件反射的过程,实现了不同情绪之间的促进抑制关系,实现了即时性和饱腹感对操作性条件反射的影响。

附图说明

28.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

29.图1为本发明的电路原理示意图。

30.图2为本发明在0

‑

90s的特定环境下的仿真结果图,其中,0

‑

30s为饥饿且无噪声环境下的仿真结果图,30

‑

60s为饥饿且有噪声环境下的仿真结果图,60

‑

90s为饱食且有噪声环境下的仿真结果图。

31.图3为本发明的促进抑制模块的输出电压仿真结果图。

32.图4为本发明的忆阻m1、m2、m3、m4、m7、m8、m9和m

10

的仿真结果图。

33.图5为本发明的即时性对比的仿真结果图。

具体实施方式

34.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于

本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

35.首先介绍一下本发明所实现的功能:在斯金纳操作性条件反射理论中,当处于饥饿且无噪声的环境下,如果鸽子啄红球,就会得到食物,食物属于正性奖励,会增加鸽子啄红球的重复率,实现了操作性条件反射中的正向增强,如图2中0

‑

30s食物图所示;如果鸽子啄篮球,就会受到电击,电击属于负性惩罚,会降低鸽子啄蓝球的重复率,实现了操作性条件反射中的正向惩罚,如图2中0

‑

30s电击图所示;如果鸽子啄黄球,黄球代表消除噪声,对于鸽子啄黄球的重复率不变,如图2中0

‑

30s消除噪声图所示。当处于饥饿且有噪声的环境下,如果鸽子啄红球,就会得到食物,食物属于正性奖励,会增加鸽子啄红球的重复率,如图2中30

‑

60s食物图所示;如果鸽子啄篮球,就会受到电击,电击属于负性惩罚,会降低鸽子啄蓝球的重复率,实现了操作性条件反射中的负向惩罚,如图2中30

‑

60s电击图所示;如果鸽子啄黄球,就会消除噪声,会增加鸽子啄黄球的重复率,如图2中30

‑

60s消除噪声图所示。当处于饱食且有噪声的环境下,如果鸽子啄红球,由于鸽子处于饱食状态,对于食物没有欲望,对于鸽子啄红球的重复率不变,如图2中60

‑

90s食物图所示;如果鸽子啄篮球,就会受到电击,电击属于负性惩罚,会降低鸽子啄蓝球的重复率,如图2中60

‑

90s电击图所示;如果鸽子啄黄球,就会消除噪声,增加鸽子啄黄球的重复率,实现了操作性条件反射中的负向增强中的逃避,如图2中60

‑

90s消除噪声图所示。若鸽子啄绿球,绿球不属于正性奖励或负性惩罚,鸽子就会慢慢遗忘,实现了操作性条件反射中的消退。

36.在不用环境下,鸽子通过啄不同颜色的球来实现操作性条件反射;通过饥饿和饱食状态,来分析鸽子的饱腹感,通过是否立即动作,来分析鸽子的即时性。

37.如图1所示,本发明实施例提供了一种基于忆阻的操作性条件反射电路,包括输入模块、电压控制模块、促进模块i、促进模块ii、抑制模块i、抑制模块ii、突触神经元模块i、突触神经元模块ii和突触神经元模块iii;输入模块分别与脉冲电源信号、促进模块i、促进模块ii、抑制模块i、抑制模块ii、突触神经元模块i和突触神经元模块ii相连接,突触神经元模块ii分别与促进模块i、促进模块ii、抑制模块i和抑制模块ii相连接,突触神经元模块i分别与促进模块ii和抑制模块ii相连接;所述脉冲电源信号分别与电压控制模块和抑制模块i相连接,电压控制模块与突触神经元模块iii相连接。通过抑制模块i,来实现负向惩罚的操作性条件反射;通过抑制模块ⅱ,来实现正向增强的操作性条件反射;通过促进模块ⅰ,来实现负向惩罚对于正向激励是有促进作用的;通过促进模块ⅱ,来实现正向激励对于负向惩罚是有抑制作用的。

38.所述输入模块包括第一压控单元、第二压控单元和加法运算单元;突触神经元模块i包括电压模块i和突触模块i;突触神经元模块ii包括电压模块ii和突触模块ii;抑制模块i包括抑制信号判断模块i、抑制信号接收处理模块i和抑制信号恢复模块i;抑制模块ⅱ包括抑制信号判断模块ii和抑制信号接收处理模块ii;促进模块i包括促进信号判断模块i、促进信号接收处理模块i和促进信号恢复模块i;促进模块ⅱ包括促进信号判断模块ii和促进信号接收处理模块ii;电压控制模块包括电压判断模块和电压接收处理模块。

39.所述第一压控单元的输入端与非门d1的输出端相连接,非门d1的输入端与脉冲电源信号相连接,脉冲电源信号分别与第二压控单元的输入端、抑制信号判断模块i和电压判断模块相连接,电压判断模块与电压接收处理模块相连接,电压接收处理模块与突触神经

元模块iii相连接;第一压控单元的输出端、第二压控单元的输出端分别与加法运算单元的输入端相连接;加法运算单元的输出端分别与促进信号接收处理模块i、促进信号接收处理模块ii、抑制信号接收处理模块i、抑制信号接收处理模块ii、电压模块i和电压模块ii相连接,电压模块i与突触模块i相连接,突触模块i分别与促进信号判断模块ii、抑制信号判断模块ii相连接,电压模块ii与突触模块ii相连接,突触模块ii分别与抑制信号判断模块i、抑制信号接收处理模块ii、促进信号判断模块i、促进信号接收处模块ii相连接;促进信号判断模块i分别与非门d1的输出端、促进信号接收处理模块i、促进信号恢复模块i相连接,促进信号判断模块ii与促进信号接收处理模块ii相连接;抑制信号判断模块i分别与脉冲电源信号、抑制信号接收处理模块i、抑制信号恢复模块i相连接;抑制信号判断模块ii与抑制信号接收处理模块ii相连接。

40.所述第一压控单元包括压控开关s1、电源v1和电阻r1;所述第二压控单元包括压控开关s2、电源v2和电阻r2;所述加法运算单元包括电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r9、电阻r

10

、电阻r

11

、运算放大器op1和运算放大器op2。在0

‑

30s和60

‑

90s时,输入信号为4v,在30

‑

60s时,输入信号为

‑

4v。

41.压控开关s1的正相输入端与非门d1的输出端相连接,压控开关s1的第一触点分别与电阻r1的一端、电阻r3的一端相连接,压控开关s1的第二触点与电源v1的正极相连接,电源v1的负极、电阻r1的另一端和压控开关s1的反相输入端均接地。

42.压控开关s2的正相输入端与脉冲电源信号相连接,压控开关s2的第一触点分别与电阻r2的一端、电阻r4的一端相连接,压控开关s2的第二触点与电源v2的正极相连接,电源v2的负极、电阻r2的另一端和压控开关s2的反相输入端均接地。

43.电阻r3的另一端分别与电阻r5的一端、电阻r7的一端和运算放大器op1的正相输入端相连接,电阻r5的另一端与抑制信号接收处理模块i相连接,电阻r7的另一端与抑制信号接收处理模块ii相连接;电阻r4的另一端分别与电阻r6的一端、电阻r8的一端和运算放大器op1的正相输入端相连接,电阻r6的另一端与促进信号接收处理模块i相连接,电阻r8的另一端与促进信号接收处理模块ii相连接,运算放大器op1的正相输入端与运算放大器op1的输出端之间连接有电阻r9,运算放大器op1的输出端与电阻r

10

的一端相连接,电阻r

10

的另一端与运算放大器op2的反相输入端相连接,运算放大器op2的反相输入端与运算放大器op2的输出端之间连接有电阻r

11

,运算放大器op2的输出端分别与电压模块i、电压模块ii相连接,运算放大器op2的正相输入端和运算放大器op1的反相输入端均接地。

44.所述电压模块i包括忆阻m1、忆阻m2、电容c1、电阻r

12

和运算放大器op3,所述突触模块i包括忆阻m5、电阻r

14

、运算放大器op4、数学运算单元abm1、运算放大器op

17

和电源v5;所述忆阻m1的k极和忆阻m2的k极均与运算放大器op2的输出端相连接,忆阻m1的a极和忆阻m2的a极均与运算放大器op3的反相输入端相连接,运算放大器op3的反相输入端与运算放大器op3的输出端之间连接有电阻r

12

,电阻r

12

上并联有电容c1,运算放大器op3的输出端分别与忆阻m5的k极、数学运算单元abm1的in2输入端相连接,忆阻m5的a极与运算放大器op4的反相输入端相连接,运算放大器op4的反相输入端与运算放大器op4的输出端之间连接有电阻r

14

,运算放大器op4的输出端与数学运算单元abm1的in1输入端相连接,数学运算单元abm1的out输出端与运算放大器op

17

的正相输入端相连接,运算放大器op

17

的反相输入端与电源v5的正极相连接,运算放大器op

17

的输出端分别与抑制信号判断模块ii、促进信号判断模块ii相连

接;运算放大器op3的正相输入端、运算放大器op4的正相输入端和电源v5的负极均接地。

45.如图1中的突触神经元ⅰ所示,忆阻m1和忆阻m2的k极与运算放大器op2的输出端相连接,在0

‑

18s,输入信号u0的电压值小于忆阻m1和忆阻m2的阈值电压,忆阻m1的阻值维持在300ω,忆阻m2的阻值维持在350ω,在18

‑

30s,输入信号u0的电压值大于忆阻m1的正阈值电压,忆阻m1的阻值迅速从600ω下降到300ω,忆阻m2的阻值保持不变,在30

‑

60s,输入信号u0的电压值大于忆阻m1的负阈值电压和忆阻m2的正阈值电压,忆阻m1的阻值迅速上升到600ω,忆阻m2的阻值从350ω下降到300ω,在60

‑

90s,输入信号u0的电压值小于忆阻m1和忆阻m2的阈值电压,忆阻m1和忆阻m2的阻值保持不变。电容c1、电阻r

12

、运算放大器op3的反相输入端与忆阻m1和忆阻m2的a极相连接,运算放大器op3的同相输入端接地,电容c1另一端、电阻r

12

另一端、运算放大器op3的输出端与忆阻m5的k极相连接,在0

‑

30s,忆阻m5的阻值从800ω下降到200ω,在30

‑

60s,忆阻m5的阻值从200ω上升到1kω,具体仿真图如图4所示。在忆阻m5的a极与电阻r

14

和运算放大器op4的反相输入端相连接,运算放大器op4的同相输入端接地,电阻r

14

的另一端和运算放大器op4的输出端与数学运算单元abm1一个输入端相连接,数学运算单元abm1另一端与电容c1另一端、电阻r

12

另一端、运算放大器op3的输出端相连接,abm1的输出值为

‑

in2/in1*10=m5/100,数学运算单元abm1的输出端与运算放大器op

17

的同相输入端相连接,运算放大器op

17

的反相输入端与电源v5的正极相连接,电源v5的负极接地,运算放大器op

17

相当于一个阈值为v5的激活函数,当op

17

的同相输入端接收到的电压小于v5时,op

17

输出

‑

5v电压,当收到的电压大于v5时,op

17

输出5v电压,反馈到促进模块ⅱ和抑制模块ⅱ中。突触神经元模块用于模拟生物神经网络中的突触和神经元,通过改变m5的阻值,可以改变突触强度的大小,m5的阻值越小突触强度越大。

46.所述电压模块ii包括忆阻m3、忆阻m4、电容c2、电阻r

13

、运算放大器op5,所述突触模块ii包括忆阻m6、电阻r

15

、运算放大器op6、数学运算单元abm2、运算放大器op7、运算放大器op8、电源v6和电源v7;忆阻m3的k极和忆阻m4的k极均与运算放大器op2的输出端相连接,忆阻m3的a极和忆阻m4的a极均与运算放大器op5的反相输入端相连接,运算放大器op5的反相输入端与运算放大器op5的输出端之间连接有电阻r

13

,电阻r

13

上并联有电容c2,运算放大器op5的输出端分别与忆阻m6的k极、数学运算单元abm2的in2输入端相连接,忆阻m6的a极与运算放大器op6的反相输入端相连接,运算放大器op6的反相输入端与运算放大器op6的输出端之间连接有电阻r

15

,运算放大器op6的输出端与数学运算单元abm2的in1输入端相连接,数学运算单元abm2的out输出端分别与运算放大器op7的正相输入端、运算放大器op8的反相输入端相连接,运算放大器op7的反相输入端与电源v6的正极相连接,运算放大器op7的输出端分别与抑制信号判断模块i、抑制信号接收处理模块ii相连接,运算放大器op8的正相输入端与电源v7的正极相连接,运算放大器op8的输出端分别与促进信号判断模块i、促进信号接收处理模块ii相连接;运算放大器op5的正相输入端、运算放大器op6的正相输入端、电源v6的负极和电源v7的负极均接地。

47.如图1中的突触神经元ⅱ所示,忆阻m3和忆阻m4的k极与运算放大器op2的输出端相连接,输入信号u0的电压值小于忆阻m1和忆阻m2的阈值电压,在0

‑

30s,忆阻m3和忆阻m4保持不变,在30

‑

60s,输入信号u0的电压值大于忆阻m3和忆阻m4的负阈值电压,忆阻m3和忆阻m4的阻值快速从300ω上升到600ω,在60

‑

90s,忆阻m3的阻值保持不变,输入信号u0的电压值大于忆阻m4的正阈值电压,忆阻m4的阻值下降到300ω。电容c2、电阻r

13

、运算放大器op5的反相

输入端与忆阻m3和忆阻m4的a极相连接,运算放大器op5的同相输入端接地,电容c2另一端、电阻r

13

另一端、运算放大器op5的输出端与忆阻m6的k极相连接,在0

‑

30s,忆阻m6的阻值从900ω下降到200ω,在30

‑

60s,忆阻m5的阻值从200ω上升到1kω,具体仿真图如图4所示。忆阻m6的a极与电阻r

15

和运算放大器op6的反相输入端相连接,运算放大器op6的同相输入端接地,电阻r

15

的另一端和运算放大器op6的输出端与数学运算单元abm2一个输入端相连接,数学运算单元abm2另一端与电容c2另一端、电阻r

13

另一端、运算放大器op5的输出端相连接,abm2的输出值为

‑

in2/in1*10=m6/100,数学运算单元abm2的输出端与运算放大器op7的同相输入端相连接,运算放大器op7的反相输入端与电源v6的正极相连接,运算放大器op7相当于一个阈值为v6的激活函数,当op7的同相输入端接收到的电压大于v5时,op

17

输出5v电压,当收到的电压小于v5时,运算放大器op7输出0v电压,反馈到促进模块ⅰ中;数学运算单元abm2的输出端与运算放大器op8的反相输入端相连接,当op8的反相输入端接收到的电压小于v7时,op

17

输出5v电压,当收到的电压大于v7时,运算放大器op8输出0v电压,反馈到促抑制模块ⅱ中。突触神经元模块用于模拟生物神经网络中的突触和神经元,通过改变m6的阻值,可以改变突触强度的大小,m6的阻值越小突触强度越大。

48.所述抑制信号判断模块i包括与门d2、压控开关s3、电压脉冲源v3和电阻r

16

;所述抑制信号接收处理模块ⅰ包括忆阻m7、运算放大器op9和电阻r

17

;所述抑制信号恢复模块i包括压控开关s5和电阻r

18

;所述与门d2的输入端分别与脉冲电源信号、运算放大器op7的输出端相连接,与门d2的输出端与压控开关s3的正相输入端相连接,压控开关s3的反相输入端接地,压控开关s3的第一触点分别与忆阻m7的k极、电阻r

16

的一端相连接,压控开关s3的第二触点与电压脉冲源v3的正极相连接,电压脉冲源v3的负极分别与电阻r

16

的另一端、压控开关s5的正相输入端相连接,电压脉冲源v3的负极接地,忆阻m7的a极与运算放大器op9的反相输入端相连接,运算放大器op9的反相输入端与运算放大器op9的输出端之间连接有电阻r

17

,运算放大器op9的正相输入端接地,运算放大器op9的输出端与电阻r5的另一端相连接,输出负性惩罚的抑制电压,压控开关s5的第一触点与电阻r

18

的一端相连接,压控开关s5的第二触点与电阻r5的另一端相连接,电阻r

18

的另一端和压控开关s5的反相输入端均接地。

49.如图1中的抑制模块ⅰ所示,突触神经元模块ⅱ输出信号u2和脉冲电源信号输出信号u6控制抑制信号判断模块ⅰ,当突触神经元模块ⅱ输出信号u2与脉冲电源信号输出信号u6均输出高电平,则与门d2导通,抑制信号判断模块ⅰ开始响应,使压控开关s3导通输出电源v3的脉冲信号,压控开关的输出端连接有保护电阻r

16

,保护电阻r

16

的另一端、压控开关s3负向输入端和电压脉冲源v3负极均接地,压控开关s3的一个触点与忆阻m7的a极相连接,当压控开关s3的一个触点的输出电压值小于忆阻m7的阈值电压,忆阻m7的阻值维持在50ω;当若压控开关s3的一个触点的输出电压大于忆阻m7的阈值电压,忆阻m7的阻值下降到32ω,如图4所示,忆阻m7的k极与运算放大器op9的反相输入端和电阻r

17

相连接,使运算放大器op9的输出电压输出到输入信号中,如图3中的v(r5)所示,用于实现操作性条件反射中的负向惩罚。压控开关s5的正向输入端与电压脉冲源v3的负极相连接,压控开关s5的一个触点与保护电阻r

18

相连接,保护电阻r

18

的另一端和压控开关s5的负向输入端均接地,使忆阻m7的阻值恢复。

50.所述抑制信号判断模块ii包括nmos管t1、电阻r

29

、电源v8和电源v9;所述抑制信号接收处理模块ii包括忆阻m8、电容c3、电阻r

19

、运算放大器op

10

、电压求和单元sum1、运算放

大器op

11

和电源v

10

;所述nmos管t1的栅极与运算放大器op

17

的输出端相连接,nmos管t1的漏极分别与电阻r

29

的一端、忆阻m8的a极相连接,电阻r

29

的另一端与电源v8的正极相连接,电源v8的负极接地,nmos管t1的源极与电源v9的正极相连接,电源v9的负极接地,忆阻m8的k极与运算放大器op

10

的反相输入端相连接,运算放大器op

10

的反相输入端与运算放大器op

10

的输出端之间连接有电阻r

19

,电阻r

19

上并联有电容c3,运算放大器op

10

的正相输入端接地,运算放大器op

10

的输出端与电压求和单元sum1的第一输入端相连接,电压求和单元sum1的第二输入端与运算放大器op7的输出端相连接,电压求和单元sum1的输出端与运算放大器op

11

的反相输入端相连接,运算放大器op

11

的正相输入端与电源v

10

的正极相连接,运算放大器op

11

的输出端与电阻r7的另一端相连接,输出正性奖励对负性惩罚的抑制电压,如图3中的v(r7)所示,电源v

10

的负极接地。

51.如图1中的抑制模块ⅱ所示,突触神经元模块ⅰ输出信号u1控制抑制信号判断模块ⅱ,当突触神经元模块ⅰ输出信号u1输出高电平时,nmos管t1输出通过保护电阻r

29

的电源v8,电源v8输出低电平,忆阻m8的a极与nmos管t1相连接,电源v8的输出信号低于忆阻m8的阈值电压,如图4所示,忆阻m8的阻值维持在1kω;当突触神经元模块ⅱ输出信号u1输出低电平时,nmos管t1输出高电平的电源v8,大于忆阻m8的阈值电压,忆阻m8的阻值快速下降到100ω,忆阻m8的k极与运算放大器op9的反相输入端、电阻r

19

和电容c3相连接,忆阻m8的k极分别与电容c3的一端、电阻r

19

的一端和运算放大器op

10

的反向输入端相连接,运算放大器op

10

的同相输入端接地,电压求和单元sum1的一个输入端分别与电容c3的另一端、电阻r

19

的另一端和运算放大器op

10

的输出端相连接,突触神经元ⅱ的抑制信号通过电压求和单元sum1的另一个输入端输入,运算放大器op

11

的反相输入端与电压求和单元sum1的输出端相连接,电源v

10

的正极与运算放大器op

11

的同相输入端相连接,若电压求和单元sum1的输出信号大于电源v

10

的电压,则运算放大器op

11

输出

‑

0.4v电压,若单元sum1的输出信号小于电源v

10

的电压,则运算放大器op

11

输出0.2v电压,op

11

的输出信号反馈到输入信号中,实现正向奖励对负性惩罚的抑制功能。

52.所述促进信号判断模块i包括与门d3、压控开关s4、电压脉冲源v4和电阻r

20

;所述促进信号接收处理模块i包括忆阻m9、运算放大器op

12

和电阻r

21

;所述促进信号恢复模块i包括压控开关s6和电阻r

22

;促进信号判断模块ii包括nmos管t2、电阻r

30

、电源v

11

和电源v

12

;所述抑制信号接收处理模块ii忆阻m

10

、电容c4、电阻r

23

、运算放大器op

13

、电压求和单元sum2、非门d5、运算放大器op

14

和电源v

13

。

53.所述与门d3的输入端分别与非门d1的输出端、运算放大器op8的输出端相连接,与门d3的输出端与压控开关s4的正相输入端相连接,压控开关s4的反相输入端接地,压控开关s4的第一触点分别与忆阻m9的k极、电阻r

20

的一端相连接,压控开关s4的第二触点与电压脉冲源v4的正极相连接,电压脉冲源v4的负极分别与电阻r

20

的另一端、压控开关s6的正相输入端相连接,电压脉冲源v4的负极接地,忆阻m9的a极与运算放大器op

12

的反相输入端相连接,运算放大器op

12

的反相输入端与运算放大器op

12

的输出端之间连接有电阻r

21

,运算放大器op

12

的正相输入端接地,运算放大器op

12

的输出端与电阻r6的另一端相连接,输出负性惩罚对正性奖励的促进电压,压控开关s6的第一触点与电阻r

22

的一端相连接,压控开关s6的第二触点与电阻r6的另一端相连接,电阻r

22

的另一端和压控开关s6的反相输入端均接地。

54.所述nmos管t2的栅极与运算放大器op

17

的输出端相连接,nmos管t2的漏极分别与

电阻r

30

的一端、忆阻m

10

的a极相连接,电阻r

30

的另一端与电源v

11

的正极相连接,电源v

11

的负极接地,nmos管t2的源极与电源v

12

的正极相连接,电源v

12

的负极接地,忆阻m

10

的k极与运算放大器op

13

的反相输入端相连接,运算放大器op

13

的反相输入端与运算放大器op

13

的输出端之间连接有电阻r

23

,电阻r

23

上并联有电容c4,运算放大器op

13

的正相输入端接地,运算放大器op

13

的输出端与电压求和单元sum2的第一输入端相连接,电压求和单元sum2的第二输入端与非门d5的输出端相连接,非门d5的输入端与运算放大器op8的输出端相连接,电压求和单元sum2的输出端与运算放大器op

14

的反相输入端相连接,运算放大器op

14

的正相输入端与电源v

13

的正极相连接,运算放大器op

14

的输出端与电阻r8的另一端相连接,电源v

13

的负极接地。

55.如图1中的促进模块ⅰ所示,突触神经元模块ⅱ输出信号u4和脉冲电源信号输出信号u8控制促进信号判断模块ⅰ,当突触神经元模块ⅱ输出信号u4与脉冲电源信号输出信号u8均输出高电平,则与门d3导通,促进信号判断模块ⅱ开始响应,使压控开关s4导通输出电源v4的脉冲信号,压控开关的输出端连接有保护电阻r

20

,保护电阻r

20

的另一端、压控开关s4负向输入端和电压脉冲源v4负极均接地,压控开关s4的一个触点与忆阻m9的a极相连接,若压控开关s4的一个触点的输出电压值小于忆阻m9的阈值电压,如图4所示,忆阻m9的阻值维持在50ω;当若压控开关s4的一个触点的输出电压大于忆阻m9的阈值电压,忆阻m7的阻值快速上升到175ω,忆阻m9的k极与运算放大器op

12

的反相输入端和电阻r

21

相连接,使运算放大器op

12

的输出电压输出到输入信号中,如图3中的v(r6)所示,用于来实现负向惩罚对于正向激励是有促进作用。压控开关s6的正向输入端与电压脉冲源v4的负极相连接,压控开关s6的一个触点与保护电阻r

22

相连接,保护电阻r

22

的另一端和压控开关s6的负向输入端均接地,使忆阻m9的阻值恢复。如图1中的促进模块ⅱ所示,突触神经元模块ⅰ输出信号u5控制抑制信号判断模块ⅱ,当突触神经元模块ⅰ输出信号u5输出高电平时,nmos管t2输出通过保护电阻r

30

的电源v

11

,电源v

11

输出低电平,忆阻m

10

的a极与nmos管t2相连接,电源v

11

的输出信号低于忆阻m

10

的阈值电压,忆阻m

10

的阻值维持在1kω,当突触神经元模块ⅰ输出信号u5输出低电平时,nmos管t2输出高电平的电源v

12

,大于忆阻m

10

的阈值电压,忆阻m

10

的阻值快速下降到100ω,具体仿真图如图4所示,忆阻m

10

的k极与运算放大器op

13

的反相输入端、电阻r

23

和电容c4相连接,忆阻m

10

的k极分别与电容c4的一端、电阻r

23

的一端和运算放大器op

13

的反向输入端相连接,运算放大器op

13

的同相输入端接地,电压求和单元sum2的一个输入端分别与电容c4的另一端、电阻r

23

的另一端和运算放大器op

13

的输出端相连接,突触神经元ⅱ的抑制信号经过非门d5连接到电压求和单元sum1的另一个输入端,运算放大器op

14

的反相输入端与电压求和单元sum2的输出端相连接,电源v

13

的正极与运算放大器op

14

的同相输入端相连接,,若电压求和单元sum2的输出信号大于电源v

13

的电压,则运算放大器op

13

输出

‑

0.6v电压,若单元sum1的输出信号小于电源v

10

的电压,则运算放大器op

11

输出

‑

0.3v电压,op

14

的输出信号反馈到输入信号中,输出负性惩罚对正向奖励的促进电压,如图3中的v(r8)所示,实现的促进功能。

56.所述电压判断模块包括pmos管t3、电阻r

24

、电源v

15

、电源v

16

、nmos管t4、电阻r

25

、电源v

17

、电源v

18

、与门d4、压控开关s7、电压脉冲源v

14

、电阻r

26

和电压求和单元sum3。所述脉冲电源信号分别与pmos管t3的栅极、与门d4的输入端和压控开关s7的正相输入端相连接,pmos管t3的漏极分别与电阻r

24

的一端、nmos管t4的栅极相连接,电阻r

24

的另一端与电源v

15

的正

极相连接,电源v

15

的负极接地,pmos管t3的源极与电源v

16

的正极相连接,电源v

16

的负极接地,nmos管t4的漏极分别与电阻r

25

的一端、与门d4的输入端相连接,电阻r

25

的另一端与电源v

17

的正极相连接,电源v

17

的负极接地,nmos管t4的源极与电源v

18

的正极相连接,电源v

18

的负极接地;压控开关s7的第一触点分别与电阻r

26

的一端、电压求和单元sum3的第一输入端相连接,压控开关s7的第二触点与电压脉冲源v

14

的正极相连接,压控开关s7的反相输入端、电压脉冲源v

14

的负极和电阻r

26

的另一端均接地;与门d4的输出端与电压求和单元sum3的第二输入端相连接,电压求和单元sum3的输出端与电压接收处理模块相连接。

57.所述电压接收处理模块包括忆阻m

11

、电流源i1、电流源i2、pmos管t5、pmos管t6、nmos管t7、nmos管t8、nmos管t9、pmos管t

10

、pmos管t

11

、nmos管t

12

、电阻r

27

、电源v

19

和电源v

20

;所述电压求和单元sum3的输出端分别与忆阻m

11

的a极、电阻r

27

的一端相连接,忆阻m

11

的k极分别与pmos管t6的源极、nmos管t

12

的源极相连接,pmos管t6的栅极与电流源i1的负极相连接,电流源i1的正极分别与nmos管t7的源极、电源v

19

的正极和nmos管t8的源极相连接,电源v

19

的负极接地,电流源i1的负极分别与pmos管t5的漏极、pmos管t5的栅极相连接,pmos管t5的源极和nmos管t9的源极均接地,nmos管t9的漏极、nmos管t9的栅极和nmos管t

12

的栅极均与电流源i2的正极相连接,电流源i2的负极分别与电源v

20

的正极、pmos管t

10

的源极和pmos管t

11

的源极相连接,电源v

20

的负极接地,pmos管t

10

的漏极、pmos管t

10

的栅极和pmos管t

11

的栅极均与nmos管t

12

的漏极相连接,pmos管t

11

的漏极分别与电阻r

27

的另一端、nmos管t8的漏极和突触神经元模块iii相连接,nmos管t8的栅极、nmos管t7的栅极、nmos管t7的漏极均与pmos管t6的漏极相连接。

58.如图1中的电压控制模块所示,脉冲电源信号输入信号u6到电压判断模块,pmos管t3和nmos管t4相当于逻辑门,当输入信号u6为低电平时,pmos管t3的漏极输出0v,当输入信号u6为高电平时,pmos管t3的漏极输出

‑

2.1v,然后通过nmos管t4,当pmos管t3的漏极输出为0v时,nmos管t4的漏极输出0v,当pmos管t3的漏极输出为

‑

2.1v时,nmos管t4的漏极输出1v。脉冲电源信号输入信号u6和nmos管t4的漏极分别与与门d4的两个输入端相连接,与门d3输出信号在低电平时输出

‑

1v,高电平时输出1.2v。通过施加第三压控单元,来实现操作性条件反射中的即时性,若鸽子听到噪声时,没有第一时间去啄黄球,那么产生的负向惩罚大于立即啄黄球时的负向惩罚,且即使随后去啄黄球,消除噪声的效果没有立即啄黄球后消除噪声的效果好,如图5中的v(m

12

(1))和v(m

12

(2))。通过电流源i1、电流源i2、pmos管t5、pmos管t6、nmos管t7、nmos管t8、nmos管t9、pmos管t

10

、pmos管t

11

、nmos管t

12

、电阻r

27

、电源v

19

和电源v

20

,组成的电流镜,可以调节输入输出比。

59.所述突触神经元模块iii包括忆阻m

12

、电阻r

28

、运算放大器op

15

、数学运算单元abm3、电源v

21

和运算放大器op

16

,电阻r

27

的另一端分别与忆阻m

12

的k极、数学运算单元abm3的in2输入端相连接,忆阻m

12

的a极与运算放大器op

15

的反相输入端相连接,运算放大器op

15

的反相输入端与运算放大器op

15

的输出端之间连接有电阻r

28

,运算放大器op

15

的正相输入端接地,运算放大器op

15

的输出端与数学运算单元abm3的in1输入端相连接,数学运算单元abm3的out输出端与运算放大器op

16

的正相输入端相连接,运算放大器op

16

的反相输入端与电源v

21

的正极相连接,电源v

21

的负极接地。

60.如图1中的突触神经元ⅲ所示,在0

‑

30s,电压控制模块输出信号u

12

的电压值小于忆阻m

12

的阈值电压,忆阻m

12

的阻值维持在800ω,在30

‑

60s,电压控制模块输出信号u

12

的电

压值大于忆阻m

12

的正阈值电压,忆阻m5的阻值从800ω下降到200ω。在忆阻m

12

的a极与电阻r

28

和运算放大器op

15

的反相输入端相连接,运算放大器op

15

的同相输入端接地,电阻r

28

的另一端和运算放大器op

15

的输出端与数学运算单元abm3一个输入端相连接,数学运算单元abm3另一端与电压控制模块输出信号u

12

相连接,abm3的输出值为

‑

in2/in1*10=m

12

/100,数学运算单元abm3的输出端与运算放大器op

16

的同相输入端相连接,运算放大器op

16

的反相输入端与电源v

21

的正极相连接,电源v

21

的负极接地,运算放大器op

16

相当于一个阈值为v

21

的激活函数,当op

16

的同相输入端接收到的电压小于v

21

时,op

16

输0v电压,当收到的电压大于v5时,op

17

输出5v电压。

61.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1