驱动装置的制作方法

1.本公开涉及一种驱动装置。

背景技术:

2.作为驱动装置的示例,jp 2018-150884 a公开了一种驱动器电路。该驱动器电路与微型计算机一起安装到电子控制单元(ecu)。该驱动器电路包括驱动器、微型计算机监控电路等。该微型计算机监控电路在微型计算机运行正常时向驱动器输入驱动允许指令,并且在微型计算机运行异常时向驱动器输入驱动禁止指令。该驱动器在驱动允许指令被输入的时段期间响应于负载控制信号驱动负载,并且在驱动禁止指令被输入的时段期间停止驱动负载。

技术实现要素:

3.尽管这不是传统技术,但驱动装置可包括用于监控负载的导通(conduction)状态的监控电路。此外,驱动装置可临时地存储负载控制信号和监控电路的监控结果。在这样的驱动装置中,诸如负载控制信号和监控结果的存储信息可能发生异常。但是,jp 2018-150884 a的驱动器电路不能确定存储信息的异常。

4.本公开的一个目的是提供一种能够确定存储信息的异常的驱动装置。

5.根据本公开的第一方面的驱动装置包括控制存储器、驱动器、判定存储器和比较器。所述控制存储器被配置为存储包括指示每个负载的导通状态的信号的控制图谱(control pattern)。所述驱动器被配置为根据所述控制图谱控制半导体开关。所述半导体开关分别对应于所述负载。所述判定存储器被配置为存储用于判定所述控制图谱的异常的判定图谱。所述判定图谱是表示每个负载的导通状态的导通图谱。比较器被配置为比较判定图谱和控制图谱作为比较图谱,并且响应于判定图谱和控制图谱满足预定的对应关系,判定控制图谱已经发生异常。

6.这样,根据第一方面的所述驱动装置存储所述控制图谱和所述判定图谱。然后,所述驱动装置将所述判定图谱与所述控制图谱进行比较以判定所述控制图谱的异常。

7.根据本公开的第二方面的驱动装置包括驱动器、监控器存储器、判定存储器、和比较器。所述驱动器被配置为根据控制图谱控制半导体开关。所述半导体开关分别对应于负载。所述控制图谱包括指示每个负载的导通状态的信号。所述监控器存储器被配置为存储监控器图谱,所述监控器图谱是监控每个负载的导通状态的结果。所述判定存储器被配置为存储用于判定监控器图谱的异常的判定图谱。所述判定图谱是表示每个负载的导通状态的导通图谱。所述比较器被配置为比较所述判定图谱和所述监控器图谱作为比较图谱,并响应于所述判定图谱和所述监控器图谱满足预定的对应关系,判定所述监控器图谱已经发生异常。

8.这样,根据第二方面的所述驱动装置存储所述监控器图谱和所述判定图谱。然后,所述驱动装置将所述判定图谱与所述监控器图谱进行比较以判定所述监控器图谱的异常。

9.根据本公开的第三方面的驱动装置包括控制存储器、驱动器、监控器存储器、判定存储器、和比较器。所述控制存储器被配置为存储包括指示每个负载的导通状态的信号的控制图谱。所述驱动器被配置为根据所述控制图谱控制半导体开关。所述半导体开关分别对应于负载。所述监控器存储器被配置为存储监控器图谱,所述监控器图谱是监控每个负载的导通状态的结果。所述判定存储器被配置为存储用于判定所述控制图谱的异常和所述监控器图谱的异常的判定图谱。所述判定图谱是表示每个负载的导通状态的导通图谱。所述比较器被配置为将所述判定图谱与所述控制图谱和所述监控器图谱进行比较作为比较图谱,响应于所述判定图谱和所述控制图谱满足预定的对应关系,判定所述控制图谱已经发生异常,并且响应于所述判定图谱与监控器图谱满足预定的对应关系,判定所述监控器图谱已经发生异常。

10.这样,根据第三方面的所述驱动装置存储所述控制图谱、所述监控器图谱、和所述判定图谱。然后,所述驱动装置将所述判定图谱与控制图谱进行比较以判定所述控制图谱的异常。此外,所述驱动装置将所述判定图谱与所述监控器图谱进行比较以判定所述监控器图谱的异常。

附图说明

11.本公开的上述和其他目的、特征和优点将通过参考附图进行的以下详细描述而变得更加明显。在图中:

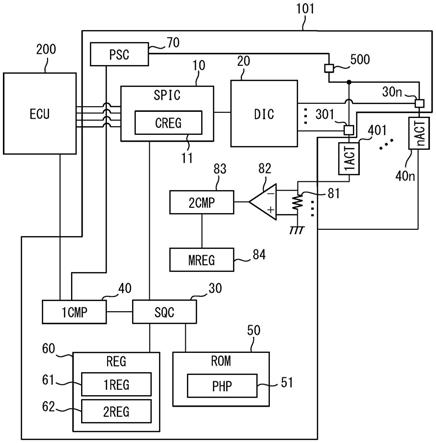

12.图1是显示根据第一实施例的驱动装置的示意性结构的电路图;

13.图2是显示根据第一实施例的驱动ic部的示意性结构的电路图;

14.图3是显示第一实施例中的禁止图谱的示意性结构的图表;

15.图4是显示根据第一实施例的控制寄存器(control register)的示意性结构的图表;

16.图5是显示根据第一实施例的驱动装置的操作的流程图;

17.图6是显示根据第一实施例的时序电路(sequence circuit)的操作的框图;

18.图7是显示第一实施例中的禁止图谱的设定操作的图表;

19.图8是显示根据第一实施例的控制图谱的设定操作的图表;

20.图9是显示根据第二实施例的驱动装置的示意性结构的电路图;

21.图10是显示第二实施例中的允许图谱的示意性结构的图表;

22.图11是显示根据第二实施例的驱动装置的操作的流程图;

23.图12是显示根据第三实施例的驱动装置的示意性结构的电路图;

24.图13是显示根据第三实施例的驱动装置的操作的流程图;

25.图14是显示根据第四实施例的驱动装置的示意性结构的电路图;

26.图15是显示根据第四实施例的驱动装置的操作的流程图;

27.图16是显示根据第五实施例的驱动装置的示意性结构的电路图;和

28.图17是显示根据第六实施例的驱动装置的示意性结构的电路图。

具体实施方式

29.下文将参考附图描述本公开的多个实施例。在每个实施例中,与前述实施例中描

述的那些部分相对应的部分用相同的附图标记表示,并且在某些情况下将省略冗余的描述。在每个实施例中,在仅描述了该配置的一部分的情况下,该配置的其它部分可以参考并应用在前的另一实施例。

30.(第一实施例)

31.将参照图1至图8描述根据第一实施例的驱动装置101。驱动装置101能够应用于例如用于驱动被安装在车辆上的负载的电路。在下文中,将描述应用于车辆的自动变速器(automatic transmission)的示例。

32.《自动变速器》

33.将描述自动变速器的示意性配置。自动变速器包括例如阀体、传动机构(transmission mechanism)、油泵、泊车锁机构(parking lock mechanism)等。传动机构具有多个摩擦元件,包括例如离合器和制动器。传动机构可通过选择性地接合每个摩擦元件来分级地改变传动比。

34.在阀体内形成有用于调节被供给至传动机构的液压油的压力的液压回路。阀体具有多个电磁阀(solenoid valve),电磁阀调节从油泵泵出的液压油并将液压油供给到摩擦元件。电磁阀具有螺线管(solenoid)。螺线管有时被称为线圈。液压油是通过控制到螺旋管的电导来调节的。

35.电磁阀对应于负载。另外,在本实施例中,采用电磁阀作为致动器401~40n,将在下面进行描述。因此,负载的导通状态对应于电磁阀(螺线管)的导通状态。线性电磁阀可以被用作所述电磁阀。

36.当选择了泊车档时,泊车锁机构设置泊车锁以锁定自动变速器的输出轴(车轴(axle))的旋转。当从泊车锁的状态选择泊车档以外的其他档位时,泊车锁机构释放泊车锁。因此,输出轴被解锁。但是,自动变速器不限于上述配置。

37.《负载驱动系统》

38.接下来,将参考图1描述负载驱动系统的示意性配置。图1是示出负载驱动系统的图。在图1中,致动器401至40n(1act至nact)的导通路径被简化。

39.负载驱动系统至少包括驱动装置101和电子控制单元(ecu)200。负载驱动系统控制致动器401至40n的导通驱动。此外,可以说负载驱动系统通过导通和驱动致动器401至40n来控制包括阀体的自动变速器。

40.请注意,n是2或更大的自然数。在本实施例中,以n=5为例。因此,本实施例采用其中第一致动器401至第五致动器405被导通和驱动的示例。此外,本实施例采用通过控制第一致动器401至第五致动器405的驱动而在第一档速至第五档速之间切换自动变速器的示例。若没有必要彼此区分,致动器401至405也称为致动器40n。

41.但是,本公开不限于以上示例。本公开还可以采用通过控制多个致动器40n的驱动而在第一档速至第八档速之间切换自动变速器的示例。此外,本公开还可以采用通过控制多个致动器40n的驱动而在p档、r档、n档和d档之间切换自动变速器的示例。此外,作为致动器40n,也可以采用开-关电磁阀。

42.ecu200包括具有至少一个中央处理单元(cpu)、至少一个存储器等的微型计算机。此外,各种传感器、其他ecu等连接到ecu200。存储器存储程序、数据等。所述数据包括预先存储的数据、从所述传感器输出的传感器信号等。

43.在ecu200中,cpu运行程序。通过运行程序,cpu使用数据的同时执行各种算术处理。ecu200输出负载控制信号等作为算术处理的结果。

44.在负载驱动系统中,驱动装置101设置在阀体上。即,驱动装置101具有与自动变速器一体的机电结构。ecu200与自动变速器机械分离。

45.ecu200和驱动装置101通过铜线等连接。在本实施例中,ecu200和驱动装置101通过串行外设接口(serial peripheral interface,简称spi)通信来发送和接收数据。ecu200向驱动装置101发送负载控制信号等。当驱动装置101接收到负载控制信号时,驱动装置101响应于负载控制信号而操作。稍后将详细描述驱动装置101的配置和操作。

46.如图1和图2所示,负载驱动系统包括多个驱动开关301至30n。驱动开关301至30n分别设置在致动器40n的导通路径上。因此,本实施例以设置第一驱动开关301至第五驱动开关305为例。当不需要彼此区分时,驱动开关301至305也被称为驱动开关30n。驱动开关30n设置在驱动装置101中。

47.当驱动开关30n接通时,电流被供给到相应的致动器40n。当驱动开关30n关断时,向相应的致动器40n的电流供应被切断。换言之,当相应的驱动开关30n接通时,每个致动器40n导通。此外,当相应的驱动开关30n关断时,每个致动器40n不导通。

48.如图1和图2所示,负载驱动系统包括电源开关500。另外,负载驱动系统包括各种传感器。但是,负载驱动系统不是必须包括电源开关500和传感器,并且电源开关500和传感器可布置在负载驱动系统的外部。

49.电源开关500设置在通到致动器40n的导通路径上。作为电源开关500,可采用诸如金属氧化物硅场效应晶体管(metal-oxide silicon field-effect transistor,简称mosfet)的半导体开关。为致动器401至405提供单个(公共)电源开关500。当电源开关500接通时,能够向每个致动器40n供应电流。当电源开关500关断时,供应至每个致动器40n的电流被切断。相对于致动器40n,电源开关500可布置在高侧(high-side),即电源侧(power-supply side),或者可布置在低侧,即接地(gnd)侧。本实施例的电源开关500布置在高侧。电源开关500设置在驱动装置101中。

50.传感器检测负载的状态。传感器检测包括阀体的自动变速器的状态。传感器的示例包括液压传感器、旋转传感器、油温传感器、泊车锁传感器等。液压传感器检测液压回路中液压流体的压力。旋转传感器检测自动变速器的转速。旋转传感器包括例如检测自动变速器的输入侧的转速的传感器和检测自动变速器的输出侧的转速的传感器。油温传感器检测液压回路中液压油的温度。泊车锁传感器检测泊车锁机构的状态。

51.《驱动装置的配置》

52.将参照图1、2至4和6描述驱动装置101。在图2中,为方便起见,仅示出了对应于一个致动器401的部分。

53.驱动装置101是用于导通和驱动致动器401至405的电路。此外,驱动装置101通过控制驱动开关301至305来导通和驱动致动器401至405。与ecu200不同,驱动装置101不包括微型计算机。即,驱动装置101通过硬件逻辑来导通和驱动致动器401至405。第一驱动开关301至第五驱动开关305中的每一个对应于半导体开关。

54.驱动装置101主要包括:spi电路(spic)10,其包括控制寄存器11;驱动ic(dic)20;第一比较器(1cmp)40;和只读存储器(rom)50。此外,驱动装置101包括时序电路(sqc)30、寄

存器单元(reg)60、电源电路(psc)70、电流检测电阻81、放大器82、第二比较器(2cmp)83、监控器寄存器(mreg)84等。此外,驱动装置101包括所述驱动开关30n和所述电源开关500。

55.spi电路10是连接到ecu200并与ecu200进行串行通信的电路。此外,spi电路10连接到驱动ic20、时序电路30等。spi电路10具有将接收到的串行数据转换为并行数据的转换电路。此外,spi电路10具有控制寄存器(creg)11。控制寄存器11对应于控制存储器。

56.从ecu200发送的串行数据的示例包括用于导通和驱动致动器401至405的负载控制信号。负载控制信号包括指示致动器401至405中的每一个的导通状态的信号(值)。即,可以说,负载控制信号包括表示分别对应于致动器401至405中的每一个的导通状态的信号。

57.负载控制信号包括例如1作为指示导通的信号和0作为指示不导通的信号。因此,负载控制信号可以用0和1来表示。在本实施例中,以5位(bit,也称比特)的负载控制信号为例。但是,本公开不限于该示例,可以采用任何多位的负载控制信号。

58.如图4所示,负载控制信号转换为并行数据并存储在控制寄存器11中。转换为并行数据的负载控制信号能够被看作是控制图谱(control pattern)。因此,负载控制信号对应于控制图谱。控制寄存器11具有与致动器401至405对应的地址位111至115。在控制寄存器11中,负载控制信号中表示致动器401至405中的每一个的导通状态的信号被写入每个地址位中。

59.第一位111对应于第一致动器401。第二位112对应于第二致动器402。第三位113对应于第三致动器403。第四位114对应于第四致动器404。第五位115对应于第五致动器405。

60.图4显示将11101作为控制图谱写入控制寄存器11的示例。此外,该控制图谱显示其中第5位115被窜改(garbled)的状态。即,原本应该在控制寄存器11中写入11100作为控制图谱。但是,在控制寄存器11中,由于驱动装置101的内部异常而将11101作为控制图谱写入。

61.将控制图谱与判定图谱(determination pattern)进行比较。因此,控制图谱可以说是比较图谱(comparison pattern)。存储在控制寄存器11中的控制图谱对应于当前时间的负载控制信号。因此,控制图谱可以说是当前时间值。

62.本实施例以spi电路10获取负载控制信号为例,但本公开不限于此,负载控制信号可通过符合控制器局域网(can)协议的通信电路来获取。在这种情况下,驱动装置101通过通信总线连接到ecu200。驱动装置101获取被包含在通过can通信接收的消息(message)中的负载控制信号。在控制寄存器11中,写入负载控制信号中表示导通状态的信号。

63.进一步地,在本公开中,可以根据多个端子的电平(level)来获取负载控制信号。在这种情况下,驱动装置101通过多条铜线连接到ecu200。驱动装置101通过比负载控制信号中表示导通状态的信号数量更多的铜线连接到ecu200。驱动装置101包括分别与铜线连接的端子。然后,驱动装置101获取每个端子的电平(hi,low)作为负载控制信号。对应于每个端子的电平的信号被写入控制寄存器11。

64.如图1和图2所示,驱动ic20连接到驱动开关301至305。驱动ic20根据控制图谱控制驱动开关301至305。即,驱动ic20根据存储在控制寄存器11中的控制图谱来输出用于接通或关断驱动开关301至305的驱动信号。此外,驱动ic20根据存储在控制寄存器11中的控制图谱来选择性地接通或关断驱动开关301至305。驱动ic20对应于驱动器。

65.可以采用脉宽调制(pwm)信号作为驱动信号。在这种情况下,驱动ic20可通过改变

pwm信号的占空比(duty ratio)来改变流过致动器40n的电流(即,导通电流)。

66.例如,当控制图谱为11100时,驱动ic20接通第一驱动开关301至第三驱动开关303。结果,驱动ic20使第一致动器401至第三致动器403处于导通状态。此时,驱动ic20关断第四驱动开关304和第五驱动开关305。结果,驱动ic20使第四致动器404和第五致动器405处于不导通状态。

67.如图6所示,时序电路30包括第一数据加载器31、第二数据加载器32等。此外,时序电路30包括多个开关元件等。时序电路30与时钟同步工作。

68.第一数据加载器31将存储在控制寄存器11中的控制图谱写入第一数据寄存器(1reg)61。即,如图8所示,第一数据加载器31加载控制寄存器11中位111至115的信号并将这些信号分别写入第一数据寄存器61的位621至625。

69.另一方面,第二数据加载器32将存储在rom50中的禁止图谱(prohibition pattern,简称为php)51写入第二数据寄存器(2reg)62。即,如图7所示,第二数据加载器32加载禁止图谱51中的位信号并将这些信号写入第二数据寄存器62的位。

70.第一比较器40包括比较器。第一比较器40将稍后描述的判定图谱与控制图谱进行比较。第一比较器40依次比较判定图谱的每个信号和控制图谱的每个信号。第一比较器40比较判定图谱与控制图谱,并且判定该判定图谱与控制图谱是否满足预定的对应关系。第一比较器40对应于比较器。

71.在本实施例中,采用禁止图谱51作为判定图谱。因此,本实施例中的预定对应关系表示禁止图谱51与控制图谱匹配。即,当禁止图谱51与控制图谱匹配时,第一比较器40判定满足预定的对应关系。另一方面,当禁止图谱51与控制图谱不同时,第一比较器40判定不满足预定的对应关系。

72.与禁止图谱51匹配的控制图谱是禁止导通图谱(prohibited conduction pattern)。因此,该控制图谱是发生了窜改位等的异常导通图谱。另一方面,与禁止图谱51不同的控制图谱不是禁止导通图谱。因此,该控制图谱是没有发生窜改位等的正常导通图谱。

73.因此,响应于禁止图谱51与控制图谱匹配,第一比较器40判定控制图谱异常。另一方面,响应于禁止图谱51与控制图谱不同,第一比较器40判定控制图谱正常。

74.取决于禁止图谱51与控制图谱是否匹配,第一比较器40的输出信号是不同的。如果它们匹配,则第一比较器40输出表示控制图谱异常的异常信号。如果它们不同,则第一比较器40输出表示控制图谱正常的正常信号。异常信号被输出到电源电路70和ecu200中的至少一个。电源电路70和ecu200中的至少一个是指电源电路70、ecu200、或电源电路70和ecu200两者。

75.可以说,第一比较器40向电源电路70输出异常信号以切断到致动器40n的电源。另一方面,可以说第一比较器40向ecu200输出异常信号以向ecu200通知异常。

76.rom50存储禁止图谱51。禁止图谱51是表示每个致动器40n的导通状态的导通图谱。此外,禁止图谱51是用于判定控制图谱异常的其中一个判定图谱。即,rom50存储禁止图谱51作为判定图谱。rom50对应于判定存储器。

77.禁止图谱51是禁止作为致动器40n的导通状态的导通图谱。禁止图谱51是引起作为自动变速器的不利操作的导通图谱。因此,与控制图谱等不同,禁止图谱51被预先存储在

rom50中。

78.图3是禁止图谱51的一个示例。在本实施例中,采用了五个禁止图谱51。在图3中,第一致动器401显示为1act,第二致动器402显示为2act,第三致动器403显示为3act,第四致动器404显示为4act,第五致动器405显示为5act。

79.rom50具有分别对应于致动器401至405的地址位。在rom50中,表示禁止图谱51中致动器401至405的导通状态的信号(值)被写入地址位。本实施例以5位控制图谱为例。因此,每个禁止图谱51具有5位,这与控制图谱相同。每个禁止图谱51包括1作为表示导通的信号和0作为表示不导通的信号。因此,每个禁止图谱51可以用0和1表示。

80.第一禁止图谱51(1ng)是11101。第二禁止图谱51(2ng)是01111。第三禁止图谱51(3ng)是11110。第四禁止图谱51(4ng)是01100。第五禁止图谱51(5ng)是11011。rom50可存储至少一个禁止图谱51。

81.寄存器单元60(reg)包括第一数据寄存器61和第二数据寄存器62。在第一数据寄存器61和第二数据寄存器62中,将由第一比较器40比较的导通图谱由时序电路30设定。在第一数据寄存器61中,设定控制图谱。在第二数据寄存器62中,设定判定图谱(禁止图谱)。

82.如图1和图2所示,电源电路70是用于接通或关断电源开关500的电路。例如,当从第一比较器40输入异常信号时,电源电路70输出表示关断电源开关500的信号。即,当控制图谱发生异常时,电源电路70关断电源开关500并且切断对每个致动器40n的电流供应。此外,可以说电源电路70关断电源开关500以防止每个致动器40n被异常控制图谱驱动。异常信号也可以说是指示关断电源开关500的信号。

83.电流检测电阻器81与放大器82一起构成电流检测单元。为每个致动器40n单独提供电流检测单元。因此,在本实施例中,驱动装置101具有五个电流检测单元。在图1中,作为代表性示例,仅示出了对应于第一致动器401的电流检测单元。

84.每个电流检测单元检测实际流过相应致动器40n(螺旋管)的电流。换言之,每个电流检测单元检测相应的致动器40n的导通状态。此外,可以说每个电流检测单元监控相应的致动器40n的导通状态。

85.除了电流检测电阻器81和放大器82之外,每个电流检测单元可包括去除由放大器82放大的电压的噪声的滤波器。滤波器可包括例如电阻器和电容器。

86.电流检测电阻器81与致动器401串联连接。电流检测电阻器81相对于第一致动器401设置在接地侧(下游侧)。放大器82放大电流检测电阻器81两端产生的与电流成比例的电压。因此,放大器82输出与流过第一致动器401的电流成比例的电压信号。因此,每个电流检测单元输出与流过相应致动器40n的电流成比例的电压信号。

87.第二比较器83包括比较器。为每个致动器40n单独提供第二比较器83。此外,第二比较器83设为具有电流检测电阻器81和放大器82的成套器件。在本实施例中,在驱动装置101中设置了五个第二比较器83。在图1中,作为代表性示例,仅示出了对应于第一致动器401的第二比较器83。

88.第二比较器83将放大器82输出的电压信号与参考值进行比较。第二比较器83在电压信号高于参考值时输出正值,在电压信号低于参考值时输出负值。作为参考值,例如,假定离合器接合时的电流值的电压值可以被使用。

89.即,可以说第二比较器83输出表示由每个电流检测单元监控的每个致动器40n的

导通状态的监控结果。例如,当第一致动器401导通时,第二比较器83输出正值。此外,例如当第一致动器401不导通时,第二比较器83输出负值。

90.每个第二比较器83的输出被写入监控器寄存器84。即,可以说监控器寄存器84存储作为监控每个致动器40n的导通状态的结果的监控器图谱。监控器寄存器84对应于监控器存储器。

91.监控器寄存器84具有对应于致动器401至405的地址位。在监控器寄存器84中,表示致动器401至405中的每一个的导通状态的信号(值)被写入每个地址位中。表示致动器401至405中的每一个的导通状态的信号是第二比较器83中的每一个的输出。

92.在监控器寄存器84中,例如,1被写入作为表示导通的信号并且0被写入作为表示不导通的信号。因此,监控器图谱可以用0和1来表示。本实施例以5位控制图谱为例。因此,监控器图谱具有5位,与控制图谱相同。

93.监控器寄存器84的第一位对应于第一致动器401。第二位对应于第二致动器402。第三位对应于第三致动器403。第四位对应于第四致动器404。第五位对应于第五致动器405。

94.监控器图谱是监控每个致动器40n的导通状态的结果。因此,当没有异常时,监控器图谱和控制图谱是相同的图谱。例如,当控制图谱为11100时,监控器图谱为11100。但是,当监控器图谱和控制图谱中的至少一个异常时,监控器图谱和控制图谱变成为不同的图谱。

95.这里的异常包括上述的窜改位、电流检测电阻器81与每个致动器40n之间的电流路径中的接地故障等。这些可视为驱动装置101的内部异常。驱动装置101不是必须包括电流检测单元、第二比较器83、和监控器寄存器84。例如,当控制图谱为11100且电流检测电阻器81与第一致动器401之间的电流路径发生接地故障时,则监控器图谱变为01100。

96.《驱动装置的操作》

97.驱动装置101的操作将参照图5至图8进行描述。当接收到负载驱动信号时,驱动装置101开始图5的流程图所示的操作。此时,假设电源电路70输出表示电源开关500接通的信号。即,每个致动器40n被供给电流。

98.在s10a中,设定禁止图谱51。如图6和图7所示,时序电路30将存储在rom50中的禁止图谱51设置在第二数据寄存器62中。更具体地,第二数据加载器32从rom50加载禁止图谱51。然后,第二数据加载器32在第二数据寄存器62中设定被加载的禁止图谱51。当禁止图谱51在第二数据寄存器62中被设定时,禁止图谱51被输出到第一比较器40。

99.当多个禁止图谱51存储在rom50中时,第二数据加载器32将存储在rom50中的禁止图谱51依次写入第二数据寄存器62。此外,当被写入第二数据寄存器62中的禁止图谱51被输出到第一比较器40时,第二数据加载器32将下一禁止图谱51写入第二数据寄存器62。

100.在s11中,设定控制图谱。如图6和图8所示,第一数据加载器31从控制寄存器11加载控制图谱。然后,第一数据加载器31在第一数据寄存器61中设定被加载的控制图谱。当控制图谱在第一数据寄存器61中被设定时,控制图谱被输出到第一比较器40。

101.在s12a中,比较所述控制图谱和所述禁止图谱。第一比较器40将第一数据寄存器61中设定的控制图谱与第二数据寄存器62中设定的禁止图谱51进行比较。当多个禁止图谱51存储在rom50中时,第一比较器40将控制图谱与每个禁止图谱51依次比较。结果,第一比

较器40将控制图谱与所有的禁止图谱51进行比较。

102.当控制图谱与所有的禁止图谱51不同时,第一比较器40进行到s13。在这种情况下,控制图谱可以被认为是正常的。

103.另一方面,当控制图谱与禁止图谱51中的一个匹配时,第一比较器40进行到s14。即,当即使禁止图谱51中的一个与控制图谱匹配时,第一比较器40进行到s14。在这种情况下,控制图谱可以被认为是异常的。在本实施例中,以控制图谱为11101为例。该控制图谱与第一禁止图谱51匹配。因此,第一比较器40判定控制图谱和禁止图谱51匹配。

104.在s13中,根据控制图谱进行供电。第一比较器40输出表示控制图谱正常的正常信号。当输入正常信号时,驱动ic20根据控制图谱向致动器40n供应电流。即,驱动ic20根据存储在控制寄存器11中的控制图谱选择性地接通或关断驱动开关301至305。结果,驱动ic20选择性地向致动器40n供应电流。

105.在s14中,通知异常。第一比较器40将表示控制图谱异常的异常信号输出至ecu200。结果,第一比较器40将异常通知给ecu200。

106.在s15中,切断电源。第一比较器40将表示控制图谱异常的异常信号输出至电源电路70。可以说,第一比较器40将异常信号输出至电源电路70以切断对致动器40n供电。当输入异常信号时,电源电路70关断电源开关500以切断对每个致动器40n的电流供应。因此,驱动装置101能防止致动器40n被异常控制图谱驱动。

107.应注意的是,根据本公开的驱动装置101必须执行s14和s15中的至少一个。

108.《效果》

109.这样,驱动装置101存储所述控制图谱和禁止图谱51。然后,驱动装置101可通过将禁止图谱51与控制图谱进行比较来判定控制图谱的异常。此外,驱动装置101可不使用微型计算机仅通过将禁止图谱51与控制图谱进行比较就能够判定控制图谱的异常。因此,驱动装置101能使用简单的配置判定控制图谱的异常。

110.作为用于判定控制图谱的异常的判定图谱,也可以采用允许作为致动器40n的导通状态的导通图谱(允许图谱)。但是,驱动装置101将禁止图谱51存储在rom50中作为判定图谱。禁止图谱51的数量小于允许图谱的数量。因此,驱动装置101能减少rom50中的判定图谱所占用的容量。

111.与ecu200不同,驱动装置101不包括微型计算机。因此,可以使驱动装置101比包括微型计算机的配置更小。此外,与包括微型计算机的配置相比,驱动装置101能减少功耗和发热。结果,与包括微型计算机的配置相比,驱动装置101对与尺寸和发热相关的可安装性的限制更少。即,与包括微型计算机的配置相比,驱动装置101能具有更高的安装自由度。此外,与包括微型计算机的配置相比,驱动装置101能减少用于功能安全性和可靠性的措施。驱动装置101能布置在致动器40n的紧邻处,从而能减少线束并且能改进可安装性。

112.以上描述了本公开的优选实施例。但是,本公开不以任何方式限于上述实施例,并且在不脱离本公开的主旨的范围内可以进行各种修改。下面将描述第二至第六实施例作为本公开的其他实施例。第二至第六实施方式可以单独实施,也可以适当组合实施。本公开可通过各种组合来执行,而不限于在实施例中描述的组合。

113.(第二实施例)

114.将参照图9、10和11描述根据第二实施例的驱动装置102。驱动装置102具有与驱动

装置101不同的判定图谱。在驱动装置102中,相同的附图标记分配给与驱动装置101相同的配置。此外,在图11的流程图中,对与图5的流程图相同的过程分配相同的步骤编号。

115.如图9所示,驱动装置102在rom50中存储允许图谱(pmp)52。允许图谱52是表示每个致动器40n的导通状态的导通图谱。此外,允许图谱52是用于判定控制图谱异常的判定图谱之一。即,rom50存储允许图谱52作为判定图谱。rom50对应于判定存储器。

116.允许图谱52是允许作为每个致动器40n的导通状态的导通图谱。更具体地,允许图谱52是其中所述操作允许作为自动变速器的导通图谱。因此,与控制图谱等不同,允许图谱52被预先存储在rom50中。

117.图10是允许图谱52的一个示例。在本实施例中,采用五个允许图谱52。rom50具有分别对应于致动器401至405的地址位。在rom50中,在地址位中写入表示允许图谱52中致动器401至405的导通状态的信号(值)。本实施例以5位控制图谱为例。因此,每个允许图谱52具有5位,这与控制图谱相同。每个允许图谱52包括作为表示导通的信号的1和作为表示不导通的信号的0。因此,每个允许图谱52可以用0和1表示。

118.第一允许图谱52(第一档速(1st speed))是11100。第二允许图谱52(第二档速)是11001。第三允许图谱52(第三档速)是10101。第四允许图谱52(第四档速)是01110。第五允许图谱52(第五档速)是01011。

119.第一比较器40依次比较允许图谱52的每个信号和控制图谱的每个信号。第一比较器40将允许图谱52与控制图谱进行比较,判定允许图谱52与控制图谱是否满足预定的对应关系。第一比较器40对应于比较器。

120.在本实施例中,采用允许图谱52作为判定图谱。因此,本实施例中的预定对应关系表示允许图谱52与控制图谱不同。即,当允许图谱52和控制图谱不同时,第一比较器40判定满足预定对应关系。另一方面,当允许图谱52与控制图谱匹配时,第一比较器40判定不满足预定对应关系。

121.与允许图谱52不同的控制图谱是不被允许的导通图谱。因此,该控制图谱是发生窜改位等的异常导通图谱。另一方面,与允许图谱52匹配的控制图谱是被允许的导通图谱。因此,该控制图谱是不发生窜改位等的正常的导通图谱。

122.因此,当允许图谱52和控制图谱不同时,第一比较器40判定控制图谱异常。当允许图谱52与控制图谱匹配时,第一比较器40判定控制图谱正常。

123.将参考图11描述驱动装置102的操作。当接收到负载驱动信号时,驱动装置102开始图11的流程图所示的操作。此时,假设电源电路70输出表示电源开关500接通的信号。即,每个致动器40n被供给电流。

124.在s10b中,设定允许图谱。时序电路30将存储在rom50中的允许图谱52设定在第二数据寄存器62中。更具体地,第二数据加载器32从rom50加载允许图谱52。然后,第二数据加载器32在第二数据寄存器62中设定被加载的允许图谱52。当允许图谱52在第二数据寄存器62中被设定时,允许图谱52被输出到第一比较器40。

125.当多个允许图谱52被存储在rom50中时,第二数据加载器32将存储在rom50中的允许图谱52依次写入第二数据寄存器62。此外,当写入第二数据寄存器62的允许图谱52被输出到第一比较器40时,第二数据加载器32将下一允许图谱52写入第二数据寄存器62。

126.在s12a中,比较所述控制图谱和允许图谱。第一比较器40将第一数据寄存器61中

设定的控制图谱与第二数据寄存器62中设定的允许图谱52进行比较。当多个允许图谱52被存储在rom50中时,第一比较器40将控制图谱与每个允许图谱52依次进行比较。结果,第一比较器40将控制图谱与所有的允许图谱52进行比较。

127.当控制图谱与允许图谱52中的一个匹配时,第一比较器40进行到s13。即,当即使允许图谱52中的一个与控制图谱匹配时,第一比较器40进行到s13。在这种情况下,控制图谱可以被认为是正常的。另一方面,当控制图谱与所有的允许图谱52不同时,第一比较器40进行到s14。在这种情况下,控制图谱可以被认为是异常的。

128.驱动装置102能够以与驱动装置101类似的方式利用简单的配置判定控制图谱的异常。此外,驱动装置102能够以与驱动装置101类似的方式提高安装自由度。此外,驱动装置102能够以类似于驱动装置101的方式减少用于功能安全性和可靠性的措施。

129.(第三实施例)

130.将参照图12和图13描述根据第三实施例的驱动装置103。驱动装置103具有与驱动装置101不同的比较图谱。在驱动装置103中,相同的附图标记被分配给与驱动装置101相同的配置。在图13的流程图中,对与图5的流程图相同的过程分配相同的步骤编号。

131.驱动装置103将监控器图谱与判定图谱进行比较。因此,监控器图谱可以说是比较图谱。与驱动装置101一样,监控器图谱被存储在监控器寄存器84中。

132.如图12所示,寄存器单元60具有其中设定监控器图谱的第三数据寄存器(3reg)63。然后,时序电路30将存储在监控器寄存器84中的监控器图谱设定在第三数据寄存器63中。

133.将参考图13描述驱动装置103的操作。当接收到负载驱动信号时,驱动装置103开始图13的流程图所示的操作。此时,假设电源电路70输出表示电源开关500接通的信号。即,每个致动器40n被供给电流。

134.在s12c中,开始控制。驱动ic20根据存储在控制寄存器11中的控制图谱选择性地接通或关断驱动开关301至305。结果,驱动ic20选择性地向致动器40n供应电流。

135.在s12d中,监控控制结果。每个电流检测单元监控相应的致动器40n的导通状态。第二比较器83输出表示由每个电流检测单元监控的每个致动器40n的导通状态的监控结果。然后,监控器寄存器84存储作为监控结果的监控器图谱。此外,在时序电路30中,数据加载器从监控器寄存器84加载监控器图谱。然后,数据加载器在第三数据寄存器63中设定被加载的监控器图谱。当监控器图谱在第三数据寄存器63中被设定时,监控器图谱被输出到第一比较器40。

136.在s12e中,比较所述监控器图谱和禁止图谱。第一比较器40将第三数据寄存器63中设定的监控器图谱与第二数据寄存器62中设定的禁止图谱51进行比较。当监控器图谱与所有的禁止图谱51不同时,第一比较器40进行到s13。另一方面,当监控器图谱与禁止图谱51中的一个匹配时,第一比较器40进行到s14。例如,如上所述,当控制图谱为11100并且发生接地故障且监控器图谱变为01100时,监控器图谱匹配第四禁止图谱51。

137.驱动装置103能具有与驱动装置101的效果类似的效果。此外,驱动装置103能由于存储在监控器寄存器84中的监控器图谱的窜改位而判定监控器图谱异常。此外,由于电流检测电阻器81与每个致动器40n之间的电流路径中的接地故障,驱动装置103能够判定监控器图谱的异常。

138.(第四实施例)

139.将参考图14和15描述根据第四实施例的驱动装置104。驱动装置104具有与驱动装置102的比较图谱不同的比较图谱。在驱动装置104中,相同的附图标记分配给与驱动装置102相同的配置。此外,在图15的流程图中,对与图11的流程图的相同的过程分配相同的步骤编号。

140.驱动装置104将监控器图谱与判定图谱进行比较。因此,监控器图谱可以说是比较图谱。监控器图谱以类似于驱动装置101的方式被存储在监控器寄存器84中。

141.如图14所示,寄存器单元60具有其中设定监控器图谱的第三数据寄存器63。然后,时序电路30将存储在监控器寄存器84中的监控器图谱设定在第三数据寄存器63中。

142.将参考图15描述驱动装置104的操作。当接收到负载驱动信号时,驱动装置104开始图15的流程图所示的操作。此时,假设电源电路70输出表示电源开关500接通的信号。即,每个致动器40n被供给电流。请注意,s12f和12g分别类似于s12c和s12d。

143.在s12h中,比较监控器图谱和允许图谱。第一比较器40将第三数据寄存器63中设定的监控器图谱与第二数据寄存器62中设定的允许图谱52进行比较。当监控器图谱与允许图谱52中的一个匹配时,第一比较器40进行到s13。另一方面,当监控器图谱与所有的允许图谱52不同时,第一比较器40进行到s14。

144.驱动装置104能具有与驱动装置102的效果类似的效果。此外,驱动装置104能以与驱动装置103类似的方式判定监控器图谱的异常。

145.(第五实施例)

146.将参考图16描述根据第五实施例的驱动装置105。驱动装置105具有与驱动装置101和驱动装置103不同的比较图谱。在驱动装置105中,相同的附图标记分配给与驱动装置101和驱动装置103相同的配置。

147.驱动装置105比较控制图谱和判定图谱,并且还比较监控器图谱和判定图谱。因此,控制图谱和监控器图谱可以说是比较图谱。驱动装置105采用禁止图谱51作为判定图谱。

148.寄存器单元60具有第一数据寄存器61、第二数据寄存器62和第三数据寄存器63。时序电路30将控制寄存器11中存储的控制图谱设定在第一数据寄存器61中。时序电路30将存储在rom50中的禁止图谱51设定在第二数据寄存器62中。时序电路30将存储在监控器寄存器84中的监控器图谱设定在第三数据寄存器63中。

149.第一比较器40与第一实施例中(s12a)一样比较控制图谱和禁止图谱。当控制图谱与所有的禁止图谱51不同时,第一比较器40进行到s13。另一方面,当控制图谱与禁止图谱51中的一个匹配时,第一比较器40进行到s14。

150.此外,第一比较器40以类似于第三实施例的方式(s12e)比较监控器图谱和禁止图谱。当监控器图谱与所有的禁止图谱51不同时,第一比较器40进行到s13。另一方面,当监控器图谱与禁止图谱51中的一个匹配时,第一比较器40进行到s14。

151.驱动装置105能具有与驱动装置101和103的效果类似的效果。

152.(第六实施例)

153.将参照图17描述根据第六实施例的驱动装置106。驱动装置106具有与驱动装置102和驱动装置104不同的比较图谱。在驱动装置106中,相同的附图标记被分配给与驱动装

置102和驱动装置104相同的配置。

154.驱动装置106比较控制图谱和判定图谱,并且还比较监控器图谱和判定图谱。因此,控制图谱和监控器图谱可以说是比较图谱。驱动装置105采用允许图谱52作为判定图谱。时序电路30和寄存器单元60与驱动装置105的时序电路30和寄存器单元60相似。

155.第一比较器40以第二实施例中的方式(s12b)比较控制图谱和允许图谱。当控制图谱与允许图谱52中的一个匹配时,第一比较器40进行到s13。另一方面,当控制图谱与所有的允许图谱52不同时,第一比较器40进行到s14。

156.此外,第一比较器40以类似于第四实施例的方式(s12h)比较监控器图谱和允许图谱。当监控器图谱与允许图谱52中的一个匹配时,第一比较器40进行到s13。另一方面,当监控器图谱与所有的允许图谱52不同时,第一比较器40进行到s14。

157.驱动装置106能具有与驱动装置102和104的效果类似的效果。

158.尽管已经根据实施例描述了本公开,但是应当理解,本公开不限于这样的实施例或结构。本公开包括落入等同范围内的各种修改和变化。此外,虽然各种要素以各种组合和配置示出,这些组合和配置是示例性的,但是包括更多、更少或仅单个要素的其他组合和配置也位于本公开的精神和范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1