一种支持异构多处理器架构的程序配置方法与流程

1.本发明涉及一种支持异构多处理器架构的程序配置方法,属于星载计算机技术领域。

背景技术:

2.我国首次火星探测通过一次飞行任务实现了火星“绕、落、巡”的目标,着陆巡视器“祝融号”火星车突破了火星表面巡视、长期自主管理等关键技术。火星车gnc分系统的导航控制单元作为系统的数据处理核心,采用了cpu+dsp的异构多处理器高性能计算架构。因此,为成功完成环境感知、自主规划、位姿确定以及运动控制等功能,系统需具有支持异构多处理器程序高效、可靠运行的管理机制,使火星车能够在复杂未知的火星表面环境中实现长距离安全行驶。

技术实现要素:

3.本发明要解决的技术问题是:克服现有技术的不足,提供了一种支持异构多处理器架构的程序配置方法,通过采用异构存储备份、在轨配置程序加载策略、多处理器程序统一管理等措施,保障了火星车导航控制单元的高效可靠运行。

4.本发明目的通过以下技术方案予以实现:

5.一种支持异构多处理器架构的程序配置方法,采用了cpu+dsp的异构多处理器架构,包括如下步骤:

6.在nor-flash存储器中,存储两份cpu的程序,存储两份dsp的程序,其中,cpu的两份程序内容一致,存储空间独立,互为同构备份,dsp的两份程序内容一致,存储空间独立,互为同构备份;

7.在eeprom存储器中,存储一份cpu的程序,存储一份dsp的程序;eeprom中存储的程序与nor-flash中的存储程序功能一致,实现程序代码的异构容错;

8.程序管理的配置参数存储在eeprom中,采取按位三模冗余存储结构;

9.配置参数中设置nor-flash和eeprom中的cpu程序内容一致性标识、nor-flash和eeprom中的dsp程序内容一致性标识、cpu程序加载策略标识、dsp程序加载策略标识;

10.cpu作为主控处理器,dsp作为协处理器,由cpu进行程序的统一管理。cpu根据配置参数要求对cpu、dsp的程序进行加载,启动多处理器运行;

11.当配置参数在轨修改后,cpu对cpu和dsp进行复位控制,停止原程序运行,并按新的配置参数要求进行程序加载,重新启动多处理器运行,完成程序的在轨更新运行。

12.优选的,nor-flash和eeprom中的cpu程序内容一致性标识取值为0xeb90146f或0x00000000;取值0xeb90146f表示nor-flash、eeprom中的cpu程序内容一致,属于异构存储、同构备份;取值0x00000000表示nor-flash、eeprom中的cpu程序内容不一致,属于异构存储、异构备份;

13.nor-flash和eeprom中的dsp程序内容一致性标识取值为0xeb90146f或

0x00000000,取值0xeb90146f表示nor-flash、eeprom中的dsp程序内容一致,属于异构存储、同构备份;取值0x00000000表示nor-flash、eeprom中的dsp程序内容不一致,属于异构存储、异构备份;

14.cpu程序加载策略标识取值为0xeb90146f或0x00000000,取值0xeb90146f表示加载nor-flash中的cpu程序;取值0x00000000表示加载eeprom中的cpu程序;

15.dsp程序加载策略标识取值为0xeb90146f或0x00000000;取值0xeb90146f表示加载nor-flash中的dsp程序;取值0x00000000表示加载eeprom中的dsp程序。

16.优选的,程序管理的配置参数还包括:1)nor-flash中第一份cpu程序的起始存储地址;2)nor-flash中第二份cpu程序的起始存储地址;3)nor-flash中cpu程序的字节个数;4)nor-flash中第一份dsp程序的起始存储地址;5)nor-flash中第二份dsp程序的起始存储地址;6)nor-flash中dsp程序的字节个数;7)eeprom中cpu程序的起始存储地址;8)eeprom中cpu程序的字节个数;9)eeprom中dsp程序的起始存储地址;10)eeprom中dsp程序的字节个数。

17.优选的,程序管理的配置参数采用在轨修改的方式进修改。

18.优选的,程序管理的配置参数存储在eeprom中,与eeprom中存储的程序保持空间隔离。

19.优选的,

20.cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0xeb90146f,配置参数“cpu程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序;若加载过程中又有数据发生错误,则从eeprom存储的cpu程序地址处继续加载程序,直至全部程序加载完毕;

21.cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0xeb90146f,配置参数“cpu程序加载策略标识”取值为0x00000000,则从eeprom存储的cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第1份cpu程序地址处继续加载程序;若加载过程中又有数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序,直至全部程序加载完毕;

22.cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0x00000000,配置参数“cpu程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序,直至全部程序加载完毕;

23.cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0x00000000,配置参数“cpu程序加载策略标识”取值为0x00000000,则从eeprom存储的cpu程序地址处开始加载程序,直至全部程序加载完毕;

24.cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0xeb90146f,配置参数“dsp程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序;若加载过程中又有数据发生错误,则从eeprom存储的dsp程序地址处继续加载程序,直至全部程序加载完毕;

25.cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0xeb90146f,配置参数“dsp程序加载策略标识”取值为0x00000000,则从eeprom存储的dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第1份dsp程序地址处继续加载程序;若加载过程中又有数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序,直至全部程序加载完毕;

26.cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0x00000000,配置参数“dsp程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序,直至全部程序加载完毕;

27.cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0x00000000,配置参数“dsp程序加载策略标识”取值为0x00000000,则从eeprom存储的dsp程序地址处开始加载程序,直至全部程序加载完毕。

28.一种异构多处理器架构,采用上述的程序配置方法进行程序配置。

29.本发明相比于现有技术具有如下有益效果:

30.(1)本发明支持系统对nor-flash、eeprom两类存储器的访问,实现程序存储的异构冗余备份,提高程序存储可靠性;

31.(2)本发明支持程序内容进行同构和异构两种备份方式,提供程序功能可靠性;

32.(3)本发明支持程序管理策略进行在轨配置,提高系统运行灵活性;

33.(4)本发明程序配置参数采用按位三模冗余的方式,支持比特级容错;

34.(5)本发明程序存储位置、大小可动态改变,部分存储空间失效后,可将程序存储在剩余有效空间,提供系统可维护性;

35.(6)本发明支持对多处理器程序的统一管理,提高异构多处理器系统的易用性;

36.(7)本发明在统一的配置框架下,不同的处理器可配置不同的管理策略,适应不同关键等级程序的运行。

附图说明

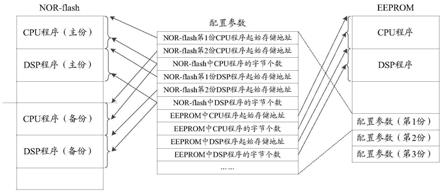

37.图1为本发明方法的配置示意图。

具体实施方式

38.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步详细描述。

39.一种支持异构多处理器架构的程序配置方法,即支持异构多处理器架构的程序管理方法,如图1所示,具体实施方式如下:

40.1、系统采用nor-flash、eeprom两种存储器来存储cpu、dsp的程序,实现程序存储的异构冗余备份;

41.2、在nor-flash存储器中,存储两份cpu的程序,存储两份dsp的程序。cpu的两份程序内容一致,存储空间独立,互为同构备份;dsp的两份程序也内容一致,存储空间独立,互为同构备份;

42.3、在eeprom存储器中,存储一份cpu的程序,存储一份dsp的程序。eeprom中的程序

与nor-flash中的程序功能一致,实现程序代码的异构容错;

43.4、程序管理的配置参数存储在eeprom中,采取三模冗余存储结构,与eeprom中的程序保持空间隔离;

44.5、程序管理的配置参数包括:1)nor-flash中第一份cpu程序的起始存储地址;2)nor-flash中第二份cpu程序的起始存储地址;3)nor-flash中cpu程序的字节个数;4)nor-flash中第一份dsp程序的起始存储地址;5)nor-flash中第二份dsp程序的起始存储地址;6)nor-flash中dsp程序的字节个数;7)eeprom中cpu程序的起始存储地址;8)eeprom中cpu程序的字节个数;9)eeprom中dsp程序的起始存储地址;10)eeprom中dsp程序的字节个数;11)nor-flash、eeprom中的cpu程序内容一致性标识;12)nor-flash、eeprom中的dsp程序内容一致性标识;13)cpu程序加载策略标识;14)dsp程序加载策略标识;

45.6、配置参数中的“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0xeb90146f或0x00000000。取值0xeb90146f表示nor-flash、eeprom中的cpu程序内容一致,属于异构存储、同构备份;取值0x00000000表示nor-flash、eeprom中的cpu程序内容不一致,属于异构存储、异构备份;

46.7、配置参数中的“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0xeb90146f或0x00000000。取值0xeb90146f表示nor-flash、eeprom中的dsp程序内容一致,属于异构存储、同构备份;取值0x00000000表示nor-flash、eeprom中的dsp程序内容不一致,属于异构存储、异构备份;

47.8、配置参数中的“cpu程序加载策略标识”取值为0xeb90146f或0x00000000。取值0xeb90146f表示加载nor-flash中的cpu程序;取值0x00000000表示加载eeprom中的cpu程序;

48.9、配置参数中的“dsp程序加载策略标识”取值为0xeb90146f或0x00000000。取值0xeb90146f表示加载nor-flash中的dsp程序;取值0x00000000表示加载eeprom中的dsp程序;

49.10、配置参数可进行在轨修改,支持对程序的高效灵活管理;

50.11、在cpu+dsp的异构多处理器高性能计算架构中,cpu作为主控处理器,dsp作为协处理器,由cpu进行程序的统一管理。cpu根据配置参数要求负责对cpu、dsp的程序进行加载,启动多处理器运行;

51.12、cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0xeb90146f,配置参数“cpu程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序;若加载过程中又有数据发生错误,则从eeprom存储的cpu程序地址处继续加载程序,直至全部程序加载完毕;

52.13、cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0xeb90146f,配置参数“cpu程序加载策略标识”取值为0x00000000,则从eeprom存储的cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第1份cpu程序地址处继续加载程序;若加载过程中又有数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序,直至全部程序加载完毕;

53.14、cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程

序内容一致性标识”取值为0x00000000,配置参数“cpu程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份cpu程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份cpu程序地址处继续加载程序,直至全部程序加载完毕;

54.15、cpu根据配置参数加载cpu程序时,若配置参数“nor-flash、eeprom中的cpu程序内容一致性标识”取值为0x00000000,配置参数“cpu程序加载策略标识”取值为0x00000000,则从eeprom存储的cpu程序地址处开始加载程序,直至全部程序加载完毕;

55.16、cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0xeb90146f,配置参数“dsp程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序;若加载过程中又有数据发生错误,则从eeprom存储的dsp程序地址处继续加载程序,直至全部程序加载完毕;

56.17、cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0xeb90146f,配置参数“dsp程序加载策略标识”取值为0x00000000,则从eeprom存储的dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第1份dsp程序地址处继续加载程序;若加载过程中又有数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序,直至全部程序加载完毕;

57.18、cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0x00000000,配置参数“dsp程序加载策略标识”取值为0xeb90146f,则从nor-flash存储的第1份dsp程序地址处开始加载程序;若加载过程中数据发生错误,则从nor-flash存储的第2份dsp程序地址处继续加载程序,直至全部程序加载完毕;

58.19、cpu根据配置参数加载dsp程序时,若配置参数“nor-flash、eeprom中的dsp程序内容一致性标识”取值为0x00000000,配置参数“dsp程序加载策略标识”取值为0x00000000,则从eeprom存储的dsp程序地址处开始加载程序,直至全部程序加载完毕;

59.20、当配置参数发生在轨修改后,cpu可对自己和dsp处理器进行复位控制,停止原程序运行,并按新的配置参数要求进行程序加载,重新启动多处理器运行,实现程序的在轨更新运行。

60.综上,采用异构多处理器高性能计算架构是提升航天器信息处理系统性能,满足航天器信息化、自主化、智能化需求,尤其是深空探测器在轨信息融合与处理能力的有效技术途径。因此,为实现航天器的在轨可靠运行,系统都需具有支持异构多处理器程序高效、可靠运行的管理机制。本发明提出的一种支持异构多处理器架构的高效程序管理方法,采用异构存储备份、在轨配置程序加载策略、多处理器程序统一管理等措施,能很好适合采用异构多处理器高性能计算架构的航天器的高可靠运行要求,具有很广的应用前景。

61.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

62.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案

的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1