辅助可编程逻辑单元调试的方法、设备及系统与流程

1.本技术涉及到一种逻辑单元调试的技术,尤其涉及一种辅助可编程逻辑单元调试的方法。本技术还涉及一种辅助可编程逻辑单元调试的装置、设备及系统。本技术还涉及一种通讯协议。

背景技术:

2.可编程逻辑单元(cpld,complex programming logic device)是一种逻辑功能可以按照用户对器件的编程来确定的通用集成电路。cpld内部不含有ram(随机存取存储器),因此无法实现在线仿真的功能,对于一些比较大型的程序来说,目前对于接口的调试,只能使用外挂逻辑分析仪的方式对cpld输出接口进行调试,但是对于cpld内部的未输出到接口上的逻辑状态,外挂的逻辑分析仪是无法进行监测的,也就没办法实现对cpld的全功能逻辑的调试。

3.目前解决cpld内部逻辑的调试问题的方法多为外接指示灯,通过将cpld内部逻辑引出到指示灯上,观察指示灯的状态来调试cpld内部逻辑。但是这对开发设计要求很高,首先cpld需要有足够的管脚能够连接足够多的指示灯,其次cpld内部的逻辑显示速率不能过高,因为过高的显示速率会使指示灯一闪而过,调试人员来不及及时的通过指示灯判断逻辑状态。因此,通过这种调试方法对cpld进行调试效率低下。

技术实现要素:

4.为了解决当前技术方案中调试cpld效率低下的问题,本技术提出一种辅助可编程逻辑单元调试的方法以及一种辅助可编程逻辑单元调试的装置。本技术还提出一种一种辅助可编程逻辑单元调试的设备、系统以及一种通讯协议。

5.本技术提供一种辅助可编程逻辑单元调试的方法,包括:

6.从可编程逻辑单元的一个管脚上接收调试信息;

7.将所述调试信息进行解析获得所述可编程器件的调试解析数据;

8.将所述调试解析数据发送到显示器件进行显示,和发送到输出单元以输出所述调试解析数据。

9.可选的,所述调试信息包括:第一调试信息;

10.所述第一调试信息是将所述辅助可编程逻辑单元的接口的逻辑电平值,按照时序先后填充到所述辅助可编程逻辑单元的通讯协议生成的。

11.可选的,所述调试信息包括:第二调试信息;

12.所述第二调试信息是将所述辅助可编程逻辑单元的寄存器值赋值到所述辅助可编程逻辑单元的通讯协议生成的。

13.本技术提供一种通讯协议,用于所述可编程逻辑单元,包括:起始段、时钟校准段、数据段和结尾段;

14.所述起始段包括:分别为30ns的高电平和低电平,所述高电平和低电平的时间误

差最大为5ns;

15.所述时钟校准段包括:分别为20ns的高电平和低电平,所述高电平和低电平的时间误差最大为15ns;

16.所述数据段包括8bit的传输信息,所述传输信息在所述时钟校准段的时间内,通过对所述辅助可编程逻辑单元进行信息采样获得;

17.所述结尾段没有时间限制。

18.可选的,所述数据段的传输信息,高4位显示到高位7段数码管,低4位显示到低位7段数码管。

19.本技术还提供一种辅助可编程逻辑单元调试的装置,包括:

20.单数据线单元,用于从可编程逻辑单元的一个管脚上接收调试信息;

21.逻辑译码单元,用于将所述调试信息进行解析获得所述可编程器件的调试解析数据;

22.显示单元,用于接收所述调试解析数据,并显示;

23.输出单元,用于接收所述调试解析数据,并输出。

24.可选的,所述调试信息包括:第一调试信息;

25.所述第一调试信息是将所述辅助可编程逻辑单元的接口的逻辑电平值,按照时序先后填充到所述辅助可编程逻辑单元的通讯协议生成的。

26.可选的,所述调试信息包括:第二调试信息;

27.所述第二调试信息是将所述辅助可编程逻辑单元的寄存器值赋值到所述辅助可编程逻辑单元的通讯协议生成的。

28.本技术还提供一种辅助可编程逻辑单元调试的设备,包括:所述通讯协议和所述可编程逻辑单元调试的装置;

29.所述可编程逻辑单元调试的装置在执行所述可编程逻辑单元调试的方法时,按照所述通讯协议进行数据传输。

30.本技术还提供一种辅助可编程逻辑单元调试的系统,包括:所述可编程逻辑单元调试的方法,和所述可编程逻辑单元调试的装置。

31.本技术相较于现有技术的优点是:

32.本技术提供一种辅助可编程逻辑单元调试的方法,包括:从可编程逻辑单元的一个管脚上接收调试信息;将所述调试信息进行解析获得所述可编程器件的调试解析数据;将所述调试解析数据发送到显示器件进行显示,和发送到输出单元以输出所述调试解析数据。通过所述可编程逻辑单元的一个管脚获取所述可编程逻辑单元的内部调试数据进行直管的显示,为开发人员准确及时的提供可编程单元的内部运行情况,增加调试效率。

附图说明

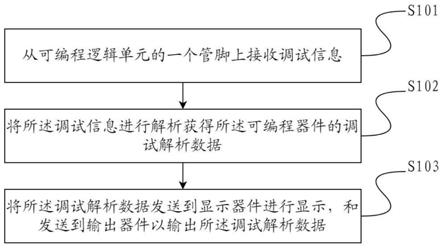

33.图1是本技术中辅助可编程逻辑单元调试的流程图。

34.图2是本技术中通讯协议的示意图。

35.图3是本技术辅助可编程逻辑单元调试的装置示意图。

具体实施方式

36.以下内容均是为了详细说明本技术要保护的技术方案所提供的具体实施过程的示例,但是本技术还可以采用不同于此的描述的其他方式实施,本领域技术人员可以在本技术构思的指引下,采用不同的技术手段实现本技术,因此本技术不受下面具体实施例的限制。

37.本技术提供一种辅助可编程逻辑单元调试的方法,包括:从可编程逻辑单元的一个管脚上接收调试信息;将所述调试信息进行解析获得所述可编程器件的调试解析数据;将所述调试解析数据发送到显示器件进行显示,和发送到输出单元以输出所述调试解析数据。通过所述可编程逻辑单元的一个管脚获取所述可编程逻辑单元的内部调试数据进行直管的显示,为开发人员准确及时的提供可编程单元的内部运行情况,增加调试效率。

38.图1是本技术中辅助可编程逻辑单元调试的流程图。

39.请参照图1所示,s101从可编程逻辑单元的一个管脚上接收调试信息。

40.所述调试信息是指需要被监测的cpld信号,所述调试信息通过cpld的内部逻辑引出到信号线上,然后通过短接所述信号线和sig信号线获取该调试信息。优选的,本技术通过单数据线连接到所述cpld的一个管脚上获取所述调试信息。

41.请参照图1所示,s102将所述调试信息进行解析获得所述可编程器件的调试解析数据。

42.在cpld中,其内部的逻辑是通过电平高低进行逻辑运算的,即所述单数据线连接到所述cpld管脚上后,获取的数据是电平值,以及所述电平存在的时间段。

43.本技术需要通过一个传输协议对由电平信号表示的调试信息进行传输,包括:判断高低电平以及所述高低电平的存在时间。具体的,就是识别电平值和电平时间。

44.一方面,需要判断一个数据从哪里开始采集,本技术通过预设一个电平的存在时间长度的预设阈值,并根据检查到的数据和预设阈值进行比较获得数据采集的开端。

45.另一方面,需要判断采集数据的时间,即采样时间。本技术通过预设一个时间段长度,作为采样时间。

46.以上,所述时间长短的控制是通过电平值进行的。

47.在收到所述调试信息后,该调试信息是按照一个通讯协议传输过来的,因此需要对所述调试信息进行解码,获得调试解析数据。

48.本技术所述调试信息包括:第一调试信息和第二调试信息。所述第一调试信息是对所述cpld接口调试的信息,包括:将所述辅助可编程逻辑单元的接口的逻辑电平值,按照时序先后填充到所述辅助可编程逻辑单元的通讯协议生成。所述第二调试信息对寄存器调试的调试信息,包括:将所述辅助可编程逻辑单元的寄存器值赋值到所述辅助可编程逻辑单元的通讯协议生成的。

49.请参照图1所示,s103将所述调试解析数据发送到显示器件进行显示,和发送到输出单元以输出所述调试解析数据。

50.具体的,将所述调试解析数据发送到显示器显示,可以通过数码管进行,根据所述调试解析数据让数码管进行对应的变化显示。具体的,采样数据的高四位显示到高位七段数码管,采样数据的低四位显示到低位七段数码管。

51.另外,该调试解析数据通过输出单元进行信息输出。

52.本技术提供一种通讯协议,用于对调试信息的传输,包括:起始段201、时钟校准段202、数据段203和结尾段204。

53.图2是本技术中通讯协议的示意图。

54.清风参照图2所示,所述起始段201包括:分别为30ns的高电平和低电平,所述高电平和低电平的时间误差最大为5ns;所述时钟校准段202包括:分别为20ns的高电平和低电平,所述高电平和低电平的时间误差最大为15ns;所述数据段203包括8bit的传输信息,所述传输信息在所述时钟校准段的时间内,通过对所述辅助可编程逻辑单元进行信息采样获得;所述结尾段204没有时间限制。

55.具体的,所述起始段201用于判断是否启动数据接收功能,当检测到连续且满足时间要求的高低电平后启动数据接收功能,之后进入时钟校准段。

56.所述时钟校准段202,在此时序段内检测高低电平的时间,并以此时间为数据段数据的采样时间。

57.所述数据段203能给传输8bit的数据,所述数据是在时钟校准段内测得的时间对数据进行采样。

58.所述结尾段204,当出现高电平到低电平的跳转则表示数据传输的结束。

59.本技术还提供一种辅助可编程逻辑单元调试的装置,包括:单数据线单元301,逻辑译码单元302,显示单元303和输出单元304。

60.图3是本技术辅助可编程逻辑单元调试的装置示意图。

61.请参照图3所示,单数据线单元301,用于从可编程逻辑单元的一个管脚上接收调试信息。

62.所述调试信息是指需要被监测的cpld信号,所述调试信息通过cpld的内部逻辑引出到信号线上,然后通过短接所述信号线和sig信号线获取该调试信息。优选的,本技术通过单数据线连接到所述cpld的一个管脚上获取所述调试信息。

63.所述单数据线单元除数据线线外,还包括3.3v电源线、电源地线。具体的,所述数据线单元采用标准的三针2.54mm插座,所述数据线通过该插座连接逻辑译码单元。

64.请参照图3所示,逻辑译码单元302,用于将所述调试信息进行解析获得所述可编程器件的调试解析数据。

65.在cpld中,其内部的逻辑是通过电平高低进行逻辑运算的,即所述单数据线连接到所述cpld管脚上后,获取的数据是电平值,以及所述电平存在的时间段。优选的,所述的逻辑译码单元采用altera公司生产的ep3c5作为控制器。

66.本技术需要通过一个传输协议对由电平信号表示的调试信息进行传输,包括:判断高低电平以及所述高低电平的存在时间。具体的,就是识别电平值和电平时间。

67.一方面,需要判断一个数据从哪里开始采集,本技术通过预设一个电平的存在时间长度的预设阈值,并根据检查到的数据和预设阈值进行比较获得数据采集的开端。

68.另一方面,需要判断采集数据的时间,即采样时间。本技术通过预设一个时间段长度,作为采样时间。

69.以上,所述时间长短的控制是通过电平值进行的。

70.在收到所述调试信息后,该调试信息是按照一个通讯协议传输过来的,因此需要对所述调试信息进行解码,获得调试解析数据。

71.本技术所述调试信息包括:第一调试信息和第二调试信息。所述第一调试信息是对所述cpld接口调试的信息,包括:将所述辅助可编程逻辑单元的接口的逻辑电平值,按照时序先后填充到所述辅助可编程逻辑单元的通讯协议生成。所述第二调试信息对寄存器调试的调试信息,包括:将所述辅助可编程逻辑单元的寄存器值赋值到所述辅助可编程逻辑单元的通讯协议生成的。

72.请参照图3所示,显示单元303,用于接收所述调试解析数据,并显示。

73.具体的,将所述调试解析数据发送到显示器显示,可以通过数码管进行,根据所述调试解析数据让数码管进行对应的变化显示。具体的,采样数据的高四位显示到高位七段数码管,采样数据的低四位显示到低位七段数码管。优选的,本技术所述的显示单元使用两位七段数码管实现,通过使用天微公司生产的tm1616对数码管进行驱动。

74.请参照图3所示,输出单元,用于接收所述调试解析数据,并输出。

75.调试解析数据通过输出单元进行信息输出。优选的,所述的数据通讯单元采用adi公司的rs-422电平转换芯片ltm2881,这是一款电流隔离型全双工rs485/rs422μmodule收发器。

76.一个具体的例子如下:

77.ep3c5通过控制数码管驱动芯片tm1616对译码信息进行显示,ep3c5与tm1616之间连接有三根控制线组成的数据线,stb(片选)线、clk(时钟)线和din(数据)线,tm1616通过seg1-7(段输出)和grid0-1(两位输出)来对两位七段数码管进行驱动。

78.本技术还提供一种辅助可编程逻辑单元调试的设备,包括:上述实施例中的通讯协议和所述可编程逻辑单元调试的装置;

79.所述可编程逻辑单元调试的装置在执上述可编程逻辑单元调试的方法时,按照所述通讯协议进行数据传输。

80.本技术还提供一种辅助可编程逻辑单元调试的系统,包括:所述可编程逻辑单元调试的方法,和所述可编程逻辑单元调试的装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1