芯片的失效点定位方法与流程

1.本发明涉及半导体技术领域,具体地,涉及芯片的失效点定位方法。

背景技术:

2.nand闪存是一种比硬盘驱动器更好的存储设备,随着人们追求功耗低、质量轻和性能佳的非易失存储产品,在电子产品中得到了广泛的应用。目前,平面结构的nand闪存已近实际扩展的极限,为了进一步的提高存储容量,降低每比特的存储成本,提出了3d结构的3d nand存储器。

3.在3d nand产品研发过程和产品制造阶段会出现许多芯片边缘失效的问题,芯片边缘的失效模式一般是有开路和高阻,对于完全开路的失效,,而3d nand存储器包括在其深度方向上堆叠的大量栅极结构,失效点的位置可能存在于该大量栅极结构中的任意栅极结构中,对于存在于存储器芯片内部的失效点在存储器芯片的深度位置的定位检测困难。

技术实现要素:

4.本发明提供一种芯片的失效点定位方法,所述芯片包括堆叠的多个金属层,包括:

5.去除所述芯片的边缘结构,以获得所述芯片的截面;

6.在所述芯片中所述多个金属层中的至少一层上提供电流;

7.在电子显微镜下获得所述芯片的截面在电流驱动下的截面图像;其中,

8.所述截面图像的明暗区交界处即是失效点的位置。

9.可选地,在去除所述芯片的边缘结构的步骤之前,还包括:

10.在所述芯片的上表面设置保护基底层。

11.可选地,所述保护基底层为玻璃层。

12.可选地,在所述在电子显微镜下获得所述芯片的截面在电流驱动下的截面图像的步骤中,还通过固定台固定所述芯片,并使所述芯片的截面朝向纳米探针台。

13.可选地,所述在所述芯片中所述多个金属层中的至少一层上提供电流步骤包括:

14.通过纳米探针,将所述多个金属层中的对应输入端和输出端的金属层分别连接至电流通道和接地通道。

15.可选地,所述去除所述芯片的边缘结构的步骤包括:

16.截面制样至所述芯片的顶层金属侧边暴露,所述芯片的截面至少暴露所述芯片的边缘位置的顶层金属。

17.可选地,所述在电子显微镜下获得所述芯片的截面在电流驱动下的截面图像的步骤包括:

18.调整扫描电子显微镜的加速电压和电子束流,获得所述芯片的截面上的截面图像,所述截面图像的明暗区交界处位置即是所述失效点的位置,其中,

19.所述截面图像的明区的至少部分未直接暴露在所述芯片的截面上。

20.可选地,在去除所述芯片的边缘结构的步骤之前,还包括:

21.进行去层,以剥离所述芯片的上表面结构,直至暴露所述芯片的顶层金属;

22.通过所述顶层金属向所述芯片的提供电流;

23.在电子显微镜下获得所述芯片在电流驱动下的上表面的平面图像;

24.根据所述平面图像的明暗区交界处位置获得所述失效点在所述芯片的俯视面上的平面位置。

25.可选地,所述在所述芯片中所述多个金属层中的至少一层上提供电流的步骤还包括:

26.根据所述失效点在所述芯片的俯视面上的平面位置,选择靠近所述失效点的顶层金属接通电流通道和接地通道。

27.可选地,所述截面图像的明暗区交界处位置包括所述失效点在所述芯片俯视面上的平面位置和所述失效点在所述芯片的深度方向的深度位置。

28.本发明提供的芯片的失效点定位方法去除芯片的边缘结构,以在芯片的截面上暴露出多个金属层的部分,通过暴露的金属层向芯片提供电流,并通过ebac(e-beam absorbance current,电子束吸收电流)技术获得芯片的截面在电流驱动下的截面图像,根据该截面图像的明暗区交界处位置直接定位获得失效点的深度位置,无需多次去层芯片,逐步暴露不同深度的底层进行多次测试,有效提升了失效点的深度位置的分析测试速度,为芯片研发提供了便利。

附图说明

29.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

30.图1示出了根据一实施例的芯片的失效点测试示意图;

31.图2示出了根据一实施例的芯片的失效点定位方法的流程图;

32.图3示出了根据一实施例的芯片的失效点定位方法的截面位置示意图;

33.图4示出了根据一实施例的芯片的边缘结构的截面示意图;

34.图5示出了根据一实施例的芯片的固定装置的结构示意图;

35.图6a和图6b示出了根据一实施例的芯片的失效点定位方法的样品截面的测试状态示意图。

具体实施方式

36.以下将参照附图更详细地描述本发明的各种实施例。在各个附图中,相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。

37.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

38.图1示出了根据一实施例的芯片的失效点测试示意图。

39.如图1所示,根据sem vc(scanning electron microscope voltage contrast,扫描电子显微镜电压衬度)图像明暗差异来确认大致失效地址(失效点位置),然后进行去层(delayer)分析逐步找到具体失效地址,其测试内容主要包括:

40.通过连接电流通道cur和接地通道gnd的纳米探针p向芯片100(例如3d存储器芯片)的边缘回路提供电流,在扫描电子显微镜(scanning electron microscope,sem)下,顶

层金属呈现出明暗差异,根据差异位置可初步确认失效点位于明暗区交界处的第一顶层金属101至第二顶层金属102之间的电回路上。

41.在sem vc无法直接找到失效地址的情况下(即还不能确认失效点在芯片100中的深度位置),使用纳米探针台(nanoprober)通过二分法(dichotomy)逐段排查,直至找到失效地址,准确定位第一顶层金属101和第二顶层金属102,再进行去层和测试定位,获得失效点的芯片100中的深度位置。

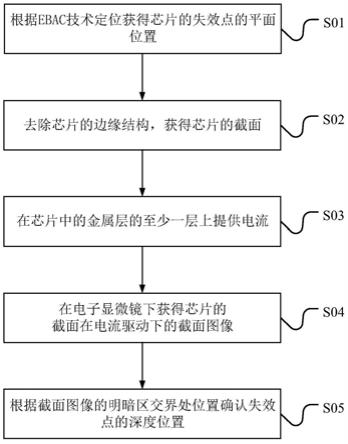

42.图2示出了根据一实施例的芯片的失效点定位方法的流程图。

43.参照图2,该实施例的芯片的失效点定位方法包括:

44.步骤s01:根据ebac技术定位获得芯片的失效点的平面位置。

45.即对芯片的上表面进行去层处理,暴露顶层金属,将去层后的芯片置于扫描电子显微镜中,通过纳米探针向芯片的顶层金属通入电流,通过扫描电子显微镜获得芯片在电流驱动下的上表面的平面图像,根据该平面图像的明暗区交界处的第一顶层金属101和第二顶层金属102的位置确认失效点位于第一顶层金属101至第二顶层金属102之间的电回路(芯片堆叠有多个金属层,电回路对应该多个金属层的连接回路)中,以获得失效点的平面位置。

46.其中,ebac(e-beam absorbance current,电子束吸收电流)技术包括:暴露芯片电回路,向芯片电回路提供电流,如果芯片电回路中存在开路(或高阻态)点,则开路点的上游电回路中根据电流有电荷注入,开路点的下游电回路为接地状态,无电荷,有电荷注入的电回路在电子显微镜(scanning electron microscope,sem,扫描电子显微镜,但本发明的实现对电子显微镜的类型不作特别限定)的电子束作用下产生反馈,电子显微镜对该部分的成像为高亮图像,对其它无电荷注入的区域的成像为暗态图像,以根据电子显微镜获得的图像的明暗状态和明暗区交界处确认对应的电回路是否开路,以及开路点的位置。

47.步骤s02:去除芯片的边缘结构,获得芯片的截面。

48.即通过截面制样技术截取去除芯片的边缘结构,直至顶层金属的侧边缘暴露。其中,芯片的顶层金属的尺寸一般稍大于底层金属的尺寸,暴露顶层金属的侧边缘时停止截面制样,对应底层金属还由少量绝缘材料覆盖,未直接暴露在样品截面上,可保障底层金属的电回路(原有连接状态)的完整性,避免截面制样对失效点所处的电回路的损伤,保障分析测试的可靠性。

49.步骤s03:在芯片中的金属层的至少一层上提供电流。

50.在步骤s03中,向芯片提供的电流通过纳米探针台的纳米探针提供,纳米探针与电流通道和接地通道分别连接,且纳米探针接至样品截面暴露的顶层金属(对应芯片的金属层的连接回路中的输入端和输出端),通过顶层金属向失效点所述的电回路提供电流。

51.在本实施例中,芯片的截面仅暴露顶层金属,通过顶层金属向芯片提供电流,在可选实施例中,芯片的截面还可暴露其它的底层金属,还可通过底层金属向芯片提供电流。

52.采用ebac(e-beam absorbance current,电子束吸收电流)技术向暴露的电回路提供电流,放大失效点信号,提高后续接通电流的部分和未接通电流的部分在电子显微镜下的明暗对比度,提高定位效率。

53.步骤s04:在电子显微镜下获得芯片的截面在电流驱动下的截面图像。

54.步骤s05:根据截面图像的明暗区交界处位置确认失效点的深度位置。

55.在步骤s05中,截面图像的明区对应接通了电流的金属层,暗区对应未接通电流的接地的金属层,其交界处位置即为金属层的连接开路位置,对应失效点的位置。

56.在本实施例中,先对失效点在芯片的平面位置进行定位,优先判断获得失效点的平面位置,便于根据失效点的平面位置,在步骤s03中直接选择靠近失效点的平面位置的第一顶层金属101和第二顶层金属102接通电流通道和接地通道,降低步骤s03对供电电流的需求,降低能耗,且便于直接定位步骤s03的扫描位置,无需对芯片100的a-a截面整体进行扫描,进一步降低分析作业的整体功耗。且直接定位的速度快。

57.在可选实施例中,除去步骤s01的平面定位步骤,对a-a截面的全部电回路提供电流(即向芯片的截面暴露的多个顶层金属的两端位置的顶层金属提供电流(参照图1的电流供应方式),以提供芯片的截面对应电回路的整体驱动),并通过电子显微镜扫描获得a-a截面在电流驱动下的全都部分的截面图像,根据整体的截面图像确认失效点在芯片100中的平面位置和深度位置。

58.在本实施例中,芯片以3d存储器芯片为例,但本发明的芯片的失效点定位方法可适用于多种具有堆叠金属层设计的芯片的内部开路失效点的分析测试,对于具体的可测芯片再此不作详述。

59.图3示出了根据一实施例的芯片的失效点定位方法的截面位置示意图。

60.参照图3,一实施例的芯片的失效点定位方法首先根据ebac技术向芯片100的边缘电路提供电流,根据明暗差异的图像确认第一顶层金属101和第二顶层金属102的位置,然后沿a-a线截取芯片100,去除芯片100的部分边缘结构,暴露最外侧电路的电回路(边缘位置的失效点所处的电回路)。

61.图4示出了根据一实施例的芯片的边缘结构的截面示意图。

62.参照图4,失效点所处的电回路20在芯片100的深度方向上层叠设置,且位于芯片100的衬底110上的结构层120,结构层120的其它部分为绝缘材料,第一顶层金属101和第二顶层金属102暴露在结构层120的顶层。

63.在a-a截面上(样品截面),至少直接暴露第一顶层金属101和第二顶层金属102,以便纳米探针p与第一顶层金属101和第二顶层金属102直接沟通,使沟通电流通道cur与第一顶层金属101,沟通接地通道gnd与第二顶层金属102,向失效点所处的电回路20(由堆叠并连接的多个金属层构成)提供电流。

64.在本实施例中,还在芯片100的顶层覆盖保护基底层40,以保护芯片100的顶层表面结构,降低截取切片操作对芯片100的表面结构的损伤,保障后续检测的可靠性。其中保护基底层40例如为玻璃层或树脂层等绝缘材料。

65.图5示出了根据一实施例的芯片的固定装置的结构示意图。

66.如图5所示,去除边缘结构后的芯片100还通过固定台200固定,使a-a截面朝向纳米探针台,与纳米探针p对应。

67.图6a和图6b示出了根据一实施例的芯片的失效点定位方法的样品截面的测试状态示意图。

68.参照图6a和图6b,在本实施例中,a-a截面上仅直接暴露第一顶层金属101和第二顶层金属102,在其它底层金属由结构层120的绝缘材料覆盖,未直接暴露,可保障失效点所处的电回路的结构完整性,保障检测分析的可靠性。

69.如图6a所示,在扫描电子显微镜的低压工作状态时,仅能观察到第一顶层金属101为亮态,第二顶层金属102和其它由绝缘材料覆盖的电回路为暗态。

70.通过调整扫描电子显微镜的加速电压、电子束流等参数,如图6b所示,提高扫描电子显微镜的输出功率,可透过绝缘材料观察到a-a截面上的明暗村度的金属绕线图像,根据亮态的第一电回路21和暗态的第二电回路22的交界处23可确认失效点的深度位置。

71.其中,进一步参考芯片100的电路结构版图,根据获得的深度位置可确认开路位置对应的工艺步骤,调整对应的工艺步骤的具体参数,即可优化芯片100的性能,提高芯片的生产良率。

72.本发明提供的芯片的失效点定位方法去除芯片的边缘结构,以在芯片的截面上暴露出多个金属层的部分,通过暴露的金属层向芯片提供电流,并通过ebac(e-beam absorbance current,电子束吸收电流)技术获得芯片的截面在电流驱动下的截面图像,根据该截面图像的明暗区交界处位置直接定位获得失效点的深度位置,无需多次去层芯片,逐步暴露不同深度的底层金属进行多次测试,有效提升了失效点的深度位置的分析测试速度,为芯片研发提供了便利。

73.进一步地,还在芯片的上表面设置保护基底,降低截面制样去除边缘结构的操作使芯片破片的风险,保障截面制样后的芯片的结构可靠性,降低分析测试的干扰因素,保障测试效率。

74.进一步地,截面制样至芯片的顶层金属的侧边暴露,使芯片至少暴露其堆叠的多个金属层中的部分,并保持其它金属层不受截面制样的破坏,保障金属层的原有连接关系,保障分析测试获得的失效点位置的可靠性。

75.进一步地,在进行深度位置定位之前,还根据同样的ebac技术进行平面定位,无需进行与其它定位技术组合,降低分析测试的硬件需求,降低成本,结合失效点的平面位置和深度位置,可方便地确认失效点的三维位置。且对于平面定位后确认无失效点的良品芯片,无需再进行深度定位,看节约分析测试资源。

76.进一步地,根据失效点的平面位置选择芯片的截面的部分进行ebac技术测试,可降低ebac的驱动面积和电子显微镜的扫描面积,降低驱动功耗和扫描时间,可降低分析测试成本,缩短测试周期,提高分析测试效率。

77.进一步地,直接根据芯片的截面图像的整体图像,可结合芯片的整体设计布局直接获得失效点的平面位置和深度位置,可降低整体的操作数量,简化分析测试流程。

78.依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1