L2中CRQ和CWQ快速deallocate实现方法及系统与流程

l2中crq和cwq快速deallocate实现方法及系统

技术领域

1.本发明涉及cpu技术领域,具体涉及一种l2中crq和cwq快速deallocate实现方法及系统。

背景技术:

2.crq(core read queue)和cwr(core write queue)在l2中的作用是将lsu的read write请求放在queue中,并且每个core都有一个crq和cwq,该queue如果不能很快的deallocate,会导致该queue很快的full,从而导致不能接收来自core的新的request请求,而l1的reload请求响应的快慢又会严重影响cpu的整体性能。

3.针对该问题,我们提出:core read queue(crq)和core write queue(cwr)只要获得了仲裁并且上了pipeline就可deallocate掉对应的entry项,如果crq/cwq能正常的完成,则正常response lsu,如果不能正常完成,则将完整的权限交给oq(outstanding queue),这样就做到以最快的速度把crq/cwq的entry项deallocate掉。

技术实现要素:

4.针对现有技术的不足,本发明公开了一种l2中crq和cwq快速deallocate实现方法及系统,用于解决crq/cwq的entry项维护着lsu的read write请求在l2的完整生命周期,导致crq/cwq的entry项deallocate很晚,最终由于crq cwq full导致l2不能接收来自l1新的read write请求的问题。

5.本发明通过以下技术方案予以实现:

6.第一方面,本发明提供一种l2中crq和cwq快速deallocate实现方法,包括以下步骤:

7.s1接收来自core和外部extend的请求,由仲裁模块收来自crq cwq epq orq efq cpq的请求,并选出其中的一个请求进入pipeline;

8.s2根据请求的类型和当前l2中tag信息及mesi状态信息,判断下游所需要的数据或权限,并对应进行分配;

9.s3通过l2向下游memory发出读请求或写请求,并由下游memory返回reload data回填到efq;

10.s4由efq上l2de pipeline,并将reload回来的数据写入l2$中,同时将数据return请求的core;

11.其中,来自core的请求为load miss请求或lsu eviction请求。

12.更进一步的,所述方法中,接收来自core和外部extend的请求,包括接收来自core的read请求,放在crq中;接收来自core的write请求,放在cwq中;接收来自外部的probe请求,放在epq中。

13.更进一步的,其特征在于,所述方法中,在pipeline中,根据请求的类型和当前l2中tag信息及mesi状态信息确定:是否可以直接写入l2;

14.是否可以直接return data给请求方;是否需要向下游memory reload数据或权限;是否需要产生evict;是否需要向下游memory write数据;是否需要probe core。

15.更进一步的,所述方法中,如果判断需要向下游memory reload数据或权限,则分配一个orq;如果判断需要向下游memory write数据,则分配一个wrq;如果判断需要probe core,则分配一个cpq,l2向core发出probe请求,都是通过cpq来完成。

16.更进一步的,所述方法中,通过l2向下游memory发出读请求,则通过orq发出,向下游memory读取到数据并拿到该数据对应的权限。

17.更进一步的,所述方法中,通过l2向下游memory发出写请求,则通过wrq,将数据从l2中写到下一级memory中。

18.更进一步的,所述方法中,进行load miss请求时,包括以下步骤:

19.load miss请求从core发出,并allocate一个crq entry项;

20.crq的load miss请求上pipeline并赢得仲裁,上pipeline;

21.如果命中了tag_ram,直接deallocate掉crq中对应的entry项;

22.如果miss,tag_ram则allocate orq并且deallocate掉crq中对应的entry项

23.orq向下一级memory发出reload请求,等到refill回填数据;

24.下级memory回填数据写入efq中;

25.efq参与并获得pipeline仲裁;

26.更新l2 tag_ram data_ram将数据返回给core,同时deallocate掉相应的orq和efq对应的entry项。

27.更进一步的,所述方法中,进行lsu eviction请求时,包括以下步骤:

28.lsu eviction请求从core发出,并allocate一个cwq entry项;

29.cwq的lsu eviction请求上pipeline并赢得仲裁,上pipeline;

30.如果命中了tag_ram,直接deallocate掉cwq中对应的entry项,同时给lsu会response;

31.如果miss,tag_ram则allocate wrq,将数据写入wrq中,如果在wrq中已存在相同的pa,则将eviction数据merge进wrq中;

32.wrq将数据写入下一级memory;

33.下级memory会response给wrq,deallocate掉wrq对应的entry项。

34.第二方面,本发明提供了一种l2中crq和cwq快速deallocate实现系统,所述系统用于实现第一方面所述的l2中crq和cwq快速deallocate实现方法,包括probe、eviction、tag ram、data ram、crq、cwq、epq、orq、wrq、efq和cpq。

35.更进一步的,所述probe用于窥视和监听,将core中dirty的数据probe下来或者为了拿到e权限,把core中的mesi状态信息进行修改;

36.所述eviction,用于保持cache中保存的数据相对新的数据,在cache中需要把数据替换出去时产生;

37.所述tag ram用于记录cacheline的addr及该cacheline在l2和所有的l2 core中的mesi状态信息;

38.所述data ram用于记录cacheline的数据信息;

39.所述crq用于接收来自core的read请求存放的队列;

40.所述cwq用于接收来自core的write请求的队列;

41.所述epq用于接收来自外部的probe请求的队列;

42.所述orq,用于在一个在l2中的请求,上l2 pipeline后,发现本cache中该cacheline不存在或该cacheline的在本cache中的访问权限不够时,则需要申请一个orq,通过orq向下一级memory reload数据并拿到相应的权限;

43.所述wrq,用于在l2需要把某条cacheline给写到下一级memory,则申请要给wrq,通过wrq将数据写入下一级memory;

44.所述efq用于在由reload数据回填l2的时候,先把数据回填写入efq中,然后通过efq上l2的pipeline将数据写入l2$同时将数据return给请求模块;

45.所述cpq用于将probe相应的core,probe请求则先存放在cpq中,然后通过cpq向对应的core发出probe请求。

46.本发明的有益效果为:

47.本发明core read queue(crq)和core write queue(cwr)只要获得了仲裁并且上了pipeline就可deallocate掉对应的entry项,如果crq/cwq能正常的完成,则正常response lsu,如果不能正常完成,则将完整的权限交给oq(outstanding queue),这样就做到以最快的速度把crq/cwq的entry项deallocate掉,从而有效的提高了cpu的整体性能。

附图说明

48.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

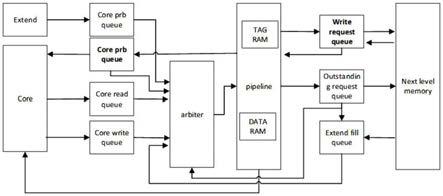

49.图1是本发明实施例l2的基本框图;

50.图2是本发明实施例load miss请求的基本流程图;

51.图3是本发明实施例lsu eviction请求的基本流程图。

具体实施方式

52.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

53.实施例1

54.参照图1所示,本实施例公开一种l2的基本框图,其基本功能描述如下:

55.本实施例接收来自core和外部extend的请求,包括

56.接收来自core的read请求,放在crq(core read queue)中

57.接收来自core的write请求,放在cwq(core write queue)中

58.接收来自外部的probe请求,放在epq(extend probe queue)中

59.本实施例仲裁模块接收来自crq cwq epq orq efq cpq的请求,选出其中的一个请求进入pipeline

60.本实施例在pipeline中,根据请求的类型,和当前l2中tag信息及mesi状态信息确定:

61.是否可以直接写入l2;

62.是否可以直接return data给请求方;

63.是否需要向下游memory reload数据或权限;

64.是否需要产生evict;

65.是否需要向下游memory write数据;

66.是否需要probe core等;

67.本实施例中,如果判断需要向下游memory reload数据或权限,则分配一个orq(outstanding request queue);

68.本实施例中,如果判断需要向下游memory write数据,则分配一个wrq(write requet queue);

69.本实施例中,如果判断需要probe core,则分配一个cpq(core probe queue),l2向core发出probe请求,都是通过cpq(core probe queue)来完成。

70.本实施例l2向下游memory发出请求:

71.读请求,则通过orq(outstanding request queue)发出,向下游memory读取到数据并拿到该数据对应的权限

72.写请求,则通过wrq(write requet queue),将数据从l2中写到下一级memory中

73.本实施例l下游memory返回reload data回填到efq(extend fill queue)。再由efq(extend fill queue)上l2de pipeline,讲reload回来的数据写入l2$中,同时将数据return请求的core。

74.实施例2

75.本实施例提供一种memory系统维护数据一致性的协议,用来表明对该cacheline当前core具有怎么的权限,具体如下:

76.m:modify,表明该core对该cacheline进行了修改,该cacheline只在本cache中存在,如果其它cache需要访问该cachelin,则需要通过probe的方式才能拿到最新dirty数据,并拿到相应的权限

77.e:exclusive表明该cacheline只在本cache中存在,如果其它cache需要访问该cacheline,则需要通过probe的方式拿到相应的数据和权限

78.s:shared表明该cacheline不仅在本cache中存在,可能还在其它的cache中存在,如果其它cache需要访问该cacheline,并拿到e/m态,则需要通过probe的方式拿到相应的数据和权限

79.i:invalid表明该cacheline不在本cache中。

80.实施例3

81.在具体实施层面,本实施例提供一个load miss和lsu eviction请求的基本流,也就是read write的基本流程。

82.本实施例中,如图2所示,load miss请求的基本流程如下:

83.1、load miss请求从core发出,并allocate一个crq entry项

84.2、crq的load miss请求上pipeline并赢得仲裁,上pipeline

85.3、如果命中了tag_ram,直接deallocate掉crq中对应的entry项

86.4、如果miss,tag_ram则allocate orq并且deallocate掉crq中对应的entry项

87.5、orq向下一级memory发出reload请求,等到refill回填数据

88.6、下级memory回填数据写入efq中

89.7、efq参与并获得pipeline仲裁

90.8、更新l2 tag_ram data_ram将数据返回给core,同时deallocate掉相应的orq(outstanding request queue)和efq((extend probe queue))对应的entry项

91.本实施例中,如图3所示,lsu eviction请求的基本流程如下:

92.1、lsu eviction请求从core发出,并allocate一个cwq entry项

93.2、cwq的lsu eviction请求上pipeline并赢得仲裁,上pipeline

94.3、如果命中了tag_ram,直接deallocate掉cwq中对应的entry项,同时给lsu会response

95.4、如果miss,tag_ram则allocate wrq,将数据写入wrq中,如果在wrq中已存在相同的pa,则将eviction数据merge进wrq中

96.5、wrq将数据写入下一级memory

97.6、下级memory会response给wrq,deallocate掉wrq对应的entry项

98.本实施例中,从上面读写流程可以看出,crq或cwq只要赢得仲裁上了pipeline,就可立马deallocate掉,从而可以空出entry项来接收lsu发来的新请求。

99.实施例4

100.本实施例提供一种l2中crq和cwq快速deallocate实现系统,包括probe、eviction、tag ram、data ram、crq、cwq、epq、orq、wrq、efq和cpq。

101.本实施例中,所述probe用于窥视和监听,将core中dirty的数据probe下来或者为了拿到e权限,把core中的mesi状态信息进行修改;

102.所述eviction,用于保持cache中保存的数据相对新的数据,在cache中需要把数据替换出去时产生;

103.所述tag ram用于记录cacheline的addr及该cacheline在l2和所有的l2 core中的mesi状态信息;

104.所述data ram用于记录cacheline的数据信息;

105.所述crq用于接收来自core的read请求存放的队列;

106.所述cwq用于接收来自core的write请求的队列;

107.所述epq用于接收来自外部的probe请求的队列;

108.所述orq,用于在一个在l2中的请求,上l2 pipeline后,发现本cache中该cacheline不存在或该cacheline的在本cache中的访问权限不够时,则需要申请一个orq,通过orq向下一级memory reload数据并拿到相应的权限;

109.所述wrq,用于在l2需要把某条cacheline给写到下一级memory,则申请要给wrq,通过wrq将数据写入下一级memory;

110.所述efq用于在由reload数据回填l2的时候,先把数据回填写入efq中,然后通过efq上l2的pipeline将数据写入l2$同时将数据return给请求模块;

111.所述cpq用于将probe相应的core,probe请求则先存放在cpq中,然后通过cpq向对

应的core发出probe请求。

112.综上,本发明core read queue(crq)和core write queue(cwr)只要获得了仲裁并且上了pipeline就可deallocate掉对应的entry项,如果crq/cwq能正常的完成,则正常response lsu,如果不能正常完成,则将完整的权限交给oq(outstanding queue),这样就做到以最快的速度把crq/cwq的entry项deallocate掉,从而有效的提高了cpu的整体性能。

113.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1