用于二值化卷积神经网络的处理器,逻辑芯片及其方法与流程

用于二值化卷积神经网络的处理器,逻辑芯片及其方法

背景技术:

1.本发明与神经网络技术相关。神经网络是一种机器学习模型,用于接受输入数据并通过一层或多层神经网络层对输入数据进行处理以输出诸如分类或决策的输出。每一神经网络层的输出将作为下一神经网络层的输入进行进一步处理。在整个神经网络的输入层和输出层之间的那些层被称为隐藏层。

2.卷积神经网络是一类由一层或多层执行卷积功能的卷积层构建的神经网络。卷积神经网络应用于多个领域,包括但不限于,图像和视频识别,图像和视频分类,声音识别和分类,面部识别,医疗数据分析,自然语言处理,用户偏好预测,时间序列预测和分析等。

3.通常的,具有大量单元层的卷积神经网络往往具有更好的性能,但同時对内存和计算资源的要求更高。因此,卷积神经网络通常在具有强大的图形处理单元(gpu)或张量处理单元(tpu)以及大量系统内存的计算机或服务器群集上实现。然而,随着机器学习和人工智能等应用的日益普及,现在亦希望能够在资源有限的设备(例如智能电话,相机和平板电脑等)上实现卷积神经网络的应用。附图简要说明

4.在附图中,除非另外规定,否则贯穿多个附图相同的附图标记表示相同或相似的部件或元素。这些附图不一定是按照比例绘制的。应该理解,这些附图仅描绘了根据本发明公开的一些实施方式,而不应将其视为是对本发明范围的限制。

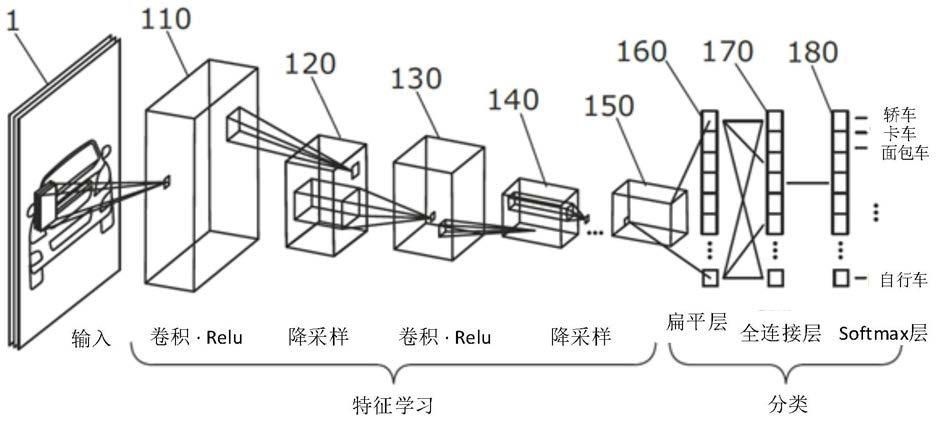

5.图1a所示为一个卷积神经网络示例;

6.图1b所示为一个卷积运算示例;

7.图1c所示为一个最大池化操作示例;

8.图2所示为根据本发明实施例的用于执行卷积神经网络的处理器示例;

9.图3a所示为根据本发明实施例的用于执行卷积神经网络的逻辑芯片示例;

10.图3b所示为根据本发明实施例的一个卷积神经网络示例;

11.图3c所示为用于执行卷积神经网络的逻辑芯片的卷积设计;

12.图3d所示为根据本发明实施例的用于执行卷积神经网络的逻辑芯片示例;

13.图4所示为根据本发明实施例的用于执行卷积神经网络的处理器示例;

14.图5a所示为根据本发明实施例的执行卷积神经网络的一个卷积层的示例方法;

15.图5b所示为根据本发明实施例的执行卷积神经网络的降采样层的示例方法;

16.图6所示为根据本发明实施例的二值化卷积运算示例;

17.图7所示为根据本发明实施例的一种增强型二值化卷积模型示例;

18.图8所示为根据本发明实施例的一种增强型二值化卷积模型示例;

19.图9所示为根据本发明实施例的一种增强型二值化卷积模型在卷积模式下执行的操作示例;

20.图10a所示为一种二元平均池化操作以及一种二元最大池化操作的示例;

21.图10b所示为根据本发明实施例的一种增强型二值化卷积模型在降采样模式下执行的操作示例;

22.图10c所示为根据本发明实施例的一种增强型二值化卷积模型在降采样模式下执行的另一种操作示例;

23.图11所示为根据本发明实施例的一种增强型二值化卷积模型在卷积模式下执行的操作示例;

24.图12所示为根据本发明实施例的一种卷积神经网络的构架示例;

25.图13所示为根据本发明实施例的一种设计卷积神经网络的方法示例;

26.图14所示为根据本发明实施例的一种将特征图分类的方法示例。

技术实现要素:

27.相应的,本发明的第一方面提供了一种用于实现二值化卷积神经网络(bcnn)的处理器,所述二值化卷积神经网络包括多个层,所述多个层包括二值化卷积层和降采样层;其中,所述二值化卷积层和所述降采样层均由所述处理器的共享逻辑模块执行,所述共享逻辑模块包括:增强单元,用于基于增强参数对输入到所述共享逻辑模块的特征图进行增强;二值化卷积单元,用于基于卷积参数对输入到所述共享逻辑模块的特征图进行二值化卷积运算;和组合单元,用于将所述增强单元的输出与所述二值化卷积单元的输出进行组合;其中,通过调节所述增强参数和所述卷积参数中的至少一个,所述共享逻辑模块可在卷积模式和降采样模式之间切换。

28.本发明的第二方面提供了一种用于实现二值化卷积神经网络的逻辑芯片,该逻辑芯片包括:共享逻辑模块,其能够对特征图执行二值化卷积操作和降采样操作两者;存储器,用于存储所述共享逻辑模块的可调参数,其中,所述可调参数用于确定所述共享逻辑模块执行二值化卷积操作或降采样操作;和控制器或控制接口,其通过调整所述共享逻辑模块的所述可调参数来控制所述共享逻辑模块执行至少一项二值化卷积操作然后执行至少一项降采样操作。

29.本发明的第三方面提供了一种方法,其经由实施二值化卷积神经网络的处理器对图像进行分类,所述方法包括:a)由所述处理器接收与待分类图像相对应的第一特征图;b)由所述处理器接收第一组参数,其包括至少一个滤波器,至少一个步幅和至少一个增强变量;c)由所述处理器使用所述至少一个滤波器和所述至少一个步幅对所述第一特征图执行二值化卷积操作以产生第二特征图;d)由所述处理器使用所述至少一个增强变量对所述第一特征图执行增强操作以产生第三特征图;e)由所述处理器将所述第二特征图和所述第三特征图进行组合;f)接收第二组参数,其包括至少一个滤波器,至少一个步幅和至少一个增强变量;g)使用第二组参数代替第一组参数,并使用组合的所述第二和第三特征图代替第一特征图,重复步骤c)至e)。

30.本发明的进一步特征和方面在所附权利要求中提供。

具体实施方式

31.为了简单和说明的目的,本公开主要通过参考其示例来描述。如本文中所用,术语“包括”(“includes”)是指包括但不限于,术语“包括”(“including”)是指包括但不限于。术语“包括”(“comprises”)是指包括但不限于,术语“包括”(“comprising”)是指包括但不限于。术语“基于”表示至少部分基于。术语“数”是指等于或大于一的任何自然数。术语“a”和

“

an”旨在表示特定元素中的至少一个。

32.图1a所示为用于将图片分类的一种卷积神经网络(cnn)示例100。特征图1表示输入卷积神经网络以进行分类的输入图像。卷积神经网络通过多个层处理输入的特征图1并输出分类结果180,例如是一系列选定图像分类中的某一种,例如小轿车,卡车,货车等。

33.在图1a的示例中,输入特征图用于表示图像,但在其他示例中输入特征图也可以表示音频信号,医疗数据,自然语言文本或其他种类的数据。特征图包括多个元素中每个元素的值,并且在一些示例中可以用矩阵来表示。卷积神经网络可以具有多个输出节点。卷积神经网络的输出可以是与某一节点(例如卡车)相对应的一种分类,也可以是基于每个预定输出节点的一种概率分布(例如95%的汽车,3%的货车,2%的卡车)。输出可以是例如基于输入特征图的分类或判定。

34.在输入1和输出180之间的卷积神经网络层对于用户可能是不可见的,因此被称为隐藏层。卷积神经网络的每一层都从前一层接收特征图,并对接收到的特征图进行处理以生成另一特征图从而输出到下一层。因此,第一特征图1被输入到卷积神经网路100并由卷积神经网络的第一层110处理以产生第二特征图,其被输入到卷积神经网络的第二层120。之后,第二层120处理该第二特征图从而产生第三特征图,其被输入到卷积神经网络的第三层130,等等。cnn通常包括多个卷积层,多个降采样层和一个或多个全连接层。

35.在图1a的示例中,层110、130和150是卷积层。卷积层是将卷积函数应用于输入特征图的层。图1b所示为卷积操作的示例,其中输入特征图1b与一滤波器(有时也称为内核)110b进行卷积运算。卷积运算可以包括在输入特征图上移动滤波器,并且在每个步骤中计算滤波器和输入特征图的点积以产生输出特征图111b的值。因此,在图1b的示例中,将3

×

3滤波器110b乘以输入特征图1b的3

×

3阴影区域,并且结果“15”作为输出特征图111b左上单元。然后,如图1b底部所示,将滤波器移至左侧,并进行另一个点积,这一次得到值“16”作为特征图111b右上单元。继续此过程,直到将滤波器移过输入特征图的每个像素进行计算并完成输出特征图为止。卷积计算使卷积神经网络识别特征成为可能。由于卷积神经网络具有许多层,较早的卷积层可以识别基本特征(例如边缘),而较后的层可以识别更抽象的特征(例如对象的形状或组成部分)。

36.在图1a的示例中,层120和140是降采样层。降采样层是用于减小输入特征图的尺寸的层。常规的神经网络通过平均池化或最大池化的方式执行降采样。在最大池化中,如图1c所示,将输入特征图1c的值划分为子集(例如,图1c中以灰色阴影显示的2x2子集),每个子集的最大值作为输出特征图111c的相应单元。在平均池化的方式中,每个子集的平均值作为输出特征图111c的相应单元。通过减小传递到下一层的特征图尺寸并保留其中最重要的信息,降采样层将卷积神经网络的节点数量保持在可管理的范围内。

37.常规的卷积神经网络使用大容量存储器来存储各种卷积滤波器的特征图和权重(值),并使用功能强大的处理器来计算各种卷积运算。这使得在一些资源受限的设备上难以实施卷积神经网络运算,这些设备具有有限的内存和功能较弱的处理器,尤其是在卷积神经网络具有许多层的情况下。虽然资源受限的设备可以在诸如专用集成电路(asic)或现场可编程门阵列(fpga)的硬件逻辑芯片上实现卷积神经网络,但由于此类逻辑芯片有限的内存和处理能力导致该实现具有挑战性。此外,由于卷积层和池化层执行不同的逻辑操作,因此这些层需要不同的逻辑组件,这将消耗大面积的硅片空间,从而增加逻辑芯片的尺寸

和成本。

38.因此,本公开提出了一种用于实现二值化卷积神经网络(bcnn)的处理器,该处理器包括多个层,该多个层包括二值化卷积层和降采样层,其中,二值化卷积层和降采样层皆可通过处理器的共享逻辑模块执行相关操作。通过调整共享逻辑模块的参数,共享逻辑模块可在用于执行卷积操作的卷积模式与用于执行降采样操作的降采样模式之间切换。共享逻辑模块之所以被称为共享逻辑模块,是因为它能够同时实现卷积神经网络的卷积层和降采样层,因此属于该两类层的共享逻辑资源。共享逻辑模块也可以称为增强型二值化卷积模块,其中的二值化表示该模块执行的是二值化卷积运算,而增强型表示其既能够执行降采样运算也能够执行卷积运算。

39.图2所示为根据本发明实施例的处理器示例200。处理器200被配置为实现包括至少一个卷积层252和至少一个降采样层254的卷积神经网络250。处理器200包括共享逻辑模块220,该共享逻辑模块220用于接收输入到该共享逻辑模块的特征图201,根据该共享逻辑模块的模块参数224处理输入特征图201,并基于此处理结果输出特征图202。共享逻辑模块220所执行的处理类型由参数224决定。通过调整参数224,共享逻辑模块220即可在卷积模式和降采样模式之间切换。

40.在卷积模式下,共享逻辑模块220对输入特征图201实施二值化卷积操作以实现卷积神经网络的卷积层252,并输出卷积特征图202。在降采样模式下,共享逻辑模块220对输入特征图201实施降采样操作以实现卷积神经网络的降采样层254,并输出降采样特征图202。

41.在一些实施例中,处理器200可以是逻辑芯片,诸如fpga或asic。由于共享逻辑模块220能够执行卷积和降采样操作两者,因此与具有分离的卷积和降采样模块的常规卷积神经网络逻辑芯片相比,共享逻辑模块220的尺寸和/或成本可以大大减小。此外,由于是通过共享逻辑模块220实现卷积层252的二值化卷积运算,因此与传统的卷积神经网络相比,其处理和存储要求显著降低。

42.在其他实施例中,共享逻辑单元220可以由处理器200可执行的机器可读指令来实现。例如,卷积神经网络可以在台式计算机,服务器或云计算服务等上实现,其中将对初始卷积神经网络进行训练并调整权重(“训练阶段”)。一旦对卷积神经网络的训练完成并最终确定了卷积权重,即可将其部署在逻辑芯片上以用于“推理阶段”。

43.图3a,3b和3c作为示意图阐述了与先前技术相比,根据本发明实施例的硬件逻辑芯片,诸如fpga或asic,如何使用更少的硬件组件和/或使用更少的硅片空间以实现所需功能。图3b示出了卷积神经网络示例300b,其包括以下系列层:第一卷积层310b,第二卷积层320b,第一降采样层330b,第三卷积层340b,第二降采样层350b和分类层360b。这些层可以执行诸如与图1a中所示的卷积,降采样和分类层同样的功能。图3a所示为根据本发明实施例的能够实现图3b中的卷积神经网络300b的逻辑芯片示例300a。同时,图3c所示为逻辑芯片300c的一种常规设计,其使用现有技术以实现图3b中的卷积神经网络300b。

44.可以看出,常规逻辑芯片300c针对卷积神经网络300b的每一层都具有单独的硬件模块。因此,逻辑芯片300c总共具有六个模块:第一卷积模块310c,第二卷积模块320c,第一池化模块330c,第三卷积模块340c,第二池化模块350c和分类层360c。每个模块实现卷积神经网络的相应层,如虚线箭头所示,例如,第一卷积层310b由第一卷积模块310c实现,第一

降采样层330b由第一池化模块330c实现等。

45.相比之下,与逻辑芯片300c的常规设计相比,逻辑芯片300a能够以较少数量的硬件模块来实现卷积神经网络300b。这是因为逻辑芯片300a包括共享逻辑模块(也可以称为增强型二值化卷积模块)320a,其能够实现卷积层和降采样层两者。因此,如虚线所示,逻辑芯片300a的增强型二值化卷积模块320a实现了卷积神经网络300b的多个层320b,330b,340b和350b。换句话说,单个模块320a执行由常规逻辑芯片300c中多个模块所执行的功能。因此,与逻辑芯片300c相比,逻辑芯片300a可以具有更小的芯片尺寸和降低的制造成本。

46.在图3a中,逻辑芯片300a包括共享逻辑模块320a,存储器322a和控制器326a。尽管在图3a中将存储器322a和控制器326a示为单独的组件,但在其他示例中,存储器和/或控制器可以集成入并成为共享逻辑模块320a的一部分。共享逻辑模块320a能够对输入到模块320a的特征图执行二值化卷积操作和降采样操作两者。存储器322a存储可调参数324a,该可调参数324a用于确定共享逻辑模块320a是对特征图执行二值化卷积操作还是降采样操作。控制器326a被配置为通过调整共享逻辑模块的可调参数324a以控制共享逻辑模块320a执行至少一个二值化卷积操作,随后执行至少一个降采样操作。

47.在一个示例中,控制器326a可以存储的一组适当的可调参数,并发送控制信号以使共享逻辑模块读取特征图并基于该组可调参数对该特征图执行操作。控制器326a可以是诸如控制逻辑芯片操作的处理组件。在其他示例中,控制器326a可以是控制接口,用于从外部设备接收控制信号至逻辑芯片300,其中该控制信号设置可调参数和/或控制共享逻辑模块320a。

48.逻辑芯片300a还可以包括解码模块310a,该解码模块310a用于接收非二值化输入,将该输入转换为二值化特征图并将二值化特征图输出到共享逻辑模块。在这种情况下,解码意味着将非二值化特征图转换为二值化特征图。例如,解码模块310a可以是卷积模块,其接收输入到逻辑芯片的特征图并执行卷积操作,接着执行二值化操作以将二值化的特征图输出到模块320a。在另一个实施例中,为了将非二值化输入转换为二值化特征图,解码模块可以将8位rgb数据转换为色温码以替代使用卷积运算。逻辑芯片接收的输入数据可以是诸如由照相机生成的图像,声音文件或其他类型的数据。在其他实施例中,逻辑芯片300a可以不包括解码模块,而是可以从外部解码模块接收二值化特征图。在此类实施例中,可以在单独的逻辑芯片上实现解码功能。

49.逻辑芯片300a还可以包括全连接层模块360a,用于针对共享逻辑模块320a输出的特征图进行分类。因此,全连接层模块360a实现了卷积神经网络300b的分类层360b。在其他示例中,逻辑芯片300a可以不包括全连接层模块,而是可以将特征图输出到外部全连接层模块。在这些其他示例中,分类层可以在单独的逻辑芯片上实现。

50.在图3a所示的实施例中,逻辑芯片300a包括共享逻辑模块320a,存储器322a和控制器326a。图3d所示为根据本发明一个实施例的逻辑芯片300d,其中存储器和控制器由外部设备提供并且不形成逻辑芯片的一部分是。逻辑芯片300d包括共享逻辑模块320d,该共享逻辑模块320d具有至少一个输入接口以接收输入特征图301,可调参数324d和控制信号326d,以及一个输出接口以输出输出特征图302。例如,可以从外部存储器读取输入特征图301和可调参数。输入特征图301可以是诸如在执行卷积神经网络的前一层运算时在前一个处理周期中由外部解码模块输出的特征图或由共享逻辑模块输出的特征图。在一些实施例

中,输入特征图可以是基于由照相机捕获的图像或由物理传感器捕获的数据。在实现了卷积神经网络的最终降采样或卷积层(例如图3b中的层350b)之后,共享逻辑模块320d可以将结果特征图输出到另一个逻辑芯片,以实现卷积神经网络的全连接层。

51.如上所述,在一些使用共享逻辑模块320a、320d的实施例中,与常规设计相比,逻辑芯片300a、300d可以节省空间并且使用更少的硬件模块。此外,当共享逻辑模块320a、320d执行二值化卷积时,与执行非二值化卷积的常规逻辑芯片相比,所使用的存储器和所需的处理能力可减少或降低。此外,当共享逻辑模块320a、320d执行降采样时,可以减少或避免在对二值化特征图执行平均或最大池化时经常发生的信息丢失。

52.图4示出了根据本发明实施例的用于实现卷积神经网络的另一处理器示例400。处理器400包括共享逻辑模块420,该共享逻辑模块420用于实现卷积神经网络450的卷积层452和降采样层454两者。这可以通过调整共享逻辑模块420的参数p1,p2来完成。处理器400,共享逻辑模块420,卷积神经网络450以及层452和454可以对应于图2所示实施例中的处理器200,共享逻辑模块220,cnn 250以及层252和254。

53.共享逻辑模块420可以包括增强单元422,二值化卷积单元424和组合单元426。增强单元422可以被配置为基于至少一个增强参数p1来增强输入到共享逻辑模块的特征图。二值化卷积单元424可以被配置为基于至少一个卷积参数p2对输入到共享逻辑模块的特征图401执行二值化卷积操作。组合单元426可以被配置为将增强单元422的输出与二值化卷积单元424的输出相组合。通过调节增强参数p1和卷积参数p2中的至少一个,共享逻辑模块420可以在卷积模式和降采样模式之间切换。

54.在一些实施例中,处理器400可以仅包含共享逻辑模块420,而在其他实施例中,处理器400可以包括由虚线430所示的其他模块。例如,这些其他模块可以包括解码模块和全连接层模块等。

55.与图2中的实施例相类似,因为图4的共享逻辑模块420能够执行卷积和降采样两者,在硬件逻辑芯片上实现卷积神经网络所需的逻辑组件的数量将会减少。由于共享逻辑单元具有二值化卷积单元,因此与非二值化方式相比,其可以用较小的存储和处理能力来实现卷积层。此外,由于降采样是由二值化卷积单元和/或增强单元来处理,而不是由平均池化或最大池化来处理,从而避免或减少了将平均池化或最大池化应用于二值化特征图时发生的信息丢失。

56.增强单元还可以帮助避免卷积层中的信息丢失。使用二值化卷积神经网络的困难之一是信息丢失,尤其是经过几次二值化卷积之后容易在网络的较深层中丢失,这会阻碍卷积神经网络的训练过程和识别模式的能力。在图4所示的处理器架构中,在每一层,将输入特征图401提供至增强单元422和二值化卷积单元424,并且将增强单元422的输出与二值化卷积单元424的输出相组合。由于增强单元所执行的增强操作可以保留输入特征图的部分或全部原始数据,并将此类信息传递到下一层,上述构架将有助于避免或减少过多的信息丢失。

57.在一个实施例中,组合单元被配置为将增强单元的输出与二值化卷积单元的输出进行级联。

58.增强单元422被配置为通过执行至少一个增强操作来增强输入特征图401。增强操作是在保持输入特征图的某些特性的同时,基于输入特征图生成新的特征图的操作。增强

操作可以包括诸如恒等功能,缩放功能,镜像功能,翻转功能,旋转功能,频道选择功能和裁剪功能中的一项或多项。恒等功能复制输入,以使从增强单元输出的特征图与输入到增强单元的特征图相同。缩放功能将输入特征图的每个单元的值乘以相同的因数。例如,如果缩放因子为2,则每个单元值加倍;如果缩放因子为0.5,则每个单元值减半。如果缩放因子为0,则输出为空。空输出表示没有输出,或是其每个单元值皆为0的输出特征图。镜像,翻转和旋转功能分别用于镜像翻转特征图,绕轴翻转特征图或旋转特征图。通道选择功能用于从特征图中选择某些单元并丢弃其他单元,例如,随机选择某些行或所有偶数行或列,同时丢弃奇数行或列等。裁剪功能会删除某些单元格以缩小特征图的尺寸,例如,移除围绕特征图边缘的单元。

59.在一个示例中,增强单元422被配置为对特征图执行缩放功能,并且增强参数p1是缩放因子。在一个实施例中,在卷积模式下将缩放因子设置为非零值,并且在降采样模式下将缩放因子设置为零值。这样在降采样模式中增强单元的输出为空值且可在降采样模式中被丢弃。在硬件实现中,在缩放因子为零的操作模式下,可以跳过增强操作以节省能量和处理能力。在通过级联进行组合的情况下,来自增强单元的空值可以减少输出通道的数量,从而使得输出通道的数量以及特征图的尺寸降低,这可能是一些卷积神经网络构架中的降采样层所需要的。。

60.图5a所示为根据本发明实施例的采用处理器的共享逻辑模块以实现二值化卷积神经网络(bcnn)的卷积层的示例方法500a。例如,该方法可以由图4中处理器400的共享逻辑模块420当其在卷积模式下时来实现。

61.在方框510a中,共享逻辑模块接收输入特征图。输入特征图可以是诸如输入到二值化卷积神经网络的特征图或从二值化卷积神经网络的前一层接收的特征图。

62.在方框520a中,共享逻辑模块接收用于执行卷积层的增强参数和卷积参数。例如,共享逻辑模块可以从存储器读取这些参数或通过控制指令接收这些参数。

63.在方框530a中,通过增强单元对输入特征图执行增强操作。

64.在方框540a中,通过二值化卷积单元对输入特征图执行二值化卷积操作。

65.在方框550a中,将二值化卷积单元与增强单元的输出进行组合。

66.在方框560a中,基于方框550中的组合输出特征图。

67.例如,可以在方框550a中将增强单元和二值化卷积单元输出的特征图进行级联,然后可以在方框560a中输出级联的特征图。

68.图5b示出了根据本发明的采用处理器的共享逻辑模块以实现二值化卷积神经网络的降采样层的示例方法500b。例如,该方法可以由图4中处理器400的共享逻辑模块420在降采样模式时实现。

69.在方框510b中,共享逻辑模块接收输入特征图。输入特征图可以是诸如输入到二值化卷积神经网络的特征图或从卷积神经网络的上一层接收的特征图。

70.在方框520b中,共享逻辑模块接收用于执行卷积层的增强参数和卷积参数。例如,共享逻辑模块可以从存储器中读取这些参数,或者可以通过控制指令接收这些参数。

71.在方框530b中,通过增强单元对输入特征图执行增强操作。

72.在方框540b中,通过二值化卷积单元对输入特征图执行二值化卷积操作。

73.在方框550b中,将二值化卷积单元和增强单元的输出进行组合。

74.在方框560b中,基于方框550中的组合,输出一个或多个特征图。

75.例如,可以在方框550b中将增强单元和二值化卷积单元输出的特征图进行级联,并可以向方框560b中输出该级联的特征图。

76.应当理解,共享逻辑模块的处理块在卷积和降采样模式下相同,但是所使用的参数不同。因此,通过调整参数,增强二值化卷积模块可以在卷积模式和降采样模式之间切换。从以上图4、5和6的示例中可以认识到,本发明涉及两个主要操作

‑

二值化卷积和增强。以上已阐述了增强操作的示例。现在将参照图6以非限制性示例的方式描述二值化卷积的示例。

77.如图6所示,二值化卷积600的操作类似于图1b所示的普通(非二值化)卷积的操作。即,滤波器620在输入特征图610上移动,并且在每一步计算滤波器正对当前元素的点积。在每一步中,滤波器都会跨越或沿着输入特征图移动等于步幅的多个单元。每一步的值之和形成输出特征图630的单元值。但是,与普通卷积不同的是,在普通的卷积中单元可能具有许多不同的值,然而在二值化卷积中,输入特征图610和滤波器620的值被二值化了。即是说,这些值被限制为两个可能值之一,例如。1和0。这大大减少了执行卷积运算所需的内存,因为只需要1位来保存输入特征图的每个单元和滤波器所计算的每个单元的值。此外,由于乘积值为1或0,从而大大简化了点积计算,因此可以使用xnor逻辑门来计算点积。由于普通卷积可能涉及浮点运算,并且通常使用功能更强大的处理器或更复杂的逻辑门布置,因此,与普通(非二值化)卷积相比,用于二值化卷积的逻辑电路所需的处理能力和复杂度大大降低。

78.在一个示例中,共享逻辑模块或增强二值化卷积模块使用的参数包括滤波器和步幅。滤波器可以是在特征图上移动以执行卷积运算的矩阵,步幅表示滤波器在卷积运算的过程中每一步所移动的单元数。

79.图7所示为根据本发明实施例的增强二值化卷积模块700的示意性示例。它可以用作诸如图2、3a,3d或图4中的共享逻辑模块或可以用来实现图5a和图5b的方法。

80.增强型二值化卷积模块700可以包括存储器710和控制器或控制接口750。存储器710可以存储输入特征图718,该输入特征图718将根据一系列参数进行处理,包括旁路参数712,步幅714和滤波器716。旁路参数712可以对应于图4中的增强参数p1,步幅和滤波器可以对应于图4中的卷积参数p2。尽管在图4中仅示出了一个步幅,滤波器,增强参数以及特征图,但本领域技术人员应当理解的是,存储器710亦可以存储多个步幅,滤波器,增强参数和/或特征图。

81.增强型二值化卷积模块700包括增强型二值化卷积单元730,旁路单元720,级联器740。增强型卷积模块可以接收输入特征图718并且将输入特征图718存储在存储器中。例如,可以从增强型二值化卷积模块700的前一处理周期或者从诸如解码模块的另一逻辑模块接收输入特征图718。

82.二值化卷积单元730被配置为对输入特征图执行二值化卷积运算。单元730可以对应于图4中的二值化卷积单元424。二值化卷积单元可以包括用于执行二值化卷积运算的逻辑门,例如xnor门。当滤波器以与步幅相等的步长在输入特征图上移动时,二值化卷积单元可以将输入特征图718的值与滤波器716的值相乘。二值化卷积单元730可以将二值化卷积的结果输出到级联器740。

83.旁路单元720被配置为将输入特征图转发给级联器740。旁路单元720之所以被称为旁路单元是因为他旁路了二值化卷积运算。在一些实施例中,旁路单元可以被配置为在将输入特征图转发给连接器之前,对输入特征图执行增强操作。因此,旁路单元可以与图4的增强单元422以类似的方式运作。

84.级联器740被配置为将二值化卷积单元的输出与旁路单元的输出级联。级联器可以对应于图4的组合单元426。

85.图8所示增强二值化卷积模块800的示意图示例,连同输入到该模块的特征图801和从该模块输出的特征图804。图8是具体实现方式的示例并且本发明不限于图8所示的特征的具体设置。相反,图8只是以上图2

‑

7中描述的增强二值化卷积模块和共享逻辑模块的一种可能的实现方式。

86.增强二值化卷积模块800包括增强单元820,二值化卷积单元830和级联器840。这些单元可以以与前述实施例所述的增强或旁路模块,二值化卷积模块以及级联器相同的方式操作。增强二值化卷积模块800还包括控制器850和一个或多个存储器,该存储器存储包括用于增强模块的缩放因子822以及用于二值化卷积单元的滤波器832和步幅834。控制器850控制模块800的操作顺序。例如,控制器可以设置缩放因子822,滤波器832和步幅834,可以使输入特征图801输入到增强单元820和二值化卷积单元830,并且可以指示增强单元820和二值化卷积单元830对输入特征图执行增强和卷积操作。

87.如图8所示,可以有多个被称为第一特征图的输入特征图801。每个特征图包括多个值,也称为激活。该特征图是二值化的,例如每个值都是1或0。每个输入特征图都可被视为当前层的输入通道,因此,如果有5个尺寸为32x32的输入特征图,则可以说,当前层具有5个输入通道,其尺寸为32x32。第一特征图801将被输入到增强单元820和二值化卷积单元830两者。

88.二值化卷积单元830可以使用滤波器832并基于步幅参数834在每个第一特征图801上执行诸如上图6所述的二值化卷积操作。二值化卷积单元可以执行n

×

n二值化卷积运算,其采用尺寸为n

×

n(例如在图6的示例中为3

×

3)的滤波器进行二值化卷积运算。在一些实施例中,在n

×

n二值化卷积操作之后跟着是批量归一化操作836和/或二值化激活操作838。

89.批量归一化操作836用于将二值化卷积得到的输出特征图进行标准化处理的过程。在本领域中已知各种类型的批量归一化操作。批量归一化的一种可能方法包括计算从二值化卷积输出的特征图中所含像素值的平均值和标准偏差,并使用这些统计信息执行归一化操作。批量归一化可以帮助减少内部协变量偏移,稳定学习过程并减少训练卷积神经网络所需的时间。

90.二值化激活操作838是对特征图的值进行二值化的操作。二值化激活可被应用于诸如由批量归一化操作836处理后的特征图,又或者如果没有批量归一化操作,则直接应用于二值化卷积830的输出。由图6可以看出,由二值化卷积输出的特征图的激活值并非二值化并且可以大于1。因此,二值化激活操作838进一步将这些激活值二值化以输出如图8所示的二值化特征图802。

91.在一些实施例中,通过将批量归一化操作的参数与n x n二值化卷积操作以及二值化激活操作的参数合并,从而可以将n x n二值化卷积操作,批量归一化和二值化激活操

作压缩进单一的计算块。例如,一旦将卷积神经网络训练好后,可在推理阶段将以上三项操作压缩进单个计算块,以降低用于实现卷积神经网络的硬件的复杂性。例如,为了将单元830、836和838压缩到单个计算块,可以将批量归一化操作836替换为符号函数,并且可以将批量归一化的运行平均值参数γ和运行方差参数β归入二值化卷积的滤波器832的激活值中。

92.因此,二值化卷积单元830在输入特征图801上执行卷积运算并输出一组被称为第二特征图的特征图802,该组特征图可以被称为第二特征图。同时,增强单元820对输入的特征图801执行增强操作。例如,增强操作可以是根据缩放因子822执行的缩放操作。增强单元输出一组可以被称为第三特征图的特征图803。

93.级联器840将第二特征图802与第三特征图803级联,从而生成一组包含第二特征图804

‑

2和第三特征图804

‑

3的输出特征图804。第二特征图和第三特征图可以以任何顺序级联。例如,如图8所示,可将第三特征图放置在前面,将第二特征图放置在其后面,反之亦然。

94.尽管图8示出的级联,其中由增强单元输出的所有特征图804

‑

3保持在一起以及由二值化卷积单元输出的所有特征图804

‑

2保持在一起,但根据本公开的级联并非仅限于此。二值化卷积单元和增强单元的输出可以逐通道进行级联(即,逐特征图),而不是将每个单元的所有通道并在一起。因此,例如,级联器可以输出增强单元的第一输出通道,接着输出二值化卷积单元的第一输出通道,之后输出增强单元的第二输出通道,等等。可以将增强单元和二值化卷积单元的各个输出通道按任何顺序或组合进行级联,就像洗一副纸牌一样。在不同实施例中,可以随机地或根据预定方案来确定通道组合的顺序。

95.图9所示为增强二值化卷积模块800处于卷积模式用于实现卷积神经网络的卷积层时的操作示例。在本实施例中,设置卷积参数包括滤波器930和步幅,其中步幅在该示例中被设置为1。在此实施例中,增强操作是将缩放因子设置为1的缩放操作,因此增强操作复制输入特征图910。

96.为便于卷积操作,可以对输入特征图910进行填充。填充涉及在输入特征图910的外围添加额外单元以增加特征图的尺寸。例如,在图9中,输入特征图910原本尺寸为6

×

6,通过在外围添加值为1的单元,使得填充后的输入特征图920具有7

×

7的尺寸。在其他实施例中,可以通过添加值为0的单元进行填充。通过特征图填充增加了滤波器930可以在特征图上移动的范围,并且可以允许更准确的特征分类或提取。

97.然后,将填充后的输入特征图920与滤波器930进行卷积。由于特征图920和滤波器930都被二值化,所以卷积是二值化卷积。在卷积的每个步骤中,滤波器930在特征图920上每一步移动的单元数量与步幅相等,在图9所示的实施例中,该步幅设置为1。图9中的虚线示出了当滤波器在特征图920上移动时所进行的三步卷积操作。在卷积运算的每一步中,滤波器的每个单元的值与特征图的每个单元的相应值相乘,并将所有乘积结果相加,作为输出特征图940的单个单元的值。因此,卷积运算中的每一步将提供输出特征图940中单个单元的值。在一个实施例中,输入特征图910对应于图8的第一特征图801,输出特征图940对应于图8的第二特征图802。由于填充,滤波器930可以在特征图920上一共移动6步,因此在该实施例中,输出特征图940的尺寸为6

×

6,其与输入特征图的尺寸相同。

98.在图9所示的实施例中,由于缩放因子被设置为1,因此在操作过程中将输入特征

图910进行复制(例如,该复制的特征图对应于图8中的第三特征图803)。将复制的输入特征图910与输出特征图940进行级联950。相级联的特征图910、940对应于图8中的输出特征图804。

99.因此,可以理解的是,在一些实施例中,在卷积模式中,二值化卷积单元被配置为其输出特征图的尺寸与其输入特征图的尺寸相同。这可以通过选择适当尺寸的滤波器,选择适当步幅和/或对输入特征图进行适当填充来实现。在其他实施例中,卷积神经网络的构架可以包括卷积层,其输出特征图的尺寸小于其输入特征图的尺寸,在这种情况下,当实现此类层时,可将二值化卷积单元配置为输出小于其输入特征图的尺寸的特征图。

100.在降采样模式下,增强二值化卷积模块执行降采样操作,该操作减小了输入特征图的尺寸。常规的卷积神经网络使用最大池化或平均池化执行降采样。然而,如图10a所示,当对输入特征图进行二值化时,平均池化和最大池化可能导致信息丢失。例如,尽管图10a中的特征图1001和1002彼此不同,但是当对二者采用2x2单元的平均池化时,将产生0.5和1的输出值,如果将0.5的值舍入到最接近的二进制值,那么输出将是相同的。同时,特征图1003和1004很不同,但是当应用最大池化操作时,两者的输出值皆为1。

101.本发明的实施例通过对至少部分降采样的操作使用二值化卷积从而避免或减少信息丢失。图10b示出了一个示例,其中对输入特征图1010进行填充,并且将填充后的特征图1020与滤波器1030进行卷积以产生输出特征图1040,与图9所示的操作类似。滤波器可以被设置为针对降采样的滤波器,其与用于二值化卷积操作的滤波器可以相同或不同。可以将步幅设置为适用于降采样的值。在一些实施例中,可将步幅设置为等于或大于2的整数值。通常,步幅越大,输出特征图1040的尺寸就越小。

102.因此,当执行降采样操作时,二值化卷积单元可被配置为其输出特征图的尺寸小于其输入特征图的尺寸。输出特征图的大小取决于是否进行了填充,滤波器的尺寸以及步幅的大小。因此,通过选择合适的滤波器和步幅,二值化卷积单元可以被配置为其输出特征图的尺寸小于其输入特征图的尺寸。

103.在图10b所示的实施例中,增强操作是缩放操作,但缩放因子被设置为零的。这使得增强单元(也可以称为旁路单元)的输出为空。在这种情况下,由于输出包括二值化卷积单元输出的特征图1040而并没有来自增强单元的特征图,因此输出通道的数量将会减少。由此参照图8,在增强单元的输出为空输出的情况下,由增强二值化卷积模块输出的特征图804将仅包括第二特征图804

‑

2。

104.因此可以理解,在一些实施例中,当增强二值化卷积模块执行降采样操作时,增强单元可被配置为输出空输出至级联器。这将有助于减少从降采样层输出的输出通道的数量。

105.尽管图10b所示实施例中的增强单元在降采样模式下输出为空值,图10c示出了另一实施例,其中增强单元在降采样模式下输出实际值(即非空)。图10c中的二值化卷积单元的操作与图10b中的相同,并且相同的附图标记表示相同的特征,即,对输入特征图1010进行填充1020,并且与滤波器1030进行卷积以生成输出特征图1040。输出特征图1040可以对应于诸如图8中的输出特征图802。但是,与图10b不同的是,在图10c中,增强单元的输出与输出特征图1040级联1050。

106.增强单元可以执行任何增强操作,但是,为了说明的目的,在图10c的实施例中,增

强单元将执行与图9中类似的恒等操作。看待这点的一种方式是,在图10b中,增强单元执行的是缩放因子为0的缩放操作(输出空输出),而在图10c中,增强单元执行的是缩放因子为1的缩放操作(即恒等操作)。在一些其他实施例中,缩放系数在降采样模式下可以具有其他非零值。例如,在一些实施例中,降采样模式下的缩放因子可以大于0但小于1。

107.增强单元(亦可称为旁路单元)可以在将其输入到增强单元的特征图转发给级联器之前执行裁剪或采样操作以减小该特征图的大小。通过此方式,当执行降采样操作并且增强单元的输出不为空时,可以将增强特征图裁剪为与从二值化卷积单元输出的特征图1040相同的大小。例如,在图10c中,增强单元复制尺寸为6

×

6的输入特征图1010,但是将特征图裁剪为3

×

3,以使其与从二值化卷积单元输出的特征图1040具有相同的大小。以这种方式,从增强单元和二值化卷积单元输出的特征图具有相同的大小并且可以被级联。

108.可以理解,在图6、9、10b和10c的实施例中仅示出了一个输入特征图,而图8的实施例示出了多个输入特征图801。实际上,在许多情况下都是将多个特征图(也称为多个输入通道)输入至增强二值化卷积模块或共享逻辑模块。例如,卷积神经网络的输入可以包括二维图像的rgb值,其可以由三个输入特征图(即,三个输入通道,各用一个特征图表示红色,绿色和蓝色的值)表示。在某些情况中,卷积神经网络可以包括解码模块,其可以输出多个特征图至增强二值化卷积模块。此外,当实现卷积神经网络的降采样层中的卷积操作时,共享逻辑或增强二值化卷积模块的输出可以包括多个输出特征图(输出通道),这些输出特征图可以输入回共享逻辑模块或增强二值化卷积模块中,以实现卷积神经网络的下一层操作。

109.因此,尽管图6、9、10b和10c示出了单个输入特征图和二维滤波器,应当理解,当存在多个输入特征图时,滤波器可以具有与输入特征图数量相同的深度,并且滤波器可以一次应用于所有输入特征图。例如,如果有五个输入通道,则滤波器的深度可为五层,并且滤波器的每一层都具有相同的值(也称为激活或激活值)。因此,滤波器与从第一个输入通道到最后一个输入通道中的输入通道切片相重叠,并且点积的总和用于为输出通道提供激活。在卷积的每个步骤中,可以将每个输入通道与滤波器的点积相加,以产生输出通道的单个单元。因此,可以理解的是,不管输入通道(输入特征图)的数量如何,二值化卷积单元中的每个滤波器都生成单个输出通道(输出特征图)。因此,来自二值化卷积单元的输出通道的数量等于滤波器的数量。

110.来自增强单元的输出通道的数量取决于所执行的增强操作的数量。增强操作的数量可以由增强参数和/或来自控制器或控制接口的控制信号来控制。在一些实施例中,在卷积模式下,增强单元被配置为产生与二值化卷积单元的输出通道的数量相同的输出通道数量。例如,如果二值化卷积单元具有十个输出通道,则增强单元亦具有十个输出通道,这样,增强二值化卷积模块或者说共享逻辑模块将总共有二十个输出通道。

111.在一些实施例中,在降采样模式下,共享逻辑模块(例如,增强二值化卷积模块)被配置为其输出通道数量少于其输入通道数量。以这种方式,降采样层不仅可以减小输入特征图的尺寸,亦可以减小输出通道的数量。这将有助于防止卷积神经网络变得太大或太复杂。一种减少输出通道数量的方式是使增强单元的输出为空,例如,由于缩放因子为零。

112.因此,在一些实施例中,在降采样模式下,增强单元被配置为提供空输出,使得在降采样模式下共享逻辑模块的输出仅包括二值化卷积单元的输出。

113.在卷积神经网络中,二值化有时会导致数据丢失,从而引致更深层的运算结果逐渐趋向于零。在本公开的一些实施例中,在卷积模式下,可以通过将增强单元的输出与增强单元的输出进行级联从而将来自先前层的特征图的信息提供给卷积神经网络的后续层。这将有助于防止或减少此类信息的丢失。在一些实施例中,增强操作是一恒等操作。在其他实施例中,增强操作可以对输入特征图引入较小的修改(例如,通过缩放,旋转,翻转或镜像操作等),这可以帮助增强卷积神经网络在输入数据的较小变化时的不变性。

114.图11所示为实施例1100,其阐述了通过级联的方式如何使得信息能够被保留并通过卷积神经网络的一层或多层进行传播。

115.在方框1110中,将一组特征图输入到卷积神经网络。在此实施例中,输入特征图包括三个尺寸为32x32的通道,其在图11中表示为32x32x3。

116.在方框1120中,执行卷积操作,产生64个尺寸为32

×

32的输出通道。卷积操作可以由诸如解码模块执行。

117.在方框1130中,可以对卷积操作1120输出的特征图进行二值化。因为一共有64个特征图,并且它们的尺寸为32x32,可将这些特征图表示为32x32x64。这组特征图在图11中被称为

①

。这些特征图

①

可以输入到共享逻辑模块或增强二值化卷积模块。

118.在方框1140中,将来自方框1130的特征图

①

输入到增强二值化卷积模块的二值化卷积单元中,并使用8个尺寸为3x3的相异滤波器执行第一二值化卷积操作。该第一二值化卷积操作生成8个特征图(由于有8个滤波器),每个特征图的尺寸为32x32。

119.在方框1150中,二值化卷积单元输出由第一二值化卷积操作生成的8x32x32的特征图。这组特征图在图11中称为

②

。

120.在方框1160中,将来自第一二值化卷积操作的特征图

②

与输入到增强二值化卷积模块的特征图

①

相级联。例如,增强单元可以执行恒等操作,并将输入的特征图

①

转发到级联单元。然后,级联单元将特征图

①

与从二值化卷积单元输出的特征图

②

进行级联。级联的特征图在图11中被称为

③

,其包括72个通道(特征图),因为这是来自方框1130的64个特征图

①

和来自方框1150的8个特征图

②

的总和。级联特征图

③

具有尺寸32x32,因此在图11中被表示为32x32x72。之后,将级联特征图

③

输出到下一个处理阶段。例如,级联特征图

③

可以被再次输入回增强二值化卷积模块的二值化卷积单元和增强单元中。

121.在方框1170中,使用尺寸为3x3的8个不同的滤波器对特征图

③

执行第二二值化卷积操作。这8个滤波器可以与方框1140中使用的滤波器相同。因此,第一二值化卷积运算中的滤波器可以在第二二值化卷积运算中重复使用。因此,第二二值化卷积运算亦产生8个尺寸为32x32的输出特征图(因为有8个过滤器)。

122.在方框1180中,二值化卷积单元输出由第二二值化卷积运算产生的8个32x32的特征图(表示为32x32x8)。这组特征图在图11中称为

④

。

123.在方框1190中,将从第二二值化卷积操作输出的特征图

④

与在方框1160中输入到增强二值化卷积模块的特征图

③

进行级联。例如,增强单元可执行恒等操作并将输入特征图

③

转发至级联单元,之后级联单元可以将特征图

③

与特征图

④

级联。在图11中将级联的特征图

④

,

③

称为特征图

⑤

。因为特征图

⑤

是72个特征图

③

和8个特征图

④

的总和,因此有80个输出特征图

⑤

(即80条通道)。特征图

⑤

具有32

×

32的尺寸,因此在图11中表示为32

×

32

×

80。

124.至此,已经描述了两个增强二值化卷积操作。第一增强二值化卷积操作对应于方框1140至1160,第二增强二值化卷积操作对应于方框1170至1190。此后的增强二值化卷积操作可以由增强二值化卷积模块以相同的方式执行。在图11所示的实施例中,总共有八个这样的增强二值化卷积运算,而第三至第八个运算将由方框1190和方框1195之间的虚线表示。

125.方框1195所示为八次二值化卷积运算结束时的输出,为32x32x128,即128个输出特征图(通道),每个特征图具有32x32的尺寸。有128个输出通道是因为有经由级联转发的64个输入通道,以及经过方框1140、1160等中的第一至第八个二值化卷积运算生成的8x8=64个输出通道,得到总共64+64=128个输出通道。

126.每个二值化卷积运算都可以使用如方框1140和1170中使用的相同的一组8个滤波器。通过采用这种方式,节省存储资源,因为在执行64个二值化卷积运算并生成128个输出通道的操作过程中,仅需要在存储器中保存8个滤波器,因为这些过滤器在每个重复迭代中被反复使用。与此相异的,用于实现具有128个输出通道的卷积神经网络构架的常规卷积处理模块将需要存储128个滤波器的存储空间(每个输出通道对应一个滤波器)。

127.因此,可以理解,根据本发明的某些实施例,二值化卷积单元可被配置为将一连串n个滤波器应用x次以产生x*n个输出通道。在本文中,n是滤波器的数量(例如,在图11的实施例中为8),x是应用该连串滤波器的次数(例如,在图11的实施中为8次)。以这种方式重复使用同一连串过滤器可以大大减少实现卷积神经网络所需的内存。

128.将增强单元的输出与二值化卷积操作的输出相级联可以进一步增加输出通道的数量,同时亦不会显著增加所需的存储资源。此外,如上所述,增强单元和级联操作可以帮助避免或减少在二值化卷积神经网络中可能发生的信息丢失。

129.图12所示为根据本发明可以由方法、处理器或逻辑芯片实现的二值化卷积神经网络的构架示例1200。例如,图12的构架可以通过以上参考图1

‑

11所描述的本发明的任一实施例来实现。

130.如图12中第1210行所示,卷积神经网络接收32x32x3的输入,即3个尺寸为32x32的输入通道。

131.后续行对应于卷积神经网络的层,其中第一列表示该层的类型,第二列表示该层的输出尺寸,第三列表示由该层所执行的操作。每一层的输出形成下一层的输入。

132.因此,行1220显示卷积神经网络的第一层是卷积层,该卷积层接收32x32x3的输入(上一层的输出)并输出特征图32x32x64(即64个尺寸为32x32的输出通道)。例如,该层可以由诸如图3a所示的解码模块310a来实现。在一些实施例中,第一卷积层的输入1210可以没有被二值化,而第一卷积层1210的输出将被二值化。例如,解码模块可以在卷积操作之后应用二值化函数对输出特征图进行二值化操作。行1220可以由上述图11中的方框1110至1120实现。

133.行1230至1260对应于卷积神经网络的二值化卷积层和降采样层,其可以由诸如以上实施例所述的共享逻辑模块或增强二值化卷积模块来实现。

134.行1230对应增强卷积层。它通过将增强操作的输出与二值化卷积操作的输出进行组合(例如级联)来执行增强卷积操作。它将一连串8个尺寸为3

×

3的卷积滤波器应用于输入特征图,并将二值化卷积的输出与增强单元的输出级联。该操作被重复8次。增强卷积层

的输出为32x32x128。图12中的行1230可以由上述图11的方框1130至1195来实现。

135.行1240为降采样层。降采样层1240的输入是来自前一增强卷积层1230的32

×

32

×

128输出。在该实施例中,降采样层应用64个尺寸为3

×

3的滤波器,以生成16x16x64的输出。此操作由二值化卷积单元执行,称为降采样卷积。应当理解的是,在该实施例中,输出特征图的尺寸是输入特征图的尺寸的一半(从32

×

32减小到16

×

16)。在该实施例中,增强单元在实现降采样层时其输出为空。由于来自增强单元的输出为空,因此该层的输出仅包括二值化卷积操作所输出的64个通道。因此,与输入通道的数量相比,输出通道的数量减半(64个输出通道相较于128个输入通道)。

136.至此,已经描述了二值化卷积层的实施例和降采样层的实施例。卷积神经网络的构架中可能包括另外的二值化卷积层和降采样层。由参考数字1250所指的虚线用来表示根据卷积神经网络的期望特性来实现的这些另外的层的存在。

137.行1260对应于最终的增强卷积层。在该处,可以通过层1250之中的各种降采样层将输入特征图的尺寸减小到2

×

2。增强卷积层1260应用8个尺寸为3

×

3的滤波器来对输入进行二值化卷积并且重复该滤波器序列8次。输出的尺寸为2x2x128。

138.行1270对应于分类层。分类层可以由诸如图3a所示的全连接层模块360a来实现。在此实施例中,分类层包括具有512个输入节点(对应于上一层输出的2x2x128个节点)和10个输出节点的全连接神经网络。这10个输出节点对应于针对输入卷积神经网络的特征图1210的10种可能的分类。可能性分类的数量等于分类层的输出节点数。在其他实施例中,可存在更多或更少的可能性分类,于是全连接神经网络亦具有更多或更少的输出节点。

139.应当理解,图11所示的方法和图12所示的架构仅是示例。在其他实施例中,可能存在不同数量的层,不同数量,大小和顺序的过滤器,每个层具有不同的输出以及分类层具有不同数量的输入节点和输出节点。

140.还应当理解,二值化卷积的输出并不一定被二值化(例如,如图9所示),但可以经由激活二值化操作(例如,如图8所示)对其进行二值化处理。此外,可以将二值化激活功能集成到二值化卷积单元中。与此同时,增强操作的输出通常会进行二值化处理,这是因为在恒等操作中,特征图没有改变,在许多其他种类的增强操作中,值的位置变化到不同的单元,但单元值本身保持不变。然而,如果增强操作是缩放操作,并且缩放因子为非零值且不等于1,则增强操作的输出可以不被二值化。在那种情况下,可以通过二值化激活操作来对增强操作的输出进行二值化处理。

141.在调整滤波器权重(滤波器的激活值或滤波器值)的训练阶段中,可将激活值前向传播以计算针对训练数据的损失,之后将其反向传播以基于梯度下降来调整滤波器权重。在一些实施例中,前向传播的过程中可以使用二值化滤波器权重来计算针对训练数据的损失,而后向传播的过程中可以首先反向传播实际的非二值化梯度以调整原始滤波器的权重,然后在执行下一次迭代之前对调整后的滤波器权重进行二值化。在推理阶段,对滤波器权重以及二值化卷积和增强运算的输出进行二值化处理。

142.图13所示为根据本发明实施例的设计二值化卷积神经网络和用于实现二值化卷积神经网络的逻辑芯片的示例方法1300。

143.在方框1310中,获得原始数据以用作训练和验证数据。

144.在方框1320中,执行数据分析和预处理以将原始数据转换为适合用作训练和验证

的数据。例如,某些数据可能会被丢弃,某些数据可能会被过滤或细化。

145.在方框1330中,设计卷积神经网络的构架。例如,该构架可以包括多个卷积层和降采样层以及这些层的操作细节和输出,例如图12所示的实施例。

146.在方框1340中,使用训练数据训练设计好的卷积神经网络,以设置过滤器的激活权重,并在训练完成后,使用验证数据进行验证。该训练和验证操作可以在计算机服务器上执行,该服务器使用处理器可执行的机器可读指令模块来实现二值化卷积神经网络。也就是说,可以在软件中模拟多个卷积层和降采样层,以执行如上所述的示例中的共享逻辑模块或增强二值化卷积模块的操作。

147.如果在方框1340中的验证结果不够满意,则可以返回方框1330来调整或重新设计构架。如果结果令人满意,则训练阶段结束。在此种情况下,该方法将前进到方框1350对模型进行量化和压缩以便在硬件上实现该模型。在一个实施例中,这个处理模块可以被表示成一种适合于硬件逻辑门实现的形式,并且,可以将二值化激活操作和批量归一化操作与二值化卷积等操作集成到同一处理块中。

148.在方框1360中,在硬件上实现卷积神经网络。例如,可以在诸如fpga或asic是一个或多个逻辑芯片上实现卷积神经网络。一旦训练完成并且卷积神经网络的激活和设计业已设置好,逻辑芯片将用于推理阶段以实践应用卷积神经网络。

149.图14所示为由处理器对特征图进行分类的方法1400。特征图可以是诸如图像,音频,视频或其他类型的数据。在一些实施例中,图像可能是由实施了本方法的设备上的相机所捕获的。在其他实施例中,图像可能是被转换成可做卷积神经网络处理的图像格式的数据。

150.在方框1410中,处理器接收第一特征图,该第一特征图对应于要分类的图像。

151.在方框1420中,处理器接收第一组参数,该第一组参数包括至少一个滤波器,至少一个步幅和至少一个增强变量。

152.在方框1430中,处理器使用至少一个滤波器和至少一个步幅参数对输入特征图执行二值化卷积运算以产生第二特征图。

153.在方框1440中,处理器使用至少一个增强变量对输入特征图执行增强操作以产生第三特征图。

154.在方框1450中,处理器将第二特征图和第三特征图进行组合。

155.在方框1460中,处理器接收第二组参数,其包括至少一个滤波器,至少一个步幅和至少一个增强变量。

156.在方框1470中,使用第二组参数代替第一组参数并且使用组合的第二和第三特征图代替第一特征图,重复方框1330至1360的步骤。

157.第一组参数的值被选择用于实现二值化卷积神经网络的二值化卷积层,第二组参数的值被选择用于实施二值化卷积神经网络的降采样层。另外,亦可以将以上实施例的任何特征整合到上述方法中。

158.该方法可以由上述实施例所描述的任一处理器或逻辑芯片来实现。该方法可以在包括处理器的通用计算机或服务器或云计算服务上实现,或者可以在诸如asic或fpga等专用硬件逻辑芯片上实现。通过在逻辑芯片上实现该方法,使得在资源受限的设备上实现卷积神经网络成为可能,例如智能手机,相机,平板电脑或嵌入式设备,例如将用于实现卷积

神经网络的逻辑芯片嵌入到无人机,电子眼镜,汽车或其他车辆,手表或家用设备中等。

159.装置可以包括物理传感器以及用于实现如以上任何实施例中所述的卷积神经网络的处理器或逻辑芯片。例如,逻辑芯片可以是fpga或asic芯片,并且可以包括如以上任何实施例中所述的共享逻辑模块或增强二值化卷积模块。例如,该装置可以是便携式装置,包括但不限于,智能电话,平板电脑,照相机,无人机,手表,可穿戴装置等。物理传感器可被配置为收集物理数据。处理器或逻辑芯片可被配置为针对上述方法对数据进行分类。物理传感器例如可以是用于生成图像数据的照相机,处理器或逻辑芯片可以被配置为将图像数据转换为二值化特征图用于通过卷积神经网络进行分类。在其他实施例中,物理传感器可以收集诸如音频数据之类的其他类型的数据,其亦可被转换为二值化特征图并由处理器或逻辑芯片实现的卷积神经网络进行分类。

160.以上实施例仅通过示例的方式进行描述。在不脱离如所附权利要求中限定的本公开的范围的情况下,许多变化是可能的。

161.为了解释清楚,在一些情况下,本技术被呈现为包括单独的功能块,这些功能块包括包含设备、设备组件、以软件体现的方法中的步骤或例程的功能块,或者硬件和软件的组合。

162.根据上述示例的方法可以使用存储的或以其他方式从计算机可读介质可用的计算机可执行指令来实现。这样的指令可以包括例如指令和数据,其导致或配置通用计算机、专用计算机或专用处理设备以执行特定功能或功能组。使用的部分计算机资源可以通过网络访问。计算机可执行指令可以是例如二进制、中间格式指令,例如汇编语言、固件或源代码。可用于存储指令、使用的信息和/或在根据所描述的示例的方法期间创建的信息的计算机可读介质的示例包括只读存储器、随机存取存储器、磁盘或光盘、闪存等。

163.实现根据这些公开的方法的设备可以包括硬件、固件和/或软件,并且可以采用多种形式因素中的任一种。此类外形因素的典型示例包括膝上型电脑、智能手机、小型个人电脑、个人数字助理、逻辑芯片等。作为进一步的例子,这样的功能也可以在不同芯片或在单个设备中执行的不同过程之间的电路板上实现。

164.指令、用于传送此类指令的介质、用于执行它们的计算资源以及用于支持此类计算资源的其他结构是用于提供在这些公开中描述的功能的装置。

165.本说明书(包括任何所附权利要求、摘要和附图)中公开的所有特征和/或如此公开的任何方法或过程的所有步骤可以以任何组合方式组合,除非组合中至少有一些这些特征和/或步骤是相互排斥的。

166.除非另有明确说明,否则本说明书(包括任何随附的权利要求、摘要和附图)中公开的每个特征可以被用于相同、等同或相似目的的替代特征替换。因此,除非另有明确说明,所公开的每个特征仅是等同或相似特征的一般系列的一个示例。

167.尽管使用各种示例和其他信息来解释所附权利要求范围内的方面,但不应基于此类示例中的特定特征或布置来暗示对权利要求的限制,因为普通技术人员将能够使用这些例子来推导出各种各样的实现。此外,虽然一些主题可能已经以特定于结构特征和/或方法步骤的示例的语言进行了描述,但是应当理解,所附权利要求中定义的主题不一定限于这些描述的特征或动作。例如,这样的功能可以不同地分布或在不同于本文所标识的组件中执行。相反,所描述的特征和步骤被公开为所附权利要求范围内的系统和方法的组件的示例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1