一种256的制作方法

一种256

×

256交换矩阵的低时延监控装置及方法

技术领域

1.本发明涉及电子信息技术领域,具体地,涉及一种256

×

256交换矩阵的低时延监控装置及方法。

背景技术:

2.在卫星通信中,交换矩阵是信号在地面传输过程中处理信号分配与转发的至关重要的器件。它可以把来自不同线缆的不同信号路由至一个或多个设备以供处理或测试等操作,提高了信号路由的自动化,提高了信号传输过程中的效率。

3.通常,卫星信号以不同的频率和极化在卫星和地面站天线之间从太空传输到地球。卫星信号经过天线接收后将对其进行分离,并将信号馈送到低噪声下变频器,信号经过下变频后通常将变为l波段或扩展l波段。接下来变频后的信号将传输至集成接收解码器,将信号解码至基带,传输过程通常可用同轴线缆传输,常需与放大器结合补偿传输损耗或射频光纤转换后通过光纤传输。

4.为了在不同的设备之间分配、解码复用、传输和交换光纤上的rf信号,可以采用不同的方式。经典方式是“硬接线”,即将输入的rf信号通过线缆直接馈送至分路器上的光电转换器。由于分流会降低信号功率,故常结合集成的放大器;而另一种方式则是利用“交换矩阵”,这种方式显然更加灵活,可将输入源切换为任意数量的输出,反之亦然。在交换矩阵中,输入与输出接口越多,意味着监控链路越加繁杂,而监控响应速度往往决定了交换矩阵的切换时延,时延越低,实时性越高。常规交换矩阵中,监控方式常选用rs232、rs485、i

²

c或spi等串行通信,此类通信方式在小规模控制系统中,由于接口简单,被广泛使用,但弊端也同样明显。串行通信需将收发指令以双方约定速率逐位传递,通信时延受指令长度、ic运行速度、cpu处理速度影响,面对大规模交换矩阵时,时延被放大,拉低系统工作效率,使用体验下降。

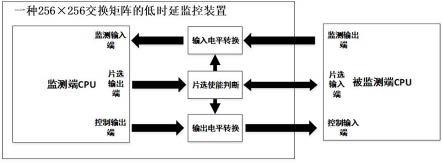

5.如图1,传统交换矩阵中的监控链路通常是以“监控端cpu+监控端通信ic”和“被监控端cpu+被监控端通信ic”组成,信号的传递伴随着cpu对指令的处理与通信ic收发模式的切换,当交换矩阵切换规模小时,时延带来的影响小,实时性高,例如4

×

8交换矩阵,共有32种端口切换组合,满载轮巡切换时间为“32

×

(cpu指令处理时延+cpu指令传输波特率

×

字节+通信ic使能时间+通信ic指令传输时延)”,信号在金属载体中传输速度约等于光速,时延忽略不计,cpu取128mhz高速时钟,传输波特率按常规值115200,字节数为8,通信ic使能时间约为7μs,通信ic指令传输时延约为0.5μs,综上,4

×

8交换矩阵满载轮巡切换时间约为18ms;256

×

256交换矩阵存在65536种端口切换组合,按4

×

8交换矩阵切换时间换算后得出其满载轮巡切换时间约为36.9s,严重影响系统工作效率和使用体验。

技术实现要素:

6.针对现有技术中存在的问题,本发明提供了一种256

×

256交换矩阵的低时延监控装置及方法,大幅度降低了交换矩阵监控时延,提升了系统工作效率,优化了交换矩阵监控

实时性。

7.为实现上述技术目的,本发明采用如下技术方案:一种256

×

256交换矩阵的低时延监控装置,所述256

×

256交换矩阵低时延监控装置包括:监测端cpu、输入电平转换电路、片选使能判断电路和输出电平转换电路,所述输入电平转换电路的输出端与监测端cpu的监测输入端连接,所述片选使能判断电路的输入端与监测端cpu的片选输出端连接,所述输出电平转换电路的输入端与监测端cpu的控制输出端连接;所述片选使能判断电路分别与输入电平转换电路、输出电平转换电路连接。

8.进一步地,所述256

×

256交换矩阵低时延监控装置与256

×

256交换矩阵连接,所述256

×

256交换矩阵、256

×

256交换矩阵低时延监控装置均与程控电源连接。

9.进一步地,所述256

×

256交换矩阵上设有被监测端cpu,所述被监测端cpu上设有监测输出端、片选输入端、控制输入端。

10.进一步地,所述被监测端cpu上的监测输出端与输入电平转换电路的输入端连接,所述输入电平转换电路通过门组合电路将被监测端cpu上的监测输出端的电平与监测端cpu的监测输入端的电路协调为同一层级。

11.进一步地,所述输入电平转换电路的输入端和输出端、被监测端cpu上的监测输出端、监测端cpu的监测输入端均为16位io并口。

12.进一步地,所述被监测端cpu上的片选输入端与片选使能判断电路的输出端连接,所述片选使能判断电路将监测端cpu的片选输出端的电平转换成与被监测端cpu上的片选输入端同层级的电平。

13.进一步地,所述片选使能判断电路的输入端和输出端、被监测端cpu上的片选输入端、监测端cpu的片选输出端均为10位io并口。

14.进一步地,所述被监测端cpu上的控制输入端与输出电平转换电路的输出端连接,所述输出电平转换电路通过与门组合电路将监测端cpu的控制输出端与被监测端cpu上的控制输入端的电平协调为同一层级。

15.进一步地,所述输出电平转换电路的输出端和输入端、被监测端cpu上的控制输入端、监测端cpu的控制输出端均为16位io并口。

16.本发明还提供了一种所述256

×

256交换矩阵的低时延监控装置的监控方法,包括如下步骤:(1)由监测端cpu的片选输出端发出片选信号;(2)被监测端cpu的片选输入端接收片选信号并通过“异或非门”和“与门”组合电路判断片选信号是否有效,当信号有效时,输出高电平片选使能通过信号给片选使能判断电路,表示片选使能判断通过;(3)片选使能判断通过后,输入电平转换电路和输出电平转换电路均开启电平数据监测;(4)电平数据监测完成时,监测端cpu的片选输出端输出低电平监控完成指示信号,关断片选使能判断电路的使能信号。

17.与现有技术相比,本发明具有如下有益效果: 本发明256

×

256交换矩阵的低时延监控装置省去了串行通信ic与其外围电路,以自研并发的256

×

256交换矩阵低时延监控装置替代,将传统监控流程中的“监控端cpu+监控端通信ic”与“被监控端cpu+被监控端通信

ic”变为“监控端cpu+被监控端cpu”,两端间的电平转换、片选、控制和监测等动作由io并口完成;且256

×

256交换矩阵的低时延监控装置中监测端cpu的监测输入端采用16路并发监控,将满载轮巡切换时间从36.9s缩短至528ms,极大降低了监控时延,提升了256

×

256交换矩阵系统工作效率,优化了交换矩阵监控实时性。

附图说明

18.图1是传统交换矩阵的监控方法原理示意图;图2是本发明256

×

256交换矩阵的低时延监控装置示意图;图3是本发明256

×

256交换矩阵的低时延监控装置的原理示意图。

具体实施方式

19.下面结合附图对本发明的技术方案作进一步地解释说明。

20.如图2是本发明256

×

256交换矩阵的低时延监控装置示意图,该256

×

256交换矩阵低时延监控装置与256

×

256交换矩阵连接,256

×

256交换矩阵采用与256

×

256交换矩阵低时延监控装置相同的监控接口,所有通道/板卡的监控电路均采用并联pin对pin方式;256

×

256交换矩阵、256

×

256交换矩阵低时延监控装置均与程控电源连接,程控电源用于为256

×

256交换矩阵低时延监控装置和256

×

256交换矩阵供电。该256

×

256交换矩阵的低时延监控装置将满载轮巡切换时间从36.9s缩短至528ms,极大降低了监控时延,提升了256

×

256交换矩阵系统工作效率,优化了交换矩阵监控实时性。

21.本发明中256

×

256交换矩阵低时延监控装置将监控与控制进行一体化设计,对外接口为2.54mm

×

50排线插座。该256

×

256交换矩阵低时延监控装置包括:监测端cpu、输入电平转换电路、片选使能判断电路和输出电平转换电路,监控端cpu的核心电路为dsp高速信号处理电路,负责发出片选信号、输出控制电平以及输入监测状态值,实现交换矩阵状态的及时更新;并发监控电路由监测端cpu的监测输入端、片选输出端、控制输出端组成,片选输出端由片选信号区分256

×

256交换矩阵的切换通道/板卡地址信息,控制输出端用于分时复用以实现并发控制所有通道/板卡状态,监测输入端用于分时复用以实现并发监测所有通道/板卡状态。输入电平转换电路的输出端与监测端cpu的监测输入端连接,片选使能判断电路的输入端与监测端cpu的片选输出端连接,输出电平转换电路的输入端与监测端cpu的控制输出端连接;片选使能判断电路分别与输入电平转换电路、输出电平转换电路连接。

22.本发明中256

×

256交换矩阵采用与256

×

256交换矩阵低时延监控装置相同的监控接口,所有通道/板卡的监控电路均采用并联pin对pin方式,因此,256

×

256交换矩阵上设有被监测端cpu,被监测端cpu上设有监测输出端、片选输入端、控制输入端。

23.本发明中输入电平转换电路的输入端与被监测端cpu上的监测输出端连接,输入电平转换电路通过门组合电路将被监测端cpu上的监测输出端的电平与监测端cpu的监测输入端的电路协调为同一层级;输入电平转换电路的输入端和输出端、被监测端cpu上的监测输出端、监测端cpu的监测输入端均为16位io并口,使得单次可同时读取16个端口状态且支持扩展。由于被监测端cpu与监测端cpu性能及功耗存在差异,所以芯片io的驱动能力与控制电平不同,故需要输入电平转换电路通过与门组合电路将监测输出端和监测输入端电

平协调为同一层级,从而保护双边io的同时增加输出端io驱动能力;需要注意的是,输入电平转换电路的功能开启存在前置条件,即片选使能判断通过。

24.本发明中输出电平转换电路的输出端与被监测端cpu上的控制输入端连接,输出电平转换电路通过与门组合电路将监测端cpu的控制输出端与被监测端cpu上的控制输入端的电平协调为同一层级;输出电平转换电路的输出端和输入端、被监测端cpu上的控制输入端、监测端cpu的控制输出端均为16位io并口,单次可同时控制16个端口且支持扩展。由于被监测端cpu与监测端cpu性能及功耗存在差异,所以芯片io的驱动能力与控制电平不同,故需要输出电平转换电路通过与门组合电路将控制输出和控制输入端电平协调为同一层级,保护双边io的同时增加输出端io驱动能力,需要注意的是,输出电平转换电路功能开启存在前置条件,即片选使能判断通过。

25.本发明中片选使能判断电路的输出端与被监测端cpu上的片选输入端连接,片选使能判断电路将监测端cpu的片选输出端的电平转换成与被监测端cpu上的片选输入端同层级的电平,从而保护双边io的同时增加片选输出端驱动能力。片选使能判断电路的输入端和输出端、被监测端cpu上的片选输入端、监测端cpu的片选输出端均为10位io并口,由于256

×

256交换矩阵由16个16

×

16板卡构成,所以共有2^8个输入地址,由该io并口完成,另2位分别为被监测端片选使能通过位和监测端数据监控完成指示位。当片选输出端给出片选信号时,片选输入端通过“异或非门”和“与门”组合电路判断片选信号是否有效,当信号有效时,输出高电平表示片选成功,此时片选使能判断通过,使得输入电平转换电路与输出电平转换电路开始工作。

26.本发明中256

×

256交换矩阵的低时延监控装置的监控方法包括如下步骤:(1)由监测端cpu的片选输出端发出片选信号;(2)被监测端cpu的片选输入端接收片选信号并通过“异或非门”和“与门”组合电路判断片选信号是否有效,当信号有效时,输出高电平片选使能通过信号给片选使能判断电路,表示片选使能判断通过;(3)片选使能判断通过后,输入电平转换电路和输出电平转换电路均开启电平数据监测;(4)电平数据监测完成时,监测端cpu的片选输出端输出低电平监控完成指示信号,关断片选使能判断电路的使能信号。

27.如图3,本发明256

×

256交换矩阵的低时延监控装置的监控流程为“监控端cpu+被监控端cpu”,两端间的电平转换、片选、控制和监测等动作由io并口完成,根据交换矩阵切换规模的差异,做出增减io并口与电路规模的调整即可,在交换矩阵产品种类中具有良好的异规模易调整性与适应性。且该256

×

256交换矩阵的低时延监控装置中监测端cpu的监测输入端,将满载轮巡切换时间从36.9s缩短至528ms,极大降低了监控时延,提升了256

×

256交换矩阵系统工作效率,优化了交换矩阵监控实时性。

28.以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1