一种面向互连裸芯与AXI主设备的转换接口及通信方法与流程

一种面向互连裸芯与axi主设备的转换接口及通信方法

技术领域

1.本发明涉及裸芯与axi主设备的接口通信技术,尤其是指一种面向互连裸芯与axi主设备的转换接口设计方法。

背景技术:

2.在单片专用集成电路中,所有组件都是在一个硅片上用同一种工艺设计和制造的。随着工艺尺寸的缩小,开发单片专用集成电路的成本和开发周期变得极高。在此情况下,多裸芯集成是未来开发高性能芯片的必然选择,即将多个功能各异且已通过验证、未被封装的芯片组件互连组装起来,并封装为同一管壳中的芯片整体,从而形成封装级网络nop(network on package),进而构建集成微系统。这些芯片组件被称为芯粒或裸芯(chiplet),其可以采用不同工艺、来自不同厂商,因此极大缩短和降低了开发周期和难度。而多裸芯集成的难点在于如何高效互连各个芯粒,并保证在功耗约束下实现较高的微系统性能。

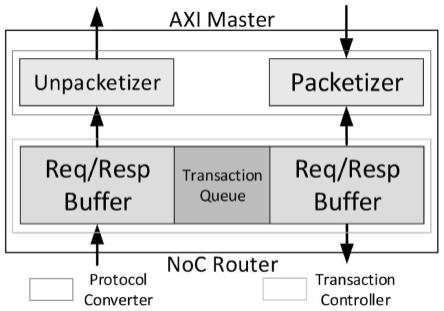

3.随着信息时代的到来,芯片计算和处理能力的市场需求大幅上升,各大厂商通过增加芯片中的处理器和各种功能单元(下文统一称为芯粒)的数量来提升芯片的计算和处理能力,从而导致单一芯片中芯粒的数量飞速增长。芯粒数量的大量增长使得传统总线式互连架构无法满足各芯粒间的高速通信任务,在这种情况下,片上网络noc(network on chip)应运而生。其脱胎于计算机网络,由一个个路由器构成,芯粒通过挂载于路由器与其他芯粒进行通信,具有传输带宽高、拓扑灵活多变以及扩展性强等特点。目前,noc理论已经得到充分研究和长足发展,随着系统级芯片的出现,片上和片间一体化网络的概念已经被提出并且在逐渐进行优化。

4.通过noc构建高速通信互连架构的关键在于提供面向多裸芯互连的标准通信协议与片上包传输协议的转换接口,在noc理论中,称其为网络接口ni(network interface)。芯粒因为功能以及制造厂商的不同,往往具有各种各样的通信接口协议,目前主流的标准通信协议有axi(advanced extensible interface)、pcie(peripheral component interconnect express)、rapid io以及ddr(double data rate)等。而noc是基于包传输协议的通信机制,因此ni的主要任务是完成片上包传输协议和标准通信协议之间的转换。另外目前片上系统soc(system onchip)一般采用全局异步局部同步的时钟布局,因而ni还需负责处理数据的跨时钟域传输。综上所述,在高性能信息处理微系统设计中需要研究具有不同类型接口的裸芯基于互连裸芯接口的扩展方法,以及外部裸芯与互连裸芯的通信过程。

技术实现要素:

5.为了保证soc中各裸芯间的高速通信,需要为不同的裸芯设计专有接口。本发明针对互连裸芯与axi主设备(裸芯)之间的扩展与通信问题,提出了一种面向高速可扩展互连裸芯与axi主设备的转换接口,解决了数据的包传输和传统的axi总线传输之间的转换问

题,实现了互连裸芯与axi主设备之间的高速通信问题。通过互连裸芯提供的axi主设备接口,可以高效地对兼容axi总线的mpu(microprocessor unit)等主设备处理器件进行快速的扩展与集成。

6.本发明本质即是面向axi主设备的ni设计,主要实现片上包传输协议(noc)和axi协议(axi主设备)之间的转换。互连裸芯面向axi主设备提供axi主设备ni,具体结构如图1所示,该接口负责连接axi主机和noc路由器(noc的基本组成单元),由协议转换器和事件控制器组成,前者中打包器(packetizer)负责数据包的生成、解包器(unpacketizer)负责数据包的解析,其分别是输入和输出两条数据通道的抽象,具体结构在图2中展示。事件控制器通过构建事件队列来对通过接口的事件进行管理,由发送缓冲区(transmit buffer)、接收缓冲区(receive buffer)和事件队列(transaction queue)组成。协议控制器除负责协议转换、数据包生成和解析工作外,在全局异步局部同步的时钟布局的soc中还负责解决数据的跨时钟域传输问题。在图1中协议控制器被抽象为打包器和解包器,但实际由shell、buffer和kernel三部分构成,如图2所示。其中,shell是一个本地总线协议控制器,按照对应功能单元所采用的总线协议进行数据的收发控制并进行必要的位宽转换,负责发送缓冲区的数据写入和接收缓冲区的数据读取。数据缓冲区buffer连接shell和kernel,由异步fifo构成,用来解决数据传输的跨时钟域问题,共有三个缓冲区,分别负责写请求、读请求和读响应通道的数据缓冲。kernel是整个接口的核心,分为打包器和解包器,打包器从发送缓冲区读取数据,按照noc传输协议的特定数据格式生成数据包;解包器将来自网络的数据包按照本地总线协议的格式进行解析,写入接收缓冲区。

7.由图3可知,事件控制器具体由请求和响应缓冲区、看门狗(watch dog)、id队列(id queue)和id生成器(id generator)组成。所谓id是事件的标记符,在网络传输中具有唯一性。当设备发出请求事件时,需要先进行id的生成然后挂起该id,确保在对应的响应事件返回之前不会被再次使用。而接收响应事件时只需要进行id释放即可。除此之外,还有负责进行超时报警的看门狗模块,当ni发出的请求事件在规定事件内未被响应时,则触发看门狗中断,将行为报告于处理器进行处理。

8.本发明的上述技术方案相比现有技术具有以下优点:本发明所述的面向高速可扩展互连裸芯与axi主设备的通信方法与接口设计方法为axi主设备提供了一种高效的转换接口,成功实现了axi协议与片上包传输协议之间的跨时钟域快速转换,互连裸芯面向axi主设备提供转换接口,可实现高性能微系统中axi主设备的快速扩展,能够承担axi主设备与互连裸芯间的高速通信任务,面向axi主设备的ni结构紧凑,采用模块化设计,各模块间独立设计、依赖程度低,整体扩展性高,能够快速继承新单元,从而实现更复杂的功能,面向axi主设备的片上网络接口的设计独立性以及紧凑的结构,保证了其良好的可移植性和可复用性,非常适合系统级芯片的模块化设计。

附图说明

9.为了使本发明的内容更容易被清楚的理解,下面根据本发明的具体实施例并结合附图,对本发明作进一步详细的说明。

10.图1是本发明所述axi主设备ni基本结构的框图;

11.图2是本发明所述协议转换器基本结构的框图;

12.图3是本发明所述事件控制器基本结构的框图;

13.图4是本发明所述协议转换器具体结构的流程框图;

14.图5是本发明所述事件控制器具体结构的流程框图。

具体实施方式

15.本方案中axi主设备ni面向axi协议进行设计,axi协议具有通道分离特性,共具有5个通道,分别是wac(写地址通道)、wdc(写数据通道)、wrc(写响应通道)、rac(读地址通道)和rdc(读数据通道)。wac、wdc和wrc服务于写事务,rac和rdc服务于读事务,其中写事务包括写请求和写响应,读事务包括读请求和读响应。

16.结合图4对axi主设备ni协议转换器作进一步介绍。由于axi将读写事件通道分离,为了保证读写分离这一特性,在axi主备ni中建立3条通道进行事件传输。写请求包含写地址和写数据,所以将wac和wdc中的信息合并存放在一个数据包中。在合并过程中,首先提取wac中的首地址、数据长度信息和wdc中的所有数据,然后依次放入体微片中(一个完整的noc传输数据包包括一个头微片、若干体微片和一个尾微片),一般首地址和数据长度放在第一个体微片,剩余体微片存放wdc的数据。为了避免mpu等待响应事件的返回从而降低系统性能,协议转换模块在一次burst传输(axi协议的一种传输模式)结束后通过写响应通道给mpu返回一次响应,真正的响应事件包则交由事件控制模块监控,这就是接口中有3条传输通道而不是4条的原因。读请求事件则只涉及rac一个通道,因此读请求数据包一般只有一个体微片,用来存放首地址和数据长度。读响应数据包则是负责传输读数据通道的信息,主要包含读取的数据,因此不能像写响应那样直接返回给mpu,而是一直等待响应数据包。

17.shell不仅仅是axi协议的数据收发控制器,还具备位宽转换的功能。紧跟着axi读写数据通道进行位宽转换,简化了kernel的设计复杂度。位宽转换分为两个部分:“窄到宽”和“宽到窄”,前者负责axi协议到片上包传输协议的转换,后者则相反。buffer由三个异步fifo构成,依次对应3条通道,分别负责写请求、读请求和读响应数据包的数据缓冲。异步fifo可以将一个时钟域的数据传输到另一个时钟域,在axi主设备ni中异步fifo两侧分别是mpu时钟域和noc时钟域,负责二者之间数据的跨时钟域传输。kernel由打包器和解包器构成,按照头、体尾的微片顺序进行数据包的打包和解包。所谓打包即是给已经具有数据包雏形的数据负载添加头尾微片以及微片格式(用于标记微片类型),解包则是将完整的数据包去掉微片格式和头尾微片,从中提取必要的控制信息和数据负载。上述过程由微片控制器全程控制,所谓微片控制器是一个状态机,其有三个状态分别对应处理头、体、尾微片。

18.需要注意的是,由于进入事件控制器后只有一个请求通道,而在协议控制器中请求通道是读写分离的,因此为了避免传输混乱,设计中加入了仲裁单元(arbiter)保证读写请求数据包先后有序地进入事件控制器。

19.图5所示是事件控制器的详细结构,一般情况下请求事件通过事件控制器时需要进行id的生成或挂起,当请求缓冲区非空时,首先查询是否有空闲id,如果所有id均被占用,则需要等待id释放,有空闲id则将该id挂起并打入数据包中,确保在对应的响应事件返回之前不会被再次使用。与此同时看门狗开始计时,若对应的响应未在规定时间内返回则触发中断,通知mpu进行处理。当响应缓冲区非空时,查询数据包包头指定位置的事件id信息,然后将id队列中相对应的id释放,接着数据包进入协议转换器,最终转换为响应通道总

线信号由axi主设备接收并处理。

20.对于请求事件来说,其首先由axi主机发起,经过axi请求通道的传输由shell单元接收并进行位宽转换,然后打入缓冲区(如果是写请求事件,此时由状态机控制写响应通道直接给主机返回写响应信号,避免等待而浪费时间)。此时kernel中的打包器检测到buffer非空,对应的打包器开始工作,为buffer中的数据添加头尾微片和微片格式,然后数据包进入事件控制器,id生成器为其生成id并挂起,最终数据包进入noc。响应事件的数据流向与请求事件相反,响应数据包首先出noc进入事件控制器,然后将数据包对应的事件id释放,接着数据包被送到协议转换器。协议转换器收到响应数据包之后,首先判断事件类型,若为读响应事件,则进行解包、位宽转换并返回给axi主机;若为写响应事件,则直接丢弃即可。以上所述数据流动过程是buffer非满、id有空闲的假设条件下的数据传输情况,若buffer已满或id均被占用,则整条数据链路停止传输,须等待下游数据链路再次通畅才可继续传输。

21.显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1