支持多卡并行的嵌入式智能计算装置

1.本发明涉及一种支持多卡并行的嵌入式智能计算系统设计方法及装置,属于计算机体系结构中嵌入式系统并行计算技术领域。

背景技术:

2.随着人工智能技术迅速发展,通过执行深度学习网络算法完成计算机视觉和自然语言处理大数据自动识别分析,实现数据处理智能化升级和有效利用,给诸如安防、人脸识别、物品检测、智能家居、智慧城市等应用领域带来了显著的经济效益和业务增长。而传统以cpu、fpga、dsp硬件计算架构为核心的数字信号处理平台在新型基于深度学习神经网络算法为代表的人工智能算法加速计算应用中面临着计算能力(以下简称算力)不足、计算效能比低、计算结果实时性无法满足等问题,为此新型人工智能专用加速处理器应运而生,比如寒武纪的mlu系列深度学习处理器、华为的昇腾系列深度学习处理器、瑞芯微rk3399系列等,但受限于单个芯片面积、功耗、成本等因素,单个智能处理器芯片集成的计算资源和计算能力有限,同时单块嵌入式计算系统板卡受限于pcb电路面积、功耗有限等苛刻约束条件,导致可集成的智能处理器芯片数量和提供系统级算力也有限,在处理大规模数据和复杂智能算法网络时,单卡形式的嵌入式智能计算系统装置仍存在计算能力不足、数据处理流程“端到端”时延无法满足实时性的问题。

技术实现要素:

3.为了克服上述问题,本发明的目的是提供一种支持多卡并行的嵌入式智能计算系统设计方法及装置,该方法采用高速rapidio分布式对等网络,并采用标准vpx嵌入式智能计算系统多卡并行计算、标准vpx fpga主控与io板卡、标准vpx rapidio网络交换板卡、标准vpx电源板卡、标准vpx背板,构建嵌入式智能计算系统多卡并行计算集群装置,在处理大规模数据和复杂智能算法网络时,通过该方法及装置不仅获得了系统级智能计算能力倍数增加和较好的算力可扩展性,同时通过采用rapidio网络交换板卡主、控与io板卡、多卡嵌入式智能计算板卡板间高速互联和并行计算设计,由rapidio总线完成板间高速数据传输与交换、fpga主要负责外部数据的接入与预处理、cpu主要负责高速ddr4缓存与拷贝、深度学习智能处理器主要负责高性能推理计算的并行异构计算架构,可实现大规模数据密集型计算密集型场景下图像/视频数据实时计算。

4.针对现有技术的不足,本发明提出一种支持多卡并行的嵌入式智能计算装置,其中包括多个嵌入式智能计算板卡、一个主控与io板卡和一个rapidio交换板卡;

5.该嵌入式智能计算板卡,采用嵌入式arm处理器和深度学习处理器的异构计算架构,集成rapidio转pcie的高速总线桥片模块;该嵌入式智能计算板卡通过该异构计算架构和该高速总线桥片模块,主要负责运行嵌入式linux操作系统、嵌入式智能算法应用程序和深度学习算法网络模型终端部署,实现高速rapidio总线图像/视频数据流的实时接收缓存和和基于卷积神经网络的深度学习算法的高性能推理加速计算;

6.该主控与io板卡,采用fpga和内存的设计架构,用于根据该设计架构提供fpga硬件逻辑编程和外部数据流缓存、预处理和推理计算任务的分发;fpga的io通信接口对外实现与图像/视频外部设备通信接口的接入,对内提供rapidio总线通信互联接口;

7.该rapidio交换板卡,用于提供多路rapidio总线通信端口和各端口内部mesh全连接交换网络,实现该主控及io单元板卡与所有该嵌入式智能计算板卡间点对点rapidio网络互联。

8.所述的支持多卡并行的嵌入式智能计算装置,其中包括电源板卡,用于为该嵌入式智能计算板卡、该主控及io板卡、该io交换板提供工作电源。

9.所述的支持多卡并行的嵌入式智能计算装置,其中采用插卡方式将所有该嵌入式智能计算板卡、该主控与io板卡、该rapidio交换板卡和该电源卡通过vpx连接器安装固定在vpx背板上。

10.所述的支持多卡并行的嵌入式智能计算装置,其中该嵌入式智能计算板卡包括该嵌入式arm处理器单元、该深度学习处理器、rapidio总线通信单元、电源模块、vpx连接器;

11.其中该嵌入式arm处理器单元为主控单元,采用pcie与该深度学习处理器、该高速rapidio总线通信单元互联,该嵌入式arm处理器单元作为pcie rc节点,该深度学习处理器单元和该高速rapidio总线通信单元均作为pcie endpoint节点;

12.该深度学习处理器则作为卷积神经网络推理加速专用部件,由专用深度学习智能处理芯片、ddr显存电路与pcie接口电路互联构成;

13.该高速rapidio总线通信单元,用于提供基于pcie总线arm处理器架构的嵌入式智能计算系统与rapidio交换板卡或其它rapidio功能板卡之间高带宽、低时延基于rapidio包交换的高速数据传输通道和rapidio网络系统级别互联功能,该高速rapidio总线通信单元采用rapidio-to-pcie桥片专用集成芯片,实现rapidio互联和rapidio总线协议转pcie总线协议的相互转换;

14.该电源模块与该vpx连接器上输入电源互联,提供该嵌入式智能计算板卡整板工作电源电压网络;

15.该vpx连接器,用于提供高速rapidio总线通信接口单元差分传输线与vpx背板互联和vpx供电输入,物理端口构成包括端口p0、端口p1、端口p2组成,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联,端口p2主要用于对外引出硬件调试通信接口。

16.所述的支持多卡并行的嵌入式智能计算装置,其中该主控与io板卡,包括fpga单元、ddr3内存单元、高速数据缓存、预处理与分发模块、硬件io可编程对外通信接口、高速rapidio总线通信互联单元、电源模块、vpx连接器;

17.其中该fpga单元用于对ddr3内存单元、对外通信硬件接口通信、rapidio总线的控制;

18.该数据缓存、预处理与分发模块,将数据缓存至该ddr3内存单元,并通过verilog/vhdl硬件编程语言完成数据预处理功能,进一步以异步的方式添加rapidio目的id等字段,将预处理后数据打包成rapidio nwrite报文,通过rapidio nwrite报文发送至该高速rapidio总线通信单元;

19.该硬件io可编程对外通信接口,用于fpga主控芯片与外部图像/视频设备间数据

通信;

20.该电源模块与该vpx连接器上输入电源互联,提供该主控与io板卡整板工作电源电压网络;

21.该vpx连接器,为该fpga单元提供高速rapidio总线传输线、对外硬件通信接口与vpx背板互联和供电输入,物理端口构成包括端口p0、端口p1、端口p2,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联、端口p2则用于对外引出硬件控制通信接口到vpx背板。

22.所述的支持多卡并行的嵌入式智能计算装置,其中该rapidio交换板卡,包括rapidio交换芯片、电源模块、vpx连接器;

23.其中该rapidio交换芯片,用于提供多路rapidio 4x模式数据通道和无阻塞交换机;

24.该电源模块与该vpx连接器上输入电源互联,提供该rapidio交换板卡整板工作电源电压网络;

25.该vpx连接器,提供多路rapidio交换芯片rapidio x4端口差分传输线与该vpx背板互联,并提供背板上电源板卡电流供电输入;该vpx连接器的端口包括端口p0、端口p1、端口p2,其中端口p0用于与该vpx背板电源输入相连,端口p1和端口p2均采用ansi/vita46标准4路rapidio x4数据通道信号定义,共设计8路rapidio x4数据通道,每路数据通道信号与交换芯片的一路rapidio x4数据通道信号点对点互联,并通过该vpx连接器与该vpx背板上交换槽位连接器互联,以实现该rapidio交换芯片多路rapidio 4x数据通道到vpx背板互联。

26.所述的支持多卡并行的嵌入式智能计算装置,其中该电源板卡,用于将输入的直流电源,经内部dcdc电路模块,电源输出指定直流电压,并将各电源与该vpx背板互联。

27.所述的支持多卡并行的嵌入式智能计算装置,其中该vpx背板,用于提供背板电源互联电路和rapidio网络互联电路;

28.该vpx背板采用多槽设计,分别为电源板卡槽位、rapidio交换板卡槽位、主控与io板卡槽位和多个嵌入式智能计算板卡槽位,其中该电源板卡槽位,用于通过连接器引出电源板上的输出引脚至背板,并通过背板电源互联电路,将电源板输出与各功能板卡电源输入互联;其它槽位以rapidio交换槽位为中心,采用全连接mesh网络,实现rapidio交换槽位、主控与io槽位以及嵌入式处理板槽位rapidio网络分布式对等互联。

29.本发明还提出了一种遥感图像探测设备,其采用所述任意一种支持多卡并行的嵌入式智能计算装置。该设备具有红外、可见光、sar一种或多种复合成像设备。

30.由以上方案可知,本发明的优点在于:

31.本发明提供了一种支持多卡并行的嵌入式智能计算系统设计方法及装置,该方法采用高速rapidio分布式对等网络,并采用标准vpx嵌入式智能计算系统多卡并行、标准vpx主控与io板卡、标准vpx rapidio网络交换板卡、vpx电源板卡、标准3u 6槽vpx背板,构建嵌入式智能计算系统多卡并行计算集群装置,可有效实现多个嵌入式智能计算系统板卡并行计算工作,达到系统级计算能力倍数增加和可扩展目的,同时通过采用rapidio网络交换板卡主、控与io板卡、多卡嵌入式智能计算板卡高速互联和板卡间并行计算设计,由rapidio总线完成板间高速数据传输与交换、由fpga主要负责外部数据的接入与预处理、由cpu主要

负责高速ddr4缓存与拷贝、由深度学习智能处理器主要负责高性能推理计算的并行异构计算架构,可实现大规模数据密集型计算密集型场景下图像/视频数据处理流程实时计算,克服了传统cpu、fpga、dsp架构数字信号处理平台和单个智能处理器芯片计算平台在大规模数据和复杂深度学习智能算法网络计算应用时面临着计算资源单一、计算能力不足、数据处理流程“端到端”时延无法满足实时性等问题,具有较好的实用推广前景。

附图说明

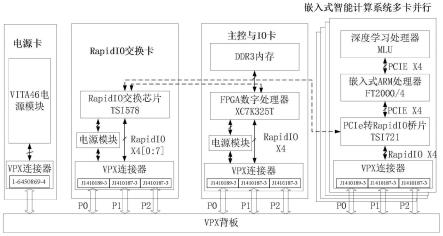

32.图1:嵌入式智能计算系统多卡并行计算装置互联框图;

33.图2:嵌入式智能计算系统多卡并行计算装置vpx背板槽位布局和互联框图。

具体实施方式

34.本发明解决其技术问题所采用的技术方案是:一种支持多卡并行的嵌入式智能计算系统设计方法及装置,其特征在于,系统由多个vpx嵌入式智能计算系统板卡、一个主控与io板卡、一个rapidio交换板、一个vpx电源板卡、一个vpx背板构成,具体实现方法包括如下步骤:

35.步骤1、嵌入式智能计算系统板卡设计,采用arm处理器+深度学习智能处理器嵌入式异构智能计算架构,系统组成包括嵌入式cpu处理器单元、深度学习智能处理器加速单元、高速rapidio总线通信单元、电源模块、vpx连接器等,其中嵌入式cpu处理器单元作为主控单元,主要负责搭载运行嵌入式linux操作系统、嵌入式智能算法应用程序以及和深度学习算法网络模型终端部署,完成rapidio总线板间高速互联和rapidio数据流高速接入与缓存、内部数据流分发与调度以及基于卷积神经网络的深度学习算法的高性能推理加速计算等功能,并与深度学习智能处理器单元、高速rapidio总线通信单元采用pcie总线互联,嵌入式cpu处理器单元作为pcie rc节点,深度学习智能处理器单元和高速rapidio总线通信接口单元均作为pcie endpoint节点;深度学习处理器单元则作为卷积神经网络推理加速专用部件,提供高效能比计算能力,由专用深度学习智能处理器芯片、ddr显存电路与pcie接口电路互联构成,与cpu主控单元采用pcie总线进行互联;高速rapidio总线通信接口单元主要是提供基于pcie总线arm处理器架构的嵌入式智能计算系统与rapidio交换板卡或其它rapidio功能板卡之间高带宽、低时延基于包交换的数据传输通道和rapidio网络系统级别互联功能,设计采用rapidio-to-pcie桥片专用集成芯片,实现rapidio互联和rapidio总线协议转pcie总线协议的相互转换;电源模块与板卡vpx连接器上输入电源互联,主要是输入vpx 12v、3.3v、5v电源,经内部dcdc电源模块电路,提供整板工作电源电压网络;标准vpx连接器接口电路,其功能主要是提供高速rapidio总线通信接口单元差分传输线与vpx背板互联和vpx供电输入,设计采用标准vita46规范的3u vpx连接器,物理端口构成包括端口p0、端口p1、端口p2组成,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联、端口p2主要用于对外引出硬件调试通信接口。

36.步骤2、主控与io板卡设计,用于提供硬件io可编程对外通信接口和高速rapidio总线内部通信互联接口,完成外部图像/视频设备数据采集、数据协议解析与缓存、数据预处理以及基于rapidio总线数据流分发至嵌入式智能计算系统计算功能。板卡设计采用fpga计算架构,功能组成包括fpga单元、ddr3内存单元、高速数据缓存、预处理与分发模块、

硬件io可编程对外通信接口、高速rapidio总线通信互联单元、电源模块、vpx连接器等,其中fpga作为核心,通过fpga verilog和ip core硬件编程,实现ddr3内存控制器、rapidio x4控制器、对外通信硬件接口通信(spi、can、cameralink等)、rapidio总线控制器等功能,进一步通过ddr3内存控制器实现fpga主控芯片对ddr3内存单元数据高速读写,通过rapidio控制器实现fpga主控芯片与rapidio交换板卡、其它rapidio功能板卡之间基于rapidio总线协议的数据传输通道和高速互联;通过数据缓存、预处理与分发模块,将数据采集模块输出数据缓存至ddr3内存单元,并通过verilog/vhdl硬件编程语言完成数据预处理过程,进一步以异步的方式添加rapidio目的id等字段,将预处理后的数据打包成rapidio nwrite报文,通过rapidio nwrite报文发送至rapidio交换;通过对硬件io可编程对外通信接口模块电气定义和verilog编程,实现fpga主控芯片与外部图像/视频设备之间数据通信;电源模块采用vpx连接器12v、3.3v、5v电源输入,经内部dcdc电源模块电路,提供fpga整板工作电源网络;标准vpx连接器接口电路,其功能主要是提供fpga主控芯片采用高速rapidio总线传输线、对外硬件通信接口与vpx背板互联和供电输入,设计采用标准vita46规范的3u vpx连接器,物理端口构成包括端口p0、端口p1、端口p2组成,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联、端口p2则用于引出对外硬件通信接口到vpx背板。

37.步骤3、rapidio交换板卡设计,用于对外提供多路rapidio通信端口和各端口全连接mesh交换rapidio网络,实现多个嵌入式智能计算系统板卡、主控及io单元板卡之间点对点rapidio网络高速互联。板卡组成主要包括rapidio交换芯片、电源模块、标准vpx连接器接口电路等,其中rapidio交换芯片作为核心模块,提供多路rapidio 4x模式数据通道和无阻塞交换(矩阵)机,支持1.25gbps、2.5gbps、3.125gbps的rapidio工作速率;电源模块主要是输入vpx 12v、3.3v、5v电源,经内部dcdc电源模块电路,输出整板工作电压电源网络;标准vpx连接器接口电路,其功能主要是提供多路rapidio交换芯片rapidio x4端口差分传输线与vpx背板互联,同时提供背板上电源板卡大电流供电输入;设计采用标准vita46规范的3u vpx连接器,物理端口构成包括端口p0、端口p1、端口p2组成,其中端口p0主要用于背板上12v、3.3v、5v电源输入,端口p1和端口p2均采用ansi/vita46标准4路rapidio x4数据通道信号定义,共设计8路rapidio x4数据通道,每路数据通道信号与交换芯片的一路rapidio x4数据通道信号点对点互联,并通过vpx连接器与背板上交换槽位连接器互联,进而实现rapidio交换芯片8路rapidio 4x数据通道到vpx背板互联。

38.步骤4、vpx电源板卡设计,用于为单机背板上嵌入式智能计算系统板卡、主控及io板卡、rapidio交换板提供工作电源。设计采用标准vita62成品电源模块,输入18vdc~36vdc电源,经内部dcdc电路模块,输出+12v、+3.3v、+5v,并通过标准vpx连接器接口电路与vpx背板互联。

39.步骤5、vpx背板设计,其功能是采用垂直插卡方式将所有功能板卡通过vpx连接器安装固定在vpx背板上,并提供背板电源互联电路和rapidio网络互联电路。背板采用标准vpx 3u 6槽设计,从左至右分别为1个电源槽(slot0)、1个rapidio交换板卡槽位(slot1)、1个主控与io单元(slot2)和4个嵌入式智能处理板槽位(slot3、slot4、slot5、slot6),其中背板上电源槽位,用于通过连接器引出电源板上的输出引脚至背板,并通过背板电源互联电路,将电源板输出与各功能板卡电源输入互联;其它槽位以rapidio交换槽位为中心,采

用全连接mesh网络,实现rapidio交换槽位、主控与io槽位以及嵌入式处理板槽位rapidio网络分布式对等互联。

40.为让本发明的上述特征和效果能阐述的更明确易懂,下文特举实施例,并配合说明书附图作详细说明如下。

41.如图1所示,一种支持多卡并行的嵌入式智能计算系统设计方法及装置由多个vpx嵌入式智能计算系统板卡、一个主控及io板卡、一个rapidio交换板、一个vpx电源板卡、一个vpx背板构成,具体实现方法包括如下步骤:

42.步骤1、嵌入式智能计算系统板卡设计,采用arm处理器+深度学习智能处理器嵌入式异构智能计算架构,系统组成包括嵌入式cpu处理器单元、深度学习智能处理器单元、高速rapidio总线通信单元、电源模块、vpx连接器等,其中嵌入式cpu处理器单元设计采用国产飞腾ft2000/4arm处理器,最小硬件外围子系统组成主要包括64位ddr4内存、micro tf卡flash存储、48mhz lvcmos时钟模块、rtl8211fs phy芯片+rj45构成的千兆网口模块和sp3232euart转rs232串口调试口模块等构成,并采用cpu处理器内置的2路pcie x16总线控制器分别与深度学习智能处理器单元、高速rapidio总线通信单元进行板内高速互联和数据交换,其中cpu处理器单元作为pcie rc节点,深度学习智能处理器单元和高速rapidio总线通信接口单元均作为pcie endpoint节点。深度学习处理器单元则作为卷积神经网络推理加速专用部件,设计采用寒武纪mlu系列深度学习智能处理器芯片、ddr显存电路与pcie接口电路互联构成,通过mlu深度学习处理器为处理人工智能任务时提供不低于10tops(mlu220,int8)的运算能力,mlu处理器通过pcie总线与cpu主控单元进行高速互联;高速rapidio总线通信接口单元设计采用idt公司rapidio-to-pcie桥片专用集成芯片tsi721,实现基于pcie总线arm处理器主控单元pcie总线协议转rapidio总线协议的桥接转换;电源模块设计采用ltm4644、ltm4647 dcdc电源模块电路,输入vpx连接器上定义的12v、3.3v、5v电源,输出整板工作电源电压网络;标准vpx连接器接口电路,设计采用1个tyco j1410189-3p0模块、1个j1410187-3p1模块、1个j1410187-3p2模块构成vpx连接器,通过模块引脚信号定义和电路互联,实现vpx供电输入和tsi721桥片高速rapidio总线通信接口差分传输线与vpx背板互联。

43.步骤2、主控与io板卡设计,采用fpga计算架构,系统组成包括fpga单元、ddr3内存单元高速数据缓存、预处理与分发模块、硬件io可编程对外通信接口、高速rapidio总线互联内部接口、电源模块、vpx连接器等,其中fpga设计采用xilinx公司xc7k325t,通过fpga verilog和ip core硬件编程,实现ddr3内存控制器、rapidio x4控制器、对外通信硬件接口通信(spi、can、cameralink等)、rapidio总线控制器等功能单元,其中通过ip core例化ddr3内存控制器实现fpga芯片对ddr3内存单元数据高速读写;通过ip core例化rapidio控制器实现fpga主控芯片与rapidio交换板卡、其它rapidio功能板卡之间高速rapidio总线数据传输通道和互联;通过数据缓存、预处理与分发模块,将采集的外部数据缓存至ddr3内存单元,并通过verilog/vhdl硬件编程语言完成数据预处理过程,并以异步的方式将预处理后的数据包打包成rapidio nwrite报文,添加rapidio目的id等字段信息,通过rapidio nwrite报文发送至rapidio交换;通过对硬件io可编程对外通信接口模块电气定义和verilog编程,实现fpga主控芯片与外部图像/视频设备之间数据通信;电源模块设计采用ltm4644、ltm4647 dcdc电源模块电路,输入vpx连接器上定义的12v、3.3v、5v电源,输出整

板工作电源电压网络;标准vpx连接器接口电路,设计采用1个tyco j1410189-3p0模块、1个j1410187-3p1模块、1个j1410187-3p2模块构成vpx连接器,通过模块引脚信号定义和电路互联,实现vpx供电输入和fpga高速rapidio总线通信接口差分传输线与vpx背板互联。

44.步骤3、rapidio交换板卡设计,采用rapidio交换芯片作为核心模块,系统组成包括rapidio交换芯片、电源模块、标准vpx连接器接口电路等,其中rapidio交换芯片采用idt tsi578,将芯片配置为8路rapidio 4x数据通道工作模式,每路rapidio 4x数据传输通道差分传输线均通过vpx连接器连接至vpx背板交换槽位,通过芯片内部交换电路寄存器配置,实现各端口全连接mesh交换rapidio网络功能;电源模块设计采用ltm4644、ltm4647 dcdc电源模块电路,输入vpx连接器上定义的12v、3.3v、5v电源,输出整板工作电源电压网络;标准vpx连接器接口电路,设计采用1个tyco j1410189-3p0模块、1个j1410187-3p1模块、1个j1410187-3p2模块构成vpx连接器,通过模块引脚信号定义和电路互联,实现vpx供电输入和8路rapidio 4x总线通信接口差分传输线与vpx背板互联。

45.步骤4、vpx电源板卡设计,采用基于vita62标准的成品电源模块,输入18vdc~36vdc电源,经内部dcdc电路模块,输出+12v、+3.3v、+5v,并通过标准vpx连接器接口电路与vpx背板互联。

46.步骤5、vpx背板设计,如图2所示,采用标准vpx 3u 6槽(slot)设计,从左至右分别为1个电源槽(slot0)、1个rapidio交换板槽位(slot1)、1个主控与io单元(slot2)和4个嵌入式智能处理板槽位(slot3、slot4、slot5、slot6),其中电源槽位连接器选用tyco 1-6450869-4型号,通过该连接器引出电源板上12vdc、5vdc、3.3vdc输出至背板,并通过背板内部电源互联电路,将电源板输出与各功能板卡vpx电源输入电气互联,其它功能槽位(slot1~slot6)连接器由tyco 1410186-1、1410140-1、1410142-1三个物理连接器型号构成,每个连接器遵循ansi/vita46端口信号定义,并通过背板rpaidio互联电路设计,实现以rapidio交换槽位为中心,rapidio交换槽位、主控与io单元槽位、嵌入式处理板槽位全连接mesh网络rapidio互联设计。

47.以下为与上述方法实施例对应的系统实施例,本实施方式可与上述实施方式互相配合实施。上述实施方式中提到的相关技术细节在本实施方式中依然有效,为了减少重复,这里不再赘述。相应地,本实施方式中提到的相关技术细节也可应用在上述实施方式中。

48.本发明还提出了一种支持多卡并行的嵌入式智能计算装置,其中包括多个嵌入式智能计算板卡、一个主控与io板卡和一个rapidio交换板卡;

49.该嵌入式智能计算板卡,采用嵌入式arm处理器和深度学习处理器的异构计算架构,集成rapidio转pcie的高速总线桥片模块;该嵌入式智能计算板卡通过该异构计算架构和该高速总线桥片模块,负责运行嵌入式linux操作系统、嵌入式智能算法应用程序和深度学习算法网络模型终端部署,实现高速rapidio总线图像/视频数据流的实时接收与缓存,和基于卷积神经网络的深度学习算法的高性能推理加速;

50.该主控与io板卡,采用fpga和ddr内存的设计架构,用于根据该设计架构提供fpga硬件逻辑编程和外部数据流缓存、数据预处理以及根据图像数据类型或帧号分发数据至各嵌入式智能计算板卡进行并行推理计算;fpga的io通信接口对外实现与外部诸如图像/视频等设备通信接口的接入,对内实现rapidio总线通信互联;其中外部指的是该嵌入式智能计算装置整体以外的设备。

51.该rapidio交换板卡,用于提供多路rapidio总线通信端口和各端口内部mesh全连接交换网络,实现该主控及io单元板卡与所有该嵌入式智能计算板卡间点对点rapidio网络互联。

52.所述的支持多卡并行的嵌入式智能计算装置,其中包括电源板卡,用于为该嵌入式智能计算板卡、该主控及io板卡、该io交换板提供工作电源。

53.所述的支持多卡并行的嵌入式智能计算装置,其中采用垂直插卡方式将所有该嵌入式智能计算板卡、该主控与io板卡、该rapidio交换板卡和该电源卡通过vpx连接器安装固定在vpx背板上。

54.所述的支持多卡并行的嵌入式智能计算装置,其中该嵌入式智能计算板卡包括该嵌入式arm处理器单元、该深度学习处理器、rapidio总线通信单元、电源模块、vpx连接器;

55.其中该嵌入式arm处理器单元为主控单元,采用pcie与该深度学习处理器、该高速rapidio总线通信单元互联,该嵌入式arm处理器单元作为pcie rc节点,该深度学习处理器单元和该高速rapidio总线通信单元均作为pcie endpoint节点;

56.该深度学习处理器则作为深度学习算法网络模型推理计算加速专用部件,由专用深度学习智能处理芯片、ddr显存电路与pcie接口电路互联构成;

57.该高速rapidio总线通信单元,用于提供基于pcie总线arm处理器架构的嵌入式智能计算系统与rapidio交换板卡或其它rapidio功能板卡之间高带宽、低时延基于rapidio包交换的高速数据传输通道和rapidio网络系统级别互联功能,该高速rapidio总线通信单元采用rapidio-to-pcie桥片专用集成芯片,实现rapidio互联和rapidio总线协议转pcie总线协议的相互转换;

58.该电源模块与该vpx连接器上输入电源互联,提供该嵌入式智能计算板卡整板工作电源电压网络;

59.该vpx连接器,用于提供高速rapidio总线通信接口单元差分传输线与vpx背板互联和vpx供电输入,物理端口构成包括端口p0、端口p1、端口p2组成,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联,端口p2则用于对外引出硬件调试通信接口到vpx背板。

60.所述的支持多卡并行的嵌入式智能计算装置,其中该主控与io板卡,包括fpga单元、ddr3内存单元、高速数据缓存、预处理与分发模块、硬件io可编程对外通信接口、高速rapidio总线通信互联单元、电源模块、vpx连接器;

61.其中该fpga单元用于对ddr3内存单元、对外通信硬件接口通信、rapidio总线的控制;

62.该数据缓存、预处理与分发模块,将数据缓存至该ddr3内存单元,并通过verilog/vhdl硬件编程语言完成数据预处理功能,进一步以异步的方式添加rapidio目的id字段,将预处理后的数据打包成rapidio nwrite报文,通过rapidio nwrite报文发送至该高速rapidio总线通信单元;

63.该硬件io可编程对外通信接口,用于fpga主控芯片与外部图像/视频设备间数据通信;

64.该电源模块与该vpx连接器上输入电源互联,提供该主控与io板卡整板工作电源电压网络;

65.该vpx连接器,为该fpga单元提供高速rapidio总线传输线、对外硬件通信接口与vpx背板互联和供电输入,物理端口构成包括端口p0、端口p1、端口p2,其中端口p0主要用于电源输入,端口p1主要用于rapidio x4高速信号互联、端口p2则用于引出对外硬件通信接口到vpx背板。

66.所述的支持多卡并行的嵌入式智能计算装置,其中该rapidio交换板卡,包括rapidio交换芯片、电源模块、vpx连接器;

67.其中该rapidio交换芯片,用于提供多路rapidio 4x模式数据通道和全双工通信、非阻塞、纵横交叉的内部交换结构,将包从输入端口传输到输出端口;

68.该电源模块与该vpx连接器上输入电源互联,提供该rapidio交换板卡整板工作电源电压网络;

69.该vpx连接器,提供多路rapidio x4端口差分传输线与该vpx背板互联,并提供背板上电源板卡供电输入;该vpx连接器的端口包括端口p0、端口p1、端口p2,其中端口p0用于与该vpx背板电源输入相连,端口p1和端口p2均采用ansi/vita46标准4路rapidio x4数据通道信号定义,共设计8路rapidio x4数据通道,每路数据通道信号与交换芯片的一路rapidio x4数据通道信号点对点互联,并通过该vpx连接器与该vpx背板上交换槽位连接器互联,以实现该rapidio交换芯片多路rapidio 4x数据通道到vpx背板互联。

70.所述的支持多卡并行的嵌入式智能计算装置,其中该电源板卡,用于将输入的直流电源,经内部dcdc电路模块,电源输出指定直流电压,并将各电源与该vpx背板互联。

71.所述的支持多卡并行的嵌入式智能计算装置,其中该vpx背板,用于提供背板电源互联电路和rapidio网络互联电路;

72.该vpx背板采用多槽设计,分别为电源板卡槽位、rapidio交换板卡槽位、主控与io板卡槽位和多个嵌入式智能计算板卡槽位,其中该电源板卡槽位,用于通过连接器引出电源板上的输出引脚至背板,并通过背板电源互联电路,将电源板输出与各功能板卡电源输入互联;其它槽位以rapidio交换槽位为中心,采用全连接mesh网络,实现rapidio交换槽位、主控与io槽位以及嵌入式处理板槽位rapidio网络分布式对等互联。

73.本发明还提出了一种遥感图像探测设备,其采用所述任意一种支持多卡并行的嵌入式智能计算装置;所述的遥感图像探测设备具有红外、可见光、sar一种或多种复合成像设备。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1