电容的静电放电失效电压模型的确定方法及装置与流程

1.本公开涉及静电放电技术领域,尤其涉及一种电容的静电放电失效电压模型的确定方法及装置。

背景技术:

2.目前,对元器件静电放电抗扰度试验已有了较为深入的研究,但由于esd(electrostatic discharge,静电放电)场的复杂性和esd试验标准的局限性,设计研制部门只能比较盲目地反复进行试探,来修改抗静电措施,以满足静电放电抗扰度的要求。

3.因此,有必要建立电容静电放电失效电压模型,为比较具体的抗静电设计提供理论依据。

技术实现要素:

4.本公开实施例提供一种电容的静电放电失效电压模型的确定方法及装置,以解决或缓解现有技术中的一项或更多项技术问题。

5.作为本公开实施例的第一个方面,本公开实施例提供一种电容的静电放电失效电压模型的确定方法,包括:

6.获取第一组电容的静电放电试验数据,静电放电试验数据包括电容的极板正对长度、电容的极板间隙以及电容的静电放电失效电压;

7.获取第一组电容的间隙击穿仿真数据,间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及电容的间隙击穿电压;

8.根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,间隙击穿电压模型为包括电容的间隙击穿电压、电容的极板正对长度和电容的极板间隙的关系式;

9.根据间隙击穿电压模型、静电放电失效电压基础模型和第一组电容的静电放电试验数据,确定静电放电失效电压模型,静电放电失效电压模型为包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙的关系式。

10.在一些可能的实现方式中,根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,包括:

11.根据帕邢定律和介电层缺陷密度理论,确定间隙击穿电压基础模型,间隙击穿电压基础模型为包括电容的间隙击穿电压、电容的极板正对长度、电容的极板间隙、第五参数、第六参数和第七参数的关系式;

12.根据间隙击穿仿真数据,对间隙击穿电压基础模型进行模型拟合,确定第五参数、第六参数和第七参数,以确定间隙击穿电压模型。

13.在一些可能的实现方式中,间隙击穿电压基础模型满足以下关系式:

14.15.其中,v0为电容的间隙击穿电压,d为电容的极板间隙,l为电容的极板正对长度,k3、e、α分别为第五参数、第六参数和第七参数。

16.在一些可能的实现方式中,

17.第五参数k3的数值范围为68~71;和/或,

18.第六参数e的数值范围为(-0.2)~(-0.4);和/或,

19.第七参数α的数值范围为(-0.104)~(-0.107)。

20.在一些可能的实现方式中,静电放电失效电压基础模型满足以下关系式:

[0021][0022]

其中,v

esd

为电容的静电放电失效电压,d为电容的极板间隙,l为电容的极板正对长度,v0为电容的间隙击穿电压,a、b、c、d分别为第一参数、第二参数、第三参数和第四参数。

[0023]

在一些可能的实现方式中,

[0024]

第一参数a的数值范围为0.42~0.62;和/或,

[0025]

第二参数b的数值范围为230~234;和/或,

[0026]

第三参数c的数值范围为20~21;和/或,

[0027]

第四参数d的数值范围为2~4。

[0028]

在一些可能的实现方式中,方法还包括:

[0029]

获取第二组电容的静电放电试验数据;

[0030]

根据间隙击穿电压模型、静电放电失效电压基础模型、第一组电容的静电放电试验数据和第二组电容的静电放电试验数据,确定修正后的静电放电失效电压模型,修正后的静电放电失效电压模型为包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙的关系式。

[0031]

在一些可能的实现方式中,

[0032]

第二组电容的静电放电试验数据中,电容的极板正对长度大于或等于30μm,电容的极板间隙大于或等于5μm;

[0033]

修正后的静电放电失效电压模型满足以下关系式:

[0034][0035]

其中,v

esd

为电容的静电放电失效电压,d为电容的极板间隙,l为电容的极板正对长度,v0为电容的间隙击穿电压,修正后的第一参数a1的数值范围为0.25~0.45,修正后的第二参数b1的数值范围为252~256,修正后的第三参数c1的数值范围为15~16.5,修正后的第四参数d1的数值范围为5~7.5。

[0036]

在一些可能的实现方式中,

[0037]

第二组电容的静电放电试验数据中,电容的极板正对长度小于或等于10μm;

[0038]

修正后的静电放电失效电压模型满足以下关系式:

[0039]

[0040]

其中,v

esd

为电容的静电放电失效电压,d为电容的极板间隙,l为电容的极板正对长度,v0为电容的间隙击穿电压,修正后的第一参数a2的数值范围为2.5~3.5,修正后的第二参数b2的数值范围为21.5~23,修正后的第三参数c2的数值范围为15~16,修正后的第四参数d2的数值范围为0.4~0.55。

[0041]

在一些可能的实现方式中,获取第一组电容的间隙击穿仿真数据,包括:

[0042]

建立静电放电模拟器模型、外接探针台等效电路模型和电容模型;

[0043]

将静电放电模拟器模型、外接探针台等效电路模型和电容模型连接,以建立电容静电放电仿真模型;

[0044]

对电容静电放电仿真模型进行仿真参数设置,以获得第一组电容的间隙击穿仿真数据,第一组电容的间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及相对应的电容的间隙击穿电压。

[0045]

在一些可能的实现方式中,电容为t型平板电容。

[0046]

作为本公开实施例的第二方面,本公开实施例提供一种电容的静电放电失效电压模型的确定装置,包括:

[0047]

第一获取模块,用于获取第一组电容的静电放电试验数据,静电放电试验数据包括电容的极板正对长度、电容的极板间隙以及电容的静电放电失效电压;

[0048]

第二获取模块,用于获取第一组电容的间隙击穿仿真数据,间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及电容的间隙击穿电压;

[0049]

第一确定模块,用于根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,间隙击穿电压模型为包括电容的间隙击穿电压、电容的极板正对长度和电容的极板间隙的关系式;

[0050]

第二确定模块,用于根据间隙击穿电压模型、静电放电失效电压基础模型和第一组电容的静电放电试验数据,确定静电放电失效电压模型,静电放电失效电压模型为包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙的关系式。

[0051]

作为本公开实施例的第三方面,本公开实施例提供一种电子设备,包括:

[0052]

至少一个处理器;以及

[0053]

与至少一个处理器通信连接的存储器;其中,

[0054]

存储器存储有可被至少一个处理器执行的指令,指令被至少一个处理器执行,以使至少一个处理器能够执行本公开任一实施例中的方法。

[0055]

作为本公开实施例的第二方面,本公开实施例提供一种存储有计算机指令的非瞬时计算机可读存储介质,其中,计算机指令用于使计算机执行根据本公开任一实施例中的方法。

[0056]

本公开实施例确定出的静电放电失效电压模型,可以为抗静电定量化设计提供理论依据,可以为实现特殊形状布线的抗静电定量化设计提供理论依据,使得抗静电设计不再仅停留在定性试验阶段,避免了通过盲目改变设计来修改抗静电措施,提高了抗静电设计的准确度和效率。

[0057]

上述概述仅仅是为了说明书的目的,并不意图以任何方式进行限制。除上述描述的示意性的方面、实施方式和特征之外,通过参考附图和以下的详细描述,本公开进一步的方面、实施方式和特征将会是容易明白的。

附图说明

[0058]

在附图中,除非另外规定,否则贯穿多个附图相同的附图标记表示相同或相似的部件或元素。这些附图不一定是按照比例绘制的。应该理解,这些附图仅描绘了根据本公开的一些实施方式,而不应将其视为是对本公开范围的限制。

[0059]

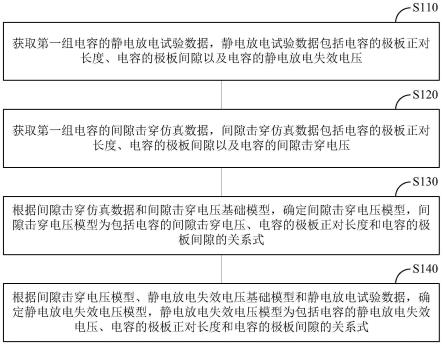

图1为本公开一实施例中电容的静电放电失效电压模型的确定方法的示意图;

[0060]

图2为本公开一实施例中电容的结构示意图;

[0061]

图3为本公开一实施例中电容的击穿失效示意图;

[0062]

图4a为击穿电压最接近失效电压情况下的失效示意图;

[0063]

图4b为击穿电压略微大于失效电压情况下的失效示意图;

[0064]

图4c为击穿电压远大于失效电压情况下的失效示意图;

[0065]

图5为人体放电模型的设备放电等效电路图;

[0066]

图6为一个实施例中静电放电模拟器实体模型的示意图;

[0067]

图7为一个实施例中静电放电模拟器集总电路元件的示意图;

[0068]

图8为一个实施例中激励电压波形的示意图;

[0069]

图9为静电放电模拟器短接输出波形的示意图(1kv电压);

[0070]

图10为静电放电模拟器500ω负载输出波形的示意图(1kv电压);

[0071]

图11一个实施例中为外接探针台等效电路模型示意图;

[0072]

图12为一个实施例中的t形平板电容几何模型;

[0073]

图13为一个实施例中的探针放电端口示意图;

[0074]

图14为一个实施例中t形平板电容静电放电仿真模型;

[0075]

图15为一个实施例中离散端口电路连接示意图;

[0076]

图16为一个实施例中v0=f(d,l)间隙击穿电压模型拟合图;

[0077]

图17为一个实施例中v

esd

=g(d,l)静电放电失效电压模型拟合图;

[0078]

图18为本公开一实施例中修正后v

esd

=g1(d,l)静电放电失效电压模型拟合图(l≥30μm);

[0079]

图19为l=45μm时采用本公开一实施例的模型预测静电放电失效电压的示意图;

[0080]

图20为本公开一实施例中修正后vesd=g2(d,l)静电放电失效电压模型拟合图(l≤10μm);

[0081]

图21为本公开一实施例中电容的静电放电失效电压模型的确定装置的结构框图。

具体实施方式

[0082]

在下文中,仅简单地描述了某些示例性实施例。正如本领域技术人员可认识到的那样,在不脱离本公开的精神或范围的情况下,可通过各种不同方式修改所描述的实施例,不同的实施例在不冲突的情况下可以任意结合。因此,附图和描述被认为本质上是示例性的而非限制性的。

[0083]

首先对本公开涉及的几个名词进行介绍和解释:

[0084]

goa:阵列基板栅极驱动技术(gate driver on array,goa);

[0085]

tft-lcd:薄膜晶体管液晶显示器;

[0086]

esd:静电放电(electrostatic discharge);

[0087]

pad:焊盘,在本文指代静电放电试验中用于探针扎针的区域。

[0088]

本公开的发明人经研究发现,薄膜晶体管液晶显示器(tft-lcd)除了面板与背光源系统以外,tft-lcd的驱动系统包括三个模块:扫描驱动电路、数据驱动电路和公共电压(vcom)模块。阵列基板栅极驱动(gate driver on array,goa)技术是将液晶显示(lcd)面板的栅极驱动器集成在玻璃基板上,代替外接的栅极集成电路(ic)芯片,在基板上形成对面板的扫描驱动,减少了栅极驱动ic的使用量,降低了功耗和成本。goa技术是lcd屏幕中的重要组成部分,对lcd产品的可靠性产生关键影响。

[0089]

静电放电(esd)是困扰许多电子产品的一个严重问题,但在goa技术的发展过程中,大多研究主要集在驱动电路方面,研究提高驱动能力和减小功耗之间的平衡,来解决大尺寸与高分辨率应用方面的问题。但针对goa产品的静电放电失效研究大多集中在如何减小工艺过程中的静电产生,如何通过改进设计提高goa产品的抗静电能力属于亟待解决的瓶颈问题。

[0090]

tft-lcd基板生产中的接触、摩擦、挤压、分离等工艺过程都容易产生静电,且玻璃基板本身是绝缘材料,静电散逸的速度很慢。并且,随着电路规模的扩大、电路特征尺寸的缩小,以及用户对高分辨率和小型化的同时追求,导致goa区域的布线密度高,布线间距及尺寸都不断减小。这就使得在goa布线区域容易发生静电击穿失效,造成线路损坏,因此,goa作为tft-lcd产品的重要组成成分,其抗静电能力将直接影响到整个液晶显示系统的可靠性。针对布线静电失效的研究较少,目前有些文献讨论了以两条栅极测试线为对比,发现在微电子器件的电路中,相同的覆盖形状和相同的测试线宽度,线越长,越容易发生静电放电。当长线长度比短线长度大14%时,静电放电主要发生在长线上,可以指导电路设计如何避免静电放电,特别是通过缩短功能线或增加更长的虚拟线来避免静电放电。

[0091]

生产实践过程中又发现t形布线结构相比其余并排布线结构更容易发生静电放电失效,因此有必要对goa产品t形布线的静电放电失效影响因素开展深入研究,t形布线结构可以看做t形平板电容结构。

[0092]

本公开的发明人经过进一步研究发现,针对goa产品t形布线静电放电失效的研究大多停留在生产设备、工艺流程改进或简单地添加绝缘层达到防止制造过程中静电放电的产生,只有少数考虑到了采取结构设计的方法来提高产品抗静电放电能力。本公开着眼于通过布线设计来改变产品的抗静电能力。现在已经开展了大量的静电放电试验,但试验标准一直没有更新,静电放电试验仍然停留在定性试验的阶段,而本公开能得到试验样件定量的静电放电失效电压。在静电放电仿真技术研究方面,大量的研究集中在建立系统级和器件级的电路仿真模型,而本公开针对更小结构的静电放电仿真开展研究,建立针对布线结构的仿真模型。现有技术由于缺少结构相关的布线静电放电失效电压模型研究,产品设计者和研制部门只能比较盲目地改变设计反复进行静电放电试验的试探,来修改抗静电措施,以满足静电放电抗扰度的要求。

[0093]

相关技术对元器件静电放电的抗扰度试验,由于esd场的复杂性和esd试验标准的局限性,只能比较盲目地反复进行试探,来修改抗静电措施,以满足静电放电抗扰度的要求。因此,需进一步建立定量的电容静电放电失效电压模型,为给出比较具体的抗静电设计提供理论依据。

[0094]

图1为本公开一实施例中电容的静电放电失效电压模型的确定方法的示意图。如

图1所示,电容的静电放电失效电压模型的确定方法,可以包括:

[0095]

s110、获取第一组电容的静电放电试验数据,静电放电试验数据包括电容的极板正对长度、电容的极板间隙以及电容的静电放电失效电压;

[0096]

s120、获取第一组电容的间隙击穿仿真数据,间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及电容的间隙击穿电压;

[0097]

s130、根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,间隙击穿电压模型为包括电容的间隙击穿电压、电容的极板正对长度和电容的极板间隙的关系式;

[0098]

s140、根据间隙击穿电压模型、静电放电失效电压基础模型和静电放电试验数据,确定静电放电失效电压模型,静电放电失效电压模型为包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙的关系式。

[0099]

示例性地,静电放电试验数据可以通过试验的方法获取。

[0100]

示例性地,间隙击穿仿真数据可以通过模型仿真的方法获取。

[0101]

本公开实施例的技术方案,根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,根据间隙击穿电压模型、静电放电失效电压基础模型和静电放电试验数据,确定静电放电失效电压模型。在确定静电放电失效电压模型的过程中,采用了第一组电容的间隙击穿仿真数据和静电放电试验数据,相比于只采用静电放电试验数据,可以避免试验过程中外接电路的寄生阻容感对波形的影响,提高确定出的静电放电失效电压模型的准确度。

[0102]

本公开实施例确定出的静电放电失效电压模型,可以为抗静电定量化设计提供理论依据,可以为实现特殊形状布线的抗静电定量化设计提供理论依据,使得抗静电设计不再仅停留在定性试验阶段,避免了通过盲目改变设计来修改抗静电措施,提高了抗静电设计的准确度和效率。

[0103]

示例性地,电容可以为t形平板电容。t形布线结构相比于并排布线结构更容易发生静电放电失效,因此,将电容设置为t形平板电容,便可以得到t形平板电容的静电放电失效电压模型,可以为t形布线结构的设计提供定量化理论依据。

[0104]

在一种实施方式中,获取第一组电容的静电放电试验数据,可以包括,获取第一组t形平板电容的静电放电试验数据。该步骤可以包括如下过程:针对第一组t形平板电容静电放电失效电压关键影响因素进行静电放电试验样件设计;制定静电放电试验方案,确定t形平板电容静电放电失效判断依据;对试验样品进行静电放电试验,记录不同结构的t形平板电容静电放电失效电压,得到t形平板电容随结构变化的失效电压数据。然后,对试验的结果进行分析,对得到的试验数据进行无效数据的排除。下面结合具体实施例对该步骤进行详细说明。

[0105]

一、试验样件设计

[0106]

设计制作试验样件,包括基板选择、加电pad设计、t形平板电容结构设计等。结构设计中需考虑设计不同关键影响因素的正交组合试验,并通过结构的设计排除干扰因素。制作的样件结构如图2所示,图2为本公开一实施例中电容的结构示意图。

[0107]

如图2所示,电容包括第一金属线结构210和第二金属线结构220。第一金属线结构210和第二金属线结构220呈t形排布,分别为电容的两个极板。示例性地,第一金属线结构

210包括第一部分211和第二部分212。第二金属线结构220包括第三部分221、第四部分222和第五部分223。

[0108]

参见图2所示,第一方向x和第二方向y垂直,第一金属线结构210沿第二方向y设置,第二金属线结构220沿第一方向x设置。w1为第二部分212在第二方向y上的尺寸,w2为第三部分221在第一方向x上的尺寸,w3为第三部分221和第四部分222在第一方向x上的尺寸,极板间隙d为第二部分212和第三部分221之间的间隙尺寸,l1为第二部分212在第一方向x上的尺寸,极板正对长度l为第三部分221在第二方向y上的尺寸,l3为第四部分222在第二方向y上的尺寸。

[0109]

示例性地,极板间隙d和极板正对长度l为同一基板100上可发生变化的尺寸参数,基板100可选用玻璃基板,pad的尺寸可选用200μm(微米)*200μm。

[0110]

示例性地,t形平板电容的结构参数可以如表1所示。在表1中,极板间隙d和极板正对长度l分别有四个不同的数值。

[0111]

表1t形平板电容几何模型参数

[0112][0113]

二、试验方案制定

[0114]

进行试验方案制定,需要准备上述样件组至少十个,准备好的样件组可以称之为第一组电容。选择静电放电电压范围适合的设备,通过减振、降噪手段排除环境干扰,通过屏蔽线将干扰信号接地,并考虑每次放电后电容累积电荷的释放。通过缩小施加电压间隔及多次试验,在电容t形结构处出现缺口或发生布线熔断时记录静电放电失效时的电压大小,得到多组较为精准的失效电压数据。试验设备包括(a)探针台、(b)hed-n5000 esd抗静电测试仪、(c)pc机。探针台用于给样件加电,抗静电测试仪为静电发生源,pc机用于控制测试仪及观察t形平板电容失效情况。

[0115]

三、试验开展

[0116]

首先将探针台与放电设备用同轴电缆连接,调整探针使探针扎到t形电容两端的pad处。然后对静电放电仪器所使用的软件进行参数设置,设置输入输出管脚、放电模型为hbm模型,放电形式为+,放电间隔为1s,放电次数为1次,每次放电后自动放出残余电荷,其余参数根据试验设备相关要求进行设定。最后设置初始电压值,步进为5v,通过显微镜的相机观察t形电容,直到出现击穿失效现象,如图3所示,图3为本公开一实施例中电容的击穿失效示意图,记录此时的电压值,得到处理前的静电放电试验数据。

[0117]

需要说明的是,在试验开展中,放电间隔时间、放电次数和电压步进值均可以根据需要设置,不限于上文中列出的具体数值。

[0118]

四、试验结果分析

[0119]

由于试验环境还存在一些误差干扰及样件本身不一致性的原因,同一结构样件的失效电压也有所不同。试验过程中观察到了不同程度的失效,如图4a、图4b和图4c所示。图4a为击穿电压最接近失效电压情况下的失效示意图,图4b为击穿电压略微大于失效电压情况下的失效示意图,图4c为击穿电压远大于失效电压情况下的失效示意图。如图4a所示,在

击穿电压最接近失效电压的情况下,失效只发生在导线汇集处。如图4b所示,在击穿电压略微大于失效电压的情况下,横向导线也出现轻微烧毁。如图4c所示,在击穿电压过高,远大于失效电压的情况下,横向导线全部熔毁,甚至部分出现纵向导线的熔毁。

[0120]

五、静电放电试验数据处理

[0121]

对试验开展中获取到的处理前的静电放电试验数据进行预处理,分析试验环境干扰的影响,对异常数据及无效数据进行清除。一般来说,如果一个量是由许多微小的独立随机因素影响的结果,那么就可以认为这个量具有正态分布,故采用正态分布拟合的方法对每个试验点的无效数据进行排除。在minitab中导入数据后选择正态分布拟合,去除无效数据后使得拟合出的正态分布曲线标准差尽可能的小的同时p值尽可能大,p>0.05时则判断数据服从正态分布,p值越大数据越服从正态分布。最后得到处理后的数据结果如表2所示,表2所示数据可以为一个实施例中的第一组电容的静电放电试验数据。

[0122]

表2 t形平板电容静电放电试验数据

[0123][0124][0125]

表2中,a31指l=30μm、d=10μm的t形平板电容;a32指l=30μm、d=15μm的t形平板电容;a33指l=30μm、d=20μm的t形平板电容;a34指l=30μm、d=25μm的t形平板电容;

[0126]

a41指l=42.5μm、d=10μm的t形平板电容;a42指l=42.5μm、d=15μm的t形平板电容;a43指l=42.5μm、d=20μm的t形平板电容;a44指l=42.5μm、d=25μm的t形平板电容;

[0127]

a51指l=53μm、d=10μm的t形平板电容;a52指l=53μm、d=15μm的t形平板电容;a53指l=53μm、d=20μm的t形平板电容;a54指l=53μm、d=25μm的t形平板电容;

[0128]

a61指l=64μm、d=10μm的t形平板电容;a62指l=64μm、d=15μm的t形平板电容;a63指l=64μm、d=20μm的t形平板电容;a64指l=64μm、d=25μm的t形平板电容。

[0129]

从表2中可以看出,静电放电试验数据包括电容的极板正对长度l、电容的极板间

隙d以及电容的静电放电失效电压v

esd

。对于每一个样件编号的t形平板电容,获取10个静电放电失效电压v

esd

。表2中的均值为对应的t形平板电容的多个静电放电失效电压有效数据的正态分布均值。

[0130]

在一种实施方式中,获取第一组电容的间隙击穿仿真数据,可以包括:获取第一组t形平板电容的间隙击穿仿真数据。

[0131]

示例性地,获取第一组电容的间隙击穿仿真数据,该步骤可以包括:建立静电放电模拟器模型、外接探针台等效电路模型和电容模型;将静电放电模拟器模型、外接探针台等效电路模型和电容模型连接,以建立电容静电放电仿真模型;对电容静电放电仿真模型进行仿真参数设置,以获得第一组电容的间隙击穿仿真数据,第一组电容的间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及相对应的电容的间隙击穿电压。

[0132]

需要说明的是,在进行上述esd试验时,设备的放电波形严格遵守了jedec标准的规定波形。由于需要外接探针台进行放电试验,虽然在放电回路中增加了同轴电缆对外界干扰进行排除,但外接电路的寄生阻容感还是可能会对波形产生一定影响,使得esd试验发生源(即静电放电设备)波形传输到样件上时有一定程度的衰减,进而使得设备的设定电压值与t形平板电容的实际失效电压值之间可能存在误差。为了得到更为精确的t形平板电容静电放电失效电压数值,即t形平板电容间隙击穿电压,需要建立一个更符合实际试验条件的电路仿真模型并进行仿真求解。下面结合具体实施例对获取第一组t形平板电容的间隙击穿仿真数据的步骤进行详细说明。

[0133]

一、静电放电模拟器搭建

[0134]

本公开一实施例中。根据esd抗扰度试验模拟的对象,结合esd测试模型的主要特点,可以采用jedec标准均规定的人体放电模型(hbm)作为静电放电设备的等效模型,模拟设备本身输出电流波形的仿真回路如图5所示,图5为人体放电模型的设备放电等效电路图。其中,c1为放电电容,c1=100pf;r1为放电电阻r1=1500ω;l1和c2为寄生电感和电容。需要说明的是,静电放电设备的等效模型并不限于人体放电模型(hbm),可以根据需要选择静电放电设备的等效模型。

[0135]

在仿真软件例如cst软件中搭建本实施例所需静电放电模拟器,通过调整尺寸参数及电路组成结构等来满足jedec标准规定的放电波形。搭建的模型实体图如图6所示,图6为一个实施例中静电放电模拟器实体模型的示意图,静电放电模拟器可以包含电介质和金属部分。电介质的相对介电常数为1。金属部分的电导率s为1s/m,金属部分为图6中除电介质以外的结构(为了减少计算时间均设置为理想导体pec材料)。静电放电模拟器还包括集总电路元件,模型中采用的集总电路元件回路参照图5的等效电路图建立,如图7所示,图7为一个实施例中静电放电模拟器集总电路元件的示意图。如图7所示,静电放电模拟器在端口4处激发,将激励端口设置为阶跃函数波形的电压,电压上升时间为10ns,电压幅值大小为1kv,模拟静电放电模拟器的集电器开关,即复现静电放电的充电和快速放电过程,施加的电压信号如图8所示,图8为一个实施例中激励电压波形的示意图。

[0136]

利用上述搭建的静电放电模拟器模型,在仿真软件例如cst软件中开展仿真分析。对静电放电模拟器模型进行网格划分,例如用自带的六面体网格对静电放电模拟器模型进行网格划分后,设置频率范围为0-500mhz,边界条件为接地板处的zmin平面接地,仿真得到的静电放电模拟器输出电流波形如图9和图10所示,图9为静电放电模拟器短接输出波形的

示意图(1kv电压),图10为静电放电模拟器500ω负载输出波形的示意图(1kv电压)。将输出波形与jedec标准规定波形参数作对比如表3所示,从表3中可以看出,电流峰值和波形上升时间都满足标准要求,只是波形下降得较快,但静电放电的失效应该是出现在电流最大的时候,所以下降时间对后续t形平板电容的静电放电仿真没有太大影响。因此,搭建的静电放电模拟器模型符合要求。

[0137]

表3 esd模拟器短路电流的仿真波形参数与标准波形参数的比较

[0138][0139]

二、设备外接探针台等效电路模型建立

[0140]

由于t形平板电容结构微小,无法直接通过放电设备进行esd抗扰度试验,需要外接探针台对样件开展试验。示例性地,外接探针台(即设备到样件的连接)可以分为三个部分,第一部分为带有插针的两根平行细导线,长度为20cm,导线一头通过插针与试验设备的两个管脚连接,另一头连接第二部分同轴电缆的芯线端;第二部分为长度为20cm的同轴电缆,同轴电缆芯线连接第一部分,屏蔽层接地,另一端与第三部分探针导线相连;第三部分为长度为240cm的探针台导线。下面分别对三个部分的等效电路模型参数进行确定。

[0141]

(1)平行细导线

[0142]

第一部分的两根导线一根为输出端,一根为接地,且导线间距较近,会产生耦合电容。故需要确认的电路参数有三个:

①

两根导线间电容c3;

②

输出端导线电阻r2;

③

输出端导线电感l2。平行细导线半径ra=0.5mm,两线间距d=10mm,长度la=20cm。

[0143]

当r

a1

=r

a2

=时,可以采用关系式(1)计算得到半径相等的两圆柱形平行直导线单位长度的电容c3,关系式(1)为:

[0144][0145]

其中,ε0为真空介电常数,ε0=8.85*10^(-12)f/m。

[0146]

电阻r2可通过导体电阻关系式(2)计算:

[0147]

r=ρ*l/s

ꢀꢀꢀꢀꢀꢀ

关系式(2)

[0148]

其中,ρ为导体电阻率,铜导体电阻率为1.75

×

10^(-8)ω

·

m,l为导体长度,s为导体横截面积,其余两部分连接线电阻均运用此公式计算。

[0149]

可以采用关系式(3),计算导线单位长度的电感,关系式(3)为:

[0150][0151]

其中,μ0为真空磁导率,μ0=4π*10^(-7)h/m。

[0152]

计算可得c3=1.86*10^(-12)f,r2=4.46*10^(-3)ω,l2=1*10^(-8)h。

[0153]

(2)同轴电缆

[0154]

本实施例中,开展试验时将同轴电缆的屏蔽层接地,故需要确认的电路参数有三

个:

①

内外导体间电容c4;

②

内导体电阻r3;

③

同轴线电感l3。内导体半径为rb=0.45mm,外导体的内半径为rb=1.6mm,长度lb=20cm,内外导体间填充有均匀绝缘介质聚乙烯(pe),内外导体可视为理想导体,电流分布于导体表面。利用高斯定理可以求得同轴线单位长度的电容和电感。

[0155]

单位长度同轴电缆电容及电感的计算公式分别如关系式(4)和关系式(5),如下:

[0156][0157][0158]

其中,ε为绝缘介质层的介电常数,聚乙烯相对介电常数为2.3。

[0159]

计算可得c4=2.02*10^(-11)f,r3=5.50*10^(-3)ω,l3=2.54*10^(-7)h。

[0160]

(3)探针台导线

[0161]

由于探针台导线间距大,两条导线间未产生电容,且其中一条导线接地,故探针台导线部分需要确定的电路参数有两个:

①

探针台导线的电阻r4;

②

探针台导线的电感l4。探针台导线长度lc=240cm,半径rc=1mm。

[0162]

计算可得r4=1.34*10^(-2)ω,l4=1.2*10^(-7)h。

[0163]

搭建的设备外接探针台等效电路模型如图11所示,图11一个实施例中为外接探针台等效电路模型示意图,图11中的co指代不同结构参数的结构样件,示例性地,图11中的co指代不同结构参数的t形平板电容。外接探针台仿真电路模型参数可以如表4所示。

[0164]

表4外接探针台仿真电路模型参数

[0165][0166]

三、t形平板电容间隙击穿电压仿真

[0167]

(1)t形平板电容模型搭建

[0168]

首先,根据图2及表1列出的t形平板电容几何结构及结构参数在cst软件中直接建立几何模型。为了减少网格数量和计算时间,仅选取单个t形平板电容结构置于玻璃基板上进行模型搭建和仿真。示例性地,可以设置玻璃基板长宽均为10mm,厚度为0.5mm,材料设置为相对介电常数为6的玻璃,根据样件制作时实际布线厚度设置t形平板电容厚度为260nm,布线材料设置为理想导体pec,搭建的几何模型如图12所示,图12为一个实施例中的t形平板电容几何模型。

[0169]

(2)间隙击穿电压仿真电路连接及仿真设置

[0170]

在开展试验时,t形平板电容的两个pad连接的放电端口示意图如图13所示,图13为一个实施例中的探针放电端口示意图。可以利用cst软件的co-simulation功能,即电路模块联合电磁场模块仿真的功能,通过添加的离散端口将建立的静电放电模拟器、外接探针台等效电路模型及t形平板电容几何模型连接起来,形成完整的t形平板电容静电放电仿真模型,如图14所示,图14为一个实施例中t形平板电容静电放电仿真模型。如图14所示,其中,端口1为阶跃电压激励端口;端口2为两个探针中的接地端;端口3为两个探针中的加电端,即与外接电路输出端口连接端;端口4为接地线接地端;端口5为设备输出标准波形的输

出端;外接探针台等效电路连接在端口3和端口5之间,整体电路连接如图15所示,图15为一个实施例中离散端口电路连接示意图。图15中的电阻r

o1

、电阻r

o2

、电阻r

o3

、电感l

o1

、电感l

o2

、电感l

o3

、电容c

o1

、电容c

o2

的参数值如表4所示。

[0171]

仿真电路完成后,需进行网格划分。设定每个波长25个网格,由于t形平板电容的尺寸与静电放电模拟器相比较小,尤其是布线厚度只有260nm,为了得到更准确的仿真结果,软件自动划分网格后对t形平板电容的网格单独划分。在其厚度方面的网格设置为260nm大小,保证金属布线与玻璃基板连接处的每个网格内只有一种材料,并保证布线的长宽上都至少有两个网格。对t形平板电容间隙处的网格进行加密处理,样件间隙宽度(极板间隙)d为10μm、15μm、20μm、25μm,正对长度(极板正对长度)l为30μm、42.5μm、53μm、64μm,故设置间隙处每个网格宽度为2.5μm,长度为3μm。

[0172]

其余参数可以设定为:频率范围设置为0-500mhz;仿真时间设置为15ns,覆盖了静电放电波形的整个上升时间;边界条件设置为open;背景材料设置为空气;求解器选用时域求解器。仿真的输入有结构参数:间隙宽度d和正对长度l、表2所列的每个参数组合下相对应的t形平板电容静电放电失效电压正态分布均值μ设置为阶跃电压幅值v

esd

。仿真的输出结果有e-field监测器监测的电场分布及voltage-monitor(电压监测器)监测的t形平板电容间隙击穿电压v0。

[0173]

(3)t形平板电容间隙击穿电压仿真结果

[0174]

通过电压监测器可以获取t形平板电容间隙击穿电压v0,即静电放电时由竖直短走线及正对长度的长走线之间形成的类平板电容结构两端的实际击穿电压,十六组结构对应的间隙击穿电压仿真结果在表5中列出,从而得到第一组电容的间隙击穿仿真数据,如表5所示。从表5中可以看出,间隙击穿仿真数据包括电容的极板正对长度l、电容的极板间隙d以及电容的间隙击穿电压v0。

[0175]

表5间隙击穿电压v0仿真结果

[0176][0177]

在一种实施方式中,电容的静电放电失效电压模型的确定方法还可以包括:建立

静电放电失效电压基础模型。

[0178]

静电放电电荷q与静电放电电流i在放电时间t相同时成线性关系,如关系式(6):

[0179][0180]

静电放电电压v

esd

与放电电流峰值i

max

也呈线性关系,故在放电电流最大,即t形平板电容间隙达到最大击穿电压发生击穿的时刻t

max

时,放电电荷q与静电放电失效电压v

esd

呈线性关系,如关系式(7):

[0181]vesd

=k1*q=k1*c*v0ꢀꢀꢀꢀꢀ

关系式(7)

[0182]

t形平板电容大小c与极板间隙d、极板正对长度l有关,电容的关系式为关系式(8):

[0183][0184]

其中,ε是一个常数,s为电容极板的正对面积,s=极板正对长度l*布线层厚度,d为电容极板间隙,k则是静电力常量。但本实施例中t形平板电容并不是常规的两块极板组成的平板电容结构,所以t形平板电容的大小满足关系式(9),如下:

[0185][0186]

通过关系式(7)和关系式(9),可以得到静电放电失效电压基础模型如关系式(10)所示:

[0187][0188]

其中,a、b、c、d依次为第一参数、第二参数、第三参数和第四参数,a、b、c、d可以通过数据拟合的方法得到。

[0189]

在一种实施方式中,根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,包括:

[0190]

根据帕邢定律和介电层缺陷密度理论,确定间隙击穿电压基础模型,间隙击穿电压基础模型包括电容的间隙击穿电压、电容的极板正对长度、电容的极板间隙、第五参数、第六参数和第七参数;根据间隙击穿仿真数据,对间隙击穿电压基础模型进行模型拟合,确定第五参数、第六参数和第七参数,以确定间隙击穿电压模型。

[0191]

下面通过具体实施例对确定间隙击穿电压模型进行详细介绍。

[0192]

(1)帕邢定律

[0193]

帕邢(paschen)定律描述了击穿电压与(压力、距离)乘积的关系。paschen曲线反映了townsend制定的汤森雪崩理论,该理论考虑了两种主要击穿机制:电子碰撞电离(eii)和二次电子发射(see)。当两个电极之间的电场足够高时,电子会从最尖锐的凹凸处局部发射,电子被电场加速并获得足够的能量来电离间隙中的气体分子。间隙中存在的阳离子被加速,直到撞击阴极并导致see。eii由电离系数α定义,该系数取决于电压v、气体压力p、间隙距离d和两个气体相关常数a和b,see与二次电离系数γ有关,根据公式:

[0194]

α=ape-bpd/v

[0195]

1-γ(e

αd-1)=0

[0196]

经典的paschen公式基于eii和see击穿机制给出:

[0197][0198]

其中,一般在空气中的气隙击穿取系数a=12cm-1

torr-1

,b=365vcm-1

torr-1

,气压p的单位为torr(一个标准大气压p=760torr),系数γ由放电电极阴极材料决定。

[0199]

(2)介电层缺陷密度理论

[0200]

薄膜电容器的击穿电压取决于介电层中的缺陷密度,其击穿概率取决于电容器面积。满足关系式(12):

[0201]

p=e-γa

ꢀꢀꢀꢀꢀꢀꢀ

关系式(12)

[0202]

其中,γ是缺陷密度/弱点,a是电容器面积。

[0203]

有学者通过公式推导结合试验验证的方法得到了电容器击穿电压u与电容器面积a的关系式,如关系式(13),其中参数α应是小于零的威布尔分布常数:

[0204]

u=ka

α

ꢀꢀꢀꢀꢀꢀꢀꢀ

关系式(13)

[0205]

(3)间隙击穿电压基础模型的建立

[0206]

由表5可知,仿真结果显示,在相似的静电放电失效电压v

esd

的作用下,正对长度l越大的t形平板电容,间隙击穿电压v0减小,电场强度随间隙击穿电压减小而减小,本应该更不容易发生失效。但试验结果表明正对长度l对静电放电失效电压并没有太大影响,这说明t形平板电容受到了介电层缺陷的影响,l越长,电容结构间介电层的缺陷越多,更易发生失效。两种规律的作用效果互相抵消,所以在静电放电失效电压中未体现正对长度l对失效电压的影响,但建立模型时仍应将其考虑进去。参考帕邢公式及介电层缺陷理论公式,确定间隙击穿电压基础模型为关系式(14),如下:

[0207][0208]

其中,k3、e、α分别为第五参数、第六参数和第七参数,可以通过拟合的方法获得k3、e、α的数值。

[0209]

根据表5中的极板间隙d、正对长度l以及对应的间隙击穿电压v0,对间隙击穿电压基础模型进行拟合,数据拟合图如图16所示,图16为v0=f(d,l)间隙击穿电压模型拟合图。拟合得到k3、e、α的数值,其中,第五参数k3的数值范围为68~71(包括端点值),第六参数e的数值范围为(-0.2)~(-0.4)(包括端点值),第七参数α的数值范围为(-0.104)~(-0.107)(包括端点值),从而得到间隙击穿电压模型。

[0210]

示例性地,第五参数k3的数值为69.6,第六参数e的数值为-0.3,第七参数α的数值为-0.1056。

[0211]

那么,间隙击穿电压模型,即v0=f(d,l)为:

[0212][0213]

在一种实施方式中,根据间隙击穿电压模型、静电放电失效电压基础模型和静电放电试验数据,确定静电放电失效电压模型。

[0214]

示例性地,可以将表2中的静电放电失效电压数据都导入matlab软件中,并将拟合

得到的间隙击穿电压模型v0=f(d,l)代入静电放电失效电压基础模型如关系式(10),对静电放电失效电压基础模型中的第一参数a、第二参数b、第三参数c和第四参数d进行拟合,选用bisquare工具,即根据距离拟合线的距离加权,有些异常值权重为0,相当于对其进行剔除。数据拟合图如图17所示,图17为一个实施例中v

esd

=g(d,l)静电放电失效电压模型拟合图。拟合得到第一参数a、第二参数b、第三参数c和第四参数d的数值,其中,第一参数a的数值范围为0.42~0.62,第二参数b的数值范围为230~234,第三参数c的数值范围为20~21,第四参数d的数值范围为2~4,从而确定出静电放电失效电压模型。

[0215]

示例性地,可以将间隙击穿电压模型关系式(15)代入静电放电失效电压基础模型如关系式(10),拟合得到第一参数a的数值为0.527,第二参数b的数值为231.9,第三参数c的数值为20.35,第四参数d的数值为3.085。

[0216]

那么,v

esd

=g(d,l)静电放电失效电压模型满足关系式(16):

[0217][0218]

在一个实施例中,为了验证确定出的静电放电失效电压模型的准确性,可以设计第二组电容的试验样件,并获取第二组电容的静电放电试验数据。可以采用表6所示样件结构参数作为第二组电容的结构参数。

[0219]

表6第二组t形平板电容几何模型参数

[0220][0221]

示例性地,d可以设计8组,其中,13μm和23μm为验证试验数据覆盖范围内(10μm~25μm)的预测准确性,5μm、7μm、30μm、35μm、40μm和60μm用于验证模型扩展范围的适用性,其中5μm和7μm的样件用于观察帕邢曲线的拐点。

[0222]

示例性地,l2可以设计5组,6μm及10μm用于观察形状引发电场集中对失效电压影响,45μm用于验证试验数据覆盖范围内的预测准确性;80μm及100μm既可用于验证模型扩展范围适用性,又可用于探究正对长度l对失效电压影响是否显著。

[0223]

可以采用上文中的获取第一组电容的静电放电试验数据的过程,对第二组电容的样件进行试验,并获取第二组电容的静电放电试验数据,得到如表7所示的试验数据。

[0224]

表7模型预测结果与验证样件试验结果对比

[0225][0226]

通过表7可以看出,对于l=45μm、80μm、100μm的验证样件,所建立的静电放电失效模型预测效果很好,误差几乎都在5%以内,但对于l=6μm、10μm的验证样件,其试验结果与所建模型预测的失效电压相差甚远,个别点会达到25%以上的误差。

[0227]

需要说明的是,采用上文中的获取第一组电容的静电放电试验数据的过程,对第二组电容的样件进行试验时,对于每一个样件编号的t形平板电容,可以获取多个静电放电

失效电压v

esd

,例如,可以获取6个静电放电失效电压v

esd

。表7中的v

esd

均值为多个静电放电失效电压的正态分布均值。

[0228]

在一种实施方式中,电容的静电放电失效电压模型的确定方法还可以包括:获取第二组电容的静电放电试验数据;根据间隙击穿电压模型、静电放电失效电压基础模型、第一组电容的静电放电试验数据和第二组电容的静电放电试验数据,确定修正后的静电放电失效电压模型,修正后的静电放电失效电压模型包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙。

[0229]

示例性地,可以将第一组电容的静电放电试验数据和第二组电容的静电放电试验数据都导入matlab中,并将拟合得到的间隙击穿电压模型v0=f(d,l)代入静电放电失效电压基础模型如关系式(10),对静电放电失效电压基础模型中的第一参数a、第二参数b、第三参数c和第四参数d进行拟合,选用bisquare工具,即根据距离拟合线的距离加权,有些异常值权重为0,相当于对其进行剔除。拟合得到修正后的第一参数a、修正后的第二参数b、修正后的第三参数c和修正后的第四参数d的数值,从而,确定修正后的静电放电失效电压模型。

[0230]

从验证样件的试验结果表7可以看出,本公开实施例确定出的静电放电失效电压模型在l∈[30,100]μm区间,d∈[5,60]μm区间内适用。而l=6μm、10μm时模型预测效果不佳,应是由于l过小形成了放电尖端,导致间隙处更容易发生失效,所以可以对静电放电失效电压模型进行分析修正。

[0231]

(1)电容的正对长度l≥30μm,d≥5μm情况下,对静电放电失效电压模型进行修正

[0232]

修正后的静电放电失效电压模型满足以下关系式(17):

[0233][0234]

其中,a1为修正后的第一参数,b1为修正后的第二参数,c1为修正后的第三参数,d1为修正后的第四参数。

[0235]

将表2中的第一组电容的静电放电试验数据和第二组电容的静电放电试验数据中l=45μm、80μm、100μm的静电放电试验数据均导入matlab中,并将拟合得到的间隙击穿电压模型v0=f(d,l)代入修正后的静电放电失效电压基础模型如关系式(17),对修正后的静电放电失效电压基础模型中的修正后的第一参数a1、修正后的第二参数b1、修正后的第三参数c1和修正后的第四参数d1进行拟合。修正模型时保证了阴极材料和试验环境相关参数不变,建模所用样件和验证所用样件的材料和试验环境均一致。数据拟合图如图18所示,图18为本公开一实施例中修正后v

esd

=g1(d,l)静电放电失效电压模型拟合图(l≥30μm)。拟合得到修正后的第一参数a1、修正后的第二参数b1、修正后的第三参数c1和修正后的第四参数d1的数值,其中,修正后的第一参数1a的数值范围为0.25~0.45,修正后的第二参数b1的数值范围为252~256,修正后的第三参数c1的数值范围为15~16.5,修正后的第四参数d1的数值范围为5~7.5,从而确定出修正后的静电放电失效电压模型v

esd

=g1(d,l)。

[0236]

示例性地,可以将间隙击穿电压模型关系式(15)代入修正后的静电放电失效电压基础模型如关系式(17),拟合得到修正后的第一参数a1的数值为0.355,修正后的第二参数b1的数值为253.7,修正后的第三参数c1的数值为15.72,修正后的第四参数d1的数值为6.3。

[0237]

那么,修正后的v

esd

=g1(d,l)静电放电失效电压模型满足关系式(18):

[0238][0239]

修正后的静电放电失效电压模型预测结果与试验结果作对比,如表8所示。从表8中可以看出,对于l≥30μm的样件,修正后的静电放电失效电压模型适用性强。

[0240]

表8 v

esd

=g1(d,l)模型预测结果与验证样件试验结果对比

[0241]

[0242][0243]

示例性地,图19为l=45μm时采用本公开一实施例的模型预测静电放电失效电压的示意图。从图19中可以看出,将正对长度l固定为45μm时,在间隙宽度d=4μm附近失效电压模型出现了拐点,这意味着模型可能不适用于4μm及以下的间隙宽度。因此,对于极板间隙d的模型适用范围,建议在d≥5μm时使用本公开实施例的静电放电失效电压模型进行失效电压的预测。

[0244]

(2)电容的正对长度l≤10μm情况下,对静电放电失效电压模型进行修正

[0245]

修正后的静电放电失效电压模型满足以下关系式(19):

[0246][0247]

其中,a2为修正后的第一参数,b2为修正后的第二参数,c2为修正后的第三参数,

d2为修正后的第四参数。

[0248]

正对长度l≤10μm时,由于此时t形平板电容形成了一个放电尖端结构,引发的电场集中会导致失效电压下降,但由于布线材料和试验环境仍然没有变化,故模型中需要修正的应该是与形状相关,即其本身电容和耦合电容等相关的参数,将第二组电容的静电放电试验数据中l=6μm、10μm的静电放电试验数据都导入matlab中,并将拟合得到的间隙击穿电压模型v0=f(d,l)代入修正后得静电放电失效电压基础模型如关系式(19),对静电放电失效电压基础模型中的修正后的第一参数a、修正后的第二参数b、修正后的第三参数c和修正后的第四参数d进行拟合。数据拟合图如图20所示,图20为本公开一实施例中修正后v

esd

=g2(d,l)静电放电失效电压模型拟合图(l≤10μm)。拟合得到修正后的第一参数a2、修正后的第二参数b2、修正后的第三参数c2和修正后的第四参数d2的数值,其中,修正后的第一参数a2的数值范围为2.5~3.5,修正后的第二参数b2的数值范围为21.5~23,修正后的第三参数c2的数值范围为15~16,修正后的第四参数d2的数值范围为0.4~0.55,从而确定出修正后的静电放电失效电压模型v

esd

=g2(d,l)。

[0249]

示例性地,可以将间隙击穿电压模型关系式(15)代入静电放电失效电压基础模型如关系式(19),拟合得到修正后的第一参数a2的数值为3,修正后的第二参数b2的数值为22.25,修正后的第三参数c2的数值为15.38,修正后的第四参数d2的数值为0.4716。

[0250]

那么,修正后的静电放电失效电压模型v

esd

=g2(d,l)满足关系式(20):

[0251][0252]

修正后的静电放电失效电压模型预测结果与试验结果作对比,如表9所示。从表9中可以看出,对于l≤10μm的样件,修正后的静电放电失效电压模型适用性强。

[0253]

表9 v

esd

=g2(d,l)模型预测结果与验证样件试验结果对比

[0254][0255]

本公开实施例确定出的静电放电失效电压模型,可以为抗静电设计提供理论依据,可以为实现特殊形状布线的抗静电定量化设计提供理论依据,使得抗静电设计不再仅

停留在定性试验阶段,避免了通过盲目改变设计来修改抗静电措施,提高了抗静电设计的效率。

[0256]

图21为本公开一实施例中电容的静电放电失效电压模型的确定装置的结构框图。本公开实施例还提供一种电容的静电放电失效电压模型的确定装置,如图21所示,包括:

[0257]

第一获取模块211,用于获取第一组电容的静电放电试验数据,静电放电试验数据包括电容的极板正对长度、电容的极板间隙以及电容的静电放电失效电压;

[0258]

第二获取模块212,用于获取第一组电容的间隙击穿仿真数据,间隙击穿仿真数据包括电容的极板正对长度、电容的极板间隙以及电容的间隙击穿电压;

[0259]

第一确定模块213,用于根据间隙击穿仿真数据和间隙击穿电压基础模型,确定间隙击穿电压模型,间隙击穿电压模型为包括电容的间隙击穿电压、电容的极板正对长度和电容的极板间隙的关系式;

[0260]

第二确定模块214,用于根据间隙击穿电压模型、静电放电失效电压基础模型和第一组电容的静电放电试验数据,确定静电放电失效电压模型,静电放电失效电压模型为包括电容的静电放电失效电压、电容的极板正对长度和电容的极板间隙的关系式。

[0261]

根据本公开的实施例,本公开还提供了一种电子设备、一种可读存储介质和一种计算机程序产品。

[0262]

本文中以上描述的系统和技术的各种实施方式可以在数字电子电路系统、集成电路系统、场可编程门阵列(fpga)、专用集成电路(asic)、专用标准产品(assp)、芯片上系统的系统(soc)、负载可编程逻辑设备(cpld)、计算机硬件、固件、软件、和/或它们的组合中实现。这些各种实施方式可以包括:实施在一个或者多个计算机程序中,该一个或者多个计算机程序可在包括至少一个可编程处理器的可编程系统上执行和/或解释,该可编程处理器可以是专用或者通用可编程处理器,可以从存储系统、至少一个输入装置、和至少一个输出装置接收数据和指令,并且将数据和指令传输至该存储系统、该至少一个输入装置、和该至少一个输出装置。

[0263]

用于实施本公开的方法的程序代码可以采用一个或多个编程语言的任何组合来编写。这些程序代码可以提供给通用计算机、专用计算机或其他可编程数据处理装置的处理器或控制器,使得程序代码当由处理器或控制器执行时使流程图和/或框图中所规定的功能/操作被实施。程序代码可以完全在机器上执行、部分地在机器上执行,作为独立软件包部分地在机器上执行且部分地在远程机器上执行或完全在远程机器或服务器上执行。

[0264]

在本公开的上下文中,机器可读介质可以是有形的介质,其可以包含或存储以供指令执行系统、装置或设备使用或与指令执行系统、装置或设备结合地使用的程序。机器可读介质可以是机器可读信号介质或机器可读储存介质。机器可读介质可以包括但不限于电子的、磁性的、光学的、电磁的、红外的、或半导体系统、装置或设备,或者上述内容的任何合适组合。机器可读存储介质的更具体示例会包括基于一个或多个线的电气连接、便携式计算机盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦除可编程只读存储器(eprom或快闪存储器)、光纤、便捷式紧凑盘只读存储器(cd-rom)、光学储存设备、磁储存设备、或上述内容的任何合适组合。

[0265]

为了提供与用户的交互,可以在计算机上实施此处描述的系统和技术,该计算机具有:用于向用户显示信息的显示装置(例如,crt(阴极射线管)或者lcd(液晶显示器)监视

器);以及键盘和指向装置(例如,鼠标或者轨迹球),用户可以通过该键盘和该指向装置来将输入提供给计算机。其它种类的装置还可以用于提供与用户的交互;例如,提供给用户的反馈可以是任何形式的传感反馈(例如,视觉反馈、听觉反馈、或者触觉反馈);并且可以用任何形式(包括声输入、语音输入或者、触觉输入)来接收来自用户的输入。

[0266]

可以将此处描述的系统和技术实施在包括后台部件的计算系统(例如,作为数据服务器)、或者包括中间件部件的计算系统(例如,应用服务器)、或者包括前端部件的计算系统(例如,具有图形用户界面或者网络浏览器的用户计算机,用户可以通过该图形用户界面或者该网络浏览器来与此处描述的系统和技术的实施方式交互)、或者包括这种后台部件、中间件部件、或者前端部件的任何组合的计算系统中。可以通过任何形式或者介质的数字数据通信(例如,通信网络)来将系统的部件相互连接。通信网络的示例包括:局域网(lan)、广域网(wan)和互联网。

[0267]

计算机系统可以包括客户端和服务器。客户端和服务器一般远离彼此并且通常通过通信网络进行交互。通过在相应的计算机上运行并且彼此具有客户端-服务器关系的计算机程序来产生客户端和服务器的关系。服务器可以是云服务器,也可以为分布式系统的服务器,或者是结合了区块链的服务器。

[0268]

应该理解,可以使用上面所示的各种形式的流程,重新排序、增加或删除步骤。例如,本发公开中记载的各步骤可以并行地执行也可以顺序地执行也可以不同的次序执行,只要能够实现本公开公开的技术方案所期望的结果,本文在此不进行限制。

[0269]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者多个该特征。在本公开的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0270]

在本公开中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接,还可以是通信;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

[0271]

上文的公开提供了许多不同的实施方式或例子用来实现本公开的不同结构。为了简化本公开,上文中对特定例子的部件和设置进行描述。当然,它们仅仅为示例,并且目的不在于限制本公开。此外,本公开可以在不同例子中重复参考数字和/或参考字母,这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施方式和/或设置之间的关系。

[0272]

上述具体实施方式,并不构成对本公开保护范围的限制。本领域技术人员应该明白的是,根据设计要求和其他因素,可以进行各种修改、组合、子组合和替代。任何在本公开的精神和原则之内所作的修改、等同替换和改进等,均应包含在本公开保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1