一种基于反向搜索和遗传算法的电路划分方法

1.本发明涉及电子设计自动化的门级电路并行仿真技术领域,特别涉及一种基于反向搜索和遗传算法的电路划分方法。

背景技术:

2.在门级电路(gate level circuit,glc)设计中,常通过仿真的方法验证电路的功能。随着电路规模逐渐增大,仿真需要消耗的时间逐渐增加。传统仿真技术已经不能满足日益增长的电路规模要求,限制了超大规模集成电路设计的发展。随着并行计算机和云计算技术的发展,可将门级电路系统进行划分,基于并行架构进行仿真方法缩减仿真时间,可有效缓解这个问题。

3.为了实现并行仿真,需要对电路进行合理划分,各仿真器之间通信量最小化和负载均衡是评价划分质量的关键指标。通信量最小化是指尽量减小各仿真器通信所花费的时间,通信花费的时间与割边的数量成正比。一般的各仿真器之间通信的时间比访问仿真器本地内存的时间高一个数量级。因此在并行仿真中,如果各仿真器之间通信频繁,那么通信花费的时间占据了工作时间的大部分。因此降低各仿真器间的通信开销是提升仿真速度的关键点。负载均衡是指各仿真器仿真的时间要大致相同,与逻辑门的数量和仿真器的计算速度相关。如果电路划分中各块的规模相差较大,那么在并行仿真中各仿真器仿真的时间差异较大,容易出现“水桶效应”,整体仿真时间受制于仿真时间最长的那个仿真器。目前的算法都是以实现通信量最小化和负载均衡为目标,但是两个问题均没有彻底解决。

技术实现要素:

4.本发明提供了一种基于反向搜索和遗传算法的电路划分方法,其目的是为了实现电路划分通信量为零且负载均衡,解决电子设计自动化的电路仿真时过长的问题。

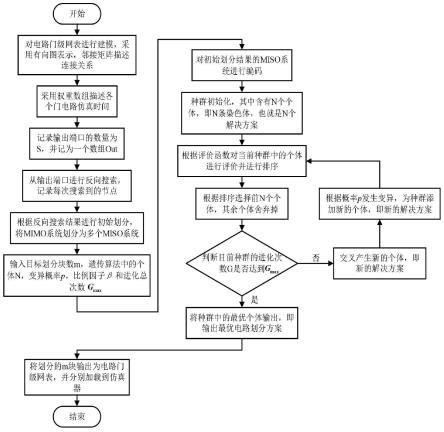

5.为了达到上述目的,本发明提供了一种基于反向搜索和遗传算法的电路划分方法,包括:

6.步骤1,对电路门级网表进行建模;

7.步骤2,从mimo门级电路的输出端口进行反向搜索并记录搜索结果,根据搜索结果进行初始划分,将mimo门级电路划分为数量与输出端口数量相同的miso系统;

8.步骤3,基于遗传算法对miso系统进行组合、合并、优化,将符合要求的初始划分的miso系统进行并集运算,得到期望的划分块数m;

9.步骤4,将电路划分的m块输出为电路门级网表,并分别加载到仿真器。

10.其中,步骤1通过将门级网表转换为有向图模型,所述有向图模型包括节点和有向边,节点表示逻辑门或触发器,有向边表示节点间的连接关系,采用邻接矩阵表示有向图模型的内部连接关系,通过权重数组描述节点的仿真时间。

11.其中,搜索结果是所有和输出端口有关联的节点。

12.其中,遗传算法采用单条染色体表示一个个体,足够数量的个体构成种群,每条染

色体中的一个基因代表初始划分的一个miso系统。

13.其中,步骤3包括:

14.步骤31,输入目标划分块数m、种群个体数量n、变异概率p、比例因子β和进化总次数g

max

;

15.步骤32,对所述miso系统进行编码;

16.步骤33,对种群进行初始化;

17.步骤34,根据评价函数对当前种群中的个体进行评价并按照评价函数的评价值进行升序排序;

18.步骤35,根据排序选择种群中的前n个个体,舍弃其余个体;

19.步骤36,判断当前种群中个体的进化次数g是否达到最大值g

max

,若否,则通过交叉产生新个体,根据变异概率p发生变异,为种群添加新的个体后重复步骤34,直至当前种群中个体的进化次数g达到最大值g

max

进行步骤37,反之,则直接进行步骤37;

20.步骤37,将种群中的最优个体输出,即输出最优电路划分方案。

21.所述遗传算法中的个体n大于50,变异概率p小于10%,比例因子β为0.5,进化总次数g

max

大于30。

22.步骤34中的评价函数包括各块权重的标准差asd

i,g

和重复度mul

i,g

;

23.各块权重的标准差asd

i,g

为

[0024][0025]

重复度mul

i,g

为

[0026]

mul

i,g

=cost

i,g-cost

initial

[0027]

评价函数f

i,g

为

[0028]fi,g

=β

·

asd

i,g

+(1-β)

·

mul

i,g

[0029]

其中,cost

i,g

为每个染色体的权重,cost

yk

(k=1,2,

…

,m)为一个染色体上编号相同的基因构成集合的权重,cost

initial

为电路划分前整体电路的总权重,β为比例因子。

[0030]

其中,交叉是选择两个个体作为父代,在父代1中选择一段子串复制到一个空串的相应位置产生一个初始后代,在父代2中随机选择一段子串,按顺序将子串复制到初始后代进行交叉。

[0031]

其中,变异是使种群中少数个体的染色体发生大幅度变动,在进化过程中产生之前不存在的新特征。

[0032]

本发明的上述方案有如下的有益效果:

[0033]

本发明杜绝了并行仿真中各仿真器之间的通信,对门级电路的各个逻辑门电路赋予权重,基于权重判断划分结果的负载均衡,使得电路划分的结果更加合理,实现了通信量为零且负载均衡。

[0034]

本发明的其它有益效果将在随后的具体实施方式部分予以详细说明。

附图说明

[0035]

图1为本发明实施例的流程图;

[0036]

图2为本发明实施例基于反向搜索的初始划分的有向图;

[0037]

图3为本发明实施例对染色体进行交叉操作图;

[0038]

图4为8位超前进位加法器的有向图;

[0039]

图5为本实施例将图4划分后的第一块的有向图;

[0040]

图6为本实施例将图4划分后的第二块的有向图;

[0041]

图7为本实施例将图4划分后的第三块的有向图。

具体实施方式

[0042]

为使本发明要解决的技术问题、技术方案和优点更加清楚,下面将结合附图及具体实施例进行详细描述。显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0043]

在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

[0044]

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是锁定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

[0045]

此外,下面所描述的本发明不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

[0046]

本发明针对现有的问题,提供了一种基于反向搜索和遗传算法的电路划分方法。

[0047]

在本发明具体实施之前,需对以下概念进行介绍:

[0048]

独立并行仿真:指各个仿真器并行仿真时,仿真器之间无需通信,没有信息交流。

[0049]

通信量:指各个仿真器并行仿真时,仿真器之间的通信数据量。在独立并行仿真中,通信量为零。

[0050]

权重:指一个逻辑门的权重是该逻辑门的输入端口数量加上1;不同节点权重的比值大致等于所对应逻辑门仿真时间的比值,门级电路的权重是它的所有逻辑门的权重之和。

[0051]

负载:指加载到仿真器中的电路数量,仿真时间长短取决于负载的多少;负载均衡指在各个仿真器仿真的电路规模差不多,即仿真时间差不多。

[0052]

mimo系统:指具有多个输入端口,多个输出端口的系统。

[0053]

miso系统:指具有多个输入端口,1个输出端口的系统。

[0054]

如图1所示,本发明的实施例提供了一种基于反向搜索和遗传算法的电路划分方法,包括:

[0055]

步骤1,对电路门级网表进行建模;通过将门级网表转换为有向图模型,有向图模

型包括节点和有向边,节点表示逻辑门或触发器,有向边表示节点间的连接关系,采用邻接矩阵表示有向图模型的内部连接关系,通过权重数组描述节点的仿真时间,对门级电路的各个逻辑门电路赋予权重,基于权重判断划分结果的负载均衡,使得电路划分的结果更加合理。

[0056]

例如:有向图g(v,e)中,v={v1,v2,

…

,vn}是节点的集合,n是有向图节点的数量,e={e1,e2,

…

,eb}是有向边的集合,其中b是有向边的数量;对于一个有n个节点的有向图,邻接矩阵的大小为n

×

n,w是权重数组,w(vi)是节点vi的权重。

[0057]

其中,邻接矩阵中第i行第j列的值d

ij

如式(1)所示。

[0058][0059]

然后进入步骤2。

[0060]

步骤2,从mimo门级电路的输出端口进行反向搜索并记录每次搜索到的结果,根据搜索结果进行初始划分,将mimo门级电路划分为数量与输出端口数量相同的miso系统;

[0061]

具体来说,如果mimo门级电路有s个输出端口,将s个输出端口计为一个集合out,然后依次从集合out中的节点开始反向搜索,当一个节点a满足d

aout(i)

=1,说明节点a和out(i)有连接关系,那么便将节点a储存到集合m{i}。如果另外一个节点b满足d

bd

=1,说明节点b和节点a有连接关系,那么便将节点b储存到集合m{i}。以此类推,将所有对输出端口out(i)有关联的节点储存到集合m{i};对有向图进行初始划分,划分为s块,将集合m{i}中的所有节点划分为第i块。

[0062]

以图2所示的一个mimo系统有向图为例,该有向图有三个输出端口,即s为3,分别是v6、v10和v11,记为集合out。从v6进行反向搜索,可以搜索到节点(v1,v2,v3,v4,v5,v6),记为m{1};从节点v10反向搜索,可以搜索到节点(v1,v2,v7,v8,v9,v10),记为m{2};从节点v11进行反向搜索,可以搜索到节点(v1,v2,v7,v8,v9,v11),记为m{3};因此可以将图2a中的有向图初始划分为3块,即3个miso系统,如图2b所示。

[0063]

步骤3,基于遗传算法对miso系统进行组合、合并、优化,将符合要求的初始划分的miso系统进行并集运算,得到期望的划分块数m;其目的是将相同单元过多的两块进行合并得到期望的划分块数m,摆脱输出端口数量的限制,确保划分结果中各块的权重大致相等,保证了负载较为均衡。

[0064]

具体来说,遗传算法采用单条染色体表示一个个体,足够数量的个体构成种群,每条染色体中每条染色体由s个基因组成,一个基因代表初始划分的一个miso系统。

[0065]

步骤3包括:

[0066]

步骤31,输入目标划分块数m、种群个体数量n、变异概率p、比例因子β和进化总次数g

max

;个体n大于50,变异概率p小于10%,比例因子β为0.5,进化总次数g

max

大于30。

[0067]

步骤32,对miso系统进行编码;

[0068]

染色体采用整数编码,每个基因的数值就是该基因被分配的集合的编号。因此,一条染色体就是一个电路划分方案。染色体采用式(2)表示:

[0069]

x

i,g

(i=1,2,

…

,n)=(x1,x2,

…

,xs)

ꢀꢀꢀꢀ

(2)

[0070]

其中,x

i,g

为染色体,i为种群中个体的编号即染色体的编号,g为进化次数,n为每

代个体的总数,s为x

i,g

的维度即反向搜索初始划分miso系统的输出端口数量。xj是一个基因,1≤xj(j=1,2,

…

,s)≤m,m为期望划分的总块数。

[0071]

例如:染色体x

2,3

为(y1,y3,y2,y2,y1,y2,y3,y3),表示第2个个体的第3代染色体,s为8,m为3。其中,基因x1和x5的编码相同,属于第y1块;基因x3、x4和x6的编码相同,属于第y2块;基因x2、x7和x8的编码相同,属于第y3块。

[0072]

步骤33,对种群进行初始化;

[0073]

初始群体是在解的范围内随机产生,对于染色体x上的任意一个基因xj(j=1,2,

…

,s)的取值范围为[1,m],初始取值为

[0074]

xj=1+round[(m-1)

·

rand(0,1)]

ꢀꢀ

(3)

[0075]

其中,round函数的作用是四舍五入到最近的整数,rand(0,1)函数的作用是随机产生[0,1]内的随机小数。

[0076]

步骤34,根据评价函数对当前种群中的个体进行评价并按照评价函数的评价值进行升序排序;建立评价函数f

i,g

,评价电路划分结果的好坏。

[0077]

具体来说,评价函数包括划分结果中的各块权重的标准差asd

i,g

和重复度mul

i,g

;

[0078]

每个染色体的权重为cost

i,g

,可以由式(4)求得:

[0079]

cost

i,g

=cost

y1

+cost

y2

+

…

+cost

ym

ꢀꢀ

(4)

[0080]

各块权重的标准差asd

i,g

为

[0081][0082]

重复度mul

i,g

为

[0083]

mul

i,g

=cost

i,g-cost

initial

ꢀꢀ

(6)

[0084]

评价函数f

i,g

为

[0085]fi,g

=β

·

asd

i,g

+(1-β)

·

mul

i,g

ꢀꢀ

(7)

[0086]

其中,cost

i,g

为每个染色体的权重,cost

yk

(k=1,2,

…

,m)为一个染色体上编号相同的基因构成集合的权重,cost

initial

为电路划分前整体电路的总权重,β为比例因子;通过控制比例因子β,可以控制电路划分结果对负载均衡和重复度的重视程度。

[0087]

按照评价函数的评价值f

i,g

进行排序,f

i,g

越低的个体排在前面。评价函数f

i,g

的数值越小,那么个体的适应度越高,越符合电路划分的要求。β为比例因子,β越大则标准差asd

i,g

对评价函数f

i,g

的影响更大,β越小则重复度mul

i,g

对评价函数f

i,g

的影响更大。

[0088]

步骤35,根据排序选择种群中的前n个个体,舍弃其余个体;

[0089]

步骤36,判断当前种群中个体的进化次数g是否达到最大值g

max

,若否,则通过交叉产生新个体,根据变异概率p发生变异,为种群添加新的个体后重复步骤34,直至当前种群中个体的进化次数g达到最大值g

max

进行步骤37,反之,则直接进行步骤37;

[0090]

交叉是选择两个个体作为父代,在父代1中选择一段子串,子串长度为s。g,并将其复制到一个空串的相应位置产生一个初始后代,在父代2中随机选择一段子串,子串长度为s-sg,按顺序将子串复制到初始后代进行交叉;如图3所示是一个交叉操作图,其中初始划分miso系统的输出端口数量s为8,目标划分块数m为3。

[0091]

变异是使种群中少数个体的染色体发生大幅度变动,在进化过程中产生之前不存在的新特征,是种群跳出局部最优解的一种方法。染色体的变异受变异概率p的影响。对于

任意一个染色体x中的一个基因xj(j=1,2,

…

s),如果

[0092]

rand(0,1)<p

ꢀꢀ

(8)

[0093]

那么该基因xj发生变异,变异的公式如下所示,

[0094]

xj=1+round[(m-1)*rand(0,1)]

ꢀꢀ

(9)。

[0095]

步骤37,将种群中的最优个体输出,即输出最优电路划分方案。

[0096]

步骤4,将电路划分的m块输出为电路门级网表,并分别加载到仿真器。

[0097]

本实施例结合8位超前进位加法器进行电路划分,如图4所示,其中有17个外部输入信号和9个输出端口。该电路网表转化为有向图后,有68个节点,总权重为325。其中输出端口s为9,集合out为{v3,v8,v14,v21,v29,v38,v48,v59,v68}。反向搜索初始划分的9个miso系统的节点数和权重如表1所示。

[0098]

表1初始划分的9个miso系统

[0099]

第几块123456789节点数158111417202325总权重416273952668198110

[0100]

然后采用遗传算法对初始划分结果组合优化,最终划分为3块,节点数和权重如表2所示。

[0101]

表2遗传算法组合合并优化后的电路划分结果

[0102][0103][0104]

最终划分结果的有向图分别如图5、图6、图7所示。

[0105]

本发明实施例首先对门级网表进行建模。采用有向图、邻接矩阵和权重数组表示门级电路,反向搜索将mimo系统划分为多个miso系统,各miso系统没有依赖关系,在并行仿真时无需通信,可以独立并行仿真,基于遗传算法对多个miso系统进行组合合并优化,得到期望的划分块数,均衡仿真负载,减少不同划分块之间的相同单元,最终得到电路划分结果。采用本发明的电路划分方法,可以提高电路并行仿真的效率。经过实践证明,实用性很高。

[0106]

本发明杜绝了并行仿真中各仿真器之间的通信,对门级电路的各个逻辑门电路赋予权重,基于权重判断划分结果的负载均衡,使得电路划分的结果更加合理,实现了通信量为零且负载均衡。

[0107]

以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明所述原理的前提下,还可以作出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1