用于对内存屏障指令有效性进行验证的方法和相关产品与流程

1.本发明一般地涉及计算机技术领域。更具体地,本发明涉及一种用于对内存屏障指令有效性进行验证的方法、设备和计算机可读存储介质。

背景技术:

2.近年来,我国科学技术等方向虽然得到不断发展,但在核心运算器、调度器、操作系统、核心算法、芯片设计原理上仍然处于摸索和学习阶段。

3.在核心处理器的设计理念上,目前我国以及世界发达国家均从“指令顺序执行”的第一代设计跨入了“指令乱序发射,乱序执行”的第二代设计阶段,出现了大量基于“指令乱序发射,乱序执行”的巅峰核心处理器设计框架,如arm v8系列,intel xeon等。“指令乱序发射,乱序执行”使得核心处理器的性能通过自我优化的方式得到显著的提升。

4.传统的指令顺序执行cpu在接到1-4条指令时,会依次如下执行:首先寻访地址“北京”移动至“广州”,其次寻访地址“天津”移动至“上海”,然后寻访地址“北京”移动至“天津”,最后寻访地址“上海”移动至“广州”。如下表1所示:

5.表1:

6.序号指令执行顺序1北京-》广州12天津-》上海23北京-》天津34上海-》广州4

7.上述执行方式的优点在于:cpu可以精准地执行每条任务,但是其所存在的缺点也显而易见。在指令路径和相关联的节点上存在时间和空间的冗余。可以明显的看出,cpu其实不用从北京到广州寻址移动两次,一次即可完成全部任务,因而在后续的cpu设计中加入了“指令乱序发射,乱序执行”的设计。首先将所有指令乱序发射到cpu的指令级队列中进行排队,然后进行排序、筛选和优化(例如部分指令不执行)。接着将不影响程序运行结果的冗余指令进行排序和优化后,进行“乱序”的优化执行,以达到优化性能的结果。经过优化后的指令的实际执行顺序如表2所示:

8.表2:

9.序号指令优化结果实际执行顺序1北京-》广州优化掉不执行2天津-》上海排序不变23北京-》天津排序114上海-》广州排序33

10.表2中各指令的执行顺序如下:首先寻访地址“北京”移动至“天津”,其次直接访问地址“天津”移动至“上海”,最后直接寻访地址“上海”移动至“广州”。由于“北京-》广州”的指令实际已经达成效果,因而优化掉不执行。上述方式使得原先顺序输入的指令由于优化

而乱序发射给 cpu的运算单元,不按照原有的顺序执行,称为“乱序发射和乱序执行”,大大加快了cpu运算的速度和效率,也是当代cpu的主流设计原理。但是上述做法在安全性上存在一定的漏洞,它破坏了指令执行的原有顺序,很容易对指令的源地址和目标地址进行预判,通过旁信道分析的方式获取一定的信息,导致信息泄露。

11.随着cpu“乱序执行”技术的发展,为了使程序严格执行运算过程中的原始指令的顺序,cpu在指令集中增加了“内存屏障”指令barrier(),使得在内存屏障两侧的语句禁止执行优化。如下表3中示出了加入内存屏障指令后的执行顺序:

12.表3:

13.序号指令执行顺序1北京-》广州不执行2天津-》上海23北京-》天津14上海-》广州35barrier()46上海-》广州67天津-》上海5

14.内存屏障指令barrier()的出现使得指令队列划分为内存屏障指令前的一组(即序号1-4的指令)以及内存屏障指令后的一组(即序号6-7的指令)。通过实际执行顺序可以看出在内存屏障指令的两侧,cpu分别对 1-4指令以及6-7指令进行乱序执行,并非按照1-7指令进行乱序执行。未增加“内存屏障”指令barrier()时,其理论上经过乱序执行产生的结果如下表4:

15.表4:

16.序号指令执行顺序1北京-》广州不执行2天津-》上海23北京-》天津14上海-》广州35上海-》广州不执行6天津-》上海不执行

17.内存屏障指令作为阻止cpu乱序执行的重要条件,其硬件实现可以由指令级隔离寄存器、开关选择门电路等实现。在细节芯片的设计工艺上,如:指令级隔离寄存器、开关门电路、选择门电路的实现上,会由于工艺、设计的缺陷导致前述器件的功能失效,其失效的结果就是内存屏障指令barrier()无法正常运转,导致大规模的指令乱序执行的发生,破坏了传统芯片的运算逻辑。如果不对这种现象及时发现,cpu内存屏障指令功能异常将会带来系统安全性差、指令运行正确性不能保证等严重问题。

18.由于cpu的生产和测试多依赖于cpu流片制造商或cpu设计商的制造水平以及测试水平,在操作系统以及用户层并不能真实反映内存屏障指令失效性的问题,因而内存屏障指令的失效对cpu执行指令的影响并不易被发现。而且目前内存屏障指令在常规编程时一般很少被引入,因而即使发生故障也不易被编程者所发觉。然而,内存屏障指令运行的正确

性关乎于系统安全以及指令运行的正确性,其作用尤其在国产自主cpu中的价值不容忽视。

19.因此,如何能快速、便捷的检测cpu屏障指令是否存在功能性的异常则成为目前亟需解决的技术问题。

技术实现要素:

20.为解决上述一个或多个技术问题,本发明提出通过各种程序结构生成包含内存屏障的验证指令,并利用cpu执行该验证指令的执行结果对cpu 中内存屏障指令的有效性进行判断,从而有效提升cpu中指令运行的有效性,减少内存屏障指令使用不当造成的越权或权限提升漏洞。为此,本发明在如下的多个方面中提供方案。

21.在第一方面中,本发明中提供了一种用于对内存屏障指令有效性进行验证的方法,包括:获取验证指令,所述验证指令包括基于验证代码集中各种程序结构的配置信息生成的一个或多个指令子集,每个指令子集中包含内存屏障指令;利用cpu运行所述验证指令,以生成对所述验证指令的执行结果;将cpu对所述验证指令的执行结果与所述验证指令对应的标准结果进行比对;以及响应于cpu对所述验证指令的执行结果与所述验证指令对应的标准结果不同,确定cpu中内存屏障指令失效。

22.在一个实施例中,所述程序结构包括以下类型中的一种或多种:顺序结构、循环结构、判断结构、队列结构、栈结构、树形结构、图形结构和嵌套结构,其中所述图形结构包括无向图结构和有向图结构。

23.在一个实施例中,所述利用cpu运行所述验证指令以生成对所述验证指令的执行结果包括:按照程序结构的复杂度从小到大的顺序分别将对应的指令子集进行排序;以及利用cpu根据所述排序分别运行每种程序结构对应的指令子集,以生成对应的执行结果。

24.在一个实施例中,所述指令子集中还包括探针,其中所述利用cpu 运行所述验证指令以生成对所述验证指令的执行结果还包括:利用所述探针获取所述验证指令在cpu中运行时的数据流信息,以便对cpu的处理过程进行监测。

25.在一个实施例中,其中将所述验证指令输入cpu之前还包括:禁用编译器的优化选项,以避免编译器对所述验证指令进行优化;以及将所述验证指令输入编译器,以将所述验证指令转换为cpu能够识别的二进制指令。

26.在一个实施例中,所述方法还包括:对所述cpu进行加压检测,以判断所述内存屏障指令在设定压力时的有效性。

27.在一个实施例中,所述对所述cpu进行加压检测以判断所述内存屏障指令在设定压力时的有效性包括:对所述cpu的负载压力进行检测,以判断所述负载压力是否大于设定压力;以及响应于所述负载压力低于设定压力,提升所述cpu的负载压力,以将所述cpu的负载压力提升至设定压力。

28.在一个实施例中,所述获取验证指令包括:从预设的验证代码集中选择一种或多种程序结构的代码信息;以及基于每种程序结构的代码信息生成指令子集,以形成用于对内存屏障的有效性进行验证的验证指令。

29.在第二方面中,本发明还提供了一种用于对内存屏障指令有效性进行验证的设备,包括:处理器;以及存储器,其存储有用于对内存屏障指令有效性进行验证的计算机指令,当所述计算机指令由所述处理器运行时,使得所述电子设备执行根据前述第一方面中

一个或多个实施例中所述的方法。

30.在第三方面中,本发明还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有用于对内存屏障指令有效性进行验证的计算机可读指令,该计算机可读指令被一个或多个处理器执行时实现如前述第一方面中一个或多个实施例中所述的方法。

31.根据本发明的技术方案,可以基于各种程序结构生成对应的验证指令,利用cpu运行该验证指令,以根据执行结果对内存屏障指令在cpu 中的有效性进行验证,从而有效提升了系统安全性和cpu中指令运行正确性。该方法不需要获取程序源码,可以在用户层实现对cpu内存屏障指令有效性的便捷且全面地检测。进一步,本发明的方案中还通过加压检测的方式,在验证过程中增加cpu的运算压力,以实现对cpu更加全面的检测。

附图说明

32.通过参考附图阅读下文的详细描述,本发明示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本发明的若干实施方式,并且相同或对应的标号表示相同或对应的部分,其中:

33.图1是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的方案的场景示意图;

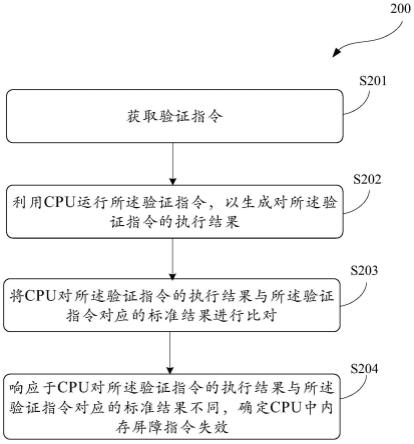

34.图2是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的方法的流程图;

35.图3是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的另一种方法的流程图;

36.图4是示意性示出根据本发明的实施例的树形程序结构中内存屏障指令的示意图;

37.图5是示意性示出根据本发明的实施例的无向图程序结构中内存屏障指令的示意图;

38.图6是示意性示出根据本发明的实施例的有向图程序结构中内存屏障指令的示意图;

39.图7是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的设备的示意图。

具体实施方式

40.下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。

41.应当理解,本发明的权利要求、说明书及附图中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。本发明的说明书和权利要求书中使用的术语“包括”和“包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

42.还应当理解,在此本发明说明书中所使用的术语仅仅是出于描述特定实施方式的

目的,而并不意在限定本发明。如在本发明说明书和权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。还应当进一步理解,在本发明说明书和权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

43.如在本说明书和权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当...时”或“一旦”或“响应于确定”或“响应于检测到”。类似地,短语“如果确定”或“如果检测到[所描述条件或事件]”可以依据上下文被解释为意指“一旦确定”或“响应于确定”或“一旦检测到[所描述条件或事件]”或“响应于检测到[所描述条件或事件]”。

[0044]

下面结合附图来详细描述本发明的具体实施方式。

[0045]

内存屏障指令类与其它传统指令不同,它的运行并不涉及处理器管脚更改电平的逻辑,其测试方法无法通过直接测量管教高低电平直接体现,只有在相应的指令级逻辑发生变化时才会予以体现,具有一定的隐蔽性。而且目前cpu制造商由于商业机密以及安全性的需求,均不会公开其内部检测机制以及检测方法,因而需要经过精巧的设计才能发现其设计缺陷。本发明的方案中通过提供一种用于对内存屏障指令的有效性进行检测的方案,从而在不知晓源码的基础上实现对cpu中内存屏障指令是否正确执行进行判断,有效提升了计算机系统运行的安全性和可靠性。

[0046]

图1是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的方案的场景100示意图。根据本发明的上下文,对cpu中内存屏障指令的有效性进行判定时,需要形成一个计算机的整体框架。该整体框架可以分为以下几个功能模块:“硬件支撑模块”、“内核”、“c 语言支撑模块”、“优化编译器”、“负载压力生成器”以及“内存屏障验证代码库”。

[0047]

硬件支撑模块主要包括主板、cpu插槽、物理内存、ssd硬盘。硬件支撑模块作为通用硬件,可以支撑cpu的验证工作,其作用为现有技术,此处不再赘述。内核是指操作系统内核,其主要作用在于硬件支撑、调度、进程管理以及内存管理,本方案中主要使用通用linux kernel。c语言支撑模块是在c语言中包装了cpu带有内存屏障指令内嵌汇编的函数,由于本方案测试时采用c语言作为验证程序的基础,因而需要通用c语言支撑库进行函数支撑。可以理解,也可以采用其他编程语言作为验证程序的基础,相应地可以包括其编程语言的支撑模块,本发明实施例在此方面没有限制。优化编译器在编译过程中需要禁止进行任何优化。程序编译时关闭所有优化选项,并且可以在验证指令生成时增加调试符号插桩环节,以实现对运行过程的可视化。内存屏障验证代码库是验证内存屏障指令的c 语言代码库,主要分为对8类程序结构进行检测的程序:顺序结构屏障检测,循环结构屏障检测,判断结构屏障检测,队列\栈结构屏障检测,树形结构屏障检测,有向图结构屏障检测,无向图结构屏障检测,嵌套结构屏障检测。

[0048]

本发明中为了示例性的目的在图1中仅示出了内存屏障验证代码库 101、编译器102和cpu103的结构。该内存屏障验证代码库101中包括用于验证各种内存屏障指令的有效性的验证代码集,该编译器102为前文中描述的优化编译器,在验证过程中需要禁用其优化功能。

[0049]

如图1所示,通过该内存屏障验证代码库101中的验证代码集,可以根据各种程序结构的配置信息生成指令子集,一个或多个指令子集可以组成验证指令,以利用cpu103执

行该验证指令,实现有效性检测过程。

[0050]

编译器102在获取该验证指令后,可以将该验证指令转为cpu能够识别的机器指令码,以便于cpu执行后输出执行结果。

[0051]

cpu103根据对验证指令的执行过程输出执行结果,将该执行结果与该验证指令对应的标准结果进行比较后,可以根据比较结果确定该cpu 中内存屏障指令是否失效。

[0052]

图2是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的方法200的流程图。

[0053]

如图2所示,在步骤s201处,获取验证指令。该验证指令可以包括基于验证代码集中各种程序结构的配置信息生成的一个或多个指令子集,每个指令子集中包含内存屏障指令。在一些实施例中,该程序结构可以包括以下类型中的一种或多种:顺序结构、循环结构、判断结构、队列结构、栈结构、树形结构、图形结构和嵌套结构,其中所述图形结构包括无向图结构和有向图结构。

[0054]

在步骤s202处,利用cpu运行验证指令,以生成对验证指令的执行结果。在一些实施例中,cpu在运行时,可以根据验证指令的类型仅对其中一种程序结构中的内存屏障指令进行验证,也可以分别对多种程序结构中的内存屏障指令进行验证。

[0055]

在步骤s203处,将cpu对验证指令的执行结果与验证指令对应的标准结果进行比对。在一些实施例中,可以通过统计在一段时间内的执行结果与标准结果的相同的次数和不同的次数,作为比对结果。

[0056]

在步骤s204处,响应于cpu对验证指令的执行结果与验证指令对应的标准结果不同,确定cpu中内存屏障指令失效。在一些实施例中,可以在cpu对验证指令的执行结果与验证指令对应的标准结果不同时,就判定该cpu中内存屏障指令失效。也可以根据前述统计的在一段时间内的执行结果与标准结果的相同的次数和不同的次数进行判断。例如在一段时间内,相同的次数的占比为99%,则可以认为该内存屏障指令能够有效执行,否则确定cpu中内存屏障指令失效。

[0057]

图3是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的另一种方法300的流程图。

[0058]

如图3所示,在步骤s301处,从预设的验证代码集中选择一种或多种程序结构的代码信息。在一些实施例中,前述内存屏障验证代码库中包含多种程序结构的代码信息,在生成验证指令的过程中,可以选择其中的一种或多种的程序机构的代码信息,以生成对应程序结构中内存屏障指令对应的验证代码。

[0059]

在步骤s302处,基于每种程序结构的代码信息生成指令子集,以形成用于对内存屏障的有效性进行验证的验证指令。在一些实施例中,每种程序结构的代码信息结合程序结构的配置信息可以生成对应程序结构的指令子集,该一个或多个指令子集可以形成用于对内存屏障的有效性进行验证的验证指令。

[0060]

在实际操作中,在cpu执行指令代码前,编译器同样会对指令代码进行优化,为了实现对cpu中内存屏障指令的有效性的准确检测,需要禁用编译器的优化功能。因此,在将前述验证指令输入cpu之前,在步骤s303处,禁用编译器的优化选项,以避免编译器对所述验证指令进行优化。

[0061]

接着,在步骤s304处,将验证指令输入编译器,以将验证指令转换为cpu能够识别

的二进制指令。

[0062]

然后,在步骤s305处,按照程序结构的复杂度从小到大的顺序分别将对应的指令子集进行排序。在一些实施例中,按照程序结构的复杂度从小到大,可以分为顺序结构、循环结构、判断结构、队列结构、栈结构、树形结构、图形结构和嵌套结构,其中所述图形结构包括无向图结构和有向图结构。基于上述顺序,可以设置验证指令中不同程序结构验证时的优先级。

[0063]

在步骤s306处,利用cpu根据排序分别运行每种程序结构对应的指令子集,以生成对应的执行结果。在一些实施例中,若其中一种程序结构对应的指令子集的运行结果与标准结果不符,就可以判定该cpu中内存屏障指令无法正常运行。此时为了实现对cpu全面的检测,仍然对每种程序结构对应的指令子集进行验证。

[0064]

进一步,前述指令子集中还可以包括探针,以探测cpu运行过程中的数据信息。在步骤s307处,利用探针可以获取验证指令在cpu中运行时的数据流信息,以便对cpu的处理过程进行监测。在一些实施例中,可以通过编译时的程序插桩过程在代码中插入探针,从而实现对cpu中程序运行时的内存监控、指令跟踪、错误检测等。

[0065]

更进一步,在步骤s308处,对cpu进行加压检测,以判断内存屏障指令在设定压力时的有效性。在一些实施例中,可以利用负载压力生成器增加cpu运算的压力。由于cpu会运转在多种模式,其负载在高负荷运算模式下,可能会以更高的方式优化运算逻辑,造成指令级的重排,或忽视内存屏障指令的有效性,因而需要对运算中cpu的负荷进行人为的调节,以判断cpu在不同负载压力的情况下是否能够正常运行内存屏障指令。

[0066]

在一些实施例中,对cpu进行加压检测以判断内存屏障指令在设定压力时的有效性时,首先对cpu的负载压力进行检测,以判断cpu的负载压力是否大于设定压力。当负载压力低于设定压力时,提升cpu的负载压力,以将cpu的负载压力提升至设定压力。通过加压检测过程还可以测试在高压下cpu能够正常运行内存屏障指令,从而实现对cpu的更加全面的检测,保证计算机系统的安全性。

[0067]

接下来将分别结合cpu中各种程序结构中的内存屏障指令的有效性检测过程,对本发明一个或多个实施例中所述的方法进行阐述。具体地,该验证指令根据指令子集的执行顺序,可以包括顺序结构屏障检测、循环结构屏障检测、判断结构屏障检测、队列结构屏障检测、栈结构屏障检测、树形结构屏障检测、无向图结构屏障检测、有向图结构屏障检测和嵌套结构屏障检测。

[0068]

第一种是顺序结构屏障检测,指的是在顺序执行的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。例如以下表5中的顺序程序结构包括顺序逻辑语句1-10。

[0069]

表5:

[0070][0071]

可以看出,其中在顺序逻辑语句4和顺序逻辑语句5之间设置有内存屏障指令1,在顺序逻辑语句7和顺序逻辑语句8之间设置有内存屏障指令2。基于此,在执行结果中将主要观测顺序逻辑语句1-4、5-7和8-10 三组顺序程序结构的逻辑正确性。

[0072]

第二种是循环结构屏障检测,指的是在循环结构的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。如下6示出了循环结构的两种样例。

[0073]

表6:

[0074][0075]

[0076]

可以看出,其中在循环结构样例1中,do-while语句之外的顺序逻辑语句2和顺序逻辑语句3之间设置有内存屏障指令1,顺序逻辑语句10 和顺序逻辑语句11之间设置有内存屏障指令3。在循环逻辑语句中,逻辑语句6和逻辑语句7之间设置有内存屏障指令2。基于此,在执行结果中除了观测顺序逻辑语句中程序结构的逻辑正确性,还观测循环逻辑语句中程序结构的逻辑正确性。

[0077]

第三种是判断结构屏障检测,指的是在判断结构的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。如下表7中示出了判断结构的两种样例。

[0078]

表7:

[0079][0080][0081]

可以看出,其中在判断结构样例1中,if-else语句之外的顺序逻辑语句2和顺序逻辑语句3之间设置有内存屏障指令1,顺序逻辑语句14和顺序逻辑语句15之间设置有内存屏

障指令4。在判断逻辑语句中,逻辑语句6和逻辑语句7之间设置有内存屏障指令2,逻辑语句12和逻辑语句13 之间设置有内存屏障指令3。基于此,在执行结果中除了观测顺序逻辑语句中程序结构的逻辑正确性,还观测判断逻辑语句中程序结构的逻辑正确性。

[0082]

第四种是队列/栈结构屏障检测,指的是在队列/栈结构的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。如下内容中分别示出了队列结构和栈结构中内存屏障指令的设置位置。

[0083]

队列结构:

[0084]

······

[0085]

待入队队列语句7

[0086]

队列语句6队列语句5内存屏障指令2队列语句4队列语句3内存屏障指令1队列语句2队列语句1

[0087]

可以看出,队列结构中队列语句2和队列语句3之间设置有内存屏障指令1,队列结构中队列语句4和队列语句5之间设置有内存屏障指令2。基于此,在执行结果中需要观测队列语句1-2、3-4和5-6三组队列语句的逻辑正确性。

[0088]

栈结构:

[0089]

入栈语句 出栈语句

[0090]

栈顶

[0091]

[0092][0093]

栈底

[0094]

可以看出,栈结构中队列语句2和队列语句3之间设置有内存屏障指令1,队列结构中队列语句4和队列语句5之间设置有内存屏障指令2,队列结构中队列语句7和队列语句8之间设置有内存屏障指令3。基于此,在执行结果中需要观测队列语句1-2、3-4、5-7和8-9三组队列语句的逻辑正确性。

[0095]

第五种是树形结构屏障检测,指的是在树形结构的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。图4是示意性示出根据本发明的实施例的树形程序结构中内存屏障指令的示意图。

[0096]

第六种是图形结构屏障检测,指的是在图形结构的程序逻辑中插入内存屏障指令,观测内存屏障指令执行的效果。该图形结构可以包括无向图结构和有向图结构。图5是示意性示出根据本发明的实施例的无向图程序结构中内存屏障指令的示意图。如图5所示,可以在各程序逻辑间插入内存屏障指令,以实现对其中内存屏障指令的有效性的验证。图6是示意性示出根据本发明的实施例的有向图程序结构中内存屏障指令的示意图。如图6所示,在有向图程序结构中各程序逻辑之间均设置有内存屏障指令,以对其中内存屏障指令的有效性进行验证。进一步,还可以包括嵌套结构屏障检测,其是指综合上述2种以上程序逻辑的混合使用,在多层嵌套中随机加入内存屏障指令以验证其逻辑的正确性。

[0097]

图7是示意性示出根据本发明的实施例的用于对内存屏障指令有效性进行验证的设备700的示意图。该用于对内存屏障指令有效性进行验证的设备700可以包括根据本发明实施例的设备701以及其外围设备和外部网络。如前所述,该设备701实现获取验证指令、将验证指令输入cpu、将执行结果与标准结果进行比较等操作,以实现前述结合图2或图3所述的本发明的方案。

[0098]

如图7中所示,设备701可以包括cpu7011,其可以是通用cpu、专用cpu或者其他信息处理以及程序运行的执行单元。进一步,设备701 还可以包括大容量存储器7012和只读存储器rom 7013,其中大容量存储器7012可以配置用于存储各类数据以及多媒体网络所需的各种程序, rom 7013可以配置成存储对于设备701的加电自检、系统中各功能模块的初始化、系统的基本输入/输出的驱动程序及引导操作系统所需的数据。

[0099]

进一步,设备701还包括其他的硬件平台或组件,例如示出的tpu (tensor processing unit,张量处理单元)7014、gpu(graphic processingunit,图形处理器)7015、fpga(field programmable gate array,现场可编程逻辑门阵列)7016和mlu(memory logic unit),存储器逻辑单元) 7017。可以理解的是,尽管在设备701中示出了多种硬件平台或组件,但这里仅仅是示例性的而非限制性的,本领域技术人员可以根据实际需要增加

或移除相应的硬件。例如,设备701可以仅包括cpu作为公知硬件平台和另一硬件平台作为本发明的测试硬件平台。

[0100]

本发明的设备701还包括通信接口7018,从而可以通过该通信接口 7018连接到局域网/无线局域网(lan/wlan)705,进而可以通过 lan/wlan连接到本地服务器706或连接到因特网(“internet”)707。替代地或附加地,本发明的设备701还可以通过通信接口7018基于无线通信技术直接连接到因特网或蜂窝网络,例如基于第三代(“3g”)、第四代 (“4g”)或第5代(“5g”)的无线通信技术。在一些应用场景中,本发明的设备701还可以根据需要访问外部网络的服务器708以及可能的数据库709。

[0101]

设备701的外围设备可以包括显示装置702、输入装置703以及数据传输接口704。在一个实施例中,显示装置702可以例如包括一个或多个扬声器和/或一个或多个视觉显示器。输入装置703可以包括例如键盘、鼠标、麦克风、姿势捕捉相机,或其他输入按钮或控件,其配置用于接收数据的输入或用户指令。数据传输接口704可以包括例如串行接口、并行接口或通用串行总线接口(“usb”)、小型计算机系统接口(“scsi”)、串行ata、火线(“firewire”)、pci express和高清多媒体接口(“hdmi”) 等,其配置用于与其他设备或系统的数据传输和交互。

[0102]

本发明的设备701的上述cpu 7011、大容量存储器7012、只读存储器rom 7013、tpu 7014、gpu 7015、fpga 7016、mlu 7017和通信接口7018可以通过总线7019相互连接,并且通过该总线与外围设备实现数据交互。在一个实施例中,通过该总线7019,cpu 7011可以控制设备701 中的其他硬件组件及其外围设备。

[0103]

在工作中,本发明的设备701的处理器cpu 7011可以通过输入装置 703或数据传输接口704获取媒体数据包,并调取存储于存储器7012中的计算机程序指令或代码对内存屏障指令有效性进行验证。

[0104]

从上面关于本发明模块化设计的描述可以看出,本发明的系统可以根据应用场景或需求进行灵活地布置而不限于附图所示出的架构。进一步,还应当理解,本发明示例的执行操作的任何模块、单元、组件、服务器、计算机或设备可以包括或以其他方式访问计算机可读介质,诸如存储介质、计算机存储介质或数据存储设备(可移除的)和/或不可移动的)例如磁盘、光盘或磁带。计算机存储介质可以包括以用于存储信息的任何方法或技术实现的易失性和非易失性、可移动和不可移动介质,例如计算机可读指令、数据结构、程序模块或其他数据。基于此,本发明也公开了一种计算机可读存储介质,其上存储有用于对内存屏障指令有效性进行验证的方法的计算机可读指令,该计算机可读指令被一个或多个处理器执行时,实现在前结合附图所描述的方法和操作。

[0105]

虽然本说明书已经示出和描述了本发明的多个实施方式,但对于本领域技术人员显而易见的是,这样的实施方式是仅以示例的方式提供的。本领域技术人员在不偏离本发明思想和精神的情况下想到许多更改、改变和替代的方式。应当理解在实践本发明的过程中,可以采用本文所描述的本发明实施方式的各种替代方案。所附权利要求书旨在限定本发明的保护范围,并因此覆盖这些权利要求范围内的模块组成、等同或替代方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1