用于IP单元级别验证的总线驱动式芯片仿真激励模型的制作方法

用于ip单元级别验证的总线驱动式芯片仿真激励模型

技术领域

1.本发明涉及芯片仿真技术领域,具体而言,涉及一种用于ip单元级别验证的总线驱动式芯片仿真激励模型,更具体地是一种通过软件架构/驱动抽象层将任意设备驱动软件用于ip单元级别验证的总线驱动式芯片仿真激励模型。

背景技术:

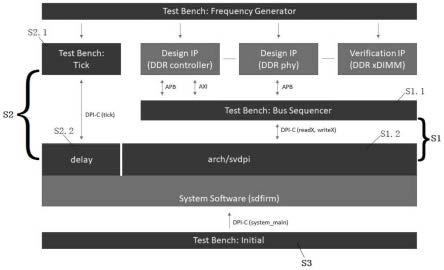

2.ip(intellectual property core)又称为ip核,是芯片中具有独立功能的电路模块的成熟设计,常见的ip单元级别验证通常为使用uvm(universal verification methodology,通用验证方法学)总线激励控制ip的寄存器接口,一个测试机台(test bench)包括被测试的设计ip(如图1中的design ip)、验证ip(如图1中verification ip)和总线功能模型(bus function model)的总线激励序列,总线功能在测试机台产生的时钟频率(frequency generator)下工作以驱动被测试的设计ip和验证ip交互,通过验证ip检查设计ip的功能是否正常。

3.然而,常用的开源操作系统如linux通常只能支持一种cpu体系结构抽象,因此无法将任意设备的驱动软件直接用作芯片仿真用的总线功能模型激励。

技术实现要素:

4.为解决上述问题,本发明提供一种用于ip单元级别验证的总线驱动式芯片仿真激励模型,通过dpi(direct programming interface)接口实现一种cpu体系结构抽象的软件层来转换开源操作系统中的硬件驱动,用作芯片仿真用的总线功能模型激励,由于所采用的native c(c语言实现的本地方法)相比于uvm方法速度更快,因此还可以比传统的uvm方法提供加快50%的仿真速度。

5.为达到上述目的,本发明提供了一种用于ip单元级别验证的总线驱动式芯片仿真激励模型,其通过以下过程实现:

6.步骤s1:替换系统软件驱动程序的io寄存器访问序列;

7.步骤s2:替换驱动程序的寄存器定时时序保证功能;

8.步骤s3:替换测试机台的测试激励初始化过程,并直接调用系统软件的验证程序入口。

9.在本发明一实施例中,其中,步骤s1包括:

10.步骤s1.1:使用verilog语言实现和ip仿真频率关联的总线master读写任务;

11.步骤s1.2:通过systemverilog的dpi接口将总线master读写任务转换成c语言能够调用的io读写函数;

12.步骤s1.3:采用如下方法实现对ip对外的多个地址空间的同一寄存器偏移的访问:

13.为不同的地址空间指定不同的基址,然后在任一读/写的rtl序列中根据传入的地址不同,调用不同的总线master读写任务,即在rtl中增加地址译码;或者

14.提供不同的总线master读写任务,并将其表现为不同的c语言函数,再到c语言端根据不同基址调用不同地址空间;

15.步骤s1.4:监控在io读写函数被c语言调用时,verilog语言中是否有时序操作能够推动芯片仿真的循环向前推进执行。

16.在本发明一实施例中,其中,步骤s2包括:

17.步骤s2.1:用verilog语言实现和ip仿真频率关联的计数器;

18.步骤s2.2:通过systemverilog的dpi接口将计数器转换成c语言能够调用的定时函数;

19.步骤s2.3:监控在定时器函数被c语言调用时,verilog语音中是否有时序操作能够做到推动芯片仿真的循环向前推进执行。

20.在本发明一实施例中,其中,所述系统软件需要具备以下特点:

21.所述系统软件包含体系结构抽象层;

22.所述系统软件包含硬件驱动抽象层;及/或

23.所述系统软件包含可配置的能力。

24.本发明提供的用于ip单元级别验证的总线驱动式芯片仿真激励模型,相较于现有技术,至少具备以下优点:

25.1)通过增加时钟滴答(tick)硬件,以实现系统软件的定时(delay)功能;

26.2)通过转换总线功能模型的总线序列(bus sequencer),实现系统软件的io访问(read、write)功能;

27.3)通过增加测试机台的初始化流程,能够直接通过dpi接口调用系统软件的测试入口;

28.4)本发明的测试机台的频率发生器能够为时钟滴答(tick)硬件和总线序列(bus sequencer)硬件提供参考时钟。

附图说明

29.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

30.图1为本发明一实施例的模型架构示意图。

具体实施方式

31.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

32.通常情况下,一个驱动程序主要包含寄存器io(输入输出)访问序列(read、write)、寄存器访问之间的时序保证(delay)。因此,本实施例通过增加以下几个系统软件和ip单元级别验证测试机台结合时各自需要修改的配置的部分,实现直接操作ip硬件:

33.1)增加时钟滴答(tick)硬件,允许系统软件通过dpi接口访问时钟滴答(tick)硬件,来获取仿真环境的参考时间以实现系统软件的定时(delay)功能;

34.2)转换总线功能模型的总线序列(bus sequencer),允许系统软件通过dpi接口访问这个总线序列来实现系统软件的io访问(read、write)功能;

35.3)增加测试机台的初始化流程,直接通过dpi接口调用系统软件的测试入口;

36.4)测试机台的频率发生器需要为时钟滴答(tick)硬件和总线序列(bus sequencer)硬件提供参考时钟。

37.图1为本发明一实施例的模型架构示意图,如图1所示,本实施例提供用于ip单元级别验证的总线驱动式芯片仿真激励模型,其通过以下过程实现:

38.步骤s1:替换系统软件驱动程序的io寄存器访问序列;

39.在本实施例中,其中,步骤s1包括:

40.步骤s1.1:使用verilog语言实现和ip仿真频率关联的总线master(可视为主控部分)读写任务;参见图1中对test bench:bus sequencer的修改,其中verilog语言一般指verilog hdl,是一种硬件描述语言(hdl:hardware description language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

41.步骤s1.2:通过systemverilog的dpi接口将总线master读写任务转换成c语言能够调用的io读写函数;例如可以转换为readb、readw、readl、writeb、writew、writel等,参见图1中对arch/svdpi的修改,其中systemverilog简称为sv语言,是一种建立在verilog语言的基础上的语言。

42.步骤s1.3:采用如下方法实现对ip对外的多个地址空间的同一寄存器偏移的访问:

43.为不同的地址空间指定不同的基址,然后在任一读/写(readx、writex)的rtl(register transfer level,称为寄存器转换级电路,也叫暂存器转移层次)序列中根据传入的地址不同,调用不同的总线master读写任务,即在rtl中增加地址译码;或者

44.提供不同的总线master读写任务,并将其表现为不同的c语言函数,例如ahb_writex、ahb_readx、axi_writel、axi_readx,再到c语言端根据不同基址调用不同地址空间;

45.由于一个ip对外可以有多个地址空间,例如ddr的配置空间是ahb,ddr的数据空间是axi。而ip单元级别验证时候,是没有基址,只有寄存器偏移的概念,因此,这时候需要区分对不同地址空间的同一个寄存器偏移的访问。

46.步骤s1.4:监控在io读写函数被c语言调用时,verilog语言中是否有时序操作能够推动芯片仿真的循环(cycle)向前推进执行。

47.由于c语言在被调用时是systemverilog规范规定的监控周期,仿真频率的cycle并不会往前推进,因此需要注意当实现io读写函数被c语言调用时,verilog中有时序操作能够做到推动芯片仿真的cycle往前走。

48.通过上述步骤s1的替换,完成了的过程转换总线功能模型的总线序列(bus sequencer)。

49.步骤s2:替换驱动程序的寄存器定时时序保证功能;

50.在本实施例中,其中,步骤s2包括:

51.步骤s2.1:用verilog语言实现和ip仿真频率关联的计数器;参见图1中对test bench:tick的修改。

52.步骤s2.2:通过systemverilog的dpi接口将计数器转换成c语言能够调用的定时函数;例如可以为tick函数,参见图1中对delay的修改。

53.步骤s2.3:监控在定时器函数被c语言调用时,verilog语音中是否有时序操作能够做到推动芯片仿真的循环(cycle)向前推进执行。

54.由于c语言被调用时是systemverilog规范规定的监控周期,仿真频率的cycle并不往前推进,因此需要注意当实现定时器函数被c语言调用时,verilog中有时序操作能够做到推动芯片仿真的cycle往前走,否则单纯的c语言连续调用定时函数(如tick函数)来实现寄存器访问之间的时序保证(delay)将永远不会达成时序要求跑死(死循环)。

55.通过步骤s2的替换,完成了增加了模型中时钟滴答(tick)硬件的过程。

56.步骤s3:替换测试机台的测试激励初始化过程,并直接调用系统软件的验证程序入口;程序入口例如可为system_main,参见图1中对test bench:initial的修改。

57.由于本实施例的方法可以与任何不带中断处理的系统软件(例如bootloader都不开中断的状态)结合,因此更进一步地,如果系统软件(system software)具备以下特性,则移植会非常容易。

58.通过上述步骤s3,完成了增加测试机台的初始化流程的过程。

59.本实施例中,其中,所述系统软件需要具备以下特点:

60.系统软件包含体系结构抽象层;通常体系结构抽象度高的系统软件都有体系结构特定目录,例如linux内核的arch/arm64、arch/riscv目录,在这类系统软件中实现一个仿真用的体系结构,例如arch/svdpi来包含步骤s1描述中的寄存器io访问替换的实现,arch/svdpi需要的其他功能用调用本地主机(例如x86服务器)c库的功能模拟实现,类似于(linux内核的um模拟器);

61.系统软件包含硬件驱动抽象层;通常驱动抽象高的系统软件允许增加特定定时硬件实现,例如linux内核的drivers/clocksource目录,在这类系统软件中实现一个仿真用的定时硬件来包含步骤s2描述中的寄存器定时时序替换的实现;及/或

62.系统软件包含可配置的能力。系统软件最好包含强大的可配置能力,这样针对目标ip做最小配置,仅包含dpi接口架构、被测试硬件ip、验证ip的驱动和对应协议栈、系统入口system_main可以被配置为适用于仿真激励的测试程序入口,这样当系统软件和仿真硬件结合时能够实现最高的执行效率。

63.本发明提供的用于ip单元级别验证的总线驱动式芯片仿真激励模型,相较于现有技术,至少具备以下优点:通过增加时钟滴答(tick)硬件,以实现系统软件的定时(delay)功能;通过转换总线功能模型的总线序列(bus sequencer),实现系统软件的io访问(read、write)功能;通过增加测试机台的初始化流程,能够直接通过dpi接口调用系统软件的测试入口;4)本发明的测试机台的频率发生器还能够为时钟滴答(tick)硬件和总线序列(bus sequencer)硬件提供参考时钟。

64.本领域普通技术人员可以理解:附图只是一个实施例的示意图,附图中的模块或流程并不一定是实施本发明所必须的。

65.本领域普通技术人员可以理解:实施例中的装置中的模块可以按照实施例描述分布于实施例的装置中,也可以进行相应变化位于不同于本实施例的一个或多个装置中。上述实施例的模块可以合并为一个模块,也可以进一步拆分成多个子模块。

66.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1