一种AIS航标基站的制作方法

一种ais航标基站

技术领域

1.本实用新型涉及船舶通讯技术领域,特别是一种ais航标基站。

背景技术:

2.船舶自动识别系统(automatic identification system,简称ais系统),由岸基(基站)设施和船载设备共同组成,是一种新型的集网络技术、现代通讯技术、计算机技术、电子信息显示技术为一体的数字助航系统和设备。ais系统配合全球定位系统(gps)将船位、船速、改变航向率及航向等船舶动态结合船名、呼号、吃水及危险货物等船舶静态资料由甚高频(vhf)向附近水域船舶及岸台广播,使邻近船舶及岸台能及时掌握附近海面所有船舶之动静态资讯,得以立刻互相通话协调,采取必要避让行动,有效保障船舶航行安全。

3.随着航运业的不断发展,传统ais设备缺乏更新,无法通过网口直连电脑进行数据交互,从而无法远程修改ais发射的报文数据,也不能实现定时回传状态信息以及响应远程控制指令,无法实现发射多个不同身份编码的ais报文信息,难以满足日益增长的航标导航需求。

技术实现要素:

4.本实用新型的目的在于提供一种ais航标基站,能够通过网口进行远程接收、发送ais报文。

5.本实用新型提供如下技术方案:一种ais航标基站,包括位于基站内部用于给主芯片模块供电的供电模块,所述供电模块包括ac/dc切换模块、电源滤波模块以及降压模块,其特征在于:还包括主芯片模块,所述主芯片模块连接有ais射频模块、以太网模块,所述ais射频模块与ais射频天线连接,所述以太网模块与基站终端通信连接,基站终端通过所述以太网模块将ais报文传输给所述主芯片模块,所述主芯片模块通过所述ais射频模块将ais报文发送给船舶。

6.进一步的,所述主芯片模块包括u4芯片、u5芯片、晶振y3、电阻r53、电阻r54、电阻r61、电阻r62、电阻r63、电阻r64、电阻r65、电阻r66、电阻r67、电阻r68、电阻r69、电阻r70、电阻r71、电阻r72、电阻r73、电阻r74、电阻r75、电阻r76、电阻r77、电容c1、电容c2、电容c3、电容c4、电容c19、电容c20、电容c21、电容c22、电容c23、电容c24、电容c35、电容c36、电容c37、电容c40、电容c41、电容c42、电容c43、电容c44、电容c45、电感l1、二极管d1、二极管d2、三极管q1、插座p1、插座p2,所述u4芯片的6号引脚与所述电容c1的一端连接后与3.3v电源连接,所述电容c1的另一端接地,所述u4芯片的19号引脚与所述电容c19的一端、所述电容c2的一端、所述电容c20的一端、所述电容c3的一端、所述电容c21的一端、所述电容c4的一端、所述电容c22的正极连接后与.3.v电源连接,所述电容c19的另一端与所述电容c2的另一端、所述电容c20的另一端、所述电容c3的另一端、所述电容c21的另一端、所述电容c4的另一端连接后接地,所述电容c22的负极接地,所述u4芯片的19号引脚与所述u4芯片的11号引脚、所述u4芯片的28号引脚、所述u4芯片的50号引脚、所述u4芯片的75号引脚、所述u4芯

片的100号引脚连接,所述u4芯片的10号引脚接地,所述u4芯片的27号引脚接地,所述u4芯片的74号引脚接地,所述u4芯片的99号引脚与所述电阻r61的一端、所述电阻r62的一端连接,所述电阻r61的另一端与3.3v电源连接,所述电阻r62的另一端接地,所述u4芯片的22号引脚与所述u4芯片的23号引脚连接后与所述电容c23的一端、所述电容c24的一端、所述电容c35的一端、所述电感l1的一端连接,所述u4芯片的20号引脚与所述电容c23的另一端、所述电容c24的另一端、所述电容c35的另一端连接后接地,所述电感l1的另一端与所述电容c36的正极连接后与3.3v电源连接,所述电容c36的负极接地,所述u4芯片的49号引脚与所述电容c37的一端连接,所述u4芯片的73号引脚与所述电容c40的一端连接,所述电容c37的另一端与所述电容c40的另一端连接后接地,所述u4芯片的14号引脚与所述电容c44的一端、所述电阻r65的一端连接,所述电容c44的另一端接地,所述电阻r65的另一端与3.3v电源连接,所述u4芯片的94号引脚与所述电阻r70的一端、所述插座p1的1号引脚连接,所述电阻r70的另一端接地,所述插座p1的2号引脚与3.3v电源连接,所述u4芯片的57号引脚与所述电阻r53的一端连接,所述电阻r53的另一端与所述电阻r54的一端、所属电容c45的一端、所述三极管q1的2号引脚连接,所述电阻r54的另一端接地,所述电容c45的另一端接地,所述三极管q1的1号引脚接地,所述三极管q1的3号引脚与所述二极管d2的负极连接,所述二极管d2的正极与所述电阻r64的一端连接,所述电阻r64的另一端与24v电源连接,所述u4芯片的1号引脚与所述二极管d1的负极连接,所述二极管d1的正极与所述电阻r63的一端连接,所述电阻r63的另一端与3.3v电源连接,所述u4芯片的37号引脚与所述电阻r71的一端连接,所述电阻r71的另一端接地,所述u4芯片的72号引脚与所述插座p2的2号引脚、电阻r68的一端连接,所述u4芯片的76号引脚与所述插座p2的3号引脚、所述电阻r67的一端连接,所述插座p2的1号引脚与所述电阻r69的一端连接,所述插座p2的4号引脚接地,所述插座p2的5号引脚与所述电阻r66的一端连接,所述电阻r66的另一端与所述电阻r67的另一端、所述电阻r68的另一端、所述电阻r69的另一端连接后与3.3v电源连接,所述u4芯片的12号引脚与所述晶振y3的一端、所述电容c41的一端连接,所述u4芯片的13号引脚与所述晶振y3的另一端、所述电容c42的一端连接,所述电容c41的另一端与所述电容c42的另一端连接后接地,所述芯片u5的1号引脚与所述电阻r77的一端连接,所述u5芯片的2号引脚与所述电阻r76的一端连接,所述u5芯片的3号引脚与所述电阻r75的一端连接,所述u5芯片的4号引脚与所述电阻r74的一端连接,所述电阻r74的另一端与所述电阻r75的另一端、所述电阻r76的另一端、所述电阻r77的另一端连接后与3.3v电源连接,所述u5芯片的7号引脚接地,所述u5芯片的8号引脚与所述u5芯片的电阻r72的一端连接,所述u5芯片的5号引脚与所述电阻r73的一端连接,所述u5芯片的6号引脚与所述电容c43的一端、所述电阻r73的另一端、所述电阻r72的另一端连接后与3.3v电源连接,所述电容c43的另一端接地,所述u5芯片的1号引脚与所述u4芯片的91号引脚连接,所述u5芯片的2号引脚与所述u4芯片的89号引脚连接,所述u5芯片的3号引脚与所述u4芯片的92号引脚连接,所述u5芯片的4号引脚与所述u4芯片的77号引脚连接,所述u5芯片的8号引脚与所述u4芯片的90号引脚连接。

7.进一步的,所述ais射频模块包括u1芯片、u10芯片、晶振y1、电阻r26、电阻r27、电阻r34、电阻r42、电容c5、电容c6、电容c7、电容c8、电容c9、电容c10、电容c11、电容c16、电容c17、电容c18、电容c39、电容c49、电容c50、电容c51、电容c52、电容c53、电容c54、电容c55、电容c61、电容c62、电容c63、电容c84、电容c85、电容c86、电感l8、电感l9、电感l10、电感

l11、电感l12、电感l17、晶体管q2、插头cn4,所述u1芯片的6号引脚与所述u1芯片的8号引脚、所述电容c10的一端、所述电容c9的一端、所述电容c7的一端、所述电容c6的一端连接后与电源连接,所述电容c6的另一端接地,所述电容c7的另一端接地,所述电容c9的另一端接地,所述电容c10的另一端接地,所述u1芯片的11号引脚与所述u4芯片的35号引脚连接,所述u1芯片的12号引脚与所述u4芯片的36号引脚连接,所述u1芯片的13号引脚所述u4芯片的95号引脚连接,所述u1芯片的14号引脚与所述u4芯片的96号引脚连接,所述u1芯片的15号引脚与所述u4芯片的47号引脚连接,所述u1芯片的1号引脚与所述u1芯片的18号引脚连接后接地,所述u1芯片的17号引脚与所述电容c16的一端连接,所述电容c16的另一端与所述晶振y1的3号引脚连接,所述晶振y1的2号引脚接地,所述晶振y1的1号引脚接地,所述晶振y1的四号引脚与所述电容c17的一端、所述电感l17的一端连接,所述电容c17的另一端接地,所述电感l17的另一端与所述电容c18的一端连接后与电源连接,所述电容c18的另一端接地,所述u1芯片的4号引脚与所述电容c5的一端、所述电感l4的一端连接,所述电感l4的另一端与所述电容c2的一端连接后与电源连接,所述电容c2的另一端接地,所述电容c5的另一端与所述电感l12的一端连接,所述电感l12的另一端与所述电容c11的一端、所述电阻r27的一端、所述电阻r34的一端连接,所述电容c11的另一端接地,所述电阻r27的另一端接地,所述电阻r34的另一端与所述电阻r26的一端、所述电容c55的一端连接,所述电阻r26的另一端接地,所述电容c55的另一端与所述电容c39的一端、所述电容c54的一端连接,所述电容c39的另一端接地,所述电容c54的另一端与所述u10芯片的1号引脚连接,所述u10的2号引脚接地,所述u10的3号引脚与所述电容c53的一端连接,所述电容c53的另一端与所述电容c52的一端、所述电容c51的一端连接,所述电容c52的另一端接地,所述电容c51的另一端与所述电容c50的一端连接,所述电容c50的另一端与所述晶体管q2的1号引脚连接,所述u10的3号引脚与所述电感l10的一端、所述电阻r42的一端连接,所述电阻r42的另一端与所述电感l10的另一端、所述电感l11的一端、所述电容c76的一端连接,所述电容c76的另一端接地,所述电感l11的另一端与所述电感l8的一端连接后与电源连接,所述电感l8的另一端与所述电容c84的一端、所述电容c85的一端、所述电容c86的一端、所述电感l9的一端连接,所述电容c84的另一端与所述电容c85的另一端、所述电容c86的另一端连接后接地,所述电感l9的另一端与所述电容c49的一端、所述电感l5的一端、所述晶体管q2的2号引脚连接,所述电容c49的另一端接地,所述晶体管q2的3号引脚接地,所述电感l5的另一端与所述电容c61的一端、所述电容c62的一端、所述电容c63的一端连接,所述电容c62的另一端与所述电容c63的另一端连接后接地,所述电容c61的另一端与所述插头cn4连接。

8.进一步的,所述以太网模块包括u2芯片、u3芯片、晶振y2、电阻r35、电阻r36、电阻r37、电阻r38、电阻r39、电阻r47、电阻r48、电阻r49、电阻r50、电阻r51、电阻r52、电容c25、电容c26、电容c27、电容c28、电容c29、电容c30、电容c31、电容c32、电容c33、电容c34,所述u3芯片的12号引脚与所述电阻r53的一端连接,所述电阻r53的另一端与所述u4芯片的25号引脚连接,所述u3芯片的13号引脚与所述u4芯片的16号引脚连接,所述u3芯片的16号引脚与所述u4芯片的48号引脚连接,所述u3芯片的17号引脚与所述u4芯片的51号引脚连接,所述u3芯片的18号引脚与所述u4芯片的52号引脚连接,所述u3芯片的7号引脚与所述u4芯片的34号引脚连接,所述u3芯片的8号引脚与所述u4芯片的33号引脚连接,所述u3芯片的11号引脚与所述u4芯片的32号引脚连接,所述u3芯片的14号引脚与所述u4芯片的24号引脚连

接,所述u3芯片的15号引脚与所述u4芯片的15号引脚、所述电阻r37的一端连接,所述电阻r37的另一端接地,所述u3芯片的24号引脚与所述电阻r38的一端连接,所述电阻r38的另一端接地,所述u3芯片的25号引脚接地,所述u3芯片的4号引脚与所述电阻r39的一端、所述晶振y2的一端、所述电容c33的一端连接,所述u3芯片的5号引脚与所述电阻r39的另一端、所述晶振y2的另一端、所述电容c34的一端连接,所述电容c33的另一端与所述电容c34的另一端连接后接地,所述u3芯片的6号引脚与所述电容c31的一端、所述电容c32的一端连接,所述电容c31的另一端与所述电容c32的另一端连接后接地,所述u3芯片的3号引脚与所述电阻r35的一端连接,所述u3芯片的2号引脚与所述电阻r36的一端连接,所述电阻r35的另一端与所述电阻r36的另一端连接后接地,所述u3芯片的19号引脚与所述u3芯片的1号引脚、所述电感l18的一端、所述电容c27的一端、所述电容c26的一端连接后与3.3v电源连接,所述电容c26的另一端与所述电容c27的另一端连接后接地,所述u3芯片的9号引脚与所述电感l18的另一端、所述电容c28的一端、所述电容c29的一端连接后与3.3v电源连接,所述电容c28的另一端与所述电容c29的另一端连接后接地,所述u3芯片的21号引脚与所述电阻r52的一端连接后与所述u2芯片的1号引脚连接,所述u3芯片的20号引脚与所述电阻r51的一端连接后与所述u2芯片的2号引脚连接,所述u3芯片的23号引脚与所述电阻r50的一端连接后与所述u2芯片的3号引脚连接,所述u3芯片的22号引脚与所述电阻r49的一端连接后与所述u2芯片的6号引脚连接,所述电阻r52的另一端与所述电阻r51的另一端、所述电阻r50的另一端、所述电阻r49、所述电容c25的一端连接后与3.3v电源连接,所述电容c25的另一端接地,所述u2芯片的4号引脚与所述u2芯片的5号引脚、所述电容c30的一端连接后与3.3v电源连接,所述电容c30的另一端接地,所述u2芯片的12号引脚与所述u3芯片的3号引脚连接,所述u2芯片的9号引脚与所述u3芯片的2号引脚连接,所述u2芯片的11号引脚与所述电阻r34的一端连接,所述u2芯片的10号引脚与所述电阻r33的一端连接,所述u2芯片的8号引脚与所述u2芯片的13号引脚、所述u2芯片的14号引脚、所述电阻r33的另一端、所述电阻r34的另一端连接后接地。

9.本实用新型的有益效果:本实用新型实现了可以发射多个不同身份编码的ais报文信息;可通过网口直连电脑,实现数据交互;可通过电脑远程修改ais发射的报文数据,身份编码、发送频率;可实现定时回传状态信息、响应远程控制命令;可远程监控设备运行状态。

附图说明

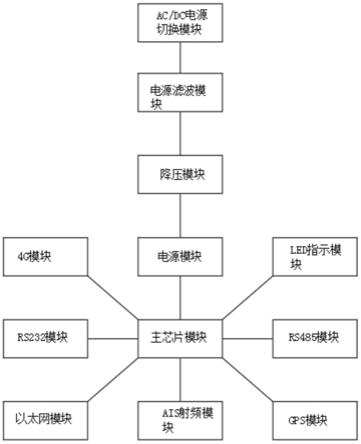

10.图1为本实用新型的电路原理框图;

11.图2为所述主芯片模块的电路原理图;

12.图3为所述ais射频模块的电路原理图;

13.图4为所述以太网模块的电路原理图。

具体实施方式

14.下面结合附图对本实用新型做进一步说明。

15.请参阅图1至图4,本实用新型提供了一实施例:一种ais航标基站,包括位于基站内部用于给主芯片模块供电的供电模块,所述供电模块包括ac/dc切换模块、电源滤波模块

以及降压模块,还包括主芯片模块,所述主芯片模块连接有ais射频模块、以太网模块,所述ais射频模块与ais射频天线连接,所述以太网模块与基站终端通信连接,基站终端通过所述以太网模块将ais报文传输给所述主芯片模块,所述主芯片模块通过所述ais射频模块将ais报文发送给船舶。

16.请参阅图2所示,本实用新型一实施例中,所述主芯片模块包括u4芯片、u5芯片、晶振y3、电阻r53、电阻r54、电阻r61、电阻r62、电阻r63、电阻r64、电阻r65、电阻r66、电阻r67、电阻r68、电阻r69、电阻r70、电阻r71、电阻r72、电阻r73、电阻r74、电阻r75、电阻r76、电阻r77、电容c1、电容c2、电容c3、电容c4、电容c19、电容c20、电容c21、电容c22、电容c23、电容c24、电容c35、电容c36、电容c37、电容c40、电容c41、电容c42、电容c43、电容c44、电容c45、电感l1、二极管d1、二极管d2、三极管q1、插座p1、插座p2,所述u4芯片的6号引脚与所述电容c1的一端连接后与3.3v电源连接,所述电容c1的另一端接地,所述u4芯片的19号引脚与所述电容c19的一端、所述电容c2的一端、所述电容c20的一端、所述电容c3的一端、所述电容c21的一端、所述电容c4的一端、所述电容c22的正极连接后与.3.v电源连接,所述电容c19的另一端与所述电容c2的另一端、所述电容c20的另一端、所述电容c3的另一端、所述电容c21的另一端、所述电容c4的另一端连接后接地,所述电容c22的负极接地,所述u4芯片的19号引脚与所述u4芯片的11号引脚、所述u4芯片的28号引脚、所述u4芯片的50号引脚、所述u4芯片的75号引脚、所述u4芯片的100号引脚连接,所述u4芯片的10号引脚接地,所述u4芯片的27号引脚接地,所述u4芯片的74号引脚接地,所述u4芯片的99号引脚与所述电阻r61的一端、所述电阻r62的一端连接,所述电阻r61的另一端与3.3v电源连接,所述电阻r62的另一端接地,所述u4芯片的22号引脚与所述u4芯片的23号引脚连接后与所述电容c23的一端、所述电容c24的一端、所述电容c35的一端、所述电感l1的一端连接,所述u4芯片的20号引脚与所述电容c23的另一端、所述电容c24的另一端、所述电容c35的另一端连接后接地,所述电感l1的另一端与所述电容c36的正极连接后与3.3v电源连接,所述电容c36的负极接地,所述u4芯片的49号引脚与所述电容c37的一端连接,所述u4芯片的73号引脚与所述电容c40的一端连接,所述电容c37的另一端与所述电容c40的另一端连接后接地,所述u4芯片的14号引脚与所述电容c44的一端、所述电阻r65的一端连接,所述电容c44的另一端接地,所述电阻r65的另一端与3.3v电源连接,所述u4芯片的94号引脚与所述电阻r70的一端、所述插座p1的1号引脚连接,所述电阻r70的另一端接地,所述插座p1的2号引脚与3.3v电源连接,所述u4芯片的57号引脚与所述电阻r53的一端连接,所述电阻r53的另一端与所述电阻r54的一端、所属电容c45的一端、所述三极管q1的2号引脚连接,所述电阻r54的另一端接地,所述电容c45的另一端接地,所述三极管q1的1号引脚接地,所述三极管q1的3号引脚与所述二极管d2的负极连接,所述二极管d2的正极与所述电阻r64的一端连接,所述电阻r64的另一端与24v电源连接,所述u4芯片的1号引脚与所述二极管d1的负极连接,所述二极管d1的正极与所述电阻r63的一端连接,所述电阻r63的另一端与3.3v电源连接,所述u4芯片的37号引脚与所述电阻r71的一端连接,所述电阻r71的另一端接地,所述u4芯片的72号引脚与所述插座p2的2号引脚、电阻r68的一端连接,所述u4芯片的76号引脚与所述插座p2的3号引脚、所述电阻r67的一端连接,所述插座p2的1号引脚与所述电阻r69的一端连接,所述插座p2的4号引脚接地,所述插座p2的5号引脚与所述电阻r66的一端连接,所述电阻r66的另一端与所述电阻r67的另一端、所述电阻r68的另一端、所述电阻r69的另一端连接后与3.3v电源连

接,所述u4芯片的12号引脚与所述晶振y3的一端、所述电容c41的一端连接,所述u4芯片的13号引脚与所述晶振y3的另一端、所述电容c42的一端连接,所述电容c41的另一端与所述电容c42的另一端连接后接地,所述芯片u5的1号引脚与所述电阻r77的一端连接,所述u5芯片的2号引脚与所述电阻r76的一端连接,所述u5芯片的3号引脚与所述电阻r75的一端连接,所述u5芯片的4号引脚与所述电阻r74的一端连接,所述电阻r74的另一端与所述电阻r75的另一端、所述电阻r76的另一端、所述电阻r77的另一端连接后与3.3v电源连接,所述u5芯片的7号引脚接地,所述u5芯片的8号引脚与所述u5芯片的电阻r72的一端连接,所述u5芯片的5号引脚与所述电阻r73的一端连接,所述u5芯片的6号引脚与所述电容c43的一端、所述电阻r73的另一端、所述电阻r72的另一端连接后与3.3v电源连接,所述电容c43的另一端接地,所述u5芯片的1号引脚与所述u4芯片的91号引脚连接,所述u5芯片的2号引脚与所述u4芯片的89号引脚连接,所述u5芯片的3号引脚与所述u4芯片的92号引脚连接,所述u5芯片的4号引脚与所述u4芯片的77号引脚连接,所述u5芯片的8号引脚与所述u4芯片的90号引脚连接。该芯片最大频率可达到168mhz,共有100个引脚,配备有丰富的接口;包含14路计时器、2路can总线、2路pwm、16路ad采集通道等,完全满足项目需求。内存可达192kb,充分保证程序顺利运行,同时芯片的稳定也是一大特点,可在-40

°

到85

°

之间正常工作。

17.请参阅图3所示,本实用新型一实施例中,所述ais射频模块包括u1芯片、u10芯片、晶振y1、电阻r26、电阻r27、电阻r34、电阻r42、电容c5、电容c6、电容c7、电容c8、电容c9、电容c10、电容c11、电容c16、电容c17、电容c18、电容c39、电容c49、电容c50、电容c51、电容c52、电容c53、电容c54、电容c55、电容c61、电容c62、电容c63、电容c84、电容c85、电容c86、电感l8、电感l9、电感l10、电感l11、电感l12、电感l17、晶体管q2、插头cn4,所述u1芯片的6号引脚与所述u1芯片的8号引脚、所述电容c10的一端、所述电容c9的一端、所述电容c7的一端、所述电容c6的一端连接后与电源连接,所述电容c6的另一端接地,所述电容c7的另一端接地,所述电容c9的另一端接地,所述电容c10的另一端接地,所述u1芯片的11号引脚与所述u4芯片的35号引脚连接,所述u1芯片的12号引脚与所述u4芯片的36号引脚连接,所述u1芯片的13号引脚所述u4芯片的95号引脚连接,所述u1芯片的14号引脚与所述u4芯片的96号引脚连接,所述u1芯片的15号引脚与所述u4芯片的47号引脚连接,所述u1芯片的1号引脚与所述u1芯片的18号引脚连接后接地,所述u1芯片的17号引脚与所述电容c16的一端连接,所述电容c16的另一端与所述晶振y1的3号引脚连接,所述晶振y1的2号引脚接地,所述晶振y1的1号引脚接地,所述晶振y1的四号引脚与所述电容c17的一端、所述电感l17的一端连接,所述电容c17的另一端接地,所述电感l17的另一端与所述电容c18的一端连接后与电源连接,所述电容c18的另一端接地,所述u1芯片的4号引脚与所述电容c5的一端、所述电感l4的一端连接,所述电感l4的另一端与所述电容c2的一端连接后与电源连接,所述电容c2的另一端接地,所述电容c5的另一端与所述电感l12的一端连接,所述电感l12的另一端与所述电容c11的一端、所述电阻r27的一端、所述电阻r34的一端连接,所述电容c11的另一端接地,所述电阻r27的另一端接地,所述电阻r34的另一端与所述电阻r26的一端、所述电容c55的一端连接,所述电阻r26的另一端接地,所述电容c55的另一端与所述电容c39的一端、所述电容c54的一端连接,所述电容c39的另一端接地,所述电容c54的另一端与所述u10芯片的1号引脚连接,所述u10的2号引脚接地,所述u10的3号引脚与所述电容c53的一端连接,所述电容c53的另一端与所述电容c52的一端、所述电容c51的一端连接,所述电容c52的另一

端接地,所述电容c51的另一端与所述电容c50的一端连接,所述电容c50的另一端与所述晶体管q2的1号引脚连接,所述u10的3号引脚与所述电感l10的一端、所述电阻r42的一端连接,所述电阻r42的另一端与所述电感l10的另一端、所述电感l11的一端、所述电容c76的一端连接,所述电容c76的另一端接地,所述电感l11的另一端与所述电感l8的一端连接后与电源连接,所述电感l8的另一端与所述电容c84的一端、所述电容c85的一端、所述电容c86的一端、所述电感l9的一端连接,所述电容c84的另一端与所述电容c85的另一端、所述电容c86的另一端连接后接地,所述电感l9的另一端与所述电容c49的一端、所述电感l5的一端、所述晶体管q2的2号引脚连接,所述电容c49的另一端接地,所述晶体管q2的3号引脚接地,所述电感l5的另一端与所述电容c61的一端、所述电容c62的一端、所述电容c63的一端连接,所述电容c62的另一端与所述电容c63的另一端连接后接地,所述电容c61的另一端与所述插头cn4连接。ais射频模块是电路板的主要功能模块,作为ais报文的信号发射模块,其核心芯片为无线收发芯片,该芯片接收来自主芯片的报文数据,按照ais报文格式,通过功放管以及一系列信号放大电路,将数据进行调制发送。

18.请参阅图4所示,本实用新型一实施例中,所述以太网模块包括u2芯片、u3芯片、晶振y2、电阻r35、电阻r36、电阻r37、电阻r38、电阻r39、电阻r47、电阻r48、电阻r49、电阻r50、电阻r51、电阻r52、电容c25、电容c26、电容c27、电容c28、电容c29、电容c30、电容c31、电容c32、电容c33、电容c34,所述u3芯片的12号引脚与所述电阻r53的一端连接,所述电阻r53的另一端与所述u4芯片的25号引脚连接,所述u3芯片的13号引脚与所述u4芯片的16号引脚连接,所述u3芯片的16号引脚与所述u4芯片的48号引脚连接,所述u3芯片的17号引脚与所述u4芯片的51号引脚连接,所述u3芯片的18号引脚与所述u4芯片的52号引脚连接,所述u3芯片的7号引脚与所述u4芯片的34号引脚连接,所述u3芯片的8号引脚与所述u4芯片的33号引脚连接,所述u3芯片的11号引脚与所述u4芯片的32号引脚连接,所述u3芯片的14号引脚与所述u4芯片的24号引脚连接,所述u3芯片的15号引脚与所述u4芯片的15号引脚、所述电阻r37的一端连接,所述电阻r37的另一端接地,所述u3芯片的24号引脚与所述电阻r38的一端连接,所述电阻r38的另一端接地,所述u3芯片的25号引脚接地,所述u3芯片的4号引脚与所述电阻r39的一端、所述晶振y2的一端、所述电容c33的一端连接,所述u3芯片的5号引脚与所述电阻r39的另一端、所述晶振y2的另一端、所述电容c34的一端连接,所述电容c33的另一端与所述电容c34的另一端连接后接地,所述u3芯片的6号引脚与所述电容c31的一端、所述电容c32的一端连接,所述电容c31的另一端与所述电容c32的另一端连接后接地,所述u3芯片的3号引脚与所述电阻r35的一端连接,所述u3芯片的2号引脚与所述电阻r36的一端连接,所述电阻r35的另一端与所述电阻r36的另一端连接后接地,所述u3芯片的19号引脚与所述u3芯片的1号引脚、所述电感l18的一端、所述电容c27的一端、所述电容c26的一端连接后与3.3v电源连接,所述电容c26的另一端与所述电容c27的另一端连接后接地,所述u3芯片的9号引脚与所述电感l18的另一端、所述电容c28的一端、所述电容c29的一端连接后与3.3v电源连接,所述电容c28的另一端与所述电容c29的另一端连接后接地,所述u3芯片的21号引脚与所述电阻r52的一端连接后与所述u2芯片的1号引脚连接,所述u3芯片的20号引脚与所述电阻r51的一端连接后与所述u2芯片的2号引脚连接,所述u3芯片的23号引脚与所述电阻r50的一端连接后与所述u2芯片的3号引脚连接,所述u3芯片的22号引脚与所述电阻r49的一端连接后与所述u2芯片的6号引脚连接,所述电阻r52的另一端与所述电阻r51的另

一端、所述电阻r50的另一端、所述电阻r49、所述电容c25的一端连接后与3.3v电源连接,所述电容c25的另一端接地,所述u2芯片的4号引脚与所述u2芯片的5号引脚、所述电容c30的一端连接后与3.3v电源连接,所述电容c30的另一端接地,所述u2芯片的12号引脚与所述u3芯片的3号引脚连接,所述u2芯片的9号引脚与所述u3芯片的2号引脚连接,所述u2芯片的11号引脚与所述电阻r34的一端连接,所述u2芯片的10号引脚与所述电阻r33的一端连接,所述u2芯片的8号引脚与所述u2芯片的13号引脚、所述u2芯片的14号引脚、所述电阻r33的另一端、所述电阻r34的另一端连接后接地。实现通过网口将射频板数据传输到pc上,达到数据交互功能,同事可以满足远程操控的需求。

19.所述主芯片模块还连接有gps模块、led指示模块、电源模块、4g模块、rs232模块、rs485模块。

20.本实用新型中的gps模块为现有技术,用于获取基站位置信息,即经纬度。采用的定位芯片定位精度可以达到平面精度5米。

21.本实用新型中的led指示模块为现有技术,led指示模块即在基站面板上装有多个led指示灯,连接到射频板上,用于指示基站内部各个模块的工作情况,绿灯常亮为工作正常,绿灯闪烁为出现故障。

22.本实用新型中的电源模块为现有技术,电源模块是电路板的电源保护部分,搭载降压芯片做到3.3v电压输出,从而给射频板上的各个部分供电,在电路输入部分装配有不同大小的电容起到滤波稳流的作用,为整个电路板正常工作提供保障。

23.本实用新型中的4g模块为现有技术,支持2/4g数传,支持volt/录音/tts语音播报,支持中国lte网络全覆盖,提供远程升级。

24.本实用新型中的rs232模块为现有技术,为电路板提供两路的232电平串口通讯接口,方便射频板调试,可以通过该接口输出的串口报文监控射频板的工作情况,方便工程师进行在线数据调试。

25.本实用新型中的rs485模块为现有技术,为电路板提供单路的485电平串口通讯接口,方便射频板调试,可以通过该接口对射频板进行参数配置,修改射频板工作参数包括发射频点、发票频率等信息,方便工程师进行设备维护。

26.本实用新型中的ac/dc电源切换模块、电源滤波模块、降压模块均为现有技术,本领域技术人员已经能够清楚了解,在此不进行详细说明。

27.本实用新型中所述u1芯片型号可以是si4463;本实用新型中所述u2芯片型号可以是51f-1202ndxnl;本实用新型中所述u3芯片型号可以是lan8720;本实用新型中所述u4芯片型号可以是stm2f407vgt6芯片;本实用新型中所述u5芯片型号可以是at45db081d芯片;本实用新型中所述u10芯片型号可以是2sk3475;但不仅限于此。

28.以上所述仅为本实用新型的较佳实施例,不能理解为对本技术的限制,凡依本实用新型申请专利范围所做的均等变化与修饰,皆应属本实用新型的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1