一种多容值芯片电容器的制作方法

1.本实用新型涉及芯片电容器领域,尤其涉及一种多容值芯片电容器。

背景技术:

2.电容器,通常简称其容纳电荷的本领为电容,用字母c表示。定义1:电容器,顾名思义,是“装电的容器”,是一种容纳电荷的器件。定义2:电容器,任何两个彼此绝缘且相隔很近的导体(包括导线)间都构成一个电容器。电容器是电子设备中大量使用的电子元件之一,广泛应用于电路中的隔直通交,耦合,旁路,滤波,调谐回路,能量转换,控制等方面。在日常使用时,经常会有需要多种电容值的电容器的情况,需要分个设计与该多个电容值对应的多种电容器,不仅设计的时间长,精力投入也较多,且在组装过程中,需要多个但容值电容器组装,个数较多,为便于组装,有必要将多个单容值电容器在一个多容值电容器上体现,提供一种多电极电容器适用于多个单容值电容需要的电容器。

技术实现要素:

3.本实用新型目的在于提供一种多容值芯片电容器,其上集合了多个单容值电极,解决现有技术中电容器组装过程中单个电容器的复杂性的问题。

4.为达到上述目的,本实用新型提供一种多容值芯片电容器,包括一介质层介质层,所述介质层的上侧面及与所述上侧面对应的下侧面分别形成有上金属层和下金属层,所述上金属层远离所述介质层的一侧形成有不同容值的上电极,所述下金属层远离所述介质层的一侧形成有下电极;所述上电极有5个,其中有2个所述上电极在测试频率1mhz条件下,电极容值为1000pf,损耗小于2.0%,尺寸为:长度1.016

±

0.127mm,宽度0.889

±

0.127mm;有3个所述上电极在测试频率1mhz条件下,电极容值为100pf,损耗小于2.0%,尺寸为:长度0.4

±

0.127mm,宽度0.35

±

0.127mm。

5.进一步优选的,所述下金属层与所述上金属层均包括从所述介质层向外延伸依次设置的一tan防扩散层、一tiw/ti粘结层及一ni阻隔层。

6.进一步优选的,所述tan防扩散层厚度为所述tiw/ti粘结层厚度为所述ni阻隔层厚度为所述上电极与所述下电极均为au电极,其厚度为2.0

±

0.5μm。

7.进一步优选的,所述多容值芯片电容器尺寸为:长度为2.3

±

0.05mm,宽为1.21

±

0.05mm,厚度为0.2

±

0.06mm。

8.进一步优选的,所述上电极的四周留边。

9.进一步优选的,所述多容值芯片电容器在测试频率1mhz条件下,损耗小于2.5%。

10.本实用新型的有益效果是:本实用新型提供一种多容值芯片电容器,其通过将多容值电极集合设置在单介质层上,使单一电容器具备多电容值性能,解决现有技术中电容器组装过程中单个电容器的复杂性的问题。

11.本实用新型通过结构、尺寸与性能的优配,使得到的多容值芯片电容器具备优良

的性能,满足人们需求,实用性高。

附图说明

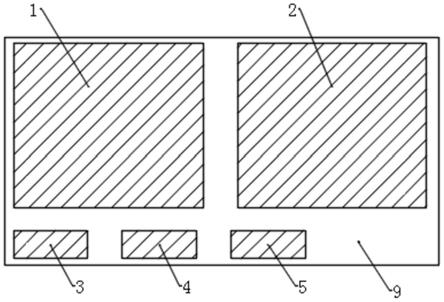

12.图1为实施例1提供的多容值芯片电容器结构俯视图;

13.图2为实施例1提供的多容值芯片电容器结构左视图;

14.图3为实施例1提供的多容值芯片电容器结构仰视图。

具体实施方式

15.下面所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

16.实施例1

17.参阅图1、图2及图3,本实施例提供一种多容值芯片电容器,包括一介质层9,所述介质层9为srtio3的陶瓷介质层,相对介电常数为15000~25000,温度范围为

‑

55℃~125℃,容量温度系数为

±

15%。所述介质层9的上侧面及与所述上侧面对应的下侧面分别形成有上金属层和下金属层,所述上金属层的上部形成有不同容值的上电极1、2、3、4、5,所述下金属层远离所述介质层的一侧形成有下电极13。

18.所述下金属层与所述上金属层均包括从所述介质层9向外延伸依次设置的一tan防扩散层8、10、一tiw粘结层7、11及一ni阻隔层6、12,所述tan防扩散层8、10厚度为可防止ti扩散,所述tiw粘结层7、11厚度为可在介质层与金属层之间建立牢固的粘结性,所述ni阻隔层5、12厚度为可在焊锡时保护粘结层,保证电容器性能,所述上电极1、2、3、4、5与所述下电极13均为au电极,其厚度为2.0

±

0.5μm。

19.所述上电极有5个,其中所述上电极1、2在测试频率1mhz下,容量为1000pf,容量精度为

±

20%,容量下限为800pf,容量上限为1200pf,尺寸为:长度1.016

±

0.127mm,宽度0.889

±

0.127mm;所述上电极3、4、5在测试频率1mhz下,容量为100pf,容量精度为

±

20%,容量下限为80pf,容量上限为120pf,尺寸为:长度0.4

±

0.127mm,宽度0.35

±

0.127mm。所述上电极1、2、3、4、5的四周留边,可提高电容器的绝缘电阻和介质耐高压。

20.所述多容值芯片电容器尺寸为:长度为2.3

±

0.05mm,宽为1.21

±

0.05mm,厚度为0.2

±

0.06mm。

21.经性能检测,所述多容值芯片电容器性能如下:

22.1、外观性能:金层表面光洁,无外来杂质污染,介质层表面、侧面无裂纹;

23.2、键合性能:至少可承受6gf拉力(25μm直径金丝);

24.3、电容器性能:损耗小于2.5%@1mhz,即在测试频率为1mhz下,损耗角正切值为小于0.025;在测试电压50vdc条件下,绝缘电阻大于1gω;工作电压为50vdc;耐电压为1255vdc;

25.4、安装工艺:支持导电胶焊接、金丝键合及金锡焊接。

26.以上所揭露的仅为本实用新型几种较佳实施例而已,当然不能以此来限定本实用

新型之权利范围,因此依本实用新型申请专利范围所作的等同变化,仍属本实用新型所涵盖的范围。

技术特征:

1.一种多容值芯片电容器,其特征在于,包括一介质层,所述介质层的上侧面及与所述上侧面对应的下侧面分别形成有上金属层和下金属层,防扩散层粘结层所述上金属层远离所述介质层的一侧形成有不同容值的上电极,所述下金属层远离所述介质层的一侧形成有下电极;所述上电极有5个,其中有2个所述上电极在测试频率1mhz条件下,电极容值为1000pf,损耗小于2.0%,尺寸为:长度1.016

±

0.127mm,宽度0.889

±

0.127mm;有3个所述上电极在测试频率1mhz条件下,电极容值为100pf,损耗小于2.0%,尺寸为:长度0.4

±

0.127mm,宽度0.35

±

0.127mm。2.如权利要求1所述的多容值芯片电容器,其特征在于,所述下金属层与所述上金属层均包括从所述介质层向外延伸依次设置的一tan防扩散层、一tiw/ti粘结层及一ni阻隔层。3.如权利要求1所述的多容值芯片电容器,其特征在于,所述tan防扩散防扩散层厚度为所述tiw/ti粘结粘结层厚度为所述ni阻隔层厚度为所述上电极与所述下电极均为au电极,其厚度为2.0

±

0.5μm。4.如权利要求3所述的多容值芯片电容器,其特征在于,所述多容值芯片电容器尺寸为:长度为2.3

±

0.05mm,宽为1.21

±

0.05mm,厚度为0.2

±

0.06mm。5.如权利要求4所述的多容值芯片电容器,其特征在于,所述上电极的四周留边。6.如权利要求5所述的多容值芯片电容器,其特征在于,所述多容值芯片电容器在测试频率1mhz条件下,损耗小于2.5%。

技术总结

本实用新型提供一种多容值芯片电容器,包括一介质层,所述介质层的上侧面及与所述上侧面对应的下侧面分别形成有上金属层和下金属层,所述下金属层与所述上金属层均包括从所述介质层向外延伸依次设置的一TaN防扩散层、一TiW/Ti粘结层及一Ni阻隔层,所述上金属层远离所述介质层的一侧形成有不同容值的上电极,所述下金属层远离所述介质层的一侧形成有下电极。本实用新型通过将多容值电极集合设置在单介质层上,使单一电容器具备多电容值性能,解决现有技术中单电容器无法适应多电容值需要的问题。并通过结构、尺寸与性能的优配,使得到的多容值芯片电容器具备优良的性能,满足人们需求,实用性高。实用性高。实用性高。

技术研发人员:熊珊 吴浩 彭高东 何培统 张浩天 席生

受保护的技术使用者:广州创天电子科技有限公司

技术研发日:2021.04.15

技术公布日:2021/11/15

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1