串联式二极管封装组件的制作方法

1.本实用新型涉及一种二极管封装组件,尤其涉及一种串联式二极管封装组件。

背景技术:

2.在电子电路中,经常会使用二极管组件来执行整流、稳压以及回路保护。若要应用于高压的电路,可在电路中串联多个二极管组件。

技术实现要素:

3.发明人认为,现有技术在电路中串联多个二极管的方式增加电路的复杂度而不利于自动化的制程。

4.有鉴于现有技术的缺失,发明人遂竭其心力提出一种串联式二极管封装组件,以应用于高压的电路,从而使所应用的电路精简而利于自动化的制程。

5.为达上揭及其他目的,本实用新型提供一种串联式二极管封装组件,其包含多个承载框架、多个二极管芯片及多个跨接框架。各该承载框架具有芯片设置部或跨接部,或具有芯片设置部及弯折于该芯片设置部的跨接部。各等二极管芯片设于各该芯片设置部上。各该跨接框架跨接于两个相邻的承载框架之间,各该跨接框架的两端分别连接于各该二极管芯片及各该跨接部,以形成串联结构。

6.在实施例中,等承载框架可包括入口框架、出口框架及排列于该入口框架于该出口框架之间的至少一个中间框架。

7.在实施例中,该入口框架仅具有该芯片设置部,该出口框架仅具有该跨接部,该至少一个中间框架可具有该芯片设置部及弯折于该芯片设置部的跨接部。

8.在实施例中,该至少一个中间框架可呈l形且彼此互补地排列于该入口框架与该出口框架之间。

9.在实施例中,彼此互补地排列的所述承载框架可具有至少一个转折处。

10.在实施例中,该串联式二极管封装组件可还包含封装体。该封装体覆盖所述承载框架、所述二极管芯片及所述跨接框架以形成封装结构。

11.在实施例中,各该承载框架可设有突出于该封装体的引脚。

12.在实施例中,所述跨接框架可彼此平行设置。

13.在实施例中,该二极管芯片可包含以硅(si)为基底的萧特基二极管、碳化硅(sic)萧特基二极管、氮化镓(gan)二极管、砷化镓(gaas)二极管、快恢复型二极管或一般pn接面二极管。

14.借此,本实用新型的串联式二极管封装组件,通过所述承载框架及所述跨接框架将多个二极管芯片加以串联,而可应用于高压电路中,从而使所应用的电路精简而利于自动化的制程。

附图说明

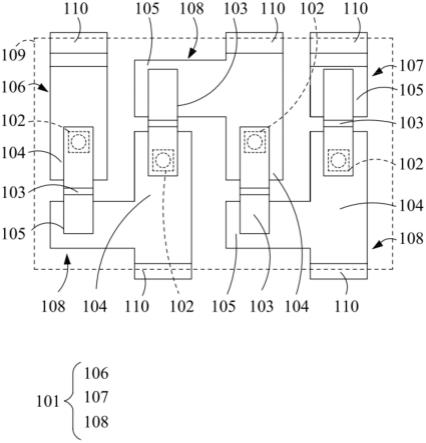

15.图1是本实用新型具体实施例的串联式二极管封装组件的俯视透视示意图;

16.图2是对应图1的入口框架、中间框架、二极管芯片及跨接框架进行跨接的剖视示意图;

17.图3是对应图1的两个中间框架、二极管芯片及跨接框架进行跨接的剖视示意图;

18.图4是对应图1的出口框架、中间框架、二极管芯片及跨接框架进行跨接的剖视示意图;

19.图5是对应图1的俯视示意图;

20.图6是对应图1的仰视示意图。

21.【符号说明】

22.100 串联式二极管封装组件

23.101 承载框架

24.102 二极管芯片

25.103 跨接框架

26.104 芯片设置部

27.105 跨接部

28.106 入口框架

29.107 出口框架

30.108 中间框架

31.109 封装体

32.110 引脚

具体实施方式

33.为充分了解本实用新型的目的、特征及效果,现通过下述具体的实施例,并配合附图,对本实用新型做进一步详细说明,说明如下:

34.请参考图1至图4,如图1所示,本实用新型的实施例提供一种串联式二极管封装组件100,其包含可导电的多个承载框架101、多个二极管芯片102及可导电的多个跨接框架103。各该承载框架101具有芯片设置部104或跨接部105,或具有芯片设置部104及弯折于该芯片设置部104的跨接部105。各该二极管芯片102设于各该芯片设置部104上。各该跨接框架103跨接于两个相邻的承载框架101之间。各该跨接框架103的两端分别连接于各该二极管芯片102及各该跨接部105,以形成串联结构。该二极管芯片102包含以硅(si)为基底的萧特基二极管、碳化硅(sic)萧特基二极管、氮化镓(gan)二极管、砷化镓(gaas)二极管、快恢复型二极管、一般pn接面二极管。但并不仅限于此,也可为其他种类的二极管芯片。

35.借此,本实用新型的实施例的串联式二极管封装组件100,通过所述承载框架101及所述跨接框架103将多个二极管芯片102加以串联,而可应用于高压电路(图中未示)中,从而使所应用的电路精简而利于自动化的制程。

36.如图1至图4所示,在实施例中,等承载框架101可包括入口框架106、出口框架107及排列于该入口框架106于该出口框架107之间的至少一个中间框架108。该入口框架106仅具有该芯片设置部104,该出口框架107仅具有该跨接部105。该至少一个中间框架108可具

有该芯片设置部104及弯折于该芯片设置部104的该跨接部105。在图1中,该中间框架108的数量为多个,而所述中间框架108分别可呈l形且彼此互补地排列于该入口框架106与该出口框架107之间,以使所形成的串联结构积集化,且使该跨接框架103的长度无须过长即可跨接两个承载框架101,图1中包括跨接于该入口框架106与一个中间框架108之间的一个跨接框架103、跨接于三个中间框架108之间的两个跨接框架103以及跨接于一个中间框架108及该出口框架107之间的一个跨接框架103。图1所示的中间框架108的数量为三个,但并不仅限于此。在上述的配置下,彼此互补地排列的所述承载框架101可具有至少一个转折处,所述跨接框架103彼此可平行设置。各该跨接框架103的两端可分别焊接于一个二极管芯片102及一个跨接部105,但并不仅限于此。所述承载框架101及所述跨接框架103的材料可为铜或铁镍合金。

37.如图1至图6所示,在实施例中,该串联式二极管封装组件100还可包含封装体109。该封装体109覆盖所述承载框架101、所述二极管芯片102及所述跨接框架103以形成封装结构。各该承载框架101可设有突出于该封装体109的引脚110,以在该串联式二极管封装组件100安装于电路板(图中未示)时,电性连接于电路板上的电路(图中未示)。如图5及图6所示,串联式二极管封装组件100的两侧皆具有突出于封装体109的多个引脚110。该封装体109可为环氧树脂或其他绝缘封装材料。

38.本实用新型在上文中已以较佳实施例揭露,然而本领域技术人员应理解的是,该实施例仅用于描绘本实用新型,而不应解读为限制本实用新型的范围。应注意的是,凡是与该实施例等效的变化与置换,均应设为涵盖于本实用新型的范围内。因此,本实用新型的保护范围当以权利要求书所界定的范围为准。

技术特征:

1.一种串联式二极管封装组件,其特征在于,包含:多个承载框架,各该承载框架具有芯片设置部或跨接部,或具有芯片设置部及弯折于该芯片设置部的跨接部;多个二极管芯片,各该二极管芯片设于各该芯片设置部上;以及多个跨接框架,各该跨接框架跨接于两个相邻的承载框架之间,各该跨接框架的两端分别连接于各该二极管芯片及各该跨接部,以形成串联结构。2.根据权利要求1所述的串联式二极管封装组件,其特征在于,所述承载框架包括入口框架、出口框架及排列于该入口框架于该出口框架之间的至少一个中间框架。3.根据权利要求2所述的串联式二极管封装组件,其特征在于,该入口框架仅具有该芯片设置部,该出口框架仅具有该跨接部,该至少一个中间框架具有该芯片设置部及弯折于该芯片设置部的该跨接部。4.根据权利要求3所述的串联式二极管封装组件,其特征在于,该至少一个中间框架呈l形且彼此互补地排列于该入口框架与该出口框架之间。5.根据权利要求4所述的串联式二极管封装组件,其特征在于,彼此互补地排列的所述承载框架具有至少一个转折处。6.根据权利要求1所述的串联式二极管封装组件,其特征在于,还包含封装体,该封装体覆盖所述承载框架、所述二极管芯片及所述跨接框架以形成封装结构。7.根据权利要求6所述的串联式二极管封装组件,其特征在于,各该承载框架设有突出于该封装体的引脚。8.根据权利要求1所述的串联式二极管封装组件,其特征在于,所述跨接框架彼此平行设置。9.根据权利要求1所述的串联式二极管封装组件,其特征在于,该二极管芯片包含以硅(si)为基底的萧特基二极管、碳化硅(sic)萧特基二极管、氮化镓(gan)二极管、砷化镓(gaas)二极管、快恢复型二极管或一般pn接面二极管。

技术总结

本实用新型提供一种串联式二极管封装组件,其包含多个承载框架、多个二极管芯片及多个跨接框架。各该承载框架具有芯片设置部或跨接部,或具有芯片设置部及弯折于该芯片设置部的跨接部。各该二极管芯片设于各该芯片设置部上。各该跨接框架跨接于两个相邻的承载框架之间,各该跨接框架的两端分别连接于各该二极管芯片及各该跨接部,以形成串联结构。以形成串联结构。以形成串联结构。

技术研发人员:廖皇順

受保护的技术使用者:力勤股份有限公司

技术研发日:2022.05.18

技术公布日:2022/9/20

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1