电源开关电路的制作方法

[0001]

本发明涉及一种电源电路,尤其涉及一种可防止软启动失效的背对背电源开关电路。

背景技术:

[0002]

在以晶体管作为电源开关的电路设计中,为了避免晶体管内部的寄生二极管(即基体二极管)被导通而导致电源开关无法完全地被关断,设计者通常会采用以背对背串接的两颗晶体管来实现电源开关。然而,由于此两颗晶体管可能具有不同的临界电压,因此当电源开关进行软启动时,此两颗晶体管可能无法同时地自关断状态转换至导通状态。若其中一颗晶体管自关断状态转换至导通状态的时间区间与另一颗晶体管自关断状态转换至导通状态的时间区间仅仅部分重叠,将会导致此两颗晶体管的整体等效电阻值的变化不平滑,如此一来,电源开关在启动的过程中将会产生涌浪电流(inrush current)而导致软启动失效。

技术实现要素:

[0003]

有鉴于此,本发明提供一种电源开关电路,此电源开关电路的输入端与输出端之间具有以背对背串接的第一晶体管及第二晶体管。电源开关电路可在完全导通第一晶体管及第二晶体管的其中一者之后,才开始控制第一晶体管及第二晶体管的其中另一者的导通状态,以防止软启动失效。

[0004]

本发明的电源开关电路包括第一晶体管、第二晶体管以及控制电路。第一晶体管具有第一端、第二端以及控制端。第一晶体管的第一端用以作为电源开关电路的输入端。第一晶体管的第二端耦接节点。第一晶体管的控制端用以接收第一控制电压。第二晶体管具有第一端、第二端以及控制端。第二晶体管的第一端用以作为电源开关电路的输出端。第二晶体管的第二端耦接节点。第二晶体管的控制端用以接收第二控制电压。控制电路耦接节点、第一晶体管的控制端以及第二晶体管的控制端。控制电路检测节点的电压,根据节点的电压判断第一晶体管与第二晶体管间的串接型态,且根据此串接型态产生第一控制电压及第二控制电压,以在完全导通第一晶体管及第二晶体管的其中一者之后,才开始控制第一晶体管及第二晶体管的其中另一者的导通状态。

[0005]

基于上述,在本发明的电源开关电路中,控制电路可判断第一晶体管与第二晶体管间的串接型态,并根据第一晶体管与第二晶体管间的串接型态来控制第一晶体管及第二晶体管。控制电路在完全导通第一晶体管及第二晶体管的其中一者之后,才开始控制第一晶体管及第二晶体管的其中另一者的导通状态。如此一来,第一晶体管自关断状态转换至导通状态的时间区间与第二晶体管自关断状态转换至导通状态的时间区间完全不重叠,故可避免电源开关电路在启动的过程中产生涌浪电流而导致软启动失效。

[0006]

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

[0007]

下面的所附附图是本发明说明书的一部分,示出了本发明的示例实施例,所附附图与说明书的描述一起说明本发明的原理;

[0008]

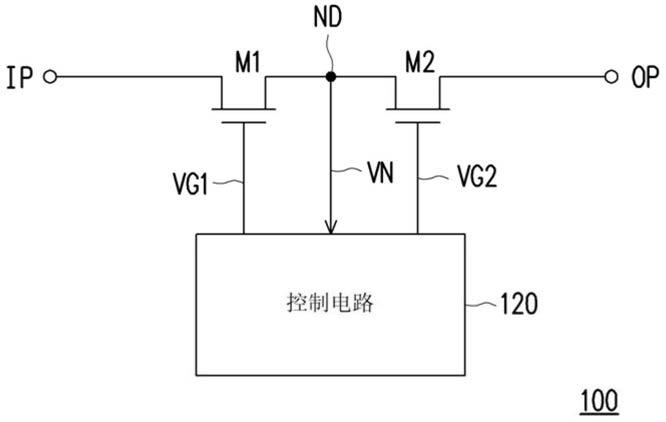

图1是依照本发明一实施例所示出的电源开关电路的电路方块示意图;

[0009]

图2是依照本发明一实施例所示出的控制电路的电路方块示意图;

[0010]

图3a是依照本发明一实施例所示出的电源开关电路的第一晶体管与第二晶体管间的串接型态为共源极串接型态的示意图;

[0011]

图3b是依照本发明另一实施例所示出的电源开关电路的第一晶体管与第二晶体管间的串接型态为共漏极串接型态的示意图;

[0012]

图4是依照本发明一实施例所示出的图2的判断电路的电路方块示意图;

[0013]

图5是依照本发明一实施例所示出的图2的控制主体的电路方块示意图;

[0014]

图6a是依照本发明一实施例所示出的图3a的第一控制电压、第二控制电压以及输入端与输出端之间的等效电阻值的波形示意图;

[0015]

图6b是依照本发明一实施例所示出的图3b的第一控制电压、第二控制电压以及输入端与输出端之间的等效电阻值的波形示意图;

[0016]

图7是依照本发明另一实施例所示出的图2的控制主体的电路方块示意图;

[0017]

图8a~图8d是依照本发明一实施例所示出的延迟电路的电路示意图;

[0018]

图9是依照本发明一实施例所示出的第一泵电压、第二泵电压及软启动就绪信号的时序示意图。

[0019]

附图标记说明

[0020]

100:电源开关电路

[0021]

120:控制电路

[0022]

122:判断电路

[0023]

124:控制主体

[0024]

4222:偏压电路

[0025]

4224:逻辑电路

[0026]

5241:第一电荷泵电路

[0027]

5242:第二电荷泵电路

[0028]

7241:电荷泵电路

[0029]

7242、7242a、7242b、7242c、7242d:延迟电路

[0030]

7243:切换电路

[0031]

c8:电容器

[0032]

d1、d2:寄生二极管

[0033]

dr:二极管串

[0034]

ds:判断信号

[0035]

dt:检测信号

[0036]

gnd:接地端

[0037]

i8:电流源电路

[0038]

ip:输入端

[0039]

m1:第一晶体管

[0040]

m2:第二晶体管

[0041]

m3:第三晶体管

[0042]

nd:节点

[0043]

op:输出端

[0044]

r8:电阻器

[0045]

ron:等效电阻值

[0046]

ssok:软启动就绪信号

[0047]

sw1、sw2:开关

[0048]

t10、t11、t12、t20、t21、t22、t30、t32:时间点

[0049]

vdd:电源端

[0050]

vg1:第一控制电压

[0051]

vg2:第二控制电压

[0052]

vn:电压

[0053]

vp1:第一泵电压

[0054]

vp2:第二泵电压

具体实施方式

[0055]

为了使本发明的内容可以被更容易明了,以下特举实施例作为本发明确实能够据以实施的范例。另外,凡可能之处,在附图及实施方式中使用相同标号的元件/构件/步骤,代表相同或类似部件。

[0056]

图1是依照本发明一实施例所示出的电源开关电路100的电路方块示意图。请参照图1,电源开关电路100可包括第一晶体管m1、第二晶体管m2以及控制电路120。第一晶体管m1具有第一端、第二端以及控制端。第一晶体管m1的第一端用以作为电源开关电路100的输入端ip。第一晶体管m1的第二端耦接节点nd。第一晶体管m1的控制端用以接收第一控制电压vg1。第二晶体管m2具有第一端、第二端以及控制端。第二晶体管m2的第一端用以作为电源开关电路100的输出端op。第二晶体管m2的第二端耦接节点nd。第二晶体管m2的控制端用以接收第二控制电压vg2。

[0057]

控制电路120耦接节点nd、第一晶体管m1的控制端以及第二晶体管m2的控制端。控制电路120可检测节点nd的电压vn。控制电路120可根据节点nd的电压vn判断第一晶体管m1与第二晶体管m2间的串接型态,且根据上述的串接型态产生第一控制电压vg1及第二控制电压vg2,以在完全导通第一晶体管m1及第二晶体管m2的其中一者之后,才开始控制第一晶体管m1及第二晶体管m2的其中另一者的导通状态。如此一来,可避免第一晶体管m1自关断状态转换至导通状态的时间区间与第二晶体管m2自关断状态转换至导通状态的时间区间部分重叠,故可防止电源开关电路100在启动的过程中产生涌浪电流(inrush current)而导致软启动失效的情况发生。

[0058]

在本发明的一实施例中,第一晶体管m1与第二晶体管m2间的串接型态可例如是共源极串接型态或是共漏极串接型态。

[0059]

图2是依照本发明一实施例所示出的控制电路120的电路方块示意图。请合并参照

图1及图2。控制电路120可包括判断电路122以及控制主体124。判断电路122用以检测节点nd的电压vn,且根据节点nd的电压vn判断第一晶体管m1与第二晶体管m2间的串接型态并产生判断信号ds。控制主体124耦接判断电路122以接收判断信号ds,且根据判断信号ds产生第一控制电压vg1及第二控制电压vg2。

[0060]

图3a是依照本发明一实施例所示出的第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态的示意图。请合并参照图2及图3a,第一晶体管m1及第二晶体管m2中的每一者为n型金氧半场效晶体管,且第一晶体管m1与第二晶体管m2为共源极串接。详细来说,第一晶体管m1的漏极端用以作为电源开关电路100的输入端ip,第一晶体管m1的源极端与基体相耦接并耦接至节点nd,其中第一晶体管m1的基体与漏极端之间具有寄生二极管d1。第二晶体管m2的漏极端用以作为电源开关电路100的输出端op,第二晶体管m2的源极端与基体相耦接并耦接至节点nd,其中第二晶体管m2的基体与漏极端之间具有寄生二极管d2。

[0061]

在电力提供至电源开关电路100的输入端ip之后且在电源开关电路100启动之前,第一晶体管m1及第二晶体管m2为关断状态,且第一晶体管m1中的寄生二极管d1为逆向偏压,致使节点nd的电压vn为低电平。因此,判断电路122可根据节点nd的电压vn为低电平而判断第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态。若判断电路122所产生的判断信号ds表示第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态,则控制主体124在切换第二控制电压vg2以完全导通第二晶体管m2之后,才开始切换第一控制电压vg1以导通第一晶体管m1,其中第一晶体管m1自关断状态转换至导通状态的时间区间与第二晶体管m2自关断状态转换至导通状态的时间区间不重叠。

[0062]

图3b是依照本发明另一实施例所示出的第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态的示意图。请合并参照图2及图3b,第一晶体管m1及第二晶体管m2中的每一者为n型金氧半场效晶体管,且第一晶体管m1与第二晶体管m2为共漏极串接。详细来说,第一晶体管m1的源极端与基体相耦接以作为电源开关电路100的输入端ip,且第一晶体管m1的漏极端耦接至节点nd,其中第一晶体管m1的基体与漏极端之间具有寄生二极管d1。第二晶体管m2的源极端与基体相耦接以作为电源开关电路100的输出端op,且第二晶体管m2的漏极端耦接至节点nd,其中第二晶体管m2的基体与漏极端之间具有寄生二极管d2。

[0063]

在电力提供至电源开关电路100的输入端ip之后且在电源开关电路100启动之前,第一晶体管m1及第二晶体管m2为关断状态,且第一晶体管m1中的寄生二极管d1为顺向偏压,致使节点nd的电压vn为高电平。因此,判断电路122可根据节点nd的电压vn为高电平而判断第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态。若判断电路122所产生的判断信号ds表示第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态,则控制主体124在切换第一控制电压vg1以完全导通第一晶体管m1之后,才开始切换第二控制电压vg2以导通第二晶体管m2,其中第一晶体管m1自关断状态转换至导通状态的时间区间与第二晶体管m2自关断状态转换至导通状态的时间区间不重叠。

[0064]

图4是依照本发明一实施例所示出的图2的判断电路122的电路方块示意图。请参照图4,判断电路122可包括第三晶体管m3、偏压电路4222以及逻辑电路4224。第三晶体管m3的第一端耦接至接地端gnd。第三晶体管m3的控制端耦接节点nd。偏压电路4222的第一端耦接第三晶体管m3的第二端以产生检测信号dt。偏压电路4222的第二端耦接至电源端vdd。逻

辑电路4224耦接偏压电路4222的第一端及第三晶体管m3的第二端以接收检测信号dt,且根据检测信号dt产生判断信号ds。

[0065]

在本发明的一实施例中,偏压电路4222可例如是电阻器或电流源电路,但本发明不限于此。

[0066]

更进一步来说,当节点nd的电压vn为低电平时,第三晶体管m3被关断,致使检测信号dt为高电平。逻辑电路4224可根据高电平的检测信号dt而判断第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态,并据以产生对应的判断信号ds。相对地,当节点nd的电压vn为高电平时,第三晶体管m3被导通,致使检测信号dt为低电平。逻辑电路4224可根据低电平的检测信号dt而判断第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态,并据以产生对应的判断信号ds。

[0067]

图5是依照本发明一实施例所示出的图2的控制主体124的电路方块示意图。请合并参照图2及图5,控制主体124可包括第一电荷泵电路5241以及第二电荷泵电路5242。第一电荷泵电路5241耦接判断电路122以接收判断信号ds,且根据判断信号ds产生第一控制电压vg1。第二电荷泵电路5242耦接判断电路122以接收判断信号ds,且根据判断信号ds产生第二控制电压vg2。

[0068]

在本发明的一实施例中,第一电荷泵电路5241以及第二电荷泵电路5242可采用现有的电荷泵来实现。

[0069]

以下搭配图3a及图6a来说明图5的控制主体124的运作。图6a是依照本发明一实施例所示出的图3a的第一控制电压vg1、第二控制电压vg2以及输入端ip与输出端op之间的等效电阻值ron的波形示意图。请合并参照图3a、图5及图6a。于本实施例中,图5的判断信号ds表示图3a的第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态,因此第二电荷泵电路5242在产生第二控制电压vg2以完全导通第二晶体管m2之后(亦即图6a的时间点t10之后),第一电荷泵电路5241于时间点t11才开始产生第一控制电压vg1以导通第一晶体管m1,并在时间点t12之后完全导通第一晶体管m1以完成电源开关电路100的软启动操作。可以理解的是,在时间点t11与t12之间的软启动区间,第二晶体管m2已完全导通,因此输入端ip与输出端op之间的等效电阻值ron实质上仅受控于第一控制电压vg1而自高阻抗平滑地变化至低阻抗,以避免产生涌浪电流。

[0070]

以下搭配图3b及图6b来说明图5的控制主体124的运作。图6b是依照本发明一实施例所示出的图3b的第一控制电压vg1、第二控制电压vg2以及输入端ip与输出端op之间的等效电阻值ron的波形示意图。请合并参照图3b、图5及图6b。于本实施例中,图5的判断信号ds表示图3b的第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态,因此第一电荷泵电路5241在产生第一控制电压vg1以完全导通第一晶体管m1之后(亦即图6b的时间点t20之后),第二电荷泵电路5242于时间点t21才开始产生第二控制电压vg2以导通第二晶体管m2,并在时间点t22之后完全导通第二晶体管m2以完成电源开关电路100的软启动操作。可以理解的是,在时间点t21与t22之间的软启动区间,第一晶体管m1已完全导通,因此输入端ip与输出端op之间的等效电阻值ron实质上仅受控于第二控制电压vg2而自高阻抗平滑地变化至低阻抗,以避免产生涌浪电流。

[0071]

图7是依照本发明另一实施例所示出的图2的控制主体124的电路方块示意图。请合并参照图2及图7,控制主体124可包括电荷泵电路7241、延迟电路7242以及切换电路

7243。电荷泵电路7241用以产生第一泵电压vp1。延迟电路7242耦接电荷泵电路7241以接收第一泵电压vp1,且延迟第一泵电压vp1以产生第二泵电压vp2,其中在第一泵电压vp1转态完成之后,第二泵电压vp2才开始转态。切换电路7243耦接电荷泵电路7241以接收第一泵电压vp1,耦接延迟电路7242以接收第二泵电压vp2,耦接判断电路122以接收判断信号ds,且耦接图3a或图3b的第一晶体管m1的控制端及第二晶体管m2的控制端。

[0072]

请合并参照图3a、图6a及图7。于本实施例中,判断信号ds表示图3a的第一晶体管m1与第二晶体管m2间的串接型态为共源极串接型态,因此切换电路7243将第一泵电压vp1输出至第二晶体管m2的控制端以作为第二控制电压vg2,且切换电路7243将第二泵电压vp2输出至第一晶体管m1的控制端以作为第一控制电压vg1。如此一来,在第二晶体管m2被完全导通之后(亦即图6a的时间点t10之后),第一控制电压vg1于时间点t11才开始控制第一晶体管m1的导通状态,并在时间点t12之后完全导通第一晶体管m1以完成电源开关电路100的软启动操作。可以理解的是,在时间点t11与t12之间的软启动区间,第二晶体管m2已完全导通,因此输入端ip与输出端op之间的等效电阻值ron实质上仅受控于第一控制电压vg1而自高阻抗平滑地变化至低阻抗,故可避免产生涌浪电流。

[0073]

请合并参照图3b、图6b及图7。于本实施例中,判断信号ds表示图3b的第一晶体管m1与第二晶体管m2间的串接型态为共漏极串接型态,因此切换电路7243将第一泵电压vp1输出至第一晶体管m1的控制端以作为第一控制电压vg1,且切换电路7243将第二泵电压vp2输出至第二晶体管m2的控制端以作为第二控制电压vg2。如此一来,在第一晶体管m1被完全导通之后(亦即图6b的时间点t20之后),第二控制电压vg2于时间点t21才开始控制第二晶体管m2的导通状态,并在时间点t22之后完全导通第二晶体管m2以完成电源开关电路100的软启动操作。可以理解的是,在时间点t21与t22之间的软启动区间,第一晶体管m1已完全导通,因此输入端ip与输出端op之间的等效电阻值ron实质上仅受控于第二控制电压vg2而自高阻抗平滑地变化至低阻抗,故可避免产生涌浪电流。

[0074]

图8a是依照本发明一实施例所示出的延迟电路7242a的电路示意图,可用于图7的延迟电路7242。请合并参照图7及图8a,延迟电路7242a包括电阻器r8。电阻器r8的第一端耦接电荷泵电路7241以接收第一泵电压vp1,且电阻器r8的第二端提供第二泵电压vp2。详细来说,延迟电路7242a通过电阻器r8与线路上的寄生电容所产生的延迟(rc delay)效应来延迟第一泵电压vp1,从而提供第二泵电压vp2。

[0075]

图8b是依照本发明另一实施例所示出的延迟电路7242b的电路示意图,可用于图7的延迟电路7242。请合并参照图7及图8b,延迟电路7242b包括电阻器r8、电容器c8以及开关sw1。电阻器r8的第一端耦接电荷泵电路7241以接收第一泵电压vp1。电阻器r8的第二端耦接电容器c8的第一端以提供第二泵电压vp2。开关sw1耦接在电容器c8的第二端与接地端gnd之间,且受控于软启动就绪信号ssok而启闭。

[0076]

当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100尚未完成软启动时,开关sw1为导通状态,因此延迟电路7242b通过电阻器r8与电容器c8所产生的延迟效应来延迟第一泵电压vp1,从而产生第二泵电压vp2。另外,当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100已完成软启动时,开关sw1为关断状态,致使第二泵电压vp2等于第一泵电压vp1。

[0077]

图8c是依照本发明又一实施例所示出的延迟电路7242c的电路示意图,可用于图7

的延迟电路7242。请合并参照图7及图8c,延迟电路7242c包括电阻器r8、电流源电路i8以及开关sw1。电阻器r8的第一端耦接电荷泵电路7241以接收第一泵电压vp1。电阻器r8的第二端耦接电流源电路i8的第一端以提供第二泵电压vp2。开关sw1耦接在电流源电路i8的第二端与接地端gnd之间,且受控于软启动就绪信号ssok而启闭。

[0078]

图9是依照本发明一实施例所示出的第一泵电压vp1、第二泵电压vp2及软启动就绪信号ssok的时序示意图。请合并参照图8c及图9。当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100尚未完成软启动时(即图9的时间点t32之前),开关sw1为导通状态,致使电流源电路i8可产生电流以在电阻器r8的第一端与第二端之间产生电压降,其中第二泵电压vp2低于第一泵电压vp1,且在第一泵电压vp1转态完成之后(即时间点t30之后),第二泵电压vp2才开始转态。另外,当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100已完成软启动时(即时间点t32之后),开关sw1为关断状态,致使电流源电路i8停止产生电流,且第二泵电压vp2等于第一泵电压vp1。

[0079]

图8d是依照本发明又一实施例所示出的延迟电路7242d的电路示意图,可用于图7的延迟电路7242。请合并参照图7及图8d,延迟电路7242d包括二极管串dr以及开关sw2。二极管串dr具有一至多个串接的二极管。二极管串dr的阳极端耦接电荷泵电路7241以接收第一泵电压vp1。二极管串dr的阴极端可提供第二泵电压vp2。开关sw2耦接在二极管串dr的阳极端及阴极端之间,且受控于软启动就绪信号ssok而启闭。

[0080]

请合并参照图8d及图9。当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100尚未完成软启动时(即时间点t32之前),开关sw2为关断状态,致使第二泵电压vp2低于第一泵电压vp1,且在第一泵电压vp1转态完成之后(即时间点t30之后),第二泵电压vp2才开始转态。另外,当软启动就绪信号ssok表示图3a(或图3b)的电源开关电路100已完成软启动时(即时间点t32之后),开关sw2为导通状态,致使第二泵电压vp2等于第一泵电压vp1。

[0081]

综上所述,在本发明实施例所提出的电源开关电路中,控制电路可判断第一晶体管与第二晶体管间的串接型态,并根据第一晶体管与第二晶体管间的串接型态来控制第一晶体管及第二晶体管。控制电路在完全导通第一晶体管及第二晶体管的其中一者之后,才开始控制第一晶体管及第二晶体管的其中另一者的导通状态。如此一来,第一晶体管自关断状态转换至导通状态的时间区间与第二晶体管自关断状态转换至导通状态的时间区间完全不重叠,故可避免电源开关电路在启动的过程中产生涌浪电流而导致软启动失效。

[0082]

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1