放电电路、浪涌保护电路、点火电路及电子设备的制作方法

[0001]

本发明涉及放电电路技术领域,尤其涉及一种放电电路、浪涌保护电路、点火电路及电子设备。

背景技术:

[0002]

电磁脉冲(electromagnetic pulse,emp)和雷击电磁脉冲(lightning electromagnetic pulse,lemp)的防护,目前主要是利用emp和lemp的高压特性做针对性的进行防护,气体放电管(gas discharge tube,gdt)正是针对高压或者过压特性设计,利用潘宁效应,在封装空间里充一定气压的气体,在金属电极上涂上阴极材料,使该器件呈现一定的直流耐压特性和脉冲击穿电压特性。目前有玻璃气体放电管和陶瓷气体放电管。

[0003]

以直流击穿电压为3000v的gdt为例,该gdt的冲击击穿电压约为3600v,该gdt的所使用的环境多为耐压1500vac的环境中,该交流环境峰值电压为2121vdc,就算该环境设计把耐压提高20%,设备的耐压是1500*1.2*1.414=2545vdc,从数据上看2545~3600v之间emp或lemp是没办法防护的,这个就是该型3000vgdt的盲区,目前在实际应用中没有很好的办法解决;在实际应用和测试中,设备被emp和lemp损坏概率非常高,其它电压等级的gdt都存在同样的问题,冲击击穿电压过高,存在保护盲区。

技术实现要素:

[0004]

本发明实施例提供一种放电电路、浪涌保护电路、点火电路及电子设备,通过将放电电路代替单个直流击穿电压较大的开关型器件,可以降低整体电路的冲击击穿电压,减小保护盲区。

[0005]

第一方面,本发明实施例提供了一种放电电路,包括:

[0006]

至少两个开关型器件,至少两个开关型器件串联连接后的两端分别与放电电路的第一端和第二端电连接;

[0007]

至少两个阻抗支路,阻抗支路与开关型器件一一对应,阻抗支路与其对应的开关型器件并联连接;

[0008]

其中,对于同一高频,阻抗支路的高频阻抗模不相等,高频大于工频。

[0009]

进一步地,按照阻抗支路的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路中,高频阻抗模大的阻抗支路对应的开关型器件的直流击穿电压小于或等于高频阻抗模小的阻抗支路对应的开关型器件的直流击穿电压。

[0010]

进一步地,在放电电路的第一端和第二端之间的电压发生高频浪涌冲击干扰时,开关型器件对应的阻抗支路的高频阻抗模越大,开关型器件越早导通。

[0011]

进一步地,所有阻抗支路的工频阻抗模相等;所有开关型器件的直流击穿电压相等。

[0012]

进一步地,按照阻抗支路的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路中,|z

h1

|>5|z

h2

|,其中,|z

h1

|为高频阻抗模大的阻抗支路的高频阻抗模,|z

h2

|为高频阻抗

模小的阻抗支路的高频阻抗模;v

brx

:v

bry

=|z

l1

|:|z

l2

|,其中,v

brx

为高频阻抗模大的阻抗支路对应的开关型器件的直流击穿电压,v

bry

为高频阻抗模小的阻抗支路对应的开关型器件的直流击穿电压,|z

l1

|为高频阻抗模大的阻抗支路的工频阻抗模,|z

l2

|为高频阻抗模小的阻抗支路的工频阻抗模。

[0013]

进一步地,除高频阻抗模最小的阻抗支路外,其余阻抗支路中,任一阻抗支路包括串联的第一子支路和第一容性元件,串联后的两端分别与对应的开关型器件的两端电连接;第一子支路包括第一阻性元件和第一感性元件中的至少一种;第一容性元件的工频阻抗模大于第一子支路的工频阻抗模的5倍;第一子支路的高频阻抗模大于第一容性元件的高频阻抗模的5倍;

[0014]

高频阻抗模最小的阻抗支路包括第二容性元件,第二容性元件的两端分别与对应的开关型器件的两端电连接;第一容性元件的容值等于第二容性元件的容值。

[0015]

进一步地,高频阻抗模最小的阻抗支路还包括第二子支路,第二子支路与第二容性元件串联,串联后的两端分别与对应的开关型器件的两端电连接;

[0016]

第二子支路包括第二阻性元件和第二感性元件中的至少一种,第一子支路的高频阻抗模大于第二子支路的高频阻抗模。

[0017]

进一步地,第一子支路包括第一阻性元件,第二子支路包括第二阻性元件,

[0018]

按照阻抗支路的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路中,高频阻抗模大的阻抗支路中的电阻的阻值大于高频阻抗模小的阻抗支路中的电阻的阻值的5倍;

[0019]

其中,r

1max

为高频阻抗模最大的阻抗支路中的第一阻性元件的阻值,c1为第一容性元件的容值,f

h

为高频,f

l

为工频。

[0020]

进一步地,第一子支路包括第一感性元件,第二子支路包括第二感性元件,

[0021]

按照阻抗支路的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路中,高频阻抗模大的阻抗支路中的电感的感值大于高频阻抗模小的阻抗支路中的电感的感值的5倍;

[0022]

其中,l

1max

为高频阻抗模最大的阻抗支路中的第一感性元件的感值,c1为第一容性元件的容值,f

h

为高频,f

l

为工频。

[0023]

进一步地,开关型器件包括:气体放电管、半导体放电管、空气间隙、石墨间隙或火花隙。

[0024]

进一步地,开关型器件的个数为三个,串联连接顺序位于中间的开关型器件对应的阻抗支路的高频阻抗模最小。

[0025]

进一步地,开关型器件包括气体放电管,

[0026]

放电电路还包括k个第二气体放电管和k个第三电容,其中,k为大于或等于2的整数,k个第二气体放电管串联连接,形成第一串联支路;

[0027]

k个第二气体放电管串联连接形成k+1个第一节点,除与第一串联支路的第一端连接的第一节点外,其余k个第一节点与k个第三电容一一对应,任一第一节点经对应的第三

电容与第一串联支路的第一端电连接;

[0028]

至少两个开关型器件与第一串联支路串联连接后的两端分别与放电电路的第一端和第二端电连接;

[0029]

第二气体放电管的直流击穿电压小于开关型器件的直流击穿电压。

[0030]

进一步地,高频大于或等于25000hz,工频为小于或等于68hz。

[0031]

第二方面,本发明实施例还提供了一种浪涌保护电路,包括本发明任意实施例提供的放电电路。

[0032]

第三方面,本发明实施例还提供了一种点火电路,包括本发明任意实施例提供的放电电路。

[0033]

第四方面,本发明实施例还提供了一种电子设备,包括本发明任意实施例提供的放电电路。

[0034]

本发明实施例的技术方案中的放电电路包括至少两个开关型器件和至少两个阻抗支路,其中,至少两个开关型器件串联连接后的两端分别与放电电路的第一端和第二端电连接;阻抗支路与开关型器件一一对应,阻抗支路与其对应的开关型器件并联连接;其中,对于同一高频,阻抗支路的高频阻抗模不相等,高频大于工频,以使得在发生雷击等浪涌冲击时,所有开关型器件不同时达到各自的冲击击穿电压,先发生击穿的开关型器件之间的电压迅速降低,浪涌电压将几乎完全施加在其余未击穿的开关型器件,随着其余未击穿的开关型器件的电压的升高,逐渐达到其直流击穿电压时发生击穿,放电电路的实际冲击击穿电压v

br0

'小于全部开关型器件的冲击击穿电压的和,即v

br0

'<v

br1

'+v

br2

'+

…

+v

brn

',解决了在发生雷击等浪涌冲击时,在浪涌冲击电压增大到直流击穿电压等于v

br1

+v

br2

+

…

+v

brn

的单个开关型器件的冲击击穿电压(等于v

br1

'+v

br2

'+

…

+v

brn

')时,单个开关型器件将被击穿导通,导致冲击击穿电压过高,存在保护盲区的问题。

附图说明

[0035]

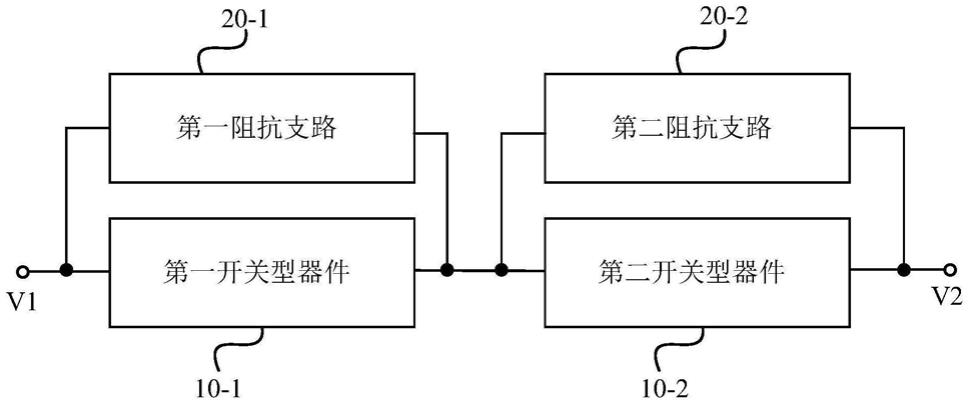

图1为本发明实施例提供的一种放电电路的结构示意图;

[0036]

图2为本发明实施例提供的一种放电电路的应用场景;

[0037]

图3为本发明实施例提供的又一种放电电路的结构示意图;

[0038]

图4为本发明实施例提供的又一种放电电路的结构示意图;

[0039]

图5为本发明实施例提供的又一种放电电路的结构示意图;

[0040]

图6为本发明实施例提供的又一种放电电路的结构示意图;

[0041]

图7为本发明实施例提供的又一种放电电路的结构示意图;

[0042]

图8为本发明实施例提供的又一种放电电路的结构示意图;

[0043]

图9为本发明实施例提供的又一种放电电路的结构示意图;

[0044]

图10为本发明实施例提供的又一种放电电路的结构示意图;

[0045]

图11为本发明实施例提供的又一种放电电路的结构示意图;

[0046]

图12为本发明实施例提供的又一种放电电路的结构示意图;

[0047]

图13为本发明实施例提供的又一种放电电路的结构示意图;

[0048]

图14为本发明实施例提供的又一种放电电路的结构示意图;

[0049]

图15为本发明实施例提供的又一种放电电路的结构示意图

[0050]

图16为本发明实施例提供的又一种放电电路的结构示意图;

[0051]

图17为本发明实施例提供的一种电子设备的结构示意图。

具体实施方式

[0052]

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

[0053]

本发明实施例提供一种放电电路。图1为本发明实施例提供的一种放电电路的结构示意图。图2为本发明实施例提供的一种放电电路的应用场景。该放电电路包括:至少两个开关型器件10和至少两个阻抗支路20。

[0054]

其中,至少两个开关型器件10串联连接后的两端分别与放电电路的第一端v1和第二端v2电连接;阻抗支路20与开关型器件10一一对应,阻抗支路20与其对应的开关型器件10并联连接;其中,对于同一高频,阻抗支路20的高频阻抗模不相等,高频大于工频。

[0055]

其中,图1示例性的画出两个开关型器件10,分别为第一开关型器件10-1和第二开关型器件10-2,以及两个阻抗支路20,分别为第一阻抗支路20-1和第二阻抗支路20-2,第一开关型器件10-1与第一阻抗支路20-1对应,第二开关型器件10-2与第二阻抗支路20-2对应的情况。其中,任一阻抗支路20可包括下述至少一种元件:阻性元件、感性元件和容性元件,该元件之间可以是串联和/或并联等方式连接,本发明实施例对此不做限定。阻性元件可以包括电阻。感性元件可包括电感。电感可以是磁珠电感,相比于普通电感,体积较小,成本较低。容性元件可包括下述至少一种:电容和带极间电容的元件。带极间电容的元件可包括压敏电阻或瞬态抑制二极管。高频阻抗模最大的阻抗支路20的阻抗模可随频率的增大而增大。高频阻抗模最小的阻抗支路20的阻抗模可随频率的增大而减小。至少一个阻抗支路20包括容性元件,以避免只用电感和电阻会引起绝缘下降的情况发生。图2示例性的画出放电电路应用在浪涌保护电路中的情况。放电电路1的第一端v1可与第一交流供电线电连接,放电电路1的第二端v2可与第二交流供电线电连接,示例性的,第一交流供电线可以是火线l,第二交流供电线可以是零线n。放电电路1可在第一交流供电线与第二交流供电线上发生浪涌干扰等过电压时导通,以泄放浪涌电流,以实现对待保护电路2的过电压保护。可选的,开关型器件包括:气体放电管、半导体放电管、空气间隙、石墨间隙或火花隙。可选的,高频f

h

大于或等于25000hz。高频的大小可与雷击等浪涌冲击的频率相等。可选的,工频f

l

为小于或等于68hz。工频可为正常工作时,供电电压的频率。可选的,工频f

l

可以是50hz、60hz或0hz。正常工作时,供电电压可以是交流或直流。

[0056]

其中,|z

11

|:|z

12

|:

…

:|z

1n

|≠v

br1

:v

br2

:

…

:v

brn

,|z

1i

|为第i个阻抗支路20的高频阻抗模,v

bri

为第i个开关型器件10的直流击穿电压,n为阻抗支路20的个数,n为大于或等于2的整数,i等于1、2

…

n,以使在放电电路的第一端v1和第二端v2之间的电压发生高频浪涌冲击干扰时,所有开关型器件10不同时达到各自的冲击击穿电压。

[0057]

直流击穿电压可以是在上升陡度低于100v/s的电压作用下,开关型器件的开始击穿的平均电压值。冲击击穿电压(或称脉冲电压)可以是在规定上升陡度的暂态电压脉冲作用下,开关型器件开始击穿的电压值,规定上升陡度可以是100v/us或1kv/us。开关型器件的响应时间或动作时延与电压脉冲的上升陡度有关,对于不同的上升陡度,开关型器件的

冲击击穿电压是不同的。直流击穿电压越小的开关型器件,其冲击击穿电压越小。

[0058]

在放电电路的第一端v1和第二端v2之间的电压发生高频浪涌冲击干扰时,浪涌电压的频率很高,部分开关型器件10的电压先达到其直流击穿电压时发生击穿,此时其余开关型器件10的电压未达到其直流击穿电压。由于先发生击穿的开关型器件10两端的电压迅速降低,浪涌电压将几乎完全施加在其余未击穿的开关型器件10,随着其余未击穿的开关型器件10的电压的升高,逐渐达到其直流击穿电压时发生击穿,整个放电电路导通,泄放电流。此时,放电电路的实际冲击击穿电压v

br0

'大于先发生击穿的开关型器件的直流击穿电压,放电电路的实际冲击击穿电压v

br0

'小于全部开关型器件的冲击击穿电压的和,即v

br0

'<v

br1

'+v

br2

'+

…

+v

brn

',其中,v

bri

'为第i个开关型器件10的冲击击穿电压。

[0059]

示例性的,如图1所示,第一开关型器件10-1的直流击穿电压为v

br1

,第二开关型器件10-2的直流击穿电压为v

br2

,第一阻抗支路20-1的高频阻抗模为|z

11

|,第二阻抗支路20-2的高频阻抗模为|z

12

|。若|z

11

|:|z

12

|>v

br1

:v

br2

,则在发生雷击等浪涌冲击时,第一开关型器件10-1先发生击穿。若|z

11

|:|z

12

|<v

br1

:v

br2

,则在发生雷击等浪涌冲击时,第二开关型器件10-2先发生击穿。

[0060]

通过在各开关型器件10上接入阻抗支路20,以使得在发生雷击等浪涌冲击时,所有开关型器件10不同时达到各自的冲击击穿电压,部分开关型器件10的电压先达到其直流击穿电压时发生击穿,此时其余开关型器件10的电压未达到其直流击穿电压。由于先发生击穿的开关型器件10之间的电压迅速降低,浪涌电压将几乎完全施加在其余未击穿的开关型器件10,随着其余未击穿的开关型器件10的电压的升高,逐渐达到其直流击穿电压时发生击穿,整个放电电路导通,泄放电流。放电电路的实际冲击击穿电压v

br0

'大于先发生击穿的开关型器件的直流击穿电压,放电电路的实际冲击击穿电压v

br0

'大于后发生击穿的开关型器件的直流击穿电压,放电电路的实际冲击击穿电压v

br0

'小于全部开关型器件的冲击击穿电压的和,即v

br0

'<v

br1

'+v

br2

'+

…

+v

brn

',故放电电路具有较低的冲击击穿电压,将放电电路替代直流击穿电压等于v

br1

+v

br2

+

…

+v

brn

的单个开关型器件,解决了在发生雷击等浪涌冲击时,在浪涌冲击电压增大到直流击穿电压等于v

br1

+v

br2

+

…

+v

brn

的单个开关型器件的冲击击穿电压(等于v

br1

'+v

br2

'+

…

+v

brn

')时,单个开关型器件将被击穿导通,导致冲击击穿电压过高,存在保护盲区的问题。

[0061]

本实施例的技术方案中的放电电路包括至少两个开关型器件和至少两个阻抗支路,其中,至少两个开关型器件串联连接后的两端分别与放电电路的第一端和第二端电连接;阻抗支路与开关型器件一一对应,阻抗支路与其对应的开关型器件并联连接;其中,对于同一高频,阻抗支路的高频阻抗模不相等,高频大于工频,以使得在发生雷击等浪涌冲击时,所有开关型器件不同时达到各自的冲击击穿电压,先发生击穿的开关型器件之间的电压迅速降低,浪涌电压将几乎完全施加在其余未击穿的开关型器件,随着其余未击穿的开关型器件的电压的升高,逐渐达到其直流击穿电压时发生击穿,放电电路的实际冲击击穿电压v

br0

'小于全部开关型器件的冲击击穿电压的和,即v

br0

'<v

br1

'+v

br2

'+

…

+v

brn

',解决了在发生雷击等浪涌冲击时,在浪涌冲击电压增大到直流击穿电压等于v

br1

+v

br2

+

…

+v

brn

的单个开关型器件的冲击击穿电压时,单个开关型器件将被击穿导通,导致冲击击穿电压过高,存在保护盲区的问题。

[0062]

可选的,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支

路20中,|z

h1

|:|z

h2

|>v

brx

:v

bry

,其中,|z

h1

|为高频阻抗模大的阻抗支路的高频阻抗模,|z

h2

|为高频阻抗模小的阻抗支路的高频阻抗模,v

brx

为高频阻抗模大的阻抗支路对应的开关型器件的直流击穿电压,v

bry

为高频阻抗模小的阻抗支路对应的开关型器件的直流击穿电压。

[0063]

其中,在放电电路的第一端v1和第二端v2之间的电压发生高频浪涌冲击干扰时,直流击穿电压小的开关型器件10先发生击穿,直流击穿电压大的开关型器件10后发生击穿,避免直流击穿电压大的开关型器件10先发生击穿,导致在直流击穿电压大的开关型器件10击穿后,直流击穿电压小的开关型器件10的电压过大导致失效的情况发生。

[0064]

可选的,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,高频阻抗模大的阻抗支路20对应的开关型器件10的直流击穿电压小于或等于高频阻抗模小的阻抗支路20对应的开关型器件10的直流击穿电压,即|z

h1

|>|z

h2

|,v

brx

≤v

bry

。

[0065]

其中,阻抗支路20的高频阻抗模越大,阻抗支路20对应的开关型器件10的直流击穿电压越小。可选的,在放电电路的第一端v1和第二端v2之间的电压发生高频浪涌冲击干扰时,开关型器件10对应的阻抗支路20的高频阻抗模越大,开关型器件10越早导通。在放电电路的第一端v1和第二端v2之间的电压发生高频浪涌冲击干扰时,直流击穿电压小的开关型器件10上的电压较高先发生击穿,直流击穿电压大的开关型器件10上的电压较低后发生击穿,避免直流击穿电压大的开关型器件10先发生击穿,导致在直流击穿电压大的开关型器件10击穿后,直流击穿电压小的开关型器件10的电压过大导致失效的情况发生。

[0066]

可选的,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,|z

h1

|>5|z

h2

|,其中,|z

h1

|为高频阻抗模大的阻抗支路20的高频阻抗模,|z

h2

|为高频阻抗模小的阻抗支路20的高频阻抗模。

[0067]

其中,|z

h1

|越大,|z

h2

|越小,放电电路的实际冲击击穿电压v

br0

'越接近于直流击穿电压最大的开关型器件的冲击击穿电压。在发生雷击等浪涌冲击时,以使高频阻抗模最大的阻抗支路20对应的开关型器件10的电压远大于其余开关型器件10的电压,使得浪涌电压几乎完全施加在高频阻抗模最大的阻抗支路20对应的开关型器件10上,以使高频阻抗模最大的阻抗支路20对应的开关型器件10先发生击穿,高频阻抗模最大的阻抗支路20对应的开关型器件10的导通电压迅速降低,使得浪涌电压几乎完全施加在高频阻抗模第二大的阻抗支路20对应的开关型器件10上,以使高频阻抗模第二大的阻抗支路20对应的开关型器件10发生击穿,依次类推,从而实现开关型器件按照与其对应的阻抗支路的高频阻抗模的大小的顺序逐个击穿。

[0068]

可选的,所有开关型器件10的直流击穿电压相等,所有开关型器件10的冲击击穿电压相等,以使放电电路的冲击击穿电压达到最小。

[0069]

示例性的,如图1所示,第一开关型器件10-1的直流击穿电压为v

br1

,第二开关型器件10-2的直流击穿电压为v

br2

。若v

br1

<v

br2

,v

br1

<v

br0

/2,v

br2

>v

br0

/2,v

br1

+v

br2

=v

br0

,两个开关型器件10的直流击穿电压不相等,两个开关型器件10的冲击击穿电压不相等,放电电路的实际冲击击穿电压v

br0

'接近于直流击穿电压为大于v

br0

/2的开关型器件的冲击击穿电压。若v

br1

=v

br2

,v

br1

=v

br0

/2,v

br2

=v

br0

/2,v

br1

+v

br2

=v

br0

,两个开关型器件10的直流击穿电压相等,两个开关型器件10的冲击击穿电压相等,放电电路的实际冲击击穿电压v

br0

'接近于直流击穿电压为等于v

br0

/2的开关型器件的冲击击穿电压。

[0070]

可选的,v

brx

:v

bry

=|z

l1

|:|z

l2

|,其中,v

brx

为高频阻抗模大的阻抗支路对应的开关

型器件的直流击穿电压,v

bry

为高频阻抗模小的阻抗支路对应的开关型器件的直流击穿电压,|z

l1

|为高频阻抗模大的阻抗支路的工频阻抗模,|z

l2

|为高频阻抗模小的阻抗支路的工频阻抗模,以使在工频电压状态时,直流击穿电压大的开关型器件的分压较大,直流击穿电压小的开关型器件的分压较小,以保证整个电路不发生击穿,保证交流耐压水平。

[0071]

其中,正常供电时,在工频电压状态时,直流击穿电压大的开关型器件10的分压较大,直流击穿电压小的开关型器件10的分压较小,以保证整个电路不发生击穿,保证交流耐压水平。正常供电时,所有开关型器件10不导通,放电电路不导通,任一开关型器件10的电压小于其开启电压。工频状态下,所有阻抗支路串联后的等效阻抗大于iec60950和iec61347等标准的4兆欧要求。

[0072]

可选的,所有阻抗支路20的工频阻抗模相等,以使在所有开关型器件10的直流击穿电压相等,开关型器件的分压相等,保证交流耐压水平。其中,可选的,第一阻抗支路20-1的阻抗模可随频率的增大而增大;第二阻抗支路20-2的阻抗模可随频率的增大而减小,以满足高频和工频下的阻抗模的大小关系。

[0073]

可选的,在上述实施例的基础上,图3为本发明实施例提供的一种放电电路的结构示意图,除高频阻抗模最小的阻抗支路20外,其余阻抗支路中,任一阻抗支路20包括串联的第一子支路21和第一容性元件c1,串联后的两端分别与对应的开关型器件10的两端电连接;第一子支路21包括第一阻性元件r1和第一感性元件l1中的至少一种;第一容性元件c1的工频阻抗模大于第一子支路21的工频阻抗模的5倍;第一子支路21的高频阻抗模大于第一容性元件c1的高频阻抗模的5倍。

[0074]

其中,图3示例性的画出第一开关型器件10-1包括气体放电管,第二开关型器件10-2包括气体放电管,高频阻抗模最小的阻抗支路为第二阻抗支路20-2,第一阻抗支路20-1中的第一子支路21包括第一阻性元件r1的情况。第一阻抗支路20-1的高频阻抗模w

h

=2πf

h

,f

h

为高频频率;第一阻抗支路20-1的工频阻抗模w

l

=2πf

l

,f

l

为工频频率。其中,其中,r1为第一阻性元件r1的阻值,c1为第一容性元件c1的容值。r1越大,|z

11

|越大。c1越大,|z

21

|越小。

[0075]

图4为本发明实施例提供的又一种放电电路的结构示意图,图4示例性的画出第一阻抗支路20-1中的第一子支路21包括第一感性元件l1的情况,第一阻抗支路20-1的高频阻抗模第一阻抗支路20-1的工频阻抗模其中,l1为第一感性元件l1的电感值。l1越大,f

h

越大,|z

11

|越大。

[0076]

可选的,在上述实施的基础上,继续参见图3和图4,高频阻抗模最小的阻抗支路20包括第二容性元件c2,第二容性元件c2的两端分别与对应的开关型器件10的两端电连接;第一容性元件c1的容值等于第二容性元件c2的容值。

[0077]

其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用,第一容性元件c1和第二容性元件c2的工频容抗模可远大于第一子支路21的工

频阻抗模。在发生雷击等浪涌冲击时,由第一子支路21起主要作用,第一子支路21的高频阻抗模可远大于第二容性元件c2和第一容性元件c1的高频容抗模。

[0078]

其中,第二阻抗支路20-2的高频阻抗模第二阻抗支路20-2的工频阻抗模其中,c2为第二容性元件c2的容值。c2越小,|z

22

|越大。

[0079]

可选的,在上述实施例的基础上,图5为本发明实施例提供的又一种放电电路的结构示意图,高频阻抗模最小的阻抗支路20还包括第二子支路22,第二子支路22与第二容性元件c2串联,串联后的两端分别与对应的开关型器件10的两端电连接。可选的,第二子支路22包括第二阻性元件r2和第二感性元件l2中的至少一种,第一子支路21的高频阻抗模大于第二子支路22的高频阻抗模。

[0080]

其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用,第一容性元件c1和第二容性元件c2的工频容抗模可远大于第一子支路21和第二子支路22的工频阻抗模。在发生雷击等浪涌冲击时,由第一子支路21和第二子支路22起主要分压作用,第一子支路21和第二子支路22的高频阻抗模可远大于第二容性元件c2和第一容性元件c1的高频容抗模。

[0081]

其中,图5示例性的画出第一开关型器件10-1包括半导体放电管,第二开关型器件10-2包括半导体放电管,高频阻抗模最小的阻抗支路为第二阻抗支路20-2,第一阻抗支路20-1中的第一子支路21包括第一阻性元件r1,第二阻抗支路20-2中的第二子支路22包括第二阻性元件r2的情况,第二阻抗支路20-2的高频阻抗模第二阻抗支路20-2的工频阻抗模其中,r2为第二阻性元件r2的阻值。c2越小,|z

22

|越大。r2越小,|z

12

|越小。

[0082]

可选的,在上述实施例的基础上,图6为本发明实施例提供的又一种放电电路的结构示意图,第一子支路21包括第一阻性元件r1,第二子支路22包括第二阻性元件r2。其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用。在发生雷击等浪涌冲击时,由第一阻性元件r1和第二阻性元件r2起主要分压作用。可选的,发生雷击等浪涌冲击时,由第一阻性元件r1和第二阻性元件r2起主要分压作用。可选的,

[0083]

可选的,在上述实施例的基础上,继续参见图6,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,高频阻抗模大的阻抗支路20中的电阻的阻值大于高频阻抗模小的阻抗支路20中的电阻的阻值的5倍。

[0084]

可选的,在上述实施例的基础上,继续参见图6,可选的,在上述实施例的基础上,继续参见图6,其中,r

1max

为高频阻抗模最大的阻抗支路20中的第一阻性元件r1的阻值,c1为第一容性元件c1的容值,f

h

为高频,f

l

为工频。

[0085]

其中,图6示例性的画出三个开关型器件10,分别为第一开关型器件10-1、第二开关型器件10-2和第三开关型器件10-3,以及三个阻抗支路20,分别为第一阻抗支路20-1、第二阻抗支路20-2和第三阻抗支路20-3,,第一开关型器件10-1与第一阻抗支路20-1对应,第二开关型器件10-2与第二阻抗支路20-2对应,第三开关型器件10-3与第三阻抗支路20-3对应,高频阻抗模最小的阻抗支路为第二阻抗支路20-2,高频阻抗模最大的阻抗支路为第一阻抗支路20-1的情况。第一阻抗支路20-1的第一子支路21的第一阻性元件r1的阻值为r

1max

,第三阻抗支路20-3的第一子支路21的第一阻性元件r1的阻值为r

1mid

,第二阻抗支路20-2的第二子支路21的第二阻性元件r2的阻值为r2,其中,r

1max

>5r

1mid

,r

1mid

>5r2。序号相邻的两个阻抗支路20中的电阻相差越大,在发生雷击等浪涌冲击时,高频阻抗模大的阻抗支路20对应的开关型器件10的电压越高,高频阻抗模大的阻抗支路20对应的开关型器件10的电压越低,放电电路的冲击击穿电压越低,越接近直流击穿电压最大的开关型器件的冲击击穿电压。

[0086]

可选的,在上述实施例的基础上,图7为本发明实施例提供的又一种放电电路的结构示意图,第一子支路21包括第一感性元件l1,第二子支路22包括第二感性元件l2。其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用。在发生雷击等浪涌冲击时,由第一感性元件l1和第二感性元件l2起主要分压作用。

[0087]

按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,高频阻抗模大的阻抗支路20中的电感的感值大于高频阻抗模小的阻抗支路20中的电感的感值的5倍。

[0088]

其中,l

1max

为高频阻抗模最大的阻抗支路中的第一感性元件的感值,c1为第一容性元件的容值,f

h

为高频,f

l

为工频。

[0089]

其中,图7示例性的画出三个开关型器件10,分别为第一开关型器件10-1、第二开关型器件10-2和第三开关型器件10-3,以及三个阻抗支路20,分别为第一阻抗支路20-1、第二阻抗支路20-2和第三阻抗支路20-3,,第一开关型器件10-1与第一阻抗支路20-1对应,第二开关型器件10-2与第二阻抗支路20-2对应,第三开关型器件10-3与第三阻抗支路20-3对应,高频阻抗模最小的阻抗支路为第二阻抗支路20-2,高频阻抗模最大的阻抗支路为第一阻抗支路20-1的情况。第一阻抗支路20-1的第一子支路21的第一感性元件l1的阻值为l

1max

,第三阻抗支路20-3的第一子支路21的第一感性元件l1的阻值为l

1mid

,第二阻抗支路20-2的第二子支路21的第二感性元件l2的阻值为l2,其中,l

1max

>5l

1mid

,l

1mid

>5l2。序号相邻的两个阻抗支路20中的电感相差越大,在发生雷击等浪涌冲击时,高频阻抗模大的阻抗支路20对应的开关型器件10的电压越高,高频阻抗模大的阻抗支路20对应的开关型器件10

的电压越低,放电电路的冲击击穿电压越低,越接近直流击穿电压最大的开关型器件的冲击击穿电压。

[0090]

图8为本发明实施例提供的又一种放电电路的结构示意图。图8示例性的画出高频阻抗模最小的阻抗支路为第二阻抗支路20-2,第一阻抗支路20-1中的第一子支路11包括第一阻性元件r1,第二阻抗支路20-2中的第二子支路22包括第二感性元件l2的情况,第二阻抗支路20-2的高频阻抗模第二阻抗支路20-2的工频阻抗模其中,l2为第二感性元件l2的电感值。c2越小,|z

22

|越大。l2越小,|z

12

|越小。其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用。在发生雷击等浪涌冲击时,由第一阻性元件r1和第二感性元件l2起主要分压作用。

[0091]

可选的,在上述实施例的基础上,继续参见图8,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,高频阻抗模大的阻抗支路20中的子支路包括电阻,高频阻抗模小的阻抗支路20中的子支路包括电感,高频阻抗模大的阻抗支路20中的电阻的阻值大于高频阻抗模小的阻抗支路20中的电感的高频感抗的5倍。示例性的,如图8所示,r1>5|jw

h

l2|。

[0092]

图9为本发明实施例提供的又一种放电电路的结构示意图。图9示例性的画出高频阻抗模最小的阻抗支路为第二阻抗支路20-2,第一阻抗支路20-1中的第一子支路11包括第一感性元件l1,第二阻抗支路20-2中的第二子支路21包括第二阻性元件r2的情况。其中,正常供电时,在工频电压状态时,由第一容性元件c1和第二容性元件c2起主要分压作用。在发生雷击等浪涌冲击时,由第一感性元件l1和第二阻性元件r2起主要分压作用。

[0093]

可选的,在上述实施例的基础上,继续参见图9,按照阻抗支路20的高频阻抗模的大小进行排序,序号相邻的两个阻抗支路20中,高频阻抗模大的阻抗支路20中的子支路包括电感,高频阻抗模小的阻抗支路20中的子支路包括电阻,高频阻抗模大的阻抗支路20中的电感的高频感抗大于高频阻抗模小的阻抗支路20中的电阻的阻值的5倍。示例性的,如图9所示,|jw

h

l1|>5r2。

[0094]

可选的,在上述实施例的基础上,图10为本发明实施例提供的又一种放电电路的结构示意图,开关型器件10的个数为三个,串联连接顺序位于中间的开关型器件10对应的阻抗支路20的高频阻抗模最小。

[0095]

其中,在发生雷击等浪涌冲击时高频阻抗模最小的阻抗支路对应的开关型器件最后启动,两边的开关型器件先启动,可以让中间的开关型器件启动时有足够的电荷量。这样设置,可以让高频阻抗模最小的阻抗支路中的电容小一点,让整个回路的工频阻抗高一些,也可以使电路的放电管更可靠一些。

[0096]

可选的,在上述实施例的基础上,图12为本发明实施例提供的又一种放电电路的结构示意图,开关型器件10包括气体放电管,放电电路还包括k个第二气体放电管gdt2和k个第三电容c3,其中,k为大于或等于2的整数,k个第二气体放电管gdt2串联连接,形成第一

串联支路40。

[0097]

其中,k个第二气体放电管gdt2串联连接形成k+1个第一节点n1,除与第一串联支路40的第一端x1连接的第一节点n1外,其余k个第一节点n1与k个第三电容c3一一对应,任一第一节点n11经对应的第三电容c3与第一串联支路40的第一端x1电连接。至少两个开关型器件10与第一串联支路40串联连接后的两端分别与放电电路的第一端v1和第二端v2电连接。第二气体放电管gdt2的直流击穿电压小于开关型器件10的直流击穿电压。

[0098]

其中,对于同一高频,高频阻抗模最小的阻抗支路20的高频阻抗模大于第三电容c3的高频阻抗模其中,c3为第三电容c3的容值,以使在发生雷击等浪涌冲击时,开关型器件10的分压大,先导通;多个串联的气体放电管gdt2的分压小,后导通。可选的,第二容性元件c2的容值小于第三电容c3的容值。k个气体放电管gdt2可集成为多间隙气体放电管。多个串联的气体放电管gdt2可以抬高弧光压,使得雷击等过电压消失后,工频电流(频率可为50hz或60hz)继续流过串联的气体放电管gdt2时,在工频续电流过零点过程中,气体放电管gdt2可自行关断,折断工频续电流。多个串联的气体放电管gdt2的高续流遮断能力,使得在异常电压的工作电压下的续流能够自行切断续流达到续流折断的目的。

[0099]

可选的,如图12所示,至少两个开关型器件10串联连接后的第一端经第一串联支路40与放电电路的第一端v1电连接;至少两个开关型器件10串联连接后的第二端与放电电路的第二端v2电连接。图12示例性的画出至少两个开关型器件10串联连接后的第一端与第一串联支路40的第二端x2电连接;第一串联支路40的第一端x1与放电电路的第一端v1电连接;至少两个开关型器件10串联连接后的第二端与放电电路的第二端v2电连接的情况。

[0100]

图13为本发明实施例提供的又一种放电电路的结构示意图。图12示例性的画出至少两个开关型器件10串联连接后的第一端与第一串联支路40的第一端x1电连接;第一串联支路40的第二端x2与第一串联支路40与放电电路的第二端v2电连接;至少两个开关型器件10串联连接后的第二端与放电电路的第一端v1电连接的情况。

[0101]

可选的,在上述实施例的基础上,图14为本发明实施例提供的又一种放电电路的结构示意图,该放电电路还包括第一压敏电阻mov1,至少两个开关型器件10与第一压敏电阻mov1串联连接后的两端分别与放电电路的第一端v1和第二端v2电连接。

[0102]

其中,其中,对于同一高频,高频阻抗模最小的阻抗支路20的高频阻抗模大于第一压敏电阻mov1的极间电容的高频阻抗模其中,c4为第一压敏电阻mov1的极间电容的容值,以使在发生雷击等浪涌冲击时,开关型器件的分压大,先导通;第一压敏电阻mov1的分压小,后导通。可选的,高频阻抗模最小的阻抗支路20的高频阻抗模大于可选的,第二容性元件c2的容值小于第一压敏电阻mov1的极间电容的容值。第一压敏电阻mov1的极间电容可为第一压敏电阻mov1的寄生电容。气体放电管搭配压敏电阻使用,利用气体放电管的在未导通时低漏电流特性克服单独压敏电阻使用时漏电流过大容易起火的问题。利用压敏电阻的钳位高电压特性和气体放电管组合的高电压远远大于电

源的工作电压,使得电源的电流灌入不到电路中,相当于拦河坝。

[0103]

可选的,在上述实施例的基础上,图15为本发明实施例提供的又一种放电电路的结构示意图,该放电电路还包括第二压敏电阻mov2,至少两个开关型器件10串联连接后的第一端与放电电路的第二端v2电连接;至少两个开关型器件10串联连接后的第二端经第二压敏电阻mov2与放电电路的第三端v3电连接;至少两个开关型器件10串联连接后的第二端经第一压敏电阻mov1与放电电路的第一端v1电连接。

[0104]

其中,对于同一高频,高频阻抗模最小的阻抗支路20的高频阻抗模大于第二压敏电阻mov2的极间电容的高频阻抗模其中,c5为第二压敏电阻mov2的极间电容的容值,以使在放电电路的第二端v2和第三端v3上发生雷击等浪涌冲击时,开关型器件10的分压大,先导通;第二压敏电阻mov2的分压小,后导通。可选的,第二容性元件c2的容值小于第二压敏电阻mov2的极间电容的容值。第二压敏电阻mov2的极间电容可为第二压敏电阻mov2的寄生电容。可选的,放电电路的第一端v1可与火线电连接,放电电路的第三端v3可与零线电连接,放电电路的第二端v2可接地。

[0105]

图16为本发明实施例提供的又一种放电电路的结构示意图。图16示例性的画出高频阻抗模最小的阻抗支路为第二阻抗支路20-2,第一阻抗支路20-1中的第一子支路11包括第一阻性元件r1,第二阻抗支路20-2中的第二子支路21包括第二阻性元件r2的情况。工频状态下,第一容性元件c1和第二容性元件c2的容抗远大于第一阻性元件r1的阻抗,c1=c2,电压近似于第一开关型器件10-1和第二开关型器件10-2平分。浪涌状态下,频率大于或等于25000hz,第一容性元件c1和第二容性元件c2的容抗远小于r1第一阻性元件r1的阻抗,近似于浪涌电压由第一阻性元件r1与第二阻性元件r2按其阻值来分,r1:r2大于5:1,浪涌电压主要分布在第一阻性元件r1上,也就等于电压主要分布在第一开关型器件10-1上,当电压大于第一开关型器件10-1的脉冲电压,第一开关型器件10-1击穿(若第一开关型器件10-1为气体放电管,则气体放电管进入辉光态),第一开关型器件10-1击穿后,第一开关型器件10-1两端电压速降,此时浪涌电压主要分布于第二开关型器件10-2两端,第二开关型器件10-2被击穿。第一开关型器件10-1和第二开关型器件10-2均为气体放电管,每个气体放电管的直流击穿电压为1500v,脉冲电压为2000v,那么整个放电电路的脉冲电压小于2000+(1500

×

0.25)=2375v。如果第一开关型器件10-1没有并联第一并联阻抗支路20-1,第二开关型器件10-2没有并联第二并联阻抗支路20-2,则第一开关型器件10-1和第二开关型器件10-2串联后的脉冲电压为3500v,而在第一开关型器件10-1上并联第一并联阻抗支路20-1,第二开关型器件10-2上并联第二并联阻抗支路20-2,整个放电电路的脉冲电压小于2375v,脉冲电压降低3500

–

2375=1125v。

[0106]

示例性的,继续参见图5,第一开关型器件10-1和第二开关型器件10-2均为半导体放电管。每个半导体放电管的直流击穿电压为800v,脉冲电压为900v,交流环境,放电电路的耐压即为800*2/1.414=1131v,直流击穿电压为800*2=1600v,脉冲电压的计算为小于900+(800*(1+1)/[(1+1)+(5+1)]=1100v。将放电电路代替直流击穿电压为1600v的半导体放电管,直流击穿电压为1600v的半导体放电管的脉冲电压为1700v,则脉冲电压可以降低1700-1100=600v左右。

[0107]

示例性的,继续参见图8,第一开关型器件10-1为半导体放电管,第二开关型器件10-2为气体放电管。半导体放电管的直流击穿电压为800v,气体放电管的直流击穿电压为800v。工频状态下,工频电压主要分配在第一容性元件和第二容性元件c2上,半导体放电管与气体放电管近似各分一半。交流环境,放电电路的耐压约为(800+800)/1.414=1131v。浪涌冲击下,电压分配由第一子支路21和第二子支路22决定,第一子支路21的高频阻抗模远大于第二子支路22的高频阻抗模,电压主要分配在第一开关型器件10-1上,半导体放电管先击穿,随后气体放电管跟着击穿,整个放电电路击穿,放电电路的脉冲电压为气体放电管的脉冲电压+4v,4v为半导体放电管击穿后的电压,半导体放电管没有辉光区的说法,直流击穿电压为800v的气体放电管的脉冲电压为1200v,那么整个放电电路的击穿电压为1204v。将放电电路代替直流击穿电压为1600v的半导体放电管,直流击穿电压为1600v的半导体放电管的脉冲电压为1700v,则脉冲电压可以降低1700-1204=496v左右。

[0108]

本发明实施例提供一种浪涌保护电路。在上述实施例的基础上,继续参见图2,该浪涌保护电路包括本发明任意实施例提供的放电电路。

[0109]

其中,本发明实施例提供的浪涌保护电路包括上述实施例中的放电电路,因此本发明实施例提供的浪涌保护电路也具备上述实施例中所描述的有益效果,此处不再赘述。

[0110]

本发明实施例提供一种点火电路。在上述实施例的基础上,该点火电路包括本发明任意实施例提供的放电电路。

[0111]

其中,可选的,点火电路还可包括升压变压器、整流电路、储能电容和电嘴。在需要点火时,交流电源经升压变压器、整流电路升压整流后,向储能电容充电。当储能电容的充电电压达到放电电路的冲击击穿电压时导通,储能电容向电嘴释放电压,使电嘴击穿产生电火花,从而点燃发动机的燃烧室、燃气设备等中的燃气混合物。可将放电电路替代现有点火电路中的气体放电管。

[0112]

本发明实施例提供的点火电路包括上述实施例中的放电电路,因此本发明实施例提供的点火电路也具备上述实施例中所描述的有益效果,此处不再赘述。

[0113]

本发明实施例提供一种电子设备。图17为本发明实施例提供的一种电子设备的结构示意图。该电子设备100包括本发明任意实施例提供的放电电路。

[0114]

其中,该电子设备100可包括本发明任意实施例提供的浪涌保护电路或点火电路。电子设备100可以是电视机、笔记本电脑、空调、通信电源、摄像机、网络交换机等。本发明实施例提供的电子设备包括上述实施例中的放电电路,因此本发明实施例提供的电子设备也具备上述实施例中所描述的有益效果,此处不再赘述。

[0115]

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整、相互结合和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1